Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

Ξ·ΧΕΙ

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | H8S/2000                                                                        |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SCI, SSU, UART/USART                            |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 55                                                                              |

| Program Memory Size        | 192KB (192K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 12K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | -                                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r4f20114nfa-u0 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Classification     | Module/<br>Function                           | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial interfaces  | I <sup>2</sup> C bus<br>interface 2<br>(IIC2) | <ul> <li>One channel (SSU and selection format)</li> <li>Continuous transmission and reception possible</li> <li>Two transmission/reception formats         <ul> <li>I<sup>2</sup>C bus format: generates start and stop conditions in master mode automatically, acknowledge bit, master or slave operation</li> <li>Clock-synchronous serial format: no acknowledge bit, master operation only</li> </ul> </li> </ul> |

|                    | Hardware<br>LIN interface                     | One channel (timer RA and SCI3 used)                                                                                                                                                                                                                                                                                                                                                                                    |

| Event link control | ller (ELC)                                    | Events (interrupts) generated by peripheral modules can be<br>interconnected between modules, enabling cooperation between<br>the modules without CPU intervention.                                                                                                                                                                                                                                                     |

| I/O ports          |                                               | I/O pins                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    |                                               | — 55 (H8S/20103 and H8S/20115 Groups)                                                                                                                                                                                                                                                                                                                                                                                   |

|                    |                                               | <ul> <li>— 69 (H8S/20203, H8S/20223, H8S/20215, and H8S/20235</li> <li>Groups)</li> </ul>                                                                                                                                                                                                                                                                                                                               |

|                    |                                               | <ul><li>Pull-up resistors settable for all ports</li><li>LED driving capability</li></ul>                                                                                                                                                                                                                                                                                                                               |

# 2.2 CPU Operating Modes

The H8S/2000 CPU has two operating modes: normal and advanced. Note that this LSI supports only advanced mode. Advanced mode supports a maximum 16-Mbyte address space.

### 2.2.1 Advanced Mode

• Address space

Linear access to a maximum address space of 16 Mbytes is possible.

• Extended registers (En)

The extended registers (E0 to E7) can be used as 16-bit registers. They can also be used as the upper 16-bit segments of 32-bit registers or address registers.

• Instruction set

All instructions and addressing modes can be used.

• Exception vector table and memory indirect branch addresses

In advanced mode, the top area starting at H'00000000 is allocated to the exception vector table in 32-bit units. In each 32 bits, the upper 8 bits are ignored and a branch address is stored in the lower 24 bits (see figure 2.1). For details of the exception vector table, see section 3, Exception Handling.

# 2.4.1 General Registers

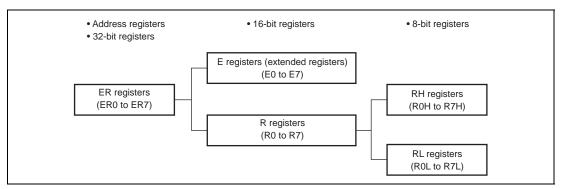

The H8S/2000 CPU has eight 32-bit general registers. These general registers are all functionally alike and can be used as both address registers and data registers. When a general register is used as a data register, it can be accessed as a 32-bit, 16-bit, or 8-bit register. Figure 2.5 illustrates the usage of the general registers. When the general registers are used as 32-bit registers or address registers, they are designated by the letters ER (ER0 to ER7).

When the general registers are used as 16-bit registers, the ER registers are divided into 16-bit general registers designated by the letters E (E0 to E7) and R (R0 to R7). These registers are functionally equivalent, providing a maximum sixteen 16-bit registers. The E registers (E0 to E7) are also referred to as extended registers.

When the general registers are used as 8-bit registers, the R registers are divided into 8-bit general registers designated by the letters RH (R0H to R7H) and RL (R0L to R7L). These registers are functionally equivalent, providing a maximum sixteen 8-bit registers.

The usage of each register can be selected independently.

General register ER7 has the function of the stack pointer (SP) in addition to its general-register function, and is used implicitly in exception handling and subroutine calls. Figure 2.6 shows the stack.

Figure 2.5 Usage of General Registers

| Instructio | n    | Size*        | Function                                                                                                        |

|------------|------|--------------|-----------------------------------------------------------------------------------------------------------------|

| AND        |      | B/W/L        | $Rd \land Rs \to Rd,  Rd \land \#IMM \to Rd$                                                                    |

|            |      |              | Performs a logical AND operation on a general register and another general register or immediate data.          |

| OR         |      | B/W/L        | $Rd \lor Rs \to Rd,  Rd \lor \#IMM \to Rd$                                                                      |

|            |      |              | Performs a logical OR operation on a general register and another general register or immediate data.           |

| XOR        |      | B/W/L        | $Rd \oplus Rs \to Rd,  Rd \oplus \#IMM \to Rd$                                                                  |

|            |      |              | Performs a logical exclusive OR operation on a general register and another general register or immediate data. |

| NOT        |      | B/W/L        | $\sim \mathrm{Rd}  ightarrow \mathrm{Rd}$                                                                       |

|            |      |              | Takes the one's complement (logical complement) of data in a general register.                                  |

| Note: *    | Size | refers to th | ne operand size.                                                                                                |

|            | B:   | Byte         |                                                                                                                 |

|            | W:   | Word         |                                                                                                                 |

|            | L:   | Longwor      | d                                                                                                               |

### Table 2.5 Logic Operations Instructions

# 2.9 Usage Notes

#### 2.9.1 TAS Instruction

Only register ER0, ER1, ER4, or ER5 should be used when using the TAS instruction. The H8S and H8/300 Series C/C++ Compiler of Renesas Electronics Corp. does not generate a TAS instruction. Accordingly, when a TAS instruction is used as a user-defined embedded function, register ER0, ER1, ER4, or ER5 should be used.

### 2.9.2 STM and LDM Instructions

The ER7 register is used as a stack pointer in an STM and LDM instructions. Accordingly, ER7 cannot be stored by STM or loaded by LDM. Two, three, or four registers can be stored or loaded by a single STM or LDM instruction. The combination of registers that can be stored or loaded are as follows.

- Two registers: ER0 and ER1, ER2 and ER3, or ER4 and ER5

- Three registers: ER0 to ER2 or ER4 to ER6

- Four registers: ER0 to ER3

The H8S and H8/300 Series C/C++ Compiler of Renesas Electronics Corp. does not generate an STM or LDM instruction that uses ER7.

### 2.9.3 Note on Bit Manipulation Instructions

Bit manipulation instructions such as BSET, BCLR, BNOT, BST, and BIST read data in byte units, perform bit manipulation, and write data in byte units. Thus, care must be taken when these bit manipulation instructions are executed for a register or port including write-only bits.

In addition, the BCLR instruction can be used to clear the flag of an internal I/O register. In this case, if the flag to be cleared has been set by an interrupt processing routine, the flag need not be read before executing the BCLR instruction.

#### (5) Port 6

### (a) Port 6 Peripheral Function Mapping Register 1 (PMCR61)

Address: H'FF0054

| Bit:               | b7 | b6         | b5 | b4 | b3 | b2 | b1         | b0 |

|--------------------|----|------------|----|----|----|----|------------|----|

|                    | _  | P61MD[2:0] |    |    | —  |    | P60MD[2:0] |    |

| Value after reset: | 0  | 1          | 0  | 1  | 0  | 1  | 0          | 1  |

| Bit    | Symbol     | Bit Name     | Description                                                       | R/W |

|--------|------------|--------------|-------------------------------------------------------------------|-----|

| 7      | _          | Reserved     | This bit is always read as 0. The write value should always be 0. | —   |

| 6 to 4 | P61MD[2:0] | P61 function | 000: Setting prohibited                                           | R/W |

|        |            | select       | 001: IRQ1 input                                                   |     |

|        |            |              | 010: RXD input (SCI3_1)                                           |     |

|        |            |              | 011: FTIOB input/output (timer RC)*                               |     |

|        |            |              | 100: TCLKB input (timer RG)                                       |     |

|        |            |              | 101: FTIOB0 input/output (timer RD_0)<br>(initial value)          |     |

|        |            |              | 110: TRGB input (timer RB)                                        |     |

|        |            |              | 111: Setting prohibited                                           |     |

| 3      | _          | Reserved     | This bit is always read as 0. The write value should always be 0. | —   |

| 2 to 0 | P60MD[2:0] | P60 function | 000: Setting prohibited                                           | R/W |

|        |            | select       | 001: IRQ0 input                                                   |     |

|        |            |              | 010: SCK3 input/output (SCI3_1)                                   |     |

|        |            |              | 011: FTIOA input/output (timer RC)*                               |     |

|        |            |              | 100: TCLKA input (timer RG)                                       |     |

|        |            |              | 101: FTIOA0 input/output (timer RD_0)<br>(initial value)          |     |

|        |            |              | 110: TREO output (timer RE)                                       |     |

|        |            |              | 111: Setting prohibited                                           |     |

H8S/20235 Groups. These bits are reserved and the function cannot be selected for these groups.

### (b) Port 6 Peripheral Function Mapping Register 2 (PMCR62)

| Address: H'FF0055  |    |    |            |    |    |    |            |    |  |  |

|--------------------|----|----|------------|----|----|----|------------|----|--|--|

| Bit:               | b7 | b6 | b5         | b4 | b3 | b2 | b1         | b0 |  |  |

|                    | _  |    | P63MD[2:0] |    |    |    | P62MD[2:0] |    |  |  |

| Value after reset: | 0  | 1  | 0          | 1  | 0  | 1  | 0          | 1  |  |  |

| Bit    | Symbol                                                                                         | Bit Name     | Description                                                       | R/W |

|--------|------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------|-----|

| 7      | <ul> <li>Reserved This bit is always read as 0. The write value should always be 0.</li> </ul> |              | —                                                                 |     |

| 6 to 4 | P63MD[2:0]                                                                                     | P63 function | 000: Setting prohibited                                           | R/W |

|        |                                                                                                | select       | 001: IRQ3 input                                                   |     |

|        |                                                                                                |              | 010: TRCOI input (timer RC)*                                      |     |

|        |                                                                                                |              | 011: FTIOD input/output (timer RC)*                               |     |

|        |                                                                                                |              | 100: TGIOB input/output (timer RG)                                |     |

|        |                                                                                                |              | 101: FTIOD0 input/output (timer RD_0)<br>(initial value)          |     |

|        |                                                                                                |              | 110: TRAO output (timer RA)                                       |     |

|        |                                                                                                |              | 111: Setting prohibited                                           |     |

| 3      | —                                                                                              | Reserved     | This bit is always read as 0. The write value should always be 0. | —   |

| 2 to 0 | P62MD[2:0]                                                                                     | P62 function | 000: Setting prohibited                                           | R/W |

|        |                                                                                                | select       | 001: IRQ2 input                                                   |     |

|        |                                                                                                |              | 010: TXD output (SCI3_1)                                          |     |

|        |                                                                                                |              | 011: FTIOC input/output (timer RC)*                               |     |

|        |                                                                                                |              | 100: TGIOA input/output (timer RG)                                |     |

|        |                                                                                                |              | 101: FTIOC0 input/output (timer RD_0)<br>(initial value)          |     |

|        |                                                                                                |              | 110: TRBO output (timer RB)                                       |     |

|        |                                                                                                |              | 111: Setting prohibited                                           |     |

H8S/20235 Groups. These bits are reserved and the function cannot be selected for these groups.

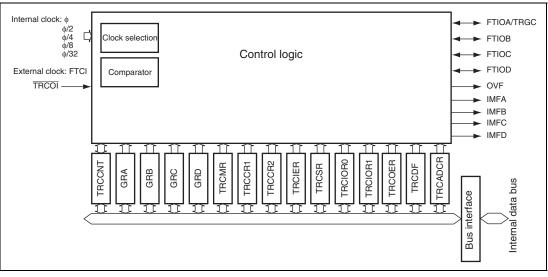

Figure 15.1 Timer RC Block Diagram

Table 15.2 summarizes the timer RC pins.

#### Table 15.2Pin Configuration

| Pin Name   | Input/<br>Output | Function                                                                                                |

|------------|------------------|---------------------------------------------------------------------------------------------------------|

| FTCI       | Input            | External clock input pin                                                                                |

| FTIOA/TRGC | I/O              | Output pin for GRA output compare/input pin for GRA input capture/<br>external trigger input pin (TRGC) |

| FTIOB      | I/O              | Output pin for GRB output compare/input pin for GRB input capture/<br>PWM output pin in PWM mode        |

| FTIOC      | I/O              | Output pin for GRC output compare/input pin for GRC input capture/<br>PWM output pin in PWM mode        |

| FTIOD      | I/O              | Output pin for GRD output compare/input pin for GRD input capture/<br>PWM output pin in PWM mode        |

| TRCOI      | Input            | Input pin for timer output disabling signal                                                             |

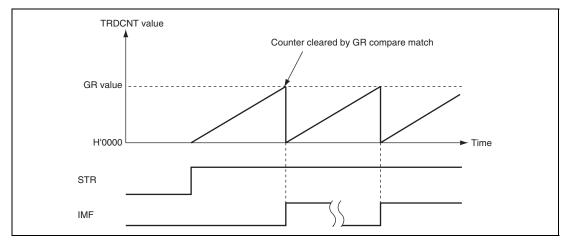

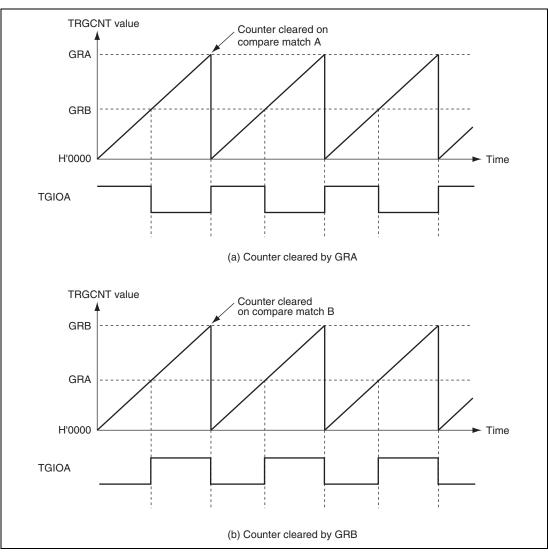

Figure 16.9 illustrates periodic counter operation.

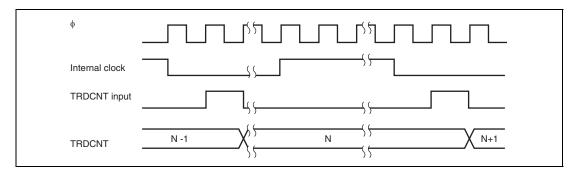

#### (2) TRDCNT Count Timing

• Internal clock operation

A system clock ( $\phi$ ), or four types of clocks ( $\phi/2$ ,  $\phi/4$ ,  $\phi/8$ , or  $\phi/32$ ) that are generated by dividing the system clock can be selected by bits TPSC2 to TPSC0 in TRDCR. Figure 16.10 illustrates this timing.

Figure 16.10 Count Timing in Internal Clock Operation

Figure 18.10 Example of PWM Mode Operation (1)

Figure 18.11 shows examples of PWM waveform output with 0% duty cycle and 100% duty cycle in PWM mode. When GRB compare match is set as the counter clearing source and the set value in GRA is greater than the value in GRB, the duty cycle of the PWM waveform is 0%. When GRA compare match is set as the counter clearing source and the set value in GRB is greater than the value in GRA, the duty cycle is 100%.

| Bit  | Symbol   | Bit Name             | Description                                                                           | R/W |

|------|----------|----------------------|---------------------------------------------------------------------------------------|-----|

| 4    | PM       | Parity mode          | (Enabled only when the PE bit is 1 in asynchronous mode)                              | R/W |

|      |          |                      | 0: Selects even parity.                                                               |     |

|      |          |                      | 1: Selects odd parity.                                                                |     |

| 3    | STOP     | Stop bit length      | (Enabled only in asynchronous mode)                                                   | R/W |

|      |          |                      | 0: 1 stop bit                                                                         |     |

|      |          |                      | 1: 2 stop bits                                                                        |     |

| 2    | MP       | Multiprocessor mode  | 0: The multiprocessor communication function is disabled.                             | R/W |

|      |          |                      | 1: The multiprocessor communication function is enabled $\ast^{\scriptscriptstyle 2}$ |     |

| 1, 0 | CKS[1:0] | Clock select 0 and 1 | 00:                                                                                   | R/W |

|      |          |                      | 01: φ/4 clock (n = 1)                                                                 |     |

|      |          |                      | 10: φ/14 clock (n = 2)                                                                |     |

|      |          |                      | 11: φ/64 clock (n = 3)                                                                |     |

Notes: 1. The SMR value is retained when (module) standby mode is entered.

2. In clocked synchronous mode, clear this bit to 0.

• STOP bit (stop bit length)

Selects the stop bit length in transmission. For reception, only the first stop bit is checked, regardless of the value in the bit. If the second stop bit is 0, it is treated as the start bit of the next transmit character.

• MP bit (multiprocessor mode)

When this bit is set to 1, the multiprocessor communication function is enabled. The PE bit and PM bit settings are invalid in multiprocessor mode.

• CKS[1:0] bits (clock select 1, 0)

These bits select the clock source for the baud rate generator.

For the relationship between the bit rate register setting and the baud rate, see section 20.2.8, Bit Rate Register (BRR). n is the decimal representation of the value of n in BRR (see section 20.2.8, Bit Rate Register (BRR)).

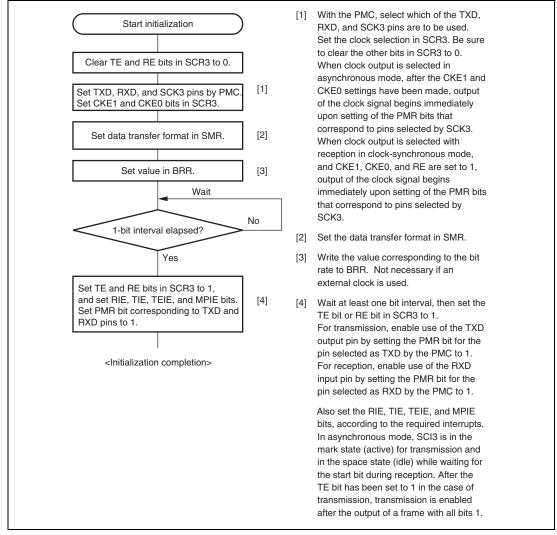

#### 20.3.2 SCI3 Initialization

Figure 20.4 shows a sample flowchart to initialize the SCI3. When the TE bit is cleared to 0, the TDRE flag is set to 1. Note that clearing the RE bit to 0 does not initialize the contents of the RDRF, PER, FER, and OER flags, or the contents of RDR. When the external clock is used in asynchronous mode, the clock must be supplied even during initialization.

#### Figure 20.4 Sample Flowchart for Initializing SCI3

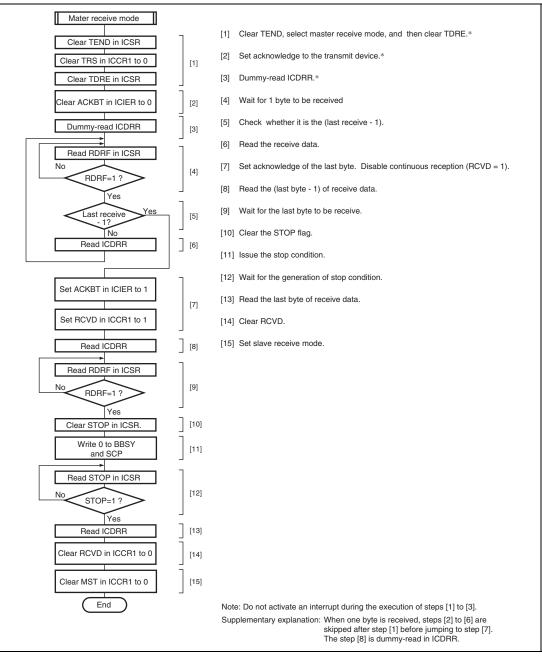

Figure 21.18 Sample Flowchart for Master Receive Mode

RENESAS

• SOOS bit (SSO/SSI pins open-drain output select)

Selects whether the serial data output pin is CMOS output or NMOS open-drain output. However, when the SSI output function is allocated to P57, this bit selects between NMOS push-pull output and NMOS open-drain output. The serial data output pin is changed according to the register setting value. For details, see section 22.3.3, Relationship between Data Input/Output Pin and Shift Register.

• CSOS bit (SCS pin open-drain output select)

Selects whether the serial data output pin is CMOS output or NMOS open-drain output. However, when the  $\overline{SCS}$  output function is allocated to P56, this bit selects between NMOS push-pull output and NMOS open-drain output.

• SSUMS bit (SSU mode select)

Selects which combination of the serial data input pin and serial data output pin is used. For details, see section 22.3.3, Relationship between Data Input/Output Pin and Shift Register.

| Bit   | Symbol        | Bit Name            | Description                                                                                                                               | R/W |

|-------|---------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4, 3  | _             | Reserved            | These bits are read as 0. The write value should be 0.                                                                                    | _   |

| 2     | ORER          | Overrun error flag  | [Setting condition]                                                                                                                       | R/W |

|       |               |                     | • When the next serial reception is completed while RDRF = 1                                                                              |     |

|       |               |                     | [Clearing condition]                                                                                                                      |     |

|       |               |                     | • When 0 is written to this bit after reading 1                                                                                           |     |

| 1     |               | Reserved            | These bits are read as 0. The write value should be 0.                                                                                    | —   |

| 0     | CE            | Conflict error flag | [Setting conditions]                                                                                                                      | R/W |

|       |               |                     | <ul> <li>When serial communication is started while<br/>SSUMS = 1 in SSMR2 and MSS = 1 in<br/>SSCRH, the SCS pin input is low</li> </ul>  |     |

|       |               |                     | <ul> <li>When the SCS pin level changes from low to<br/>high during transfer while SSUMS = 1 in<br/>SSMR2 and MSS = 0 in SSCRH</li> </ul> |     |

|       |               |                     | [Clearing condition]                                                                                                                      |     |

|       |               |                     | • When 0 is written to this bit after reading 1                                                                                           |     |

| Notes | s: In standby | mode, SSSR is rese  | et.                                                                                                                                       |     |

Notes: In standby mode, SSSR is reset.

- \* The DTC clears the peripheral module flags when all of the following three conditions are satisfied.

- 1. When the DISEL bit is 0.

- 2. When the transfer counter (DTC transfer count register A (CRA) in normal mode and repeat mode, or DTC transfer count register B (CRB) in block mode) is not 0.

- 3 When chain transfer is not used

- ORER bit (overrun error flag) •

Indicates that the RDRF bit is abnormally terminated in reception because an overrun error has occurred. SSRDR retains received data before the overrun error occurs and the received data after the overrun error occurs is lost. When this bit is set to 1, subsequent serial reception cannot be continued. When the MSS bit in SSCRH is 1, this is also applied to serial transmission.

### (2) Low Voltage Detect Interrupt 2 (LVDI2)

LVDI2 is an interrupt generated by the LVD2 circuit. Figure 26.8 shows the operation timing of LVDI2.

The LVD2 enters the module-standby state after release from a power-on reset. To operate the LVDI2, set the VD2E bit in LD2CRL to 1, wait for 50  $\mu$ s ( $t_{d(E-A)}$ ) until the detection voltage and the low-voltage detection circuit 2 operation have stabilized using a software timer, etc., then clear the VD2MS bit to 0 and set the VD2RE bit to 1 in LD2CRH. After that, the output settings of I/O ports must be made. To cancel the LVDI2, first the VD2RE bit in LD2CRH should be cleared to 0 and then the VD2E bit in LD2CRL should be cleared to 0. Figure 26.9 shows the procedure to set the LVDI2.

When the power-supply voltage falls below Vdet2, the LVDI2 clears the  $\overline{\text{LVDINT2}}$  signal to 0 and the VD2DFS bit in LD2CRH is set to 1. If the VD2DFS or VD2IRCS bit in LD2CRH is 1 at this time, an LVD2 interrupt request is simultaneously generated. In this case, the necessary data must be saved in the on-chip flash memory area or external EEPROM, etc, and a transition must be made to standby mode or sleep mode. Until this processing is completed, the power supply voltage must be higher than the lower limit of the guaranteed operating voltage.

When the power-supply voltage does not fall below Vdet0 but rises above Vdet2, the LVDI2 sets the  $\overline{\text{LVDINT2}}$  signal to 1 and set the VD2UF bit in LD2CRH to 1. If the VD2DFS bit in LD2CRH is 1 or the VD2IRCS bit in LD2CRH is 0 at this time, an LVD2 interrupt request is simultaneously generated.

If the power supply voltage falls below Vdet0, a power-on reset occurs.

| Register<br>Abbrevi-     |          |          |           |          |          |          |          |          |                       |

|--------------------------|----------|----------|-----------|----------|----------|----------|----------|----------|-----------------------|

| ation                    | Bit 7    | Bit 6    | Bit 5     | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | Module                |

| TRDOER2_23 <sup>∗⁵</sup> | PTO      | _        | _         | _        | _        | _        | _        | _        | Timer RD              |

| TRDOCR_23*⁵              | TOD1     | TOC1     | TOB1      | TOA1     | TOD0     | TOC0     | TOB0     | TOA0     | Unit 1<br>(channels 2 |

| TRDADCR_23*⁵             | ADTRGD1E | ADTRGC1E | ADTRGB1E  | ADTRGA1E | ADTRGD0E | ADTRGC0E | ADTRGB0E | ADTRGA0E |                       |

| ICCR1                    | ICE      | RCVD     | MST       | TRS      |          | CKS      | 6[3:0]   |          | IIC2/SSU              |

| SSCRH                    | _        | RSSTP    | MSS       | _        | _        |          | CKS[2:0] |          | -                     |

| ICCR2                    | BBSY     | SCP      | SDAO      | SDAOP    | SCLO     | _        | IICRST   | _        | -                     |

| SSCRL                    | _        | _        | SOL       | SOLP     | _        | _        | SRES     | _        | -                     |

| ICMR                     | MLS      | WAIT     | _         | _        | BCWP     |          | BC[2:0]  |          | -                     |

| SSMR                     | MLS      | CPOS     | CPHS      | _        | _        |          | BC[2:0]  |          | -                     |

| ICIER                    | TIE      | TEIE     | RIE       | NAKIE    | STIE     | ACKE     | ACKBR    | ACKBT    | -                     |

| SSER                     | TIE      | TEIE     | RIE       | TE       | RE       | _        | _        | CEIE     | -                     |

| ICSR                     | TDRE     | TEND     | RDRF      | NACKF    | STOP     | AL_OVE   | AAS      | ADZ      | -                     |

| SSSR                     | TDRE     | TEND     | RDRF      | _        | _        | ORER     | _        | CE       | -                     |

| SAR                      |          |          |           | SVA[6:0] |          |          |          | FS       | -                     |

| SSMR2                    | BIDE     | SCKS     | CS        | S[1:0]   | SCKOS    | SOOS     | CSOS     | SSUMS    | -                     |

| ICDRT                    |          |          |           |          |          |          |          |          | -                     |

| SSTDR                    |          |          |           |          |          |          |          |          | -                     |

| ICDRR                    |          |          |           |          |          |          |          |          | -                     |

| SSRDR                    |          |          |           |          |          |          |          |          | -                     |

| DADR0                    |          |          |           |          |          |          |          |          | D/A converter         |

| DADR1                    |          |          |           |          |          |          |          |          | -                     |

| DACR                     | DAOE1    | DAOE0    | _         | _        | _        | _        | _        | _        | -                     |

| IrCR                     | IrE      |          | IrCK[2:0] |          | IrTXINV  | IrRXINV  | _        | _        | SCI3_2<br>(IrDA)      |

| ADDR0                    |          |          |           |          |          |          |          |          | A/D converter         |

|                          |          |          | _         | _        | _        | _        | _        | _        | (unit 1)              |

| CMPR                     | CMP7     | CMP6     | CMP5      | CMP4     | CMP3     | CMP2     | CMP1     | CMP0     | -                     |

| ADDR1                    |          |          |           |          |          |          |          |          | _                     |

|                          |          |          | _         | _        | _        | _        | _        | _        | -                     |

# Section 28 Electrical Characteristics

# 28.1 Absolute Maximum Ratings

#### Table 28.1 Absolute Maximum Ratings

| Item                  |                                                             | Symbol          | Value                         | Unit | Notes |

|-----------------------|-------------------------------------------------------------|-----------------|-------------------------------|------|-------|

| Power supply ve       | oltage                                                      | V <sub>cc</sub> | –0.3 to +6.5                  | V    | *1    |

| Analog power s        | upply voltage                                               | $AV_{cc}$       | -0.3 to +6.5                  | V    |       |

| Input voltage         | All pins<br>(other than<br>AN pin, DA pin,<br>OSC1, and X1) | V <sub>IN</sub> | –0.3 to $V_{cc}$ +0.3         | V    |       |

|                       | AN pin, DA pin                                              | $AV_{IN}$       | –0.3 to AV <sub>cc</sub> +0.3 | V    |       |

|                       | OSC1, X1                                                    | V               | –0.3 to +1.65                 | V    | *2    |

|                       | OSC1                                                        | V <sub>IN</sub> | –0.3 to V $_{\rm cc}$ +0.3    | V    | *3    |

| Operating temperature |                                                             | $T_{opr}$       | N version: -20 to +85         | °C   | *4    |

|                       |                                                             |                 | D version: -40 to +85         | °C   |       |

| Storage temper        | ature                                                       | $T_{stg}$       | –55 to +125                   | °C   |       |

Notes: 1. Permanent damage may result if maximum ratings are exceeded. Normal operation should be under the conditions specified in Electrical Characteristics. Exceeding these values can result in incorrect operation and reduced reliability.

The OSC1 pin is used when the external oscillator function is selected. (PMRJ1 = 1, PMRJ0 = 1)

3. When the external clock input function is selected. (PMRJ1 = 0, PMRJ0 = 1)

4. N-version products are used for customer products. D-version products are used for customer products and industrial equipment.

| Item                                                                                                                  | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                    |                    |                     |

|-----------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|

| Section 9 Peripheral I/O<br>Mapping Controller<br>Table 9.1 Multiplexed Pin<br>Functions (Ports 1, 2, 3, 5,<br>and 6) | 237  | Amended                                                                                                                                                                                                                                                                                              |                    |                     |

|                                                                                                                       |      | Group 1                                                                                                                                                                                                                                                                                              | Pin Name           | Function 4          |

|                                                                                                                       |      | Port 1                                                                                                                                                                                                                                                                                               | Pm7                | <del>SCL/</del> SSI |

|                                                                                                                       |      | Port 2                                                                                                                                                                                                                                                                                               | Pm6 <del>SD/</del> | input/output        |

|                                                                                                                       |      | Port 3                                                                                                                                                                                                                                                                                               |                    | <del>SDA/</del> SCS |

|                                                                                                                       |      | Port 5                                                                                                                                                                                                                                                                                               |                    | input/output        |

|                                                                                                                       |      | Port 6                                                                                                                                                                                                                                                                                               |                    |                     |

|                                                                                                                       |      | <ul> <li>Notes: 1. The timer RC is not available on the H8S/20203, H8S/20223, H8S/20215, and H8S/20235 Groups; therefore, the function cannot be selected for these groups.</li> <li>2. The SCL and SDA functions for the IIC2 module are not allocatable to pins other than P56 and P57.</li> </ul> |                    |                     |

| 9.1 Register Description                                                                                              | 243  | Added                                                                                                                                                                                                                                                                                                |                    |                     |

| 9.1.2 Port Group 1                                                                                                    |      | Notes: 1. For the H8S/20103 and H8S/20115 Groups, P1<br>is not provided and P14MD[2:0] are reserved.<br>The initial value is B'001. The write value shoul<br>be B'001.                                                                                                                               |                    |                     |

| Peripheral Function Mapping<br>Registers 1 to 4 (PMCRn1 to<br>PMCRn4 ( $n = 1, 2, 3, 5, and$<br>6))                   |      |                                                                                                                                                                                                                                                                                                      |                    |                     |

| (c) Port 1 Peripheral Function<br>Mapping Register 3<br>(PMCR13)                                                      | l    |                                                                                                                                                                                                                                                                                                      |                    |                     |

| Item                                                                            | Page | Revision (See Manual for Details)                                                                                                                                                      |

|---------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.8 Usage Notes                                                                | 368  | Added                                                                                                                                                                                  |

| 11.8.4 Limitation on Usage of<br>the Interrupt Vector Offset<br>Register (VOFR) |      |                                                                                                                                                                                        |

| Section 12 Event Link<br>Controller                                             | 370  | Amended // //                                                                                                                                                                          |

| 12.1 Overview                                                                   |      |                                                                                                                                                                                        |

| Figure 12.1 Block Diagram of<br>Event Link Controller                           |      | ELSR0 to ELSR32                                                                                                                                                                        |

| 12.2 Register Descriptions                                                      | 372  | Amended                                                                                                                                                                                |

| 12.2.2 Event Link Setting<br>Registers 0 to 32 (ELSR0 to<br>ELSR32)             |      | Table 12.1 shows the correspondence between ELSR0 to ELSR32 and the peripheral modules                                                                                                 |

| 12.2.7 Port-Group Control<br>Registers 1 and 2 (PGC1 and<br>PGC2)               | 379  | Amended                                                                                                                                                                                |

| FGC2)                                                                           |      | The correspondence between PGC and ports is shown in table 12.3.                                                                                                                       |

| 12.2.8 Port Buffer Registers 1                                                  | 380  | Amended                                                                                                                                                                                |

| and 2 (PDBF1 and PDBF2)                                                         |      | PDBF is an 8-bit readable/writable register used in combination with PGR. For PDBF operations, see section 12.3, Operation. The correspondence of PDBF and PDR is shown in table 12.3. |

| 12.3 Operation                                                                  | 392  | Amended                                                                                                                                                                                |

| 12.3.5 Port Operation upon                                                      |      | (1) Single-Ports and Port-Groups                                                                                                                                                       |

| Event Input and Event<br>Generation                                             |      | A port-group can be set by specifying any two or<br>more bits in the port* to which an event can be<br>connected using the PGC register                                                |