Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Obsolete                                                   |

| Core Processor             | e300                                                       |

| Core Size                  | 32-Bit Single-Core                                         |

| Speed                      | 400MHz                                                     |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, USB OTG       |

| Peripherals                | DMA, WDT                                                   |

| Number of I/O              | 147                                                        |

| Program Memory Size        | -                                                          |

| Program Memory Type        | ROMIess                                                    |

| EEPROM Size                | -                                                          |

| RAM Size                   | 128K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.08V ~ 3.6V                                               |

| Data Converters            | -                                                          |

| Oscillator Type            | External                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                            |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 516-BBGA                                                   |

| Supplier Device Package    | 516-PBGA (27x27)                                           |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc5123vy400b |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Pin Assignments

| Г           |                    |                  | <b>J</b>           | -     |

|-------------|--------------------|------------------|--------------------|-------|

| Signal      | Package Pin Number | Pad Type         | Power Supply       | Notes |

| PCI_GNT0    | E25                | PCI              | V <sub>DD_IO</sub> | —     |

| PCI_GNT1    | G22                | PCI              | V <sub>DD_IO</sub> | —     |

| PCI_GNT2    | E24                | PCI              | V <sub>DD_IO</sub> | —     |

| PCI_CLK     | C26                | PCI              | V <sub>DD_IO</sub> | —     |

|             | PSC Inte           | erface (61 Total | )                  |       |

| PSC_MCLK_IN | C17                | General IO       | V <sub>DD_IO</sub> |       |

| PSC0_0      | D16                | General IO       | V <sub>DD_IO</sub> |       |

| PSC0_1      | A17                | General IO       | V <sub>DD_IO</sub> |       |

| PSC0_2      | E15                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC0_3      | C16                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC0_4      | B16                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC1_0      | C15                | General IO       | V <sub>DD_IO</sub> | —     |

| PSC1_1      | A16                | General IO       | V <sub>DD_IO</sub> | —     |

| PSC1_2      | E14                | General IO       | V <sub>DD_IO</sub> | —     |

| PSC1_3      | A15                | General IO       | V <sub>DD_IO</sub> | —     |

| PSC1_4      | D14                | General IO       | V <sub>DD_IO</sub> | —     |

| PSC2_0      | C14                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC2_1      | B14                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC2_2      | E13                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC2_3      | A14                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC2_4      | D13                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC3_0      | AF3                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC3_1      | AB5                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC3_2      | AC4                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC3_3      | AD4                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC3_4      | AF4                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC4_0      | AB1                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC4_1      | AA3                | General IO       | V <sub>DD_IO</sub> |       |

| PSC4_2      | AB3                | General IO       | V <sub>DD_IO</sub> |       |

| PSC4_3      | AA5                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC4_4      | AC2                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC5_0      | AC1                | General IO       | V <sub>DD_IO</sub> | _     |

| PSC5_1      | AC3                | General IO       | V <sub>DD_IO</sub> |       |

| PSC5_2      | AD1                | General IO       | V <sub>DD_IO</sub> |       |

Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 7 of 12)

#### **Pin Assignments**

| Signal          | Package Pin Number                                                                                                                                                                                                                                                                                                                      | Pad Type        | Power Supply      | Notes                |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|----------------------|

| V <sub>SS</sub> | A2, A3, A25, B1,B2,<br>B3, B5, B7, B12, B17,<br>B20, B22, B26, C1,<br>C4, C23, C25, D2,<br>D12, D17, D24, D25,<br>E18, F2, F3, F4, F5,<br>F6, F8, F10, F16, F17,<br>F21, G5, H6, H23,<br>H25, K6, K21, L6, L11,<br>L12, L13, L14, L15,<br>L16, L21, M2, M4,<br>M11, M12, M13, M14,<br>M15, M16, N5, N11,<br>N12, N13, N14, N15,<br>N16, | Ground          | _                 | _                    |

| V <sub>SS</sub> | N23, N25, P11, P12,<br>P13, P14, P15, P16,<br>R11, R12, R13, R14,<br>R15, R16, T6, T11,<br>T12, T13, T14, T15,<br>T16, T21, U2, U4, U6,<br>U21, V23, V25, Y24,<br>AA6, AA10, AA11,<br>AA16, AA17, AA21,<br>AB2, AB4, AB10,<br>AB24, AC8, AC12,<br>AC17, AC22, AD3,<br>AD25, AE7, AE12,<br>AE17, AE23, AE26                              | Ground          | _                 |                      |

| SYS_PLL_AVDD    | T22                                                                                                                                                                                                                                                                                                                                     | Analog Power    |                   | —                    |

| SYS_PLL_AVSS    | U22                                                                                                                                                                                                                                                                                                                                     | Analog Ground   |                   | —                    |

| CORE_PLL_AVDD   | AA19                                                                                                                                                                                                                                                                                                                                    | Analog Power    |                   | —                    |

| CORE_PLL_AVSS   | AD23                                                                                                                                                                                                                                                                                                                                    | Analog Ground   |                   | —                    |

| VBAT_RTC        | D19                                                                                                                                                                                                                                                                                                                                     | Power           |                   | —                    |

| AVDD_FUSEWR     | C9                                                                                                                                                                                                                                                                                                                                      | Power           | _                 | —                    |

| MVTT0           | AB7                                                                                                                                                                                                                                                                                                                                     | Analog Input    | SSTL(DDR2) Termir | nation (ODT) Voltage |

| MVTT1           | AF9                                                                                                                                                                                                                                                                                                                                     | Analog Input    | SSTL(DDR2) Termir | nation (ODT) Voltage |

| MVTT2           | AE11                                                                                                                                                                                                                                                                                                                                    | Analog Input    | SSTL(DDR2) Termir | nation (ODT) Voltage |

| MVTT3           | AE14                                                                                                                                                                                                                                                                                                                                    | Analog Input    | SSTL(DDR2) Termir | nation (ODT) Voltage |

|                 | Power and Grou                                                                                                                                                                                                                                                                                                                          | und Supplies (U | SB PHY)           |                      |

| USB_PLL_GND     | E23                                                                                                                                                                                                                                                                                                                                     | Analog Ground   | _                 |                      |

| USB_PLL_PWR3    | D23                                                                                                                                                                                                                                                                                                                                     | Analog Power    | —                 | —                    |

| USB_RREF        | E22                                                                                                                                                                                                                                                                                                                                     | Analog Power    | —                 | —                    |

| USB_VSSA_BIAS   | B23                                                                                                                                                                                                                                                                                                                                     | Analog Ground   | —                 |                      |

### Table 3. MPC5121e/MPC5123 TE-PBGA Pinout Listing (Sheet 11 of 12)

| Characteristic                                       | Condition                                                            | Symbol               | Min                                     | Max                                     | Unit | SpecID |

|------------------------------------------------------|----------------------------------------------------------------------|----------------------|-----------------------------------------|-----------------------------------------|------|--------|

| Input leakage current                                | RTC_XTALI Vin = 0 or V <sub>DD_IO</sub>                              | I <sub>IN</sub>      | _                                       | 1.0                                     | μA   | D3.23  |

| Input current, pullup resistor <sup>6</sup>          | Pullup $V_{DD_{IO}}$ Vin = VIL                                       | I <sub>INpu</sub>    | 25                                      | 150                                     | μA   | D3.24  |

| Input current,<br>pulldown resistor <sup>8</sup>     | Pulldown V <sub>DD_IO</sub> Vin = VIH                                | I <sub>INpd</sub>    | 25                                      | 150                                     | μA   | D3.25  |

| Output high voltage                                  | IOH is driver dependent <sup>7</sup> V <sub>DD_IO</sub>              | V <sub>OH</sub>      | $0.8 \times V_{DD_{-}IO}$               | —                                       | V    | D3.26  |

| Output high voltage                                  | IOH is driver dependent <sup>7</sup><br>V <sub>DD_MEM_IO_DDR</sub>   | V <sub>OHDDR</sub>   | 1.90                                    | —                                       | V    | D3.27  |

| Output high voltage                                  | IOH is driver dependent <sup>7</sup><br>V <sub>DD_MEM_IO_DDR2</sub>  | V <sub>OHDDR2</sub>  | 1.396                                   | _                                       | V    | D3.28  |

| Output high voltage                                  | IOH is driver dependent <sup>7</sup><br>V <sub>DD_MEM_IO_LPDDR</sub> | V <sub>OHLPDDR</sub> | V <sub>DD_MEM_IO</sub><br>- 0.28        |                                         | V    | D3.28  |

| Output low voltage                                   | IOL is driver dependent <sup>7</sup> V <sub>DD_IO</sub>              | V <sub>OL</sub>      | _                                       | $0.2 \times V_{DD_{-}IO}$               | V    | D3.30  |

| Output low voltage                                   | IOL is driver dependent <sup>7</sup><br>V <sub>DD_MEM_IO_DDR</sub>   | V <sub>OLDDR</sub>   |                                         | 0.36                                    | V    | D3.31  |

| Output low voltage                                   | IOL is driver dependent <sup>7</sup><br>VDD_MEM_IO_DDR2              | V <sub>OLDDR2</sub>  |                                         | 0.28                                    | V    | D3.32  |

| Output low voltage                                   | IOL is driver dependent <sup>7</sup><br>V <sub>DD_MEM_IO_LPDDR</sub> | V <sub>OLLPDDR</sub> |                                         | 0.28                                    | V    | D3.33  |

| Differential cross point<br>voltage<br>(DDR MCK/MCK) | _                                                                    | V <sub>OXMCK</sub>   | 0.5 x<br>V <sub>DD_MEM_IO</sub> – 0.125 | 0.5 ×<br>V <sub>DD_MEM_IO</sub> + 0.125 | V    | D3.34  |

| DC Injection Current<br>Per Pin <sup>8</sup>         | _                                                                    | I <sub>CS</sub>      | -1.0                                    | 1.0                                     | mA   | D3.35  |

| Input Capacitance<br>(digital pins)                  | _                                                                    | C <sub>in</sub>      |                                         | 7                                       | pF   | D3.36  |

| Input Capacitance<br>(analog pins)                   | _                                                                    | C <sub>in</sub>      |                                         | 10                                      | pF   | D3.37  |

| On Die Termination<br>(DDR2)                         | _                                                                    | R <sub>ODT</sub>     | 120                                     | 180                                     | Ω    | D3.38  |

<sup>1</sup> This parameter is meant for those who do not use quartz crystals or resonators, but CAN osc, in crystal mode. In that case, Vextal – Vxtal - 400mV criteria has to be met for oscillator's comparator to produce output clock.

<sup>2</sup> This parameter is meant for those who do not use quartz crystals or resonators, but signal generator clock to drive, in bypass mode. In that case, drive only the EXTAL pin not connecting anything to other pin for the oscillator's comparator to produce output clock.

<sup>3</sup> This parameter is meant for those who do not use quartz crystals or resonators, but CAN osc, in crystal mode. In that case, drive one of the XTAL\_IN or XTAL\_OUT pins not connecting anything to other pin for the oscillator's comparator to produce output clock.

<sup>4</sup> This parameter is meant for those who do not use quartz crystals or resonators, but signal generator clock to drive, in bypass mode. In that case, drive only the xtal\_in pin not connecting anything to other pin for the oscillator's comparator to produce output clock.

<sup>5</sup> Leakage current is measured with output drivers disabled and pull-up/pull-downs inactive.

<sup>6</sup> Pullup current is measured at VIL and pulldown current is measured at VIH.

- $^4\,$  Fall time is measured from 20% of vdd to 80% of V\_DD.

- <sup>5</sup> SYS\_XTALI duty cycle is measured at V<sub>M</sub>.

## 3.2.2 RTC Oscillator Electrical Characteristics

#### Table 13. RTC Oscillator Electrical Characteristics

| Characteristic      | Symbol                | Min | Typical | Max | Unit | SpecID |

|---------------------|-----------------------|-----|---------|-----|------|--------|

| RTC_XTALI frequency | f <sub>rtc_xtal</sub> |     | 32.768  |     | kHz  | O2.1   |

# 3.2.3 System PLL Electrical Characteristics

**Table 14. System PLL Specifications**

| Characteristic                                       | Symbol                   | Min | Typical | Max | Unit | SpecID |

|------------------------------------------------------|--------------------------|-----|---------|-----|------|--------|

| Sys PLL input clock frequency <sup>1</sup>           | f <sub>sys_xtal</sub>    | 16  | 33.3    | 67  | MHz  | O3.1   |

| Sys PLL input clock jitter <sup>2</sup>              | t <sub>jitter</sub>      |     | —       | 10  | ps   | O3.2   |

| Sys PLL VCO frequency <sup>1</sup>                   | f <sub>VCOsys</sub>      | 400 | _       | 800 | MHz  | O3.3   |

| Sys PLL VCO output jitter (Dj), peak to peak / cycle | f <sub>VCOjitterDj</sub> | _   | _       | 40  | ps   | O3.4   |

| Sys PLL VCO output jitter (Rj), RMS 1 sigma          | f <sub>VCOjitterRj</sub> | —   | —       | 12  | ps   | O3.5   |

| Sys PLL relock time—after power up <sup>3</sup>      | t <sub>lock1</sub>       | —   | —       | 200 | μs   | O3.6   |

| Sys PLL relock time—when power was on <sup>4</sup>   | t <sub>lock2</sub>       | —   | —       | 170 | μs   | O3.7   |

<sup>1</sup> The SYS\_XTALI frequency and PLL Configuration bits must be chosen such that the resulting system frequency, CPU (core) frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies.

<sup>2</sup> This represents total input jitter—short term and long term combined. Two different types of jitter can exist on the input to CORE\_SYSCLK, systemic and true random jitter. True random jitter is rejected. Systemic jitter is passed into and through the PLL to the internal clock circuitry.

<sup>3</sup> PLL relock time is the maximum amount of time required for the PLL lock after a stable VDD and CORE\_SYSCLK are reached during the power-on reset sequence.

<sup>4</sup> PLL relock time is the maximum amount of time required for the PLL lock after the PLL has been disabled and subsequently re-enabled during sleep modes.

# 3.2.4 e300 Core PLL Electrical Characteristics

The internal clocking of the e300 core is generated from and synchronized to the system clock by means of a voltage-controlled core PLL.

| Characteristic                      | Symbol               | Min | Typical | Max | Unit | SpecID |

|-------------------------------------|----------------------|-----|---------|-----|------|--------|

| e300 frequency <sup>1</sup>         | f <sub>core</sub>    | 200 |         | 400 | MHz  | O4.1   |

| e300 PLL VCO frequency <sup>1</sup> | f <sub>VCOcore</sub> | 400 | —       | 800 | MHz  | O4.3   |

| e300 PLL input clock frequency      | f <sub>CSB_CLK</sub> | 50  |         | 200 | MHz  | O4.4   |

| e300 PLL input clock cycle time     | t <sub>CSB_CLK</sub> | 5   | —       | 20  | ns   | O4.5   |

| e300 PLL relock time <sup>2</sup>   | t <sub>lock</sub>    | —   | —       | 200 | μS   | O4.6   |

Table 15. e300 PLL Specifications

# 3.3 AC Electrical Characteristics

# 3.3.1 Overview

Hyperlinks to the indicated timing specification sections are provided in the following:

- AC Operating Frequency Data

- Resets

- External Interrupts

- SDRAM (DDR)

- PCI

- LPC

- NFC

- PATA

- SATA PHY

- FEC

- USB ULPI

- On-Chip USB PHY

### AC Test Timing Conditions:

Unless otherwise noted, all test conditions are as follows:

- $T_{\rm A} = -40$  to 85 °C

- $V_{DD\_CORE} = 1.33 \text{ to } 1.47 \text{ V}$  $V_{DD\_IO} = 3.0 \text{ to } 3.6 \text{ V}$

- Input conditions: All Inputs: tr, tf  $\leq 1$  ns

- Output Loading: All Outputs: 50 pF

# 3.3.2 AC Operating Frequency Data

Table 16 provides the operating frequency information for the MPC5121e/MPC5123.

### Table 16. Clock Frequencies

|                     | Min  | Мах | Units | SpecID |

|---------------------|------|-----|-------|--------|

| e300 Processor Core | 200  | 400 | MHz   | A1.1   |

| SDRAM Clock         | 28.6 | 200 | MHz   | A1.2   |

| CSB Bus Clock       | 50.0 | 200 | MHz   | A1.3   |

| IP Bus Clock        | 8.3  | 83  | MHz   | A1.4   |

| PCI Clock           | 4.43 | 66  | MHz   | A1.5   |

| LPC Clock           | 2.08 | 83  | MHz   | A1.6   |

• DIU

•

**SDHC**

- SPDIF

- CAN

- · I<sup>2</sup>C

- J1850

- PSC

- GPIOs and Timers

- Fusebox

- IEEE 1149.1 (JTAG)

- VIU

**Electrical and Thermal Characteristics**

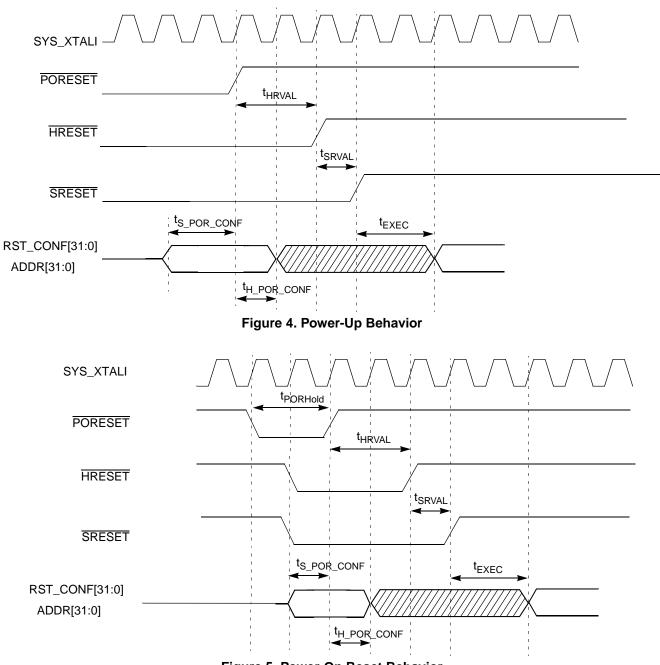

Figure 5. Power-On Reset Behavior

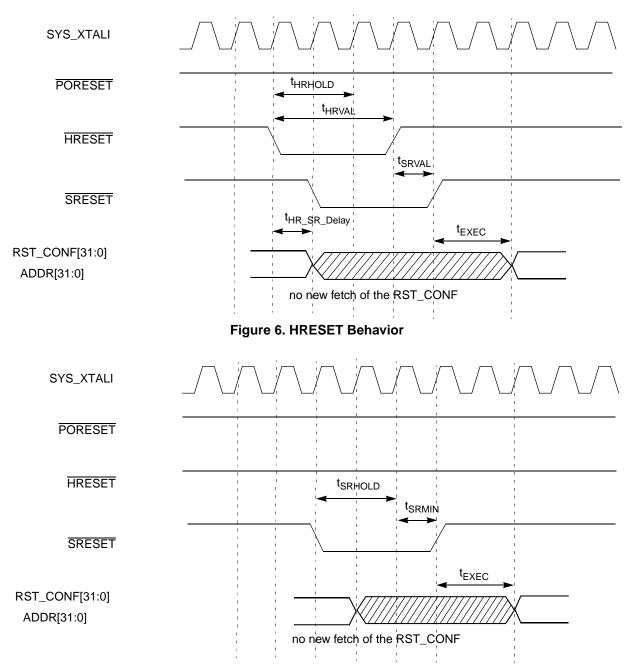

#### Figure 7. SRESET Behavior

#### Table 18. Reset Timing

| Symbol               | Description                                                    | Value<br>SYS_XTALI | SpecID |

|----------------------|----------------------------------------------------------------|--------------------|--------|

| t <sub>PORHOLD</sub> | Time PORESET must be held low before a qualified reset occurs  | 4 cycles           | A3.10  |

| t <sub>HRVAL</sub>   | Time HRESET is asserted after a qualified reset occurs         | 26810 cycles       | A3.11  |

| t <sub>SRVAL</sub>   | Time SRESET is asserted after assertion of HRESET              | 32 cycles          | A3.12  |

| t <sub>EXEC</sub>    | Time between SRESET assertion and first core instruction fetch | 4 cycles           | A3.13  |

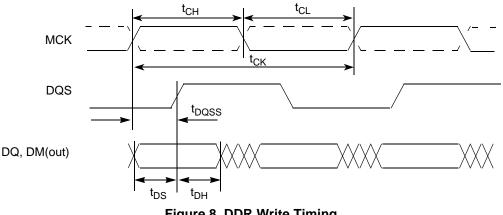

#### **DDR and DDR2 SDRAM AC Timing Specifications** 3.3.5.1

#### Table 20. DDR and DDR2 (DDR2-400) SDRAM Timing Specifications

At recommended operating conditions with V\_{DD \ MEM \ IO} of  $\pm 5\%$

| Parameter                                                         | Symbol                 | Min                         | Max                        | Unit            | Notes     | SpecID |

|-------------------------------------------------------------------|------------------------|-----------------------------|----------------------------|-----------------|-----------|--------|

| Clock cycle time, CL=x                                            | t <sub>CK</sub>        | 5000                        |                            | ps              |           | A5.1   |

| CK HIGH pulse width                                               | t <sub>CH</sub>        | 0.47                        | 0.53                       | t <sub>CK</sub> | 1,2       | A5.3   |

| CK LOW pulse width                                                | t <sub>CL</sub>        | 0.47                        | 0.53                       | t <sub>CK</sub> | 1,2       | A5.4   |

| Skew between MCK and DQS transitions                              | t <sub>DQSS</sub>      | -0.25                       | 0.25                       | t <sub>CK</sub> | 2,3       | A5.5   |

| Address and control output setup time relative to MCK rising edge | t <sub>OS(base)</sub>  | (t <sub>CK</sub> /2 – 750)  |                            | ps              | 2,3       | A5.6   |

| Address and control output hold time relative to MCK rising edge  | t <sub>OH(base)</sub>  | (t <sub>CK</sub> /2 – 750)  | _                          | ps              | 2,3       | A5.7   |

| DQ and DM output setup time relative to DQS                       | t <sub>DS1(base)</sub> | (t <sub>CK</sub> /4 – 500)  | _                          | ps              | 2,3       | A5.8   |

| DQ and DM output hold time relative to DQS                        | t <sub>DH1(base)</sub> | (t <sub>CK</sub> /4 – 500)  | _                          | ps              | 2,3       | A5.9   |

| DQS-DQ skew for DQS and associated DQ inputs                      | t <sub>DQSQ</sub>      | -(t <sub>CK</sub> /4 - 600) | (t <sub>CK</sub> /4 – 600) | ps              | 2         | A5.10  |

| DQS window start position related to CAS read command             | t <sub>DQSEN</sub>     | TBD                         | TBD                        | ps              | 1,2,3,4,5 | A5.11  |

1 Measured with clock pin loaded with differential 100 termination resistor.

<sup>2</sup> All transitions measured at mid-supply (VDD\_MEM\_IO/2).

Measured with all outputs except the clock loaded with 50  $\Omega$  termination resistor to V<sub>DD\_MEM\_IO</sub>/2. 3

4 In this window, the first rising edge of DQS should occur. From the start of the window to DQS rising edge, DQS should be low.

<sup>5</sup> Window position is given for  $t_{DQSEN} = 2.0 t_{CK}$ . For other values of  $t_{DQSEN}$ , window position is shifted accordingly.

Figure 8 shows the DDR SDRAM write timing.

Figure 8. DDR Write Timing

Figure 9 and Figure 10 shows the DDR SDRAM read timing.

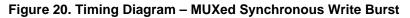

## 3.3.7.2 MUXed Mode

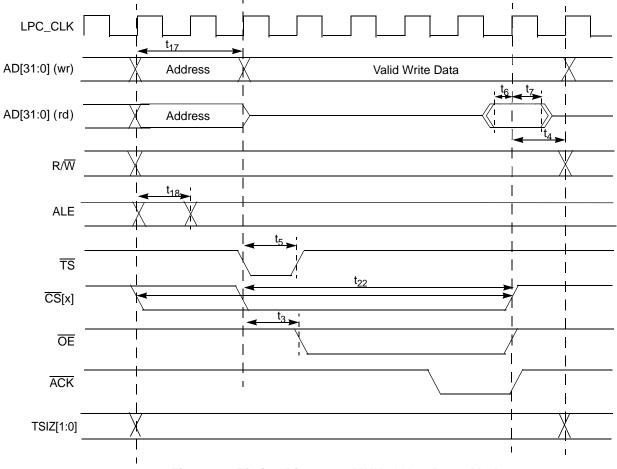

### 3.3.7.2.1 MUXed Non-Burst Mode

Figure 18. Timing Diagram – MUXed Non-Burst Mode

### NOTE

$\overline{ACK}$  is asynchonous input signal and has no timing requirements.  $\overline{ACK}$  needs to be deasserted after  $\overline{CS}[x]$  is deasserted.

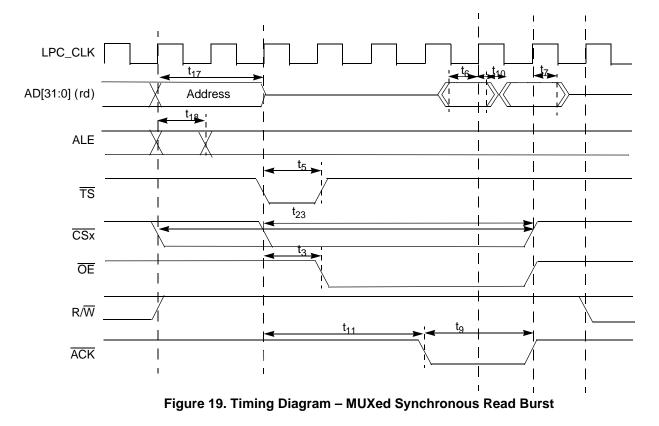

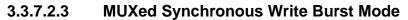

## 3.3.7.2.2 MUXed Synchronous Read Burst Mode

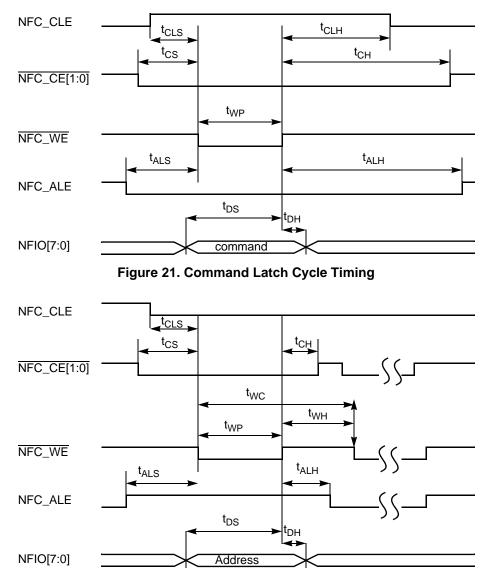

# 3.3.8 NFC

The NAND flash controller (NFC) implements the interface to standard NAND Flash memory devices. This section describes the timing parameters of the NFC.

Figure 22. Address Latch Cycle Timing

Timing parameters are explained in Table 31.

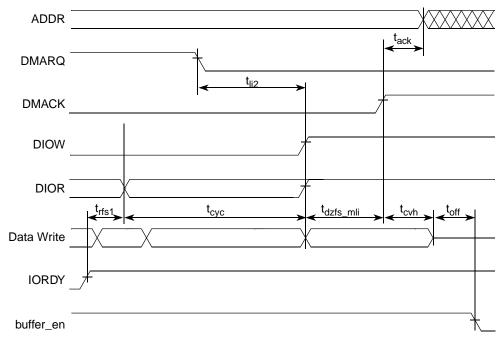

| ATA<br>Parameter  | UDMA Out<br>Timing<br>Parameter | Value                                                                                                                                | How to meet                                   | SpecID |

|-------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------|

| t <sub>ack</sub>  | t <sub>ack</sub>                | $t_{ack(min)} = (time_ack \times T) - (t_{skew1} + t_{skew2})$                                                                       | calculate and program time_ack. <sup>1</sup>  | A9.63  |

| t <sub>env</sub>  | t <sub>env</sub>                | $    t_{env(min)} = (time_env \times T) - (t_{skew1} + t_{skew2})     t_{env(max)} = (time_env \times T) + (t_{skew1} + t_{skew2}) $ | calculate and program time_env. <sup>1</sup>  | A9.64  |

| t <sub>dvs</sub>  | t <sub>dvs</sub>                | $t_{dvs} = (time_dvs \times T) - (t_{skew1} + t_{skew2})$                                                                            | calculate and program time_dvs. <sup>1</sup>  | A9.65  |

| t <sub>dvh</sub>  | t <sub>dvh</sub>                | $t_{dvs} = (time_dvh \times T) - (t_{skew1} + t_{skew2})$                                                                            | calculate and program time_dvh. <sup>1</sup>  | A9.66  |

| t <sub>cyc</sub>  | t <sub>cyc</sub>                | $t_{cyc} = time\_cyc \times T - (t_{skew1} + t_{skew2})$                                                                             | calculate and program time_cyc. <sup>1</sup>  | A9.67  |

| t <sub>2cyc</sub> | —                               | $t_{2cyc} = time_cyc \times 2 \times T$                                                                                              | calculate and program time_cyc. <sup>1</sup>  | A9.68  |

| t <sub>rfs1</sub> | t <sub>rfs1</sub>               | $t_{rfs1} = 1.6 \times T + t_{sui} + t_{co} + t_{buf} + t_{buf}$                                                                     | —                                             | A9.69  |

| _                 | t <sub>dzfs</sub>               | $t_{dzfs}$ = time_dzfs × T - ( $t_{skew1}$ )                                                                                         | calculate and program time_dzfs. <sup>1</sup> | A9.70  |

| t <sub>ss</sub>   | t <sub>ss</sub>                 | $t_{ss} = time\_ss \times T - (t_{skew1} + t_{skew2})$                                                                               | calculate and program time_ss. <sup>1</sup>   | A9.71  |

| t <sub>mli</sub>  | t <sub>dzfs_mli</sub>           | $t_{dzfs_mli} = max(time_dzfs, time_mli) \times T - (t_{skew1} + t_{skew2})$                                                         | -                                             | A9.72  |

| t <sub>li</sub>   | t <sub>li1</sub>                | t <sub>ii1</sub> > 0                                                                                                                 | —                                             | A9.73  |

| ATA<br>Parameter | UDMA Out<br>Timing<br>Parameter     | Value                                                                                | How to meet                                  | SpecID |

|------------------|-------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------|--------|

| t <sub>li</sub>  | t <sub>li2</sub>                    | t <sub>li2</sub> > 0                                                                 | —                                            | A9.74  |

| t <sub>li</sub>  | t <sub>li3</sub>                    | t <sub>ii3</sub> > 0                                                                 | —                                            | A9.75  |

| t <sub>cvh</sub> | t <sub>cvh</sub>                    | $t_{cvh} = (time_cvh \times T) - (t_{skew1} + t_{skew2})$                            | calculate and program time_cvh. <sup>1</sup> | A9.76  |

| _                | t <sub>on</sub><br>t <sub>off</sub> | $  t_{on} = time_on \times T - t_{skew1}   t_{off} = time_off \times T - t_{skew1} $ | —                                            | A9.77  |

Table 31. Timing Parameters UDMA Out Burst (continued)

<sup>1</sup> See the MPC5121e Microcontroller Reference Manual.

## 3.3.10 SATA PHY

1.5 Gbps SATA PHY Layer

See "Serial ATA: High Speed Serialized AT Attachment" Revision 1.0a, 7-January-2003.

# 3.3.11 FEC

AC Test Timing Conditions:

• Output Loading All Outputs: 25 pF

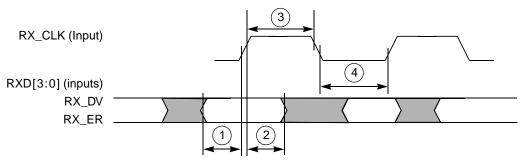

Table 32. MII Rx Signal Timing

| Symbol | Description                            | Min | Мах | Unit                       | SpecID |

|--------|----------------------------------------|-----|-----|----------------------------|--------|

| 1      | RXD[3:0], RX_DV, RX_ER to RX_CLK setup | 5   | _   | ns                         | A11.1  |

| 2      | RX_CLK to RXD[3:0], RX_DV, RX_ER hold  | 5   | _   | ns                         | A11.2  |

| 3      | RX_CLK pulse width high                | 35% | 65% | RX_CLK Period <sup>1</sup> | A11.3  |

| 4      | RX_CLK pulse width low                 | 35% | 65% | RX_CLK Period <sup>1</sup> | A11.4  |

<sup>1</sup> RX\_CLK shall have a frequency of 25% of data rate of the received signal. See the IEEE 802.3 Specification.

Figure 36. Ethernet Timing Diagram – MII Rx Signal

## 3.3.16 SPDIF

The Sony/Philips Digital Interface (SPDIF) timing is totally asynchronous, therefore there is no need for relationship with the clock.

# 3.3.17 CAN

The CAN functions are available as TX and CAN3/4\_RX pins at normal IO pads and as CAN1/2 RX pins at the VBAT\_RTC domain. There is no filter for the WakeUp dominant pulse. Any High-to-Low edge can cause WakeUp, if configured.

# 3.3.18 I<sup>2</sup>C

This section specifies the timing parameters of the Inter-Integrated Circuit (I<sup>2</sup>C) interface. Refer to the I<sup>2</sup>C Bus Specification.

| Symbol | Description                                                    | Min | Max | Units                     | SpecID |

|--------|----------------------------------------------------------------|-----|-----|---------------------------|--------|

| 1      | Start condition hold time                                      | 2   | —   | IP-Bus Cycle <sup>1</sup> | A18.1  |

| 2      | Clock low time                                                 | 8   |     | IP-Bus Cycle <sup>1</sup> | A18.2  |

| 4      | Data hold time                                                 | 0.0 |     | ns                        | A18.3  |

| 6      | Clock high time                                                | 4   | _   | IP-Bus Cycle <sup>1</sup> | A18.4  |

| 7      | Data setup time                                                | 0.0 |     | ns                        | A18.5  |

| 8      | Start condition setup time (for repeated start condition only) | 2   | _   | IP-Bus Cycle <sup>1</sup> | A18.6  |

| 9      | Stop condition setup time                                      | 2   |     | IP-Bus Cycle <sup>1</sup> | A18.7  |

Table 40. I<sup>2</sup>C Input Timing Specifications – SCL and SDA

<sup>1</sup> Inter Peripheral Clock is defined in the MPC5121e/MPC5123 *Reference Manual*.

#### Table 41. I<sup>2</sup>C Output Timing Specifications – SCL and SDA

| Symbol         | Description                                                    | Min | Max | Units                     | SpecID |

|----------------|----------------------------------------------------------------|-----|-----|---------------------------|--------|

| 1 <sup>1</sup> | Start condition hold time                                      | 6   | —   | IP-Bus Cycle <sup>2</sup> | A18.8  |

| 2 <sup>1</sup> | Clock low time                                                 | 10  | —   | IP-Bus Cycle <sup>2</sup> | A18.9  |

| 3 <sup>3</sup> | SCL/SDA rise time                                              |     | 7.9 | ns                        | A18.10 |

| 4 <sup>1</sup> | Data hold time                                                 | 7   | —   | IP-Bus Cycle <sup>2</sup> | A18.11 |

| 5 <sup>1</sup> | SCL/SDA fall time                                              |     | 7.9 | ns                        | A18.12 |

| 6 <sup>1</sup> | Clock high time                                                | 10  | _   | IP-Bus Cycle <sup>2</sup> | A18.13 |

| 7 <sup>1</sup> | Data setup time                                                | 2   | —   | IP-Bus Cycle <sup>2</sup> | A18.14 |

| 8 <sup>1</sup> | Start condition setup time (for repeated start condition only) | 20  | —   | IP-Bus Cycle <sup>2</sup> | A18.15 |

| 9 <sup>1</sup> | Stop condition setup time                                      | 10  | —   | IP-Bus Cycle <sup>2</sup> | A18.16 |

<sup>1</sup> Programming IFDR with the maximum frequency results in the minimum output timings listed. The I<sup>2</sup>C interface is designed to scale the data transition time, moving it to the middle of the SCL low period. The actual position is affected by the prescale and division values programmed in IFDR.

<sup>2</sup> Because SCL and SDA are open-drain-type outputs, which the processor can only actively drive low, the time SCL or SDA takes to reach a high level depends on external signal capacitance and pull-up resistor values.

<sup>3</sup> Inter Peripheral Clock is defined in the MPC5121e/MPC5123 Reference Manual.

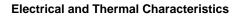

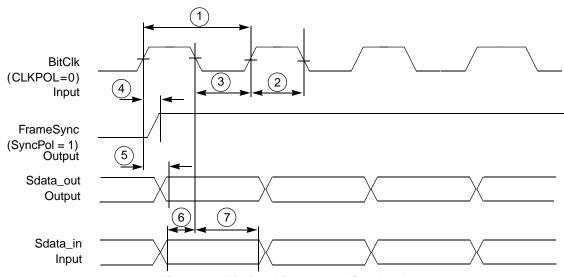

Figure 47. Timing Diagram – 8, 16, 24, and 32-bit CODEC/I<sup>2</sup>S Master Mode

| Table 43. Timing Specifications – 8, | 16, 24, and 32-bit CODEC/ | I <sup>2</sup> S Slave Mode |

|--------------------------------------|---------------------------|-----------------------------|

|--------------------------------------|---------------------------|-----------------------------|

| Symbol | Description                        | Min | Тур | Max  | Units          | SpecID |

|--------|------------------------------------|-----|-----|------|----------------|--------|

| 1      | Bit Clock cycle time               |     | —   | _    | ns             | A20.9  |

| 2      | Clock duty cycle                   | —   | 50  |      | % <sup>1</sup> | A20.10 |

| 3      | FrameSync setup time               | 1.0 | _   | _    | ns             | A20.11 |

| 4      | Output Data valid after clock edge | _   | _   | 14.0 | ns             | A20.12 |

| 5      | Input Data setup time              | 1.0 | _   | _    | ns             | A20.13 |

| 6      | Input Data hold time               | 1.0 | —   | _    | ns             | A20.14 |

<sup>1</sup> Bit Clock cycle time

#### NOTE

Output timing is specified at a nominal 50 pF load.

Figure 49. Timing Diagram – AC97 Mode

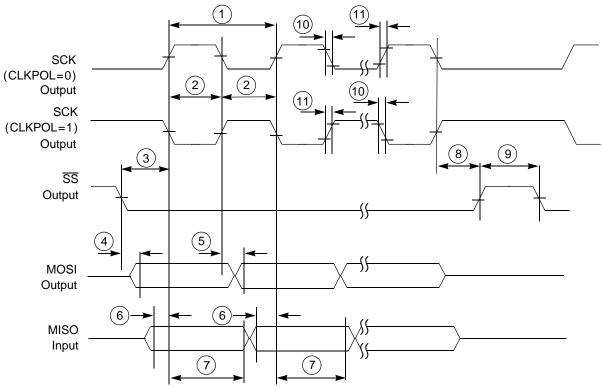

## 3.3.20.3 SPI Mode

| Symbol | Description                                                             |      | Max  | Units | SpecID |

|--------|-------------------------------------------------------------------------|------|------|-------|--------|

| 1      | SCK cycle time, programable in the PSC CCS register                     | 30.0 | _    | ns    | A20.26 |

| 2      | SCK pulse width, 50% SCK duty cycle                                     | 15.0 |      | ns    | A20.27 |

| 3      | Slave select clock delay, programable in the PSC CCS register           | 30.0 | _    | ns    | A20.28 |

| 4      | Output Data valid after Slave Select (SS)                               |      | 8.9  | ns    | A20.29 |

| 5      | Output Data valid after SCK                                             |      | 8.9  | ns    | A20.30 |

| 6      | Input Data setup time                                                   | 6.0  | _    | ns    | A20.31 |

| 7      | Input Data hold time                                                    |      | _    | ns    | A20.32 |

| 8      | Slave disable lag time                                                  |      | TSCK | ns    | A20.33 |

| 9      | Sequential Transfer delay, programmable in the PSC CTUR / CTLR register | 15.0 | _    | ns    | A20.34 |

| 10     | Clock falling time                                                      |      | 7.9  | ns    | A20.35 |

| 11     | Clock rising time                                                       |      | 7.9  | ns    | A20.36 |

## NOTE

Output timing is specified at a nominal 50 pF load.

**Electrical and Thermal Characteristics**

Figure 50. Timing Diagram – SPI Master Mode, Format 0 (CPHA = 0)

| Table 46. Timing Specifications | - SPI Slave Mode | , Format 0 | (CPHA = 0) |

|---------------------------------|------------------|------------|------------|

|---------------------------------|------------------|------------|------------|

| Symbol | Description                                                            |      | Max  | Units | SpecID |

|--------|------------------------------------------------------------------------|------|------|-------|--------|

| 1      | SCK cycle time, programable in the PSC CCS register                    | 30.0 |      | ns    | A20.37 |

| 2      | SCK pulse width, 50% SCK duty cycle                                    | 15.0 |      | ns    | A20.38 |

| 3      | Slave select clock delay                                               |      |      | ns    | A20.39 |

| 4      | Input Data setup time                                                  | 1.0  | _    | ns    | A20.40 |

| 5      | Input Data hold time                                                   | 1.0  |      | ns    | A20.41 |

| 6      | Output data valid after SS                                             | —    | 14.0 | ns    | A20.42 |

| 7      | Output data valid after SCK                                            | _    | 14.0 | ns    | A20.43 |

| 8      | Slave disable lag time                                                 |      | _    | ns    | A20.44 |

| 9      | Minimum Sequential Transfer delay = $2 \times IP$ Bus clock cycle time | 30.0 | _    | _     | A20.45 |

## NOTE

Output timing is specified at a nominal 50 pF load.

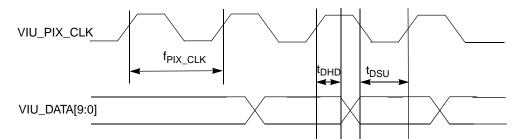

# 3.3.24 VIU

The Video Input Unit (VIU) is an interface which accepts the ITU656 format compatible video stream.

Figure 58 shows the VIU interface timing and Table 52 lists the timing parameters.

Figure 58. VIU Interface Timing Diagram

| Table 52. | VIU | Interface | Timing | Parameters |

|-----------|-----|-----------|--------|------------|

|-----------|-----|-----------|--------|------------|

| Parameter           | Description               | Min | Тур | Мах | Unit | SpecID |

|---------------------|---------------------------|-----|-----|-----|------|--------|

| f <sub>PIX_CK</sub> | VIU Pixel Clock Frequency | —   | _   | 83  | MHz  | A24.1  |

| t <sub>DSU</sub>    | VIU Data Setup Time       | 2.5 | _   | —   | ns   | A24.2  |

| t <sub>DHD</sub>    | VIU Data Hold Time        | 2.5 | —   | —   | ns   | A24.3  |

# 4 System Design Information

# 4.1 Power Up/Down Sequencing

Power sequencing between the 1.4 V power supply  $V_{DD\_CORE}$  and the remaining supplies is required to prevent excessive current during power up phase.

The required power sequence is as follows:

- Use 12 V/millisecond or slower time for all supplies.

- Power up V<sub>DD\_IO</sub>, PLL\_AV<sub>DD</sub>, V<sub>BAT\_RTC</sub> (if not applied permanently), V<sub>DD\_MEM\_IO</sub>, USB PHY, and SATA PHY supplies first in any order and then power up V<sub>DD\_CORE</sub>. If required, AV<sub>DD\_FUSEWR</sub> should be powered up afterwards.

- All the supplies must reach the specified operating conditions before the **PORESET** can be released.

- For power down, drop AV<sub>DD FUSEWR</sub> to 0 V first, drop V<sub>DD CORE</sub> to 0 V, and then drop all other supplies.

- V<sub>DD\_CORE</sub> should not exceed V<sub>DD\_IO</sub>, V<sub>DD\_MEM\_IO</sub>, V<sub>BAT\_RTC</sub>, or PLL\_AV<sub>DD</sub>s by more than 0.4 V at any time, including power-up.

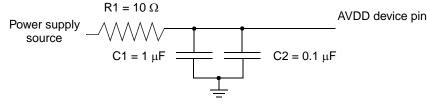

# 4.2 System and CPU Core AVDD Power Supply Filtering

Each of the independent PLL power supplies require filtering external to the device. The following drawing Figure 59 is a recommendation for the required filter circuit.

Each circuit should be placed as close as possible to the specific  $AV_{DD}$  pin being supplied to minimize noise coupled from nearby circuits.

All traces should be as low impedance as possible, especially ground pins to the ground plane.

The filter for System/Core  $PLLV_{DD}$  to  $V_{SS}$  should be connected to the power and ground planes, respectively, not fingers of the planes.

In addition to keeping the filter components for System/Core  $PLLV_{DD}$  as close as practical to the body of the MPC5121e as previously mentioned, special care should be taken to avoid coupling switching power supply noise or digital switching noise onto the portion of that supply between the filter and the MPC5121e.

Figure 59. Power Supply Filtering

The capacitors for C2 in Figure 59 should be rated X5R or better due to temperature performance. It is recommended to add a bypass capacitance of at least 1  $\mu$ F for the V<sub>BAT RTC</sub> pin.

# 4.3 Connection Recommendations

To ensure reliable operation, connect unused inputs to an appropriate signal level. Unused active low inputs should be tied to  $V_{DD}$  IO. Unused active high inputs should be connected to  $V_{SS}$ . All NC (no-connect) signals must remain unconnected.

Power and ground connections must be made to all external V<sub>DD</sub> and V<sub>SS</sub> pins of the MPC5121e/MPC5123.

The unused AV<sub>DD FUSEWR</sub> power should be connected to V<sub>SS</sub> directly or via a resistor.

For DDR or LPDDR modes the unused pins MVTT[3:0] for DDR2 Termination voltage can be unconnected.

Product Documentation

# 6 **Product Documentation**

This Data Sheet is labeled as a particular type: Product Preview, Advance Information, or Technical Data. Definitions of these types are available at: http://www.freescale.com.

Table 55 provides a revision history for this document.

| Table 55 | . Document | Revision | History |

|----------|------------|----------|---------|

|----------|------------|----------|---------|

| Revision       | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                             |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 0, DraftA | First Draft (5/2008)                                                                                                                                                                                                                                                                                                                                              |

| Rev. 0, DraftB | Second Draft (5/2008)                                                                                                                                                                                                                                                                                                                                             |

| Rev. 0, DraftC | Third Draft (7/2008)                                                                                                                                                                                                                                                                                                                                              |

| Rev. 1         | Advance Information (10/2008)                                                                                                                                                                                                                                                                                                                                     |

| Rev. 2         | Technical Data (2/2009)                                                                                                                                                                                                                                                                                                                                           |

| Rev. 3         | Technical Data (2/2009). Corrected Table 5, Footnote 3.                                                                                                                                                                                                                                                                                                           |

| Rev. 3.1       | Technical Data (12/2009). Interim release for removing AVDD_FUSERD throughout document, changing pin D9 to VDD_IO, and adding D9 to list of pins for VDD_IO.                                                                                                                                                                                                      |

| Rev. 4         | Technical Data (1/2010). Minor editorial and graphical updates.<br>No technical updates.                                                                                                                                                                                                                                                                          |

| Rev 5          | <ul> <li>Updated table "DDR and DDR2 SDRAM Timing Specification", removed<br/>the row of 'MCK AC differential crosspoint voltage'.</li> <li>Updated table "Thermal Resistance Data".</li> <li>Added table "NFC Timing Characteristics in Symmetric Mode "and<br/>added figure "Read data latch timing in Symmetric Mode".</li> <li>Published as Rev. 5</li> </ul> |