Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Betuils                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 69                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-TQFP                                                                          |

| Supplier Device Package    | 80-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc708-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

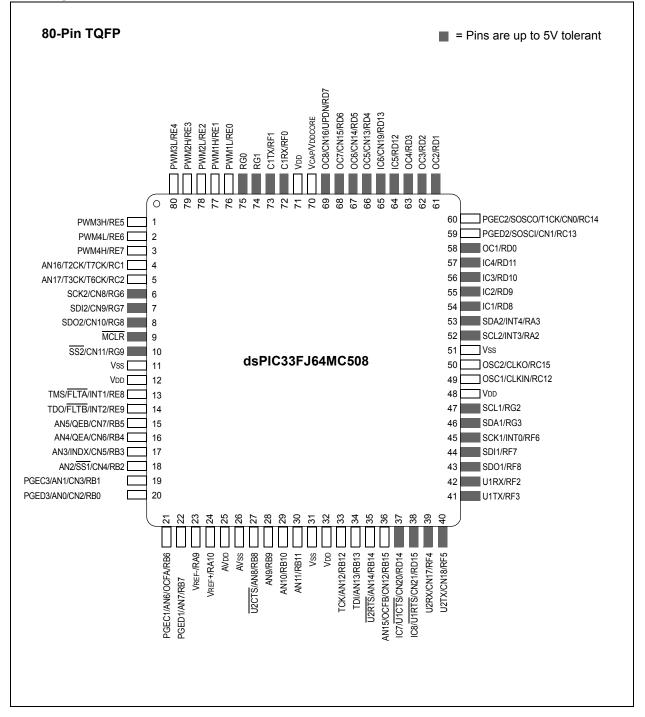

#### **Pin Diagrams (Continued)**

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 2, MPLAB ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip website.

- *"MPLAB<sup>®</sup> ICD 2 In-Circuit Debugger User's Guide"* DS51331

- *"Using MPLAB<sup>®</sup> ICD 2"* (poster) DS51265

- "MPLAB<sup>®</sup> ICD 2 Design Advisory" DS51566

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™" (poster) DS51749

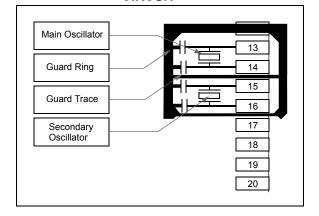

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

## FIGURE 2-3: SU OF

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

## 3.0 CPU

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2. "CPU"** (DS70204) in the *"dsPIC33F Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJXXXMCX06/X08/X10 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJXXXMCX06/X08/X10 devices have sixteen 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The dsPIC33FJXXXMCX06/X08/X10 instruction set has two classes of instructions: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C com-For most instructions, efficiency. piler the dsPIC33FJXXXMCX06/X08/X10 is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model for the dsPIC33FJXXXMCX06/X08/X10 is shown in Figure 3-2.

## 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The data space also includes 2 Kbytes of DMA RAM, which is primarily used for DMA data transfers but may be used as general purpose RAM.

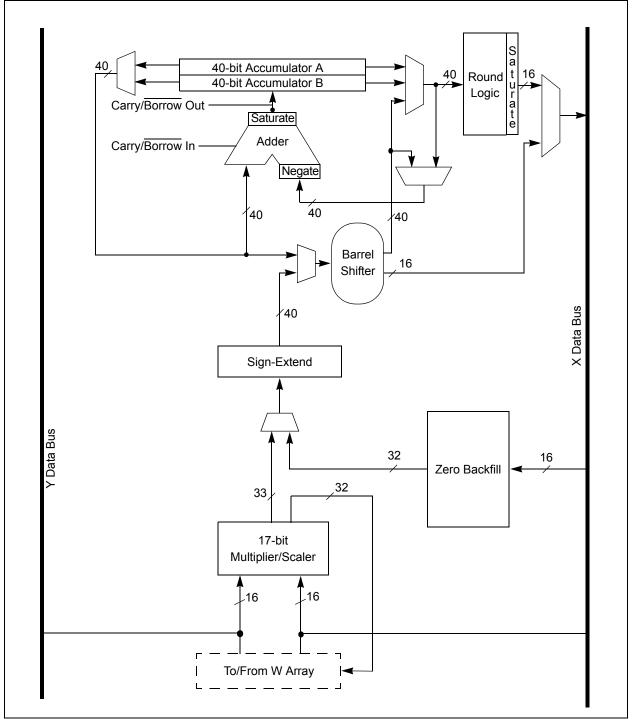

## 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM memory data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

## 4.2 Data Address Space

The dsPIC33FJXXXMCX06/X08/X10 CPU has a separate 16-bit wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. Data memory maps of devices with different RAM sizes are shown in Figure 4-3 through Figure 4-5.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

dsPIC33FJXXXMCX06/X08/X10 devices implement a total of up to 30 Kbytes of data memory. Should an EA point to a location outside of this area, an all-zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes of each word have even addresses, while the Most Significant Bytes have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> microcontrollers and improve data space memory usage efficiency, the dsPIC33FJXXXMCX06/X08/X10 instruction set supports both word and byte operations. As a consequence of byte accessibility, all effective address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSb of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A sign-extend instruction (SE) is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSb of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

### 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33FJXXXMCX06/X08/X10 core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Please refer to the corresponding device tables and pinout diagrams for device-specific information.

#### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area between 0x0000 and 0x1FFF is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

#### TABLE 4-13: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7         | Bit 6   | Bit 5 | Bit 4       | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|--------|----------|--------|--------|--------|-------|------------|---------------|---------|-------|-------------|--------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   |        | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0       | WAKE          | LPBACK  | ABAUD | URXINV      | BRGH   | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT       | URXISE        | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        | _      | _        | _      | _      | _      | —     |            |               |         | UART  | Transmit Re | gister |       |        |       | xxxx          |

| U1RXREG  | 0226        | _        | _      | _        | _      | _      | —      | _     |            |               |         | UART  | Receive Reg | gister |       |        |       | 0000          |

| U1BRG    | 0228        |          |        |          |        |        |        | Bau   | d Rate Ger | nerator Presc | aler    |       |             |        |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: UART2 REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7        | Bit 6   | Bit 5 | Bit 4       | Bit 3   | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------------|----------|--------|----------|--------|--------|--------|-------|----------|--------------|---------|-------|-------------|---------|-------|--------|-------|---------------|

| U2MODE      | 0230        | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0     | WAKE         | LPBACK  | ABAUD | URXINV      | BRGH    | PDSE  | _<1:0> | STSEL | 0000          |

| U2STA       | 0232        | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT     | URXISE       | EL<1:0> | ADDEN | RIDLE       | PERR    | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234        | _        | _      | —        | _      | _      | _      | _     |          |              |         | UART  | Transmit Re | egister |       |        |       | xxxx          |

| U2RXREG     | 0236        | _        | _      | —        | _      | _      | _      | _     |          |              |         | UART  | Receive Re  | gister  |       |        |       | 0000          |

| U2BRG       | 0238        |          |        |          |        |        |        | Bauc  | Rate Gen | erator Presc | aler    |       |             |         |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-15: SPI1 REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------------|--------|--------|---------|--------|--------|--------|------------|-------------|--------------|----------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI1STAT    | 0240        | SPIEN  | —      | SPISIDL | _      | _      | —      | —          |             |              | SPIROV   | —     | _     | —         |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1    | 0242        | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE         | SSEN         | CKP      | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2    | 0244        | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _      | _          | _           | _            | _        | _     | -     | _         | _     | FRMDLY | _      | 0000          |

| SPI1BUF     | 0248        |        |        |         |        |        |        | SPI1 Trans | mit and Red | ceive Buffer | Register |       |       |           |       |        |        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-16: SPI2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8       | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|---------|--------|--------|--------|-----------|-------------|--------------|----------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI2STAT | 0260        | SPIEN  | _      | SPISIDL | _      | _      | —      | _         | _           | _            | SPIROV   | _     | _     | _         | _     | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262        | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP       | CKE         | SSEN         | CKP      | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264        | FRMEN  | SPIFSD | FRMPOL  | -      | _      | _      | _         | _           | _            | _        | _     | _     | _         | _     | FRMDLY | _      | 0000          |

| SPI2BUF  | 0268        |        |        |         |        |        |        | SPI2 Tran | smit and Re | ceive Buffer | Register |       |       |           |       |        |        | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-32: PORTG REGISTER MAP<sup>(1)</sup>

| File | Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|------|------|------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|---------------|

| TRIS | G    | 02E4 | TRISG15 | TRISG14 | TRISG13 | TRISG12 |        |        | TRISG9 | TRISG8 | TRISG7 | TRISG6 | -     | -     | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF          |

| POR  | RTG  | 02E6 | RG15    | RG14    | RG13    | RG12    | _      | _      | RG9    | RG8    | RG7    | RG6    | _     | _     | RG3    | RG2    | RG1    | RG0    | xxxx          |

| LATO | G    | 02E8 | LATG15  | LATG14  | LATG13  | LATG12  | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | LATG3  | LATG2  | LATG1  | LATG0  | xxxx          |

| ODC  | G    | 06E4 | ODCG15  | ODCG14  | ODCG13  | ODCG12  |        |        | ODCG9  | ODCG8  | ODCG7  | ODCG6  |       |       | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-33: SYSTEM CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8 | Bit 7   | Bit 6  | Bit 5  | Bit 4      | Bit 3 | Bit 2          | Bit 1   | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|-----------|--------|--------|--------|-----------|-------|---------|--------|--------|------------|-------|----------------|---------|-------|---------------------|

| RCON      | 0740 | TRAPR  | IOPUWR | _         | _      | —      | _      | _         | VREGS | EXTR    | SWR    | SWDTEN | WDTO       | SLEEP | IDLE           | BOR     | POR   | <sub>XXXX</sub> (1) |

| OSCCON    | 0742 | _      | (      | COSC<2:0> | >      | —      | 1      | NOSC<2:0> | >     | CLKLOCK | _      | LOCK   | _          | CF    | _              | LPOSCEN | OSWEN | 0300 <b>(2)</b>     |

| CLKDIV    | 0744 | ROI    | [      | DOZE<2:0> | •      | DOZEN  | FI     | RCDIV<2:0 | )>    | PLLPOS  | T<1:0> |        |            | F     | PLLPRE<4:      | :0>     |       | 3040                |

| PLLFBD    | 0746 | _      | _      | _         | _      | _      | _      | _         |       |         |        | F      | PLLDIV<8:0 | )>    |                |         |       | 0030                |

| OSCTUN    | 0748 | -      | —      | _         | _      | —      | _      | _         |       | —       | —      |        |            | TUN   | <b> </b> <5:0> |         |       | 0000                |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values dependent on type of Reset.

2: OSCCON register Reset values dependent on the FOSC Configuration bits and type of Reset.

#### TABLE 4-34: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets   |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|--------|-------|--------|-------|-----------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | _      | _      | -      | -     | —     | —     | ERASE | _     | _     |        | NVMO  | P<3:0> |       | 0000 <b>(1)</b> |

| NVMKEY    | 0766 | -      | —      | _      | _      | _      |        |       | —     |       |       |       | NVMKE | Y<7:0> |       |        |       | 0000            |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-35: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|-------|--------|-------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEIMD  | PWMMD | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | C2MD  | C1MD   | AD1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD | IC1MD | OC8MD  | OC7MD | OC6MD | OC5MD  | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3      | 0774 | T9MD   | T8MD   | T7MD   | T6MD   | _      | _      | —     | _     | _      | _     | _     | _      | _      | _     | I2C2MD | AD2MD | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| R/W-0           | R/W-0          | R/W-0                                   | R/W-0            | R/W-0            | R/W-0            | R/W-0          | R/W-0   |

|-----------------|----------------|-----------------------------------------|------------------|------------------|------------------|----------------|---------|

| U2TXIF          | U2RXIF         | INT2IF                                  | T5IF             | T4IF             | OC4IF            | OC3IF          | DMA21IF |

| bit 15          |                |                                         |                  |                  |                  |                | bit 8   |

| R/W-0           | R/W-0          | R/W-0                                   | R/W-0            | R/W-0            | U-0              | R/W-0          | R/W-0   |

| IC8IF           | IC7IF          | AD2IF                                   | INT1IF           | CNIF             |                  | MI2C1IF        | SI2C1IF |

| bit 7           | 10711          | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                  | 0.111            |                  |                | bit C   |

| Legend:         |                |                                         |                  |                  |                  |                |         |

| R = Readable    | bit            | W = Writable                            | bit              | U = Unimple      | mented bit, read | d as '0'       |         |

| -n = Value at P | POR            | '1' = Bit is set                        |                  | '0' = Bit is cle | eared            | x = Bit is unk | nown    |

|                 |                |                                         |                  |                  |                  |                |         |

| bit 15          | U2TXIF: UAF    | RT2 Transmitte                          | r Interrupt Flag | g Status bit     |                  |                |         |

|                 |                | request has oc                          |                  |                  |                  |                |         |

|                 | -              | request has no                          |                  |                  |                  |                |         |

| bit 14          |                | RT2 Receiver I                          |                  | Status bit       |                  |                |         |

|                 | •              | request has oc<br>request has no        |                  |                  |                  |                |         |

| bit 13          | •              | rnal Interrupt 2                        |                  | t                |                  |                |         |

| bit 15          |                | request has oc                          | -                | l                |                  |                |         |

|                 |                | request has no                          |                  |                  |                  |                |         |

| bit 12          | T5IF: Timer5   | Interrupt Flag                          | Status bit       |                  |                  |                |         |

|                 |                | request has oc<br>request has no        |                  |                  |                  |                |         |

| bit 11          | -              | Interrupt Flag                          |                  |                  |                  |                |         |

|                 | 1 = Interrupt  | request has oc<br>request has no        | curred           |                  |                  |                |         |

| bit 10          | •              | ut Compare Ch                           |                  | upt Flag Status  | s bit            |                |         |

|                 | 1 = Interrupt  | request has oc<br>request has no        | curred           |                  |                  |                |         |

| bit 9           | •              | ut Compare Ch                           |                  | upt Flag Status  | s bit            |                |         |

|                 | 1 = Interrupt  | request has oc<br>request has no        | curred           |                  |                  |                |         |

| bit 8           |                |                                         |                  | Complete Inte    | rrupt Flag Statu | ıs bit         |         |

|                 |                | request has oc                          |                  | · · · · ·        |                  |                |         |

|                 | 0 = Interrupt  | request has no                          | t occurred       |                  |                  |                |         |

| bit 7           | IC8IF: Input ( | Capture Chann                           | el 8 Interrupt F | lag Status bit   |                  |                |         |

|                 | •              | request has oc                          |                  |                  |                  |                |         |

| hit 6           | -              | request has no                          |                  | Ing Status bit   |                  |                |         |

| bit 6           | 1 = Interrupt  | Capture Chann<br>request has oc         | curred           | -lag Status bit  |                  |                |         |

|                 | -              | request has no                          |                  |                  |                  |                |         |

| bit 5           |                | 2 Conversion C                          | •                | rupt Flag Statu  | is bit           |                |         |

|                 | 1 = Interrupt  | request has oc                          |                  |                  |                  |                |         |

|                 |                |                                         |                  |                  |                  |                |         |

| bit 4           | -              | rnal Interrupt 1                        |                  | t                |                  |                |         |

## REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

| REGISTER 7-26: IPC11: INTERRUPT PRIORITY CONTROL REGISTER 11 | <b>REGISTER 7-26:</b> |

|--------------------------------------------------------------|-----------------------|

|--------------------------------------------------------------|-----------------------|

| U-0                | R/W-1                   | R/W-0                                  | R/W-0                           | U-0              | R/W-1            | R/W-0           | R/W-0   |

|--------------------|-------------------------|----------------------------------------|---------------------------------|------------------|------------------|-----------------|---------|

| _                  |                         | T6IP<2:0>                              |                                 | —                |                  | DMA4IP<2:0>     |         |

| bit 15             |                         |                                        |                                 |                  |                  |                 | bit 8   |

| U-0                | U-0                     | U-0                                    | U-0                             | U-0              | R/W-1            | R/W-0           | R/W-0   |

|                    |                         |                                        |                                 |                  | 10/00-1          | OC8IP<2:0>      | 10,00-0 |

| bit 7              |                         |                                        |                                 |                  |                  | 00011 32.05     | bit     |

|                    |                         |                                        |                                 |                  |                  |                 |         |

| Legend:            |                         |                                        |                                 |                  |                  |                 |         |

| R = Readab         | le bit                  | W = Writable                           | oit                             | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value a       | It POR                  | '1' = Bit is set                       |                                 | '0' = Bit is cle | ared             | x = Bit is unkr | iown    |

|                    |                         |                                        |                                 |                  |                  |                 |         |

| bit 15             | Unimpleme               | nted: Read as 'o                       | )'                              |                  |                  |                 |         |

| bit 14-12          | T6IP<2:0>:              | Timer6 Interrupt                       | Priority bits                   |                  |                  |                 |         |

|                    | 111 = Interr            | upt is priority 7 (I                   | nighest priorit                 | y interrupt)     |                  |                 |         |

|                    | •                       |                                        |                                 |                  |                  |                 |         |

|                    | •                       |                                        |                                 |                  |                  |                 |         |

|                    | •<br>001 = Interr       | upt is priority 1                      |                                 |                  |                  |                 |         |

|                    |                         | upt is phoney is dis                   | abled                           |                  |                  |                 |         |

| bit 11             |                         | nted: Read as 'o                       |                                 |                  |                  |                 |         |

| bit 10-8           | -                       | 0>: DMA Channe                         |                                 | sfer Complete    | Interrunt Priori | tv hits         |         |

|                    |                         | upt is priority 7 (I                   |                                 | -                | interrupt i non  |                 |         |

|                    | •                       | арт ю р.:от, у (.                      |                                 | ,                |                  |                 |         |

|                    | •                       |                                        |                                 |                  |                  |                 |         |

|                    | •                       |                                        |                                 |                  |                  |                 |         |

|                    |                         | upt is priority 1<br>upt source is dis | ablad                           |                  |                  |                 |         |

|                    |                         | •                                      |                                 |                  |                  |                 |         |

| hit 7 2            | Ilnimnlama              | ntad: Dood on '/                       | `                               |                  |                  |                 |         |

|                    | -                       | nted: Read as '                        |                                 |                  |                  |                 |         |

|                    | OC8IP<2:0>              | : Output Compa                         | re Channel 8                    | -                | ity bits         |                 |         |

|                    | OC8IP<2:0>              |                                        | re Channel 8                    | -                | ity bits         |                 |         |

|                    | OC8IP<2:0>              | : Output Compa                         | re Channel 8                    | -                | ity bits         |                 |         |

|                    | OC8IP<2:0>              | : Output Compa                         | re Channel 8                    | -                | ity bits         |                 |         |

| bit 7-3<br>bit 2-0 | OC8IP<2:0> 111 = Intern | : Output Compa                         | re Channel 8<br>highest priorit | -                | ity bits         |                 |         |

## 7.4 Interrupt Setup Procedures

### 7.4.1 INITIALIZATION

To configure an interrupt source, do the following:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

Note: At a device Reset, the IPCx registers are initialized such that all user interrupt sources are assigned to priority level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

## 7.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address will depend on the programming language (i.e., C or assembler) and the language development tool suite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (level 8-level 15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

#### REGISTER 8-3: DMAXSTA: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER A

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|----------------------------------------------------------------------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |                                                                      |                  | STA   | <15:8>                                  |       |       |       |

| bit 15          |                                                                      |                  |       |                                         |       |       | bit 8 |

|                 |                                                                      |                  |       |                                         |       |       |       |

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |                                                                      |                  | STA   | <7:0>                                   |       |       |       |

| bit 7           |                                                                      |                  |       |                                         |       |       | bit 0 |

|                 |                                                                      |                  |       |                                         |       |       |       |

| Legend:         |                                                                      |                  |       |                                         |       |       |       |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |       | d as '0'                                |       |       |       |

| -n = Value at P | OR                                                                   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

#### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                               | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|-------------------------------------|------------------------------------|-------|-------|-------|

|                                    |       |       | STB                                 | <15:8>                             |       |       |       |

| bit 15                             |       |       |                                     |                                    |       |       | bit 8 |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                               | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |       | STE                                 | 3<7:0>                             |       |       |       |

| bit 7                              |       |       |                                     |                                    |       |       | bit 0 |

|                                    |       |       |                                     |                                    |       |       |       |

| Legend:                            |       |       |                                     |                                    |       |       |       |

| R = Readable bit W = Writable bit  |       |       | bit                                 | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unk |                                    | nown  |       |       |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

## 11.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired digital-only pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See **"Pin Diagrams"** for the available pins and their functionality.

## 11.3 Configuring Analog Port Pins

The ADxPCFGH, ADxPCFGL and TRIS registers control the operation of the ADC port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

Clearing any bit in the ADxPCFGH or ADxPCFGL register configures the corresponding bit to be an analog pin. This is also the Reset state of any I/O pin that has an analog (ANx) function associated with it.

| Note: | In devices with two ADC modules, if the     |

|-------|---------------------------------------------|

|       | corresponding PCFG bit in either            |

|       | AD1PCFGH(L) and AD2PCFGH(L) is              |

|       | cleared, the pin is configured as an analog |

|       | input.                                      |

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

| Note: | The voltage on an analog input pin can be |

|-------|-------------------------------------------|

|       | between -0.3V to (VDD + 0.3 V).           |

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 |

|------|------------|

| MOV  | W0, TRISBB |

| NOP  |            |

| btss | PORTB, #13 |

## 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

### 11.5 Input Change Notification

The input change notification function of the I/O ports allows the dsPIC33FJXXXMCX06/X08/X10 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature is capable of detecting input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 24 external signals (CN0 through CN23) that can be selected (enabled) for generating an interrupt request on a change-of-state.

There are four control registers associated with the CN module. The CNEN1 and CNEN2 registers contain the CN interrupt enable (CNxIE) control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source that is connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the weak pull-up enable (CNxPUE) bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

Note: Pull-ups on change notification pins should always be disabled whenever the port pin is configured as a digital output.

<sup>;</sup> Configure PORTB<15:8> as inputs ; and PORTB<7:0> as outputs ; Delay 1 cycle ; Next Instruction

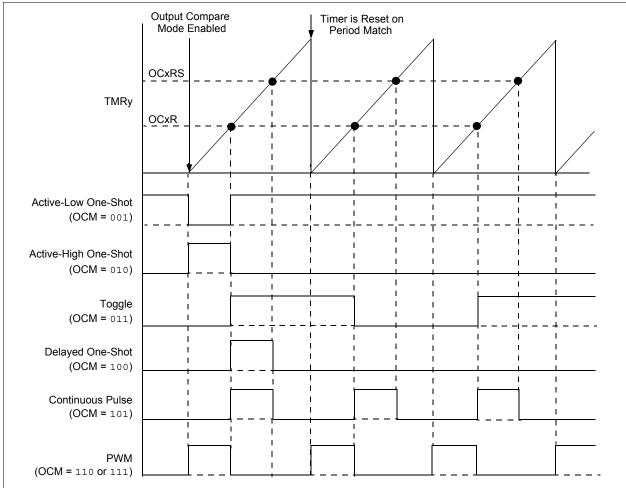

## 15.1 Output Compare Modes

Configure the Output Compare modes by setting the appropriate Output Compare Mode (OCM<2:0>) bits in the Output Compare Control (OCxCON<2:0>) register. Table 15-1 lists the different bit settings for the Output Compare modes. Figure 15-2 illustrates the output compare operation for various modes. The user

TABLE 15-1: OUTPUT COMPARE MODES

application must disable the associated timer when writing to the Output Compare Control registers to avoid malfunctions.

Note: See Section 13. "Output Compare" in the "dsPIC33F Family Reference Manual" (DS70209) for OCxR and OCxRS register restrictions.

| OCM<2:0> | Mode                         | OCx Pin Initial State                                                   | OCx Interrupt Generation         |  |  |

|----------|------------------------------|-------------------------------------------------------------------------|----------------------------------|--|--|

| 000      | Module Disabled              | Controlled by GPIO register                                             | _                                |  |  |

| 001      | Active-Low One-Shot          | 0                                                                       | OCx rising edge                  |  |  |

| 010      | Active-High One-Shot         | 1                                                                       | OCx falling edge                 |  |  |

| 011      | Toggle                       | Current output is maintained                                            | OCx rising and falling edge      |  |  |

| 100      | Delayed One-Shot             | 0                                                                       | OCx falling edge                 |  |  |

| 101      | Continuous Pulse             | 0                                                                       | OCx falling edge                 |  |  |

| 110      | PWM without Fault Protection | '0', if OCxR is zero<br>'1', if OCxR is non-zero                        | No interrupt                     |  |  |

| 111      | PWM with Fault Protection    | <ul><li>'0', if OCxR is zero</li><li>'1', if OCxR is non-zero</li></ul> | OCFA falling edge for OC1 to OC4 |  |  |

#### FIGURE 15-2: OUTPUT COMPARE OPERATION

## 19.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. Circuit™ "Inter-Integrated (l<sup>2</sup>C<sup>™</sup>)" (DS70195) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The Inter-Integrated Circuit ( $I^2C$ ) module, with its 16-bit interface, provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard.

The dsPIC33FJXXXMCX06/X08/X10 devices have up to two I<sup>2</sup>C interface modules, denoted as I2C1 and I2C2. Each I<sup>2</sup>C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each  $I^2C$  module 'x' (x = 1 or 2) offers the following key features:

- I<sup>2</sup>C interface supports both master and slave operation.

- I<sup>2</sup>C Slave mode supports 7- and 10-bit addresses.

- I<sup>2</sup>C Master mode supports 7- and 10-bit addresses.

- I<sup>2</sup>C Port allows bidirectional transfers between master and slaves.

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control).

- I<sup>2</sup>C supports multi-master operation; it detects bus collision and will arbitrate accordingly.

## 19.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The I<sup>2</sup>C module can operate either as a slave or a master on an I<sup>2</sup>C bus.

The following types of  $I^2C$  operation are supported:

- I<sup>2</sup>C slave operation with 7-bit address

- I<sup>2</sup>C slave operation with 10-bit address

- I<sup>2</sup>C master operation with 7 or 10-bit address

For details about the communication sequence in each of these modes, please refer to the "*dsPIC30F Family Reference Manual*".

## 19.2 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CSTAT are read/write.

I2CxRSR is the shift register used for shifting data, whereas I2CxRCV is the buffer register to which data bytes are written, or from which data bytes are read. I2CxRCV is the receive buffer. I2CxTRN is the transmit register to which bytes are written during a transmit operation.

The I2CxADD register holds the slave address. A status bit, ADD10, indicates 10-bit Address mode. The I2CxBRG acts as the Baud Rate Generator (BRG) reload value.

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV and an interrupt pulse is generated.

Internal Data Bus I2CxRCV Read SCLx Shift Clock I2CxRSR LSb  $\boxtimes$ SDAx Address Match Write Match Detect I2CxMSK Read Write I2CxADD Read Start and Stop Bit Detect Write Start and Stop I2CxSTAT Bit Generation Control Logic Read Collision Write Detect I2CxCON Acknowledge Read Generation Clock Stretching Write I2CxTRN LSb Read Shift Clock Reload Control Write BRG Down Counter I2CxBRG Read TCY/2

REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                            | U-0            | R/W-0 HC          | R/W-0                                 | R-0              | R-1          |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|---------------------------------------|------------------|--------------|--|--|--|--|

| UTXISEL1        | UTXINV                                                                                                                                                                                                                                                                                                                                                                                                    | UTXISEL0                                                                                                                         | —              | UTXBRK            | UTXEN <sup>(1)</sup>                  | UTXBF            | TRMT         |  |  |  |  |

| bit 15          |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |                |                   |                                       |                  | bit 8        |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |                |                   |                                       |                  |              |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                            | R-1            | R-0               | R-0                                   | R/C-0            | R-0          |  |  |  |  |

| URXIS           | EL<1:0>                                                                                                                                                                                                                                                                                                                                                                                                   | ADDEN                                                                                                                            | RIDLE          | PERR              | FERR                                  | OERR             | URXDA        |  |  |  |  |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |                |                   |                                       |                  | bit C        |  |  |  |  |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                                                                           | HC = Hardwa                                                                                                                      | re cleared     |                   |                                       |                  |              |  |  |  |  |

| R = Readable    | e bit                                                                                                                                                                                                                                                                                                                                                                                                     | W = Writable I                                                                                                                   | oit            | U = Unimpler      | nented bit, read                      | as '0'           |              |  |  |  |  |

| -n = Value at I | POR                                                                                                                                                                                                                                                                                                                                                                                                       | '1' = Bit is set                                                                                                                 |                | '0' = Bit is cle  | ared                                  | x = Bit is unkr  | nown         |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |                |                   |                                       |                  |              |  |  |  |  |

| bit 15,13       | UTXISEL<1:                                                                                                                                                                                                                                                                                                                                                                                                | <b>)&gt;:</b> Transmissio                                                                                                        | n Interrupt N  | lode Selection I  | bits                                  |                  |              |  |  |  |  |

| , -             | 11 = Reserve                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |                |                   |                                       |                  |              |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                           | •                                                                                                                                | ter is transfe | erred to the Trar | nsmit Shift Regis                     | ster, and as a r | esult, the   |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                           | buffer become                                                                                                                    |                |                   | <b>T</b>                              |                  | .,           |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                           | 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit                               |                |                   |                                       |                  |              |  |  |  |  |

|                 | •                                                                                                                                                                                                                                                                                                                                                                                                         | operations are completed<br>00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is |                |                   |                                       |                  |              |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                           | one character o                                                                                                                  |                |                   | U                                     | · ·              |              |  |  |  |  |

| bit 14          | UTXINV: Transmit Polarity Inversion bit                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |                |                   |                                       |                  |              |  |  |  |  |

|                 | <u>If IREN = 0:</u>                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |                |                   |                                       |                  |              |  |  |  |  |

|                 | 1 = UxTX Idle state is '0'<br>0 = UxTX Idle state is '1'                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |                |                   |                                       |                  |              |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |                |                   |                                       |                  |              |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>IREN = 1:</li> <li>IrDA<sup>®</sup> encoded UxTX Idle state is '1'</li> </ul>                                           |                |                   |                                       |                  |              |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                           | coded UxTX Id                                                                                                                    |                |                   |                                       |                  |              |  |  |  |  |

| bit 12          | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                | ted: Read as 'd                                                                                                                  | )'             |                   |                                       |                  |              |  |  |  |  |

| bit 11          | UTXBRK: Tra                                                                                                                                                                                                                                                                                                                                                                                               | ansmit Break bi                                                                                                                  | t              |                   |                                       |                  |              |  |  |  |  |

|                 | 1 = Send Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |                |                   |                                       |                  |              |  |  |  |  |

|                 | cleared by hardware upon completion<br>0 = Sync Break transmission disabled or completed                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |                |                   |                                       |                  |              |  |  |  |  |

| bit 10          | •                                                                                                                                                                                                                                                                                                                                                                                                         | smit Enable bit                                                                                                                  |                | completed         |                                       |                  |              |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |                |                   |                                       |                  |              |  |  |  |  |

|                 | <ul> <li>1 = Transmit enabled, UxTX pin controlled by UARTx</li> <li>0 = Transmit disabled, any pending transmission is aborted and buffer is reset. UxTX pin controlled</li> </ul>                                                                                                                                                                                                                       |                                                                                                                                  |                |                   |                                       |                  |              |  |  |  |  |

|                 | by port.                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |                |                   |                                       |                  |              |  |  |  |  |