Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 69                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 80-TQFP                                                                           |

| Supplier Device Package    | 80-TQFP (12x12)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc708t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name    | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                       |  |  |  |

|-------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AN0-AN31    | I           | Analog         | Analog input channels.                                                                                                                                                            |  |  |  |

| AVDD        | Р           | Р              | Positive supply for analog modules. This pin must be connected at all times.                                                                                                      |  |  |  |

| AVss        | Р           | Р              | Ground reference for analog modules.                                                                                                                                              |  |  |  |

| CLKI        | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                            |  |  |  |

| CLKO        | Ö           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associate with OSC2 pin function. |  |  |  |

| CN0-CN23    | I           | ST             | Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                         |  |  |  |

| C1RX        | I           | ST             | ECAN1 bus receive pin.                                                                                                                                                            |  |  |  |

| C1TX        | 0           | _              | ECAN1 bus transmit pin.                                                                                                                                                           |  |  |  |

| C2RX        | I           | ST             | ECAN2 bus receive pin.                                                                                                                                                            |  |  |  |

| C2TX        | 0           | _              | ECAN2 bus transmit pin.                                                                                                                                                           |  |  |  |

| PGED1       | I/O         | ST             | Data I/O pin for programming/debugging communication channel 1.                                                                                                                   |  |  |  |

| PGEC1       | I.          | ST             | Clock input pin for programming/debugging communication channel 1.                                                                                                                |  |  |  |

| PGED2       | I/O         | ST             | Data I/O pin for programming/debugging communication channel 2.                                                                                                                   |  |  |  |

| PGEC2       | I           | ST             | Clock input pin for programming/debugging communication channel 2.                                                                                                                |  |  |  |

| PGED3       | I/O         | ST             | Data I/O pin for programming/debugging communication channel 3.                                                                                                                   |  |  |  |

| PGEC3       |             | ST             | Clock input pin for programming/debugging communication channel 3.                                                                                                                |  |  |  |

| IC1-IC8     | I           | ST             | Capture inputs 1 through 8.                                                                                                                                                       |  |  |  |

| INDX        | I           | ST             | Quadrature Encoder Index Pulse input.                                                                                                                                             |  |  |  |

| QEA         | 1           | ST             | Quadrature Encoder Phase A input in QEI mode. Auxiliary Timer External                                                                                                            |  |  |  |

|             |             |                | Clock/Gate input in Timer mode.                                                                                                                                                   |  |  |  |

| QEB         | 1           | ST             | Quadrature Encoder Phase A input in QEI mode. Auxiliary Timer External                                                                                                            |  |  |  |

|             |             |                | Clock/Gate input in Timer mode.                                                                                                                                                   |  |  |  |

| UPDN        | 0           | CMOS           | Position Up/Down Counter Direction State.                                                                                                                                         |  |  |  |

| INT0        | I           | ST             | External interrupt 0.                                                                                                                                                             |  |  |  |

| INT1        | 1           | ST             | External interrupt 1.                                                                                                                                                             |  |  |  |

| INT2        | 1           | ST             | External interrupt 2.                                                                                                                                                             |  |  |  |

| INT3        | 1           | ST             | External interrupt 3.                                                                                                                                                             |  |  |  |

| INT4        | I I         | ST             | External interrupt 4.                                                                                                                                                             |  |  |  |

| FLTA        | I           | ST             | PWM Fault A input.                                                                                                                                                                |  |  |  |

| FLTB        | 1           | ST             | PWM Fault B input.                                                                                                                                                                |  |  |  |

| PWM1L       | 0           | —              | PWM 1 low output.                                                                                                                                                                 |  |  |  |

| PWM1H       | 0           | _              | PWM 1 high output.                                                                                                                                                                |  |  |  |

| PWM2L       | 0           | _              | PWM 2 low output.                                                                                                                                                                 |  |  |  |

| PWM2H       | 0           | _              | PWM 2 high output.                                                                                                                                                                |  |  |  |

| PWM3L       | 0           | —              | PWM 3 low output.                                                                                                                                                                 |  |  |  |

| PWM3H       | 0           | _              | PWM 3 high output.                                                                                                                                                                |  |  |  |

| PWM4L       | 0           | —              | PWM 4 low output.                                                                                                                                                                 |  |  |  |

| PWM4H       | 0           | —              | PWM 4 high output.                                                                                                                                                                |  |  |  |

| MCLR        | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                        |  |  |  |

| OCFA        | I           | ST             | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).                                                                                                                       |  |  |  |

| OCFB        | I           | ST             | Compare Fault B input (for Compare Channels 5, 6, 7 and 8).                                                                                                                       |  |  |  |

| OC1-OC8     | 0           |                | Compare outputs 1 through 8.                                                                                                                                                      |  |  |  |

| OSC1        | I           | ST/CMOS        |                                                                                                                                                                                   |  |  |  |

| OSC2        | I/O         | —              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                          |  |  |  |

| Legend: CMC | S = CMO     | S compatible   | e input or output Analog = Analog input P = Power                                                                                                                                 |  |  |  |

|             |             |                | with CMOS levels $O = Output$ I = Input                                                                                                                                           |  |  |  |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS

© 2009 Microchip Technology Inc.

| TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)                                                                                                  |                                                                            |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                                                                                                        | Pin<br>Type                                                                | Buffer<br>Type                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| RA0-RA7                                                                                                                                         | I/O                                                                        | ST                                                               | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| RA9-RA10                                                                                                                                        | I/O                                                                        | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| RA12-RA15                                                                                                                                       | I/O                                                                        | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| RB0-RB15                                                                                                                                        | I/O                                                                        | ST                                                               | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| RC1-RC4                                                                                                                                         | I/O                                                                        | ST                                                               | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| RC12-RC15                                                                                                                                       | I/O                                                                        | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| RD0-RD15                                                                                                                                        | I/O                                                                        | ST                                                               | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| RE0-RE9                                                                                                                                         | I/O                                                                        | ST                                                               | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| RF0-RF8                                                                                                                                         | I/O                                                                        | ST                                                               | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| RF12-RF13                                                                                                                                       |                                                                            | _                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| RG0-RG3                                                                                                                                         | I/O                                                                        | ST                                                               | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| RG6-RG9                                                                                                                                         | I/O                                                                        | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| RG12-RG15                                                                                                                                       | I/O                                                                        | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| SCK1                                                                                                                                            | I/O                                                                        | ST                                                               | Synchronous serial clock input/output for SPI1.                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| SDI1                                                                                                                                            | I                                                                          | ST                                                               | SPI1 data in.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| SDO1                                                                                                                                            | 0                                                                          | _                                                                | SPI1 data out.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| SS1                                                                                                                                             | I/O                                                                        | ST                                                               | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| SCK2                                                                                                                                            | I/O                                                                        | ST                                                               | Synchronous serial clock input/output for SPI2.                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| SDI2                                                                                                                                            | I                                                                          | ST                                                               | SPI2 data in.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| SDO2                                                                                                                                            | 0                                                                          | -                                                                | SPI2 data out.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| SS2                                                                                                                                             | I/O                                                                        | ST                                                               | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| SCL1                                                                                                                                            | I/O                                                                        | ST                                                               | Synchronous serial clock input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| SDA1                                                                                                                                            | I/O                                                                        | ST                                                               | Synchronous serial data input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| SCL2                                                                                                                                            | I/O                                                                        | ST                                                               | Synchronous serial clock input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| SDA2                                                                                                                                            | I/O                                                                        | ST                                                               | Synchronous serial data input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| SOSCI                                                                                                                                           |                                                                            | ST/CMOS                                                          | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                                                                                                                                                                                                                                    |  |  |

| SOSCO                                                                                                                                           | 0                                                                          |                                                                  | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| TMS                                                                                                                                             | I                                                                          | ST                                                               | JTAG Test mode select pin.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| TCK                                                                                                                                             | I                                                                          | ST                                                               | JTAG test clock input pin.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| TDI                                                                                                                                             |                                                                            | ST                                                               | JTAG test data input pin.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| TDO                                                                                                                                             | 0                                                                          | —                                                                | JTAG test data output pin.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| T1CK                                                                                                                                            |                                                                            |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                                                                                                                                                 | I                                                                          | ST                                                               | Timer1 external clock input.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| T2CK                                                                                                                                            |                                                                            | ST                                                               | Timer2 external clock input.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| T2CK<br>T3CK                                                                                                                                    |                                                                            | ST<br>ST                                                         | Timer2 external clock input.<br>Timer3 external clock input.                                                                                                                                                                                                                                                                                                                                                      |  |  |

| T2CK<br>T3CK<br>T4CK                                                                                                                            |                                                                            | ST<br>ST<br>ST                                                   | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                                                                                                                                                                                                                      |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK                                                                                                                    |                                                                            | ST<br>ST<br>ST<br>ST                                             | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.                                                                                                                                                                                                                                                                                      |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK                                                                                                            |                                                                            | ST<br>ST<br>ST<br>ST<br>ST                                       | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.                                                                                                                                                                                                                                                      |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK                                                                                                    |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST                                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.                                                                                                                                                                                                                      |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK                                                                                            |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST                                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.                                                                                                                                                                                      |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK                                                                                    |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                           | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.                                                                                                                                                      |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br><u>U1CTS</u>                                                                    |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST                                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.                                                                                                                              |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br><u>U1CTS</u><br>U1RTS                                                           |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.                                                                                                                                                      |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX                                                 | <br> <br> <br> <br> <br> <br> <br> <br> <br>                               | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                           | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.                                                                                                      |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX                                         | <br> <br> <br> <br> <br> <br> <br> <br> <br>                               | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.                                                                                    |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS                                | <br>                     | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br>       | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.<br>UART1 transmit.                                                                 |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX                        | <br>                     | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br>       | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 receive.       |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX                        |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br> | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.                               |  |  |

| T2CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX<br>U2TX<br>VDD | <br> | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br> | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 receive. |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RX<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX<br>U2TX                 |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br> | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 receive.<br>UART2 transmit.            |  |  |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

NOTES:

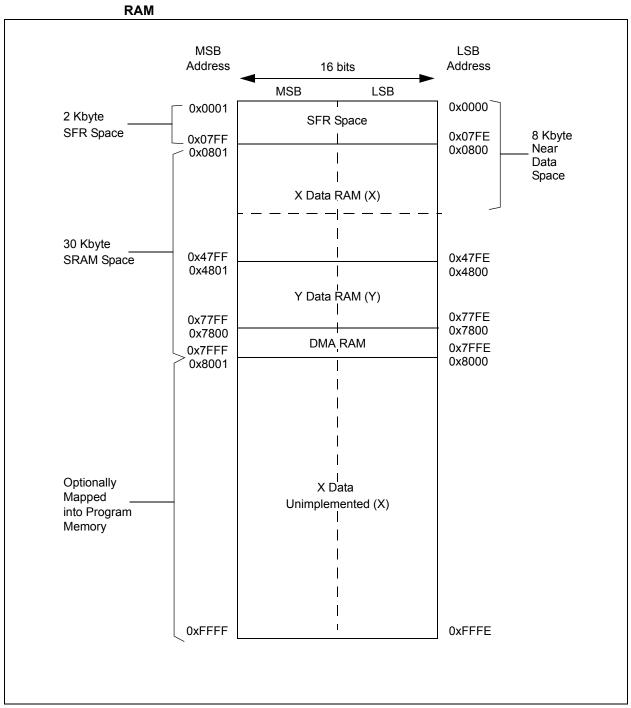

#### FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJXXXMCX06/X08/X10 DEVICES WITH 30 KB

| Addressing Mode                        | Description                                                                                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                   | The address of the file register is specified explicitly.                                              |

| Register Direct                        | The contents of a register are accessed directly.                                                      |

| Register Indirect                      | The contents of Wn forms the EA.                                                                       |

| Register Indirect Post-Modified        | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified         | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset  | The sum of Wn and a literal forms the EA.                                                              |

### TABLE 4-36: FUNDAMENTAL ADDRESSING MODES SUPPORTED

#### 4.3.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the Addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the Addressing     |

|-------|----------------------------------------------|

|       | mode specified in the instruction can differ |

|       | for the source and destination EA.           |

|       | However, the 4-bit Wb (Register Offset)      |

|       | field is shared between both source and      |

|       | destination (but typically only used by      |

|       | one).                                        |

In summary, the following Addressing modes are supported by move and accumulator instructions:

- Register Direct

- · Register Indirect

- Register Indirect Post-modified

- · Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

| Note: | Not    | all   | instructions  | support     | all   | the   |

|-------|--------|-------|---------------|-------------|-------|-------|

|       | Addr   | essii | ng modes give | n above. I  | ndivi | idual |

|       | instru | uctio | ns may suppo  | rt differen | t sub | sets  |

|       | of the | ese / | Addressing mo | odes.       |       |       |

### 4.3.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of addressing modes to allow the user to effectively manipulate the data pointers through register indirect tables.

The 2-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU and W10 and W11 will always be directed to the Y AGU. The effective addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

| Note: | Register   | Indirect  | with    | Register  | Offset |

|-------|------------|-----------|---------|-----------|--------|

|       | Addressir  | ng mode i | s only  | available | for W9 |

|       | (in X spac | ce) and W | /11 (in | Y space). |        |

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- · Register Indirect with Register Offset (Indexed)

### 4.3.5 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

## 4.4 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing

| U-0          | R/W-1                                                                         | R/W-0                                   | R/W-0         | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|--------------|-------------------------------------------------------------------------------|-----------------------------------------|---------------|------------------|-----------------|-----------------|-------|--|--|--|--|

|              |                                                                               | T1IP<2:0>                               |               |                  |                 | OC1IP<2:0>      |       |  |  |  |  |

| bit 15       |                                                                               |                                         |               |                  |                 |                 | bit   |  |  |  |  |

| U-0          | R/W-1                                                                         | R/W-0                                   | R/W-0         | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|              |                                                                               | IC1IP<2:0>                              |               | _                |                 | INT0IP<2:0>     |       |  |  |  |  |

| bit 7        |                                                                               |                                         |               |                  | 1               |                 | bit   |  |  |  |  |

| Legend:      |                                                                               |                                         |               |                  |                 |                 |       |  |  |  |  |

| R = Readab   | le bit                                                                        | W = Writable I                          | oit           | U = Unimple      | mented bit, rea | ad as '0'       |       |  |  |  |  |

| -n = Value a | t POR                                                                         | '1' = Bit is set                        |               | '0' = Bit is cle | eared           | x = Bit is unkn | own   |  |  |  |  |

| bit 15       | Unimpleme                                                                     | nted: Read as 'o                        | )'            |                  |                 |                 |       |  |  |  |  |

| bit 14-12    | T1IP<2:0>:                                                                    | Timer1 Interrupt                        | Priority bits |                  |                 |                 |       |  |  |  |  |

|              | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>         |                                         |               |                  |                 |                 |       |  |  |  |  |

|              | •                                                                             | •                                       |               |                  |                 |                 |       |  |  |  |  |

|              | •                                                                             |                                         |               |                  |                 |                 |       |  |  |  |  |

|              |                                                                               | upt is priority 1<br>upt source is disa | abled         |                  |                 |                 |       |  |  |  |  |

| bit 11       |                                                                               | nted: Read as '0                        |               |                  |                 |                 |       |  |  |  |  |

| bit 10-8     | <b>OC1IP&lt;2:0&gt;:</b> Output Compare Channel 1 Interrupt Priority bits     |                                         |               |                  |                 |                 |       |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)                    |                                         |               |                  |                 |                 |       |  |  |  |  |

|              | •                                                                             |                                         |               |                  |                 |                 |       |  |  |  |  |

|              |                                                                               |                                         |               |                  |                 |                 |       |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                                            |                                         |               |                  |                 |                 |       |  |  |  |  |

|              | 000 <b>= Interr</b>                                                           | upt source is disa                      | abled         |                  |                 |                 |       |  |  |  |  |

| bit 7        | Unimpleme                                                                     | nted: Read as 'o                        | )'            |                  |                 |                 |       |  |  |  |  |

| bit 6-4      | IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits                   |                                         |               |                  |                 |                 |       |  |  |  |  |

|              | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>         |                                         |               |                  |                 |                 |       |  |  |  |  |

|              | •                                                                             |                                         |               |                  |                 |                 |       |  |  |  |  |

|              | •                                                                             |                                         |               |                  |                 |                 |       |  |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled           |                                         |               |                  |                 |                 |       |  |  |  |  |

| bit 3        |                                                                               | -                                       |               |                  |                 |                 |       |  |  |  |  |

| bit 3-0      | Unimplemented: Read as '0'<br>INT0IP<2:0>: External Interrupt 0 Priority bits |                                         |               |                  |                 |                 |       |  |  |  |  |

| DIL 2-0      |                                                                               | upt is priority 7 (h                    |               |                  |                 |                 |       |  |  |  |  |

|              | •                                                                             | optio pilotity i (i                     | g. eet p. et  | (j               |                 |                 |       |  |  |  |  |

|              | •                                                                             |                                         |               |                  |                 |                 |       |  |  |  |  |

|              | •                                                                             |                                         |               |                  |                 |                 |       |  |  |  |  |

|              | 001 = Interr                                                                  | upt is priority 1                       |               |                  |                 |                 |       |  |  |  |  |

## REGISTER 7-15: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

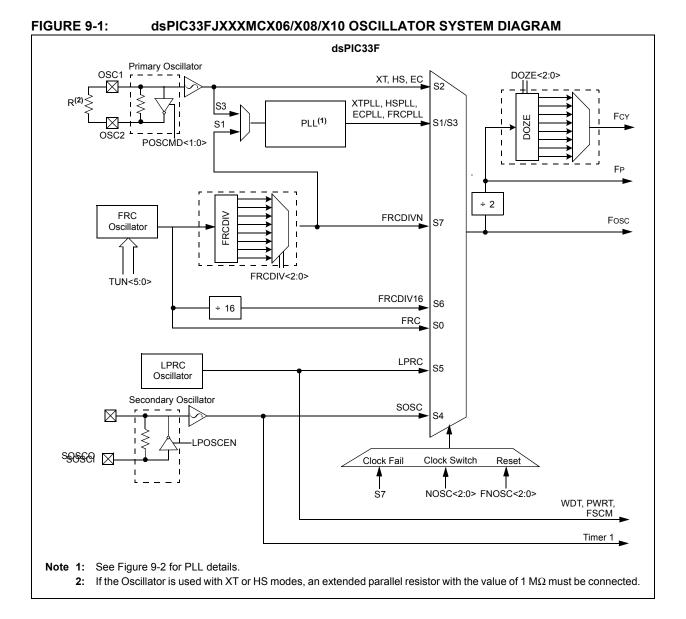

## 9.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJXXXMCX06/X08/X10 oscillator system provides the following:

Various external and internal oscillator options as clock sources

- An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- The internal FRC oscillator can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- A Clock Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

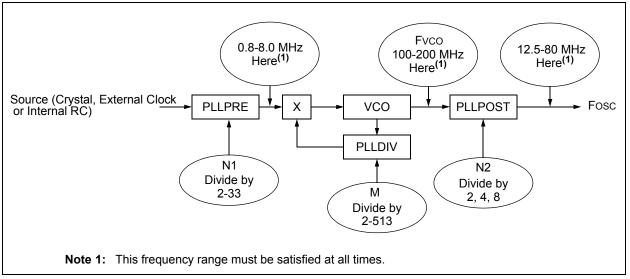

**XT WITH PLL MODE**

= 40 MIPS

**EXAMPLE**

$FCY = \frac{FOSC}{2} = \frac{1}{2} \left( \frac{10000000 \cdot 32}{2 \cdot 2} \right)$

**EQUATION 9-3:**

For example, suppose a 10 MHz crystal is being used with "XT with PLL" as the selected oscillator mode. If PLLPRE<4:0> = 0, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz. If PLLDIV<8:0> = 0x1E, then M = 32. This yields a VCO output of 5 \* 32 = 160 MHz, which is within the 100-200 MHz ranged needed.

If PLLPOST<1:0> = 0, then N2 = 2. This provides a Fosc of 160/2 = 80 MHz. The resultant device operating speed is 80/2 = 40 MIPS.

### FIGURE 9-2: dsPIC33FJXXXMCX06/X08/X10 PLL BLOCK DIAGRAM

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                  | <b>Oscillator Source</b> | POSCMD<1:0> | FNOSC<2:0> | Note |

|--------------------------------------------------|--------------------------|-------------|------------|------|

| Fast RC Oscillator with Divide-by-N<br>(FRCDIVN) | Internal                 | xx          | 111        | 1, 2 |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)  | Internal                 | xx          | 110        | 1    |

| Low-Power RC Oscillator (LPRC)                   | Internal                 | xx          | 101        | 1    |

| Secondary (Timer1) Oscillator (SOSC)             | Secondary                | xx          | 100        | 1    |

| Primary Oscillator (HS) with PLL<br>(HSPLL)      | Primary                  | 10          | 011        | -    |

| Primary Oscillator (XT) with PLL<br>(XTPLL)      | Primary                  | 01          | 011        | -    |

| Primary Oscillator (EC) with PLL<br>(ECPLL)      | Primary                  | 00          | 011        | 1    |

| Primary Oscillator (HS)                          | Primary                  | 10          | 010        | _    |

| Primary Oscillator (XT)                          | Primary                  | 01          | 010        | _    |

| Primary Oscillator (EC)                          | Primary                  | 00          | 010        | 1    |

| Fast RC Oscillator with PLL (FRCPLL)             | Internal                 | xx          | 001        | 1    |

| Fast RC Oscillator (FRC)                         | Internal                 | xx          | 000        | 1    |

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

### REGISTER 16-1: PXTCON: PWM TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| PTEN   | —   | PTSIDL | —   | —   | —   | —   | —     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0    | R/W-0   | R/W-0 | R/W-0  |

|-------|-------|---------|-------|----------|---------|-------|--------|

|       | PTOPS | \$<3:0> |       | PTCK     | PS<1:0> | PTMO  | D<1:0> |

| bit 7 |       |         |       | <u>.</u> |         |       | bit 0  |

| Legend:                     |                   |                                                                  |                               |                               |  |  |  |  |

|-----------------------------|-------------------|------------------------------------------------------------------|-------------------------------|-------------------------------|--|--|--|--|

| R = Readable bit W = Writal |                   | W = Writable bit U = Unimplemented bit, read                     |                               | read as '0'                   |  |  |  |  |

| -n = Value at               | POR               | '1' = Bit is set                                                 | '0' = Bit is cleared          | x = Bit is unknown            |  |  |  |  |

|                             |                   |                                                                  |                               |                               |  |  |  |  |

| bit 15                      |                   | WM Time Base Timer Enable                                        | e bit                         |                               |  |  |  |  |

|                             |                   | time base is on time base is off                                 |                               |                               |  |  |  |  |

| bit 14                      | Unimpler          | mented: Read as '0'                                              |                               |                               |  |  |  |  |

| bit 13                      | PTSIDL:           | PWM Time Base Stop in Idle                                       | e Mode bit                    |                               |  |  |  |  |

|                             |                   | time base halts in CPU Idle time base runs in CPU Idle           |                               |                               |  |  |  |  |

| bit 12-8                    | Unimpler          | mented: Read as '0'                                              |                               |                               |  |  |  |  |

| bit 7-4                     | PTOPS<3           | PTOPS<3:0>: PWM Time Base Output Postscale Select bits           |                               |                               |  |  |  |  |

|                             | 1111 <b>= 1</b> : | :16 postscale                                                    |                               |                               |  |  |  |  |

|                             | •                 |                                                                  |                               |                               |  |  |  |  |

|                             | •                 |                                                                  |                               |                               |  |  |  |  |

|                             | •                 |                                                                  |                               |                               |  |  |  |  |

|                             |                   | 2 postscale<br>1 postscale                                       |                               |                               |  |  |  |  |

| bit 3-2                     | PTCKPS            | <1:0>: PWM Time Base Inpu                                        | ut Clock Prescale Select bits |                               |  |  |  |  |

|                             | 11 = PWN          | M time base input clock perio                                    | od is 64 Tcy (1:64 prescale)  |                               |  |  |  |  |

|                             |                   | I time base input clock perio                                    |                               |                               |  |  |  |  |

|                             |                   | M time base input clock period<br>M time base input clock period |                               |                               |  |  |  |  |

| bit 1-0                     |                   | 1:0>: PWM Time Base Mode                                         |                               |                               |  |  |  |  |

|                             | 11 <b>= PW</b>    |                                                                  | ontinuous Up/Down Count mo    | de with interrupts for double |  |  |  |  |

|                             |                   |                                                                  | ontinuous Up/Down Count mo    | de                            |  |  |  |  |

|                             |                   | I time base operates in Sing                                     | -                             |                               |  |  |  |  |

|                             | 00 <b>= PW</b>    | I time base operates in a Fr                                     | ee-Running mode               |                               |  |  |  |  |

#### 18.0 SERIAL PERIPHERAL **INTERFACE (SPI)**

This data sheet summarizes the features Note: of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) in the "dsPIC33F Family Reference Manual", which is available the from Microchip web site (www.microchip.com)

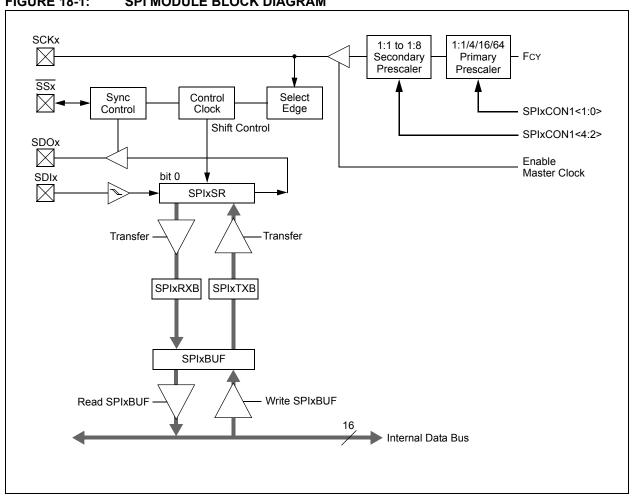

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, ADC, etc. The SPI module is compatible with SPI and SIOP from Motorola®.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 or SPI2 module.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates various status conditions.

The serial interface consists of 4 pins: SDIx (serial data input), SDOx (serial data output), SCKx (shift clock input or output) and SSx (active-low slave select).

In Master mode operation, SCK is a clock output, but in Slave mode, it is a clock input.

SPI MODULE BLOCK DIAGRAM **FIGURE 18-1:**

## 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "UART" (DS70188) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

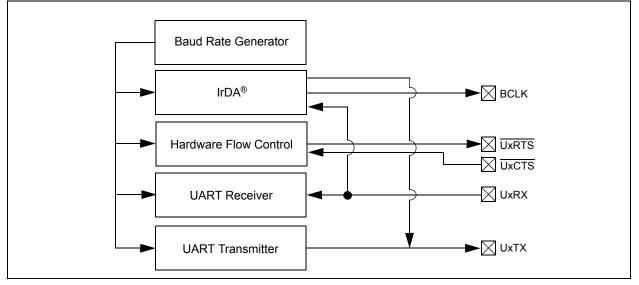

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33FJXXXMCX06/X08/X10 device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-bit or 9-bit Data Transmission through the UxTX and UxRX pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator with 16-bit Prescaler

- Baud rates ranging from 1 Mbps to 15 bps at 16x mode at 40 MIPS

- Baud rates ranging from 4 Mbps to 61 bps at 4x mode at 40 MIPS

- 4-deep First-In-First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- Transmit and Receive Interrupts

- A Separate Interrupt for all UART Error Conditions

- · Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection