Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc710-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F Family Reference Manual", which is available from the Microchip website (www.microchip.com).

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJXXXMCX06/X08/X10 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

- VCAP/VDDCORE (see Section 2.3 "Capacitor on Internal Voltage Regulator (VCAP/VDDCORE)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

| Note: | The   | AVdd    | and   | AVss   | pins | mus | st be |

|-------|-------|---------|-------|--------|------|-----|-------|

|       | conn  | ected   | indep | endent | of   | the | ADC   |

|       | volta | ge refe |       |        |      |     |       |

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz <  $F_{IN}$  < 8 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

## 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 2, ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in this register that correspond to the A/D pins that are initialized by MPLAB ICD 2, ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 2, ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor to Vss on unused pins and drive the output to logic low.

#### TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXMCX10 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2       | 0062        | _       | -       | _       | _       | _       | _       | _      | _      | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2       | 006A        | —       | _       | _       | _       | _       | _       | _      | -      | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXMCX08 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|---------|---------|---------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE         | 0000          |

| CNEN2       | 0062        | —       | _       | _       | _       | _       | —       |        | _      | _      |        | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | —       | _       | _       | _       | _       | _       | _      | _      | _      | -      | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-4: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXMCX06 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|--------|---------|---------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE  | CN2IE   | CN1IE   | CN0IE         | 0000          |

| CNEN2       | 0062        | _       | _       | _       | _       | _       | _       | _      | _      | _      | _      | CN21IE  | CN20IE  | -      | CN18IE  | CN17IE  | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | CN3PUE | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | —       | _       | _       | _       | _       | _       | _      | _      | _      | _      | CN21PUE | CN20PUE | _      | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJXXXMCX06/X08/X10 devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- 2. Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJXXXMCX06/X08/X10 device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (Vss) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data by blocks (or 'rows') of 64 instructions (192 bytes) at a time or by single program memory word; and the user can erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

## 5.1 Table Instructions and Flash Programming

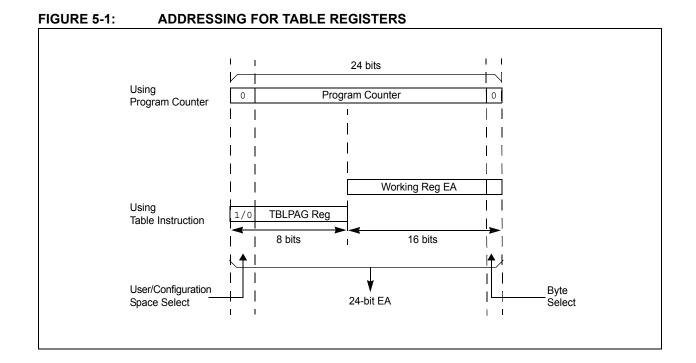

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits <7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and TBLWTL instructions are used to read or write to bits <15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits <23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

| U-0           | R/W-0                             | R/W-0                           | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |

|---------------|-----------------------------------|---------------------------------|----------------|------------------|------------------|-----------------|--------|--|--|

|               | DMA1IE                            | AD1IE                           | U1TXIE         | U1RXIE           | SPI1IE           | SPI1EIE         | T3IE   |  |  |

| bit 15        |                                   | ·                               |                |                  | •                | ÷               | bit 8  |  |  |

| R/W-0         | R/W-0                             | R/W-0                           | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |

| T2IE          | OC2IE                             | IC2IE                           | DMA0IE         | T1IE             | OC1IE            | IC1IE           | INTOIE |  |  |

| bit 7         | UC2IE                             | ICZIE                           | DIVIAULE       |                  | OCTIE            | ICTIE           | bit 0  |  |  |

| Legend:       |                                   |                                 |                |                  |                  |                 |        |  |  |

| R = Readable  | e bit                             | W = Writable                    | bit            | U = Unimpler     | mented bit, read | d as '0'        |        |  |  |

| -n = Value at |                                   | '1' = Bit is set                |                | '0' = Bit is cle |                  | x = Bit is unkr | iown   |  |  |

| iii valao at  |                                   | 1 Bitle co                      | •              | o Dicio dia      |                  |                 |        |  |  |

| bit 15        | Unimplemen                        | ted: Read as '                  | 0'             |                  |                  |                 |        |  |  |

| bit 14        | DMA1IE: DM                        | A Channel 1 D                   | ata Transfer C | Complete Interi  | rupt Enable bit  |                 |        |  |  |

|               |                                   | equest enable                   |                |                  |                  |                 |        |  |  |

|               |                                   | equest not en                   |                |                  |                  |                 |        |  |  |

| bit 13        |                                   |                                 |                | rupt Enable bit  |                  |                 |        |  |  |

|               |                                   | equest enable<br>equest not ena |                |                  |                  |                 |        |  |  |

| bit 12        | •                                 | RT1 Transmitte                  |                | able bit         |                  |                 |        |  |  |

|               |                                   | equest enable                   | •              |                  |                  |                 |        |  |  |

|               | 0 = Interrupt request not enabled |                                 |                |                  |                  |                 |        |  |  |

| bit 11        |                                   | RT1 Receiver I                  | •              | le bit           |                  |                 |        |  |  |

|               |                                   | equest enable<br>equest not ena |                |                  |                  |                 |        |  |  |

| bit 10        | -                                 | Event Interrup                  |                |                  |                  |                 |        |  |  |

|               |                                   | equest enable                   |                |                  |                  |                 |        |  |  |

|               |                                   | equest not en                   |                |                  |                  |                 |        |  |  |

| bit 9         | SPI1EIE: SPI                      | 1 Error Interru                 | pt Enable bit  |                  |                  |                 |        |  |  |

|               |                                   | equest enable                   |                |                  |                  |                 |        |  |  |

|               | •                                 | equest not en                   |                |                  |                  |                 |        |  |  |

| bit 8         |                                   | Interrupt Enab                  |                |                  |                  |                 |        |  |  |

|               |                                   | equest enable<br>equest not ena |                |                  |                  |                 |        |  |  |

| bit 7         | -                                 | Interrupt Enab                  |                |                  |                  |                 |        |  |  |

|               |                                   | equest enable                   |                |                  |                  |                 |        |  |  |

|               | 0 = Interrupt r                   | equest not en                   | abled          |                  |                  |                 |        |  |  |

| bit 6         | •                                 | ut Compare Ch                   |                | upt Enable bit   |                  |                 |        |  |  |

|               |                                   | equest enable                   |                |                  |                  |                 |        |  |  |

| bit 5         | •                                 | equest not en<br>Capture Chann  |                | Enabla bit       |                  |                 |        |  |  |

| DIL 5         | •                                 | equest enable                   | •              |                  |                  |                 |        |  |  |

|               |                                   | request not en                  |                |                  |                  |                 |        |  |  |

| bit 4         | DMA0IE: DM                        | A Channel 0 D                   | ata Transfer C | Complete Interi  | rupt Enable bit  |                 |        |  |  |

|               |                                   | equest enable                   |                |                  |                  |                 |        |  |  |

|               |                                   | equest not en                   |                |                  |                  |                 |        |  |  |

| bit 3         |                                   | Interrupt Enab                  |                |                  |                  |                 |        |  |  |

|               |                                   | equest enable<br>equest not en  |                |                  |                  |                 |        |  |  |

|               |                                   |                                 |                |                  |                  |                 |        |  |  |

## REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | U-0 | R/W-0 | R/W-0 | R/W-0  |

|--------|--------|--------|--------|-----|-------|-------|--------|

| C2TXIE | C1TXIE | DMA7IE | DMA6IE | _   | U2EIE | U1EIE | FLTBIE |

| bit 7  |        |        |        |     |       |       | bit 0  |

| Legend:                                                                     |                                                                   |                                          |                              |                    |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------|------------------------------|--------------------|--|--|--|--|--|--|--|

| R = Readat                                                                  | ole bit                                                           | W = Writable bit                         | U = Unimplemented bit,       | read as '0'        |  |  |  |  |  |  |  |

| -n = Value a                                                                | at POR                                                            | '1' = Bit is set                         | '0' = Bit is cleared         | x = Bit is unknown |  |  |  |  |  |  |  |

|                                                                             |                                                                   |                                          |                              |                    |  |  |  |  |  |  |  |

| bit 15-8                                                                    | Unimple                                                           | mented: Read as '0'                      |                              |                    |  |  |  |  |  |  |  |

| bit 7                                                                       | C2TXIE:                                                           | ECAN2 Transmit Data Requ                 | est Interrupt Enable bit     |                    |  |  |  |  |  |  |  |

|                                                                             |                                                                   | Interrupt request enabled                |                              |                    |  |  |  |  |  |  |  |

| 0 = Interrupt request not enabled                                           |                                                                   |                                          |                              |                    |  |  |  |  |  |  |  |

| bit 6                                                                       | 6 <b>C1TXIE:</b> ECAN1 Transmit Data Request Interrupt Enable bit |                                          |                              |                    |  |  |  |  |  |  |  |

|                                                                             |                                                                   | rupt request enabled                     |                              |                    |  |  |  |  |  |  |  |

| 0 = Interrupt request not enabled                                           |                                                                   |                                          |                              |                    |  |  |  |  |  |  |  |

| bit 5 <b>DMA7IE:</b> DMA Channel 7 Data Transfer Complete Enable Status bit |                                                                   |                                          |                              |                    |  |  |  |  |  |  |  |

|                                                                             |                                                                   | rupt request enabled                     |                              |                    |  |  |  |  |  |  |  |

|                                                                             |                                                                   | rupt request not enabled                 |                              |                    |  |  |  |  |  |  |  |

| bit 4                                                                       |                                                                   |                                          | fer Complete Enable Status b | it                 |  |  |  |  |  |  |  |

|                                                                             |                                                                   | rupt request enabled                     |                              |                    |  |  |  |  |  |  |  |

|                                                                             |                                                                   | rupt request not enabled                 |                              |                    |  |  |  |  |  |  |  |

| bit 3                                                                       | -                                                                 | mented: Read as '0'                      |                              |                    |  |  |  |  |  |  |  |

| bit 2                                                                       |                                                                   | JART2 Error Interrupt Enable             | e bit                        |                    |  |  |  |  |  |  |  |

|                                                                             |                                                                   | rupt request enabled                     |                              |                    |  |  |  |  |  |  |  |

|                                                                             |                                                                   | rupt request not enabled                 |                              |                    |  |  |  |  |  |  |  |

| bit 1 U1EIE: UART1 Error Interrupt Enable bit                               |                                                                   |                                          |                              |                    |  |  |  |  |  |  |  |

|                                                                             |                                                                   | rupt request enabled                     |                              |                    |  |  |  |  |  |  |  |

|                                                                             |                                                                   | rupt request not enabled                 |                              |                    |  |  |  |  |  |  |  |

| bit 0                                                                       |                                                                   | FLTBIE: PWM Fault B Interrupt Enable bit |                              |                    |  |  |  |  |  |  |  |

|                                                                             |                                                                   | rupt request enabled                     |                              |                    |  |  |  |  |  |  |  |

|                                                                             | 0 = inter                                                         | rupt request not enabled                 |                              |                    |  |  |  |  |  |  |  |

|                                                                             |                                                                   |                                          |                              |                    |  |  |  |  |  |  |  |

## REGISTER 7-32: IPC17: INTERRUPT PRIORITY CONTROL REGISTER 17

| U-0                     | R/W-1                                                            | R/W-0                                  | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |

|-------------------------|------------------------------------------------------------------|----------------------------------------|-----------------|------------------|-----------------|-----------------|---------|--|--|--|--|

| —                       |                                                                  | C2TXIP<2:0>                            |                 | —                |                 | C1TXIP<2:0>     |         |  |  |  |  |

| bit 15                  |                                                                  |                                        |                 |                  |                 |                 | bit 8   |  |  |  |  |

| U-0                     | R/W-1                                                            | R/W-0                                  | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |

|                         | 10/00-1                                                          | DMA7IP<2:0>                            | 11/00-0         |                  | 10/00-1         | DMA6IP<2:0>     | 10,00-0 |  |  |  |  |

| bit 7                   |                                                                  |                                        |                 |                  |                 |                 | bit     |  |  |  |  |

|                         |                                                                  |                                        |                 |                  |                 |                 |         |  |  |  |  |

| Legend:<br>R = Readable | , hit                                                            | W = Writable                           | hit             | LI – Unimplo     | montod hit ro   | od oo '0'       |         |  |  |  |  |

| n = Value at            |                                                                  | '1' = Bit is set                       |                 | '0' = Bit is cle | mented bit, re  | x = Bit is unkn | 0,4/0   |  |  |  |  |

|                         | FUK                                                              | I – Dit is set                         |                 |                  | aleu            |                 | OWIT    |  |  |  |  |

| bit 15                  | Unimpleme                                                        | nted: Read as 'o                       | כ'              |                  |                 |                 |         |  |  |  |  |

| bit 14-12               | C2TXIP<2:0>: ECAN2 Transmit Data Request Interrupt Priority bits |                                        |                 |                  |                 |                 |         |  |  |  |  |

|                         | 111 = Interr                                                     | upt is priority 7 (I                   | nighest priorit | ty interrupt)    |                 |                 |         |  |  |  |  |

|                         | •                                                                |                                        |                 |                  |                 |                 |         |  |  |  |  |

|                         | •                                                                |                                        |                 |                  |                 |                 |         |  |  |  |  |

|                         |                                                                  | upt is priority 1                      |                 |                  |                 |                 |         |  |  |  |  |

|                         | 000 = Interr                                                     | 000 = Interrupt source is disabled     |                 |                  |                 |                 |         |  |  |  |  |

| bit 11                  | Unimpleme                                                        | Unimplemented: Read as '0'             |                 |                  |                 |                 |         |  |  |  |  |

| bit 10-8                |                                                                  | >: ECAN1 Trans                         |                 |                  | Priority bits   |                 |         |  |  |  |  |

|                         | 111 = Interr                                                     | upt is priority 7 (I                   | nighest priorit | ty interrupt)    |                 |                 |         |  |  |  |  |

|                         | •                                                                |                                        |                 |                  |                 |                 |         |  |  |  |  |

|                         | •                                                                |                                        |                 |                  |                 |                 |         |  |  |  |  |

|                         |                                                                  | upt is priority 1<br>upt source is dis | abled           |                  |                 |                 |         |  |  |  |  |

| bit 7                   |                                                                  | nted: Read as '                        |                 |                  |                 |                 |         |  |  |  |  |

| bit 6-4                 | -                                                                | 0>: DMA Channe                         |                 | nsfer Complete   | Interrunt Prid  | ority hits      |         |  |  |  |  |

|                         |                                                                  | upt is priority 7 (I                   |                 | •                | monupting       | Shiry Sho       |         |  |  |  |  |

|                         | •                                                                |                                        |                 | ·) ······        |                 |                 |         |  |  |  |  |

|                         | •                                                                |                                        |                 |                  |                 |                 |         |  |  |  |  |

|                         | •<br>001 - Intorr                                                | unt is priority 1                      |                 |                  |                 |                 |         |  |  |  |  |

|                         |                                                                  | upt is priority 1<br>upt source is dis | abled           |                  |                 |                 |         |  |  |  |  |

| bit 3                   |                                                                  | nted: Read as '                        |                 |                  |                 |                 |         |  |  |  |  |

| bit 2-0                 | -                                                                | 0>: DMA Channe                         |                 | nsfer Complete   | Interrupt Price | pritv bits      |         |  |  |  |  |

|                         |                                                                  | upt is priority 7 (I                   |                 | -                |                 |                 |         |  |  |  |  |

|                         | •                                                                |                                        | 5 1             | - 1/             |                 |                 |         |  |  |  |  |

|                         | •                                                                |                                        |                 |                  |                 |                 |         |  |  |  |  |

|                         | •                                                                |                                        |                 |                  |                 |                 |         |  |  |  |  |

|                         | 001 - Interr                                                     | upt is priority 1                      |                 |                  |                 |                 |         |  |  |  |  |

## 7.4 Interrupt Setup Procedures

## 7.4.1 INITIALIZATION

To configure an interrupt source, do the following:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

Note: At a device Reset, the IPCx registers are initialized such that all user interrupt sources are assigned to priority level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

## 7.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address will depend on the programming language (i.e., C or assembler) and the language development tool suite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

## 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (level 8-level 15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

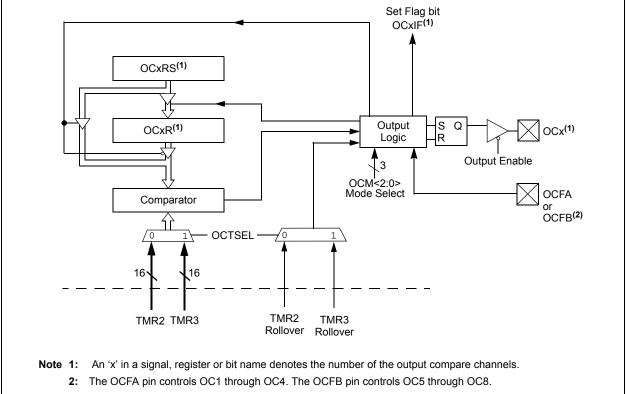

## 15.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F Family Reference Manual", Section 13. "Output Compare" (DS70209), which is available on the Microchip web site (www.microchip.com).

The output compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two Compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

The output compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without Fault Protection

- · PWM mode with Fault Protection

## REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

| bit 4-2 | <b>SPRE&lt;2:0&gt;:</b> Secondary Prescale bits (Master mode) <sup>(2)</sup><br>111 = Secondary prescale 1:1<br>110 = Secondary prescale 2:1 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                                            |

|         | •                                                                                                                                            |

|         | •                                                                                                                                            |

|         | 000 = Secondary prescale 8:1                                                                                                                 |

| bit 1-0 | <b>PPRE&lt;1:0&gt;:</b> Primary Prescale bits (Master mode) <sup>(2)</sup>                                                                   |

|         | 11 = Primary prescale 1:1                                                                                                                    |

|         | 10 = Primary prescale 4:1                                                                                                                    |

|         | 01 = Primary prescale 16:1                                                                                                                   |

|         |                                                                                                                                              |

- 00 = Primary prescale 64:1

- **Note 1:** The CKE bit is not used in the Framed SPI modes. The user should program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: Do not set both the Primary and Secondary prescalers to a value of 1:1.

- **3:** This bit must be cleared when FRMEN = 1.

| R-0 HSC         | R-0 HSC                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                                                                                                            | U-0                        | U-0              | R/C-0 HS                                        | R-0 HSC                               | R-0 HSC         |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------|-------------------------------------------------|---------------------------------------|-----------------|--|--|

| ACKSTAT         | TRSTAT                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                              | _                          | _                | BCL                                             | GCSTAT                                | ADD10           |  |  |

| bit 15          |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                |                            |                  |                                                 |                                       | bit 8           |  |  |

|                 |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                |                            |                  |                                                 |                                       |                 |  |  |

| R/C-0 HS        | R/C-0 HS                                                                                                                                                                                                                     | R-0 HSC                                                                                                                                                                                                                                                                                                        | R/C-0 HSC                  | R/C-0 HSC        | R-0 HSC                                         | R-0 HSC                               | R-0 HSC         |  |  |

| IWCOL           | I2COV                                                                                                                                                                                                                        | D_A                                                                                                                                                                                                                                                                                                            | Р                          | S                | R_W                                             | RBF                                   | TBF             |  |  |

| bit 7           |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                |                            |                  |                                                 |                                       | bit 0           |  |  |

| Legend:         |                                                                                                                                                                                                                              | U = Unimpler                                                                                                                                                                                                                                                                                                   | nented bit rea             | ad as '0'        |                                                 |                                       |                 |  |  |

| R = Readable    | bit                                                                                                                                                                                                                          | W = Writable                                                                                                                                                                                                                                                                                                   |                            | HS = Set in h    | ardware                                         | HSC = Hardwa                          | are set/cleared |  |  |

| -n = Value at P | OR                                                                                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                                                               |                            | '0' = Bit is cle | ared                                            | x = Bit is unkr                       | iown            |  |  |

|                 |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                |                            |                  |                                                 |                                       |                 |  |  |

| bit 15          | ACKSTAT: Ac<br>(when operation<br>1 = NACK rec<br>0 = ACK recein<br>Hardware set                                                                                                                                             | ng as I <sup>2</sup> C mas<br>reived from sla<br>ived from slave                                                                                                                                                                                                                                               | ter, applicable<br>ve<br>e |                  | nsmit operation                                 | )                                     |                 |  |  |

| bit 14          | <b>TRSTAT:</b> Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                                                                                      |                                                                                                                                                                                                                                                                                                                |                            |                  |                                                 |                                       |                 |  |  |

|                 | <ul> <li>1 = Master transmit is in progress (8 bits + ACK)</li> <li>0 = Master transmit is not in progress</li> <li>Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.</li> </ul> |                                                                                                                                                                                                                                                                                                                |                            |                  |                                                 |                                       |                 |  |  |

| bit 13-11       | Unimplement                                                                                                                                                                                                                  | Jnimplemented: Read as '0'                                                                                                                                                                                                                                                                                     |                            |                  |                                                 |                                       |                 |  |  |

| bit 10          | BCL: Master                                                                                                                                                                                                                  | <b>3CL:</b> Master Bus Collision Detect bit                                                                                                                                                                                                                                                                    |                            |                  |                                                 |                                       |                 |  |  |

|                 | 1 = A bus coll<br>0 = No collisio<br>Hardware set                                                                                                                                                                            | on                                                                                                                                                                                                                                                                                                             |                            | ing a master o   | peration                                        |                                       |                 |  |  |

| bit 9           | GCSTAT: Ger                                                                                                                                                                                                                  | neral Call Statu                                                                                                                                                                                                                                                                                               | ıs bit                     |                  |                                                 |                                       |                 |  |  |

|                 | 0 = General c                                                                                                                                                                                                                | all address wa<br>all address wa<br>when address                                                                                                                                                                                                                                                               | s not received             |                  | ss. Hardware c                                  | lear at Stop det                      | ection.         |  |  |

| bit 8           | ADD10: 10-Bi                                                                                                                                                                                                                 | it Address Stat                                                                                                                                                                                                                                                                                                | us bit                     |                  |                                                 |                                       |                 |  |  |

|                 |                                                                                                                                                                                                                              | ress was not r                                                                                                                                                                                                                                                                                                 | natched                    | ched 10-bit ad   | dress. Hardwai                                  | re clear at Stop                      | detection.      |  |  |

| bit 7           | IWCOL: Write                                                                                                                                                                                                                 | Collision Dete                                                                                                                                                                                                                                                                                                 | ect bit                    |                  |                                                 |                                       |                 |  |  |

|                 | 0 = No collisio                                                                                                                                                                                                              | on                                                                                                                                                                                                                                                                                                             | -                          |                  | ause the I <sup>2</sup> C mo<br>usy (cleared by | -                                     |                 |  |  |

| bit 6           | I2COV: Recei                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                |                            |                  |                                                 |                                       |                 |  |  |

|                 | 1 = A byte wa<br>0 = No overflo                                                                                                                                                                                              | s received whi                                                                                                                                                                                                                                                                                                 | le the I2CxRC              | -                | till holding the j                              | -                                     |                 |  |  |

| bit 5           |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                |                            |                  | (,,,,                                           | · · · · · · · · · · · · · · · · · · · |                 |  |  |

|                 | 1 = Indicates 1<br>0 = Indicates 1                                                                                                                                                                                           | <ul> <li>D_A: Data/Address bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Indicates that the last byte received was data</li> <li>0 = Indicates that the last byte received was device address</li> <li>Hardware clear at device address match. Hardware set by reception of slave byte.</li> </ul> |                            |                  |                                                 |                                       |                 |  |  |

| bit 4           | P: Stop bit                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                |                            |                  |                                                 |                                       |                 |  |  |

|                 | P: Stop bit<br>1 = Indicates that a Stop bit has been detected last<br>0 = Stop bit was not detected last<br>Hardware set or clear when Start, Repeated Start or Stop detected.                                              |                                                                                                                                                                                                                                                                                                                |                            |                  |                                                 |                                       |                 |  |  |

## REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

## **REGISTER 21-9:** CiCFG1: ECAN<sup>™</sup> BAUD RATE CONFIGURATION REGISTER 1

| U-0           | U-0                               | U-0                                                                                    | U-0        | U-0                                | U-0    | U-0             | U-0                |  |

|---------------|-----------------------------------|----------------------------------------------------------------------------------------|------------|------------------------------------|--------|-----------------|--------------------|--|

| _             | —                                 | _                                                                                      | _          | _                                  | _      | _               | _                  |  |

| bit 15        |                                   |                                                                                        |            |                                    |        |                 | bit 8              |  |

|               |                                   |                                                                                        |            |                                    |        |                 |                    |  |

| R/W-0         | R/W-0                             | R/W-0                                                                                  | R/W-0      | R/W-0                              | R/W-0  | R/W-0           | R/W-0              |  |

| SJ\           | V<1:0>                            |                                                                                        |            | BRF                                | P<5:0> |                 |                    |  |

| bit 7         |                                   |                                                                                        |            |                                    |        |                 | bit 0              |  |

|               |                                   |                                                                                        |            |                                    |        |                 |                    |  |

| Legend:       |                                   |                                                                                        |            |                                    |        |                 |                    |  |

| R = Readabl   | R = Readable bit W = Writable bit |                                                                                        |            | U = Unimplemented bit, read as '0' |        |                 |                    |  |

| -n = Value at | = Value at POR '1' = Bit is set   |                                                                                        |            | '0' = Bit is cleared x =           |        | x = Bit is unkr | a = Bit is unknown |  |

|               |                                   |                                                                                        |            |                                    |        |                 |                    |  |

| bit 15-8      | Unimplemen                        | ted: Read as '                                                                         | 0'         |                                    |        |                 |                    |  |

| bit 7-6       | <b>SJW&lt;1:0&gt;:</b> S          | synchronization                                                                        | Jump Width | bits                               |        |                 |                    |  |

|               | 11 = Length i                     |                                                                                        |            |                                    |        |                 |                    |  |

|               | 10 = Length i<br>01 = Length i    |                                                                                        |            |                                    |        |                 |                    |  |

|               | 00 = Length is                    |                                                                                        |            |                                    |        |                 |                    |  |

| bit 5-0       | C C                               | Baud Rate Pres                                                                         | caler bits |                                    |        |                 |                    |  |

|               | 11 1111 <b>= T</b>                | Q = 2 x 64 x 1/                                                                        | FCAN       |                                    |        |                 |                    |  |

|               | •                                 |                                                                                        |            |                                    |        |                 |                    |  |

|               | •                                 |                                                                                        |            |                                    |        |                 |                    |  |

|               | •                                 |                                                                                        |            |                                    |        |                 |                    |  |

|               |                                   | $Q = 2 \times 3 \times 1/F_{0}$                                                        |            |                                    |        |                 |                    |  |

|               |                                   | 00 0001 = $TQ = 2 \times 2 \times 1/FCAN$<br>00 0000 = $TQ = 2 \times 1 \times 1/FCAN$ |            |                                    |        |                 |                    |  |

|               | 00 0000 = 1                       | $Q = 2 \times 1 \times 1/F$                                                            | CAN        |                                    |        |                 |                    |  |

|                                    | ,15)                           |                                    |                |                                    |       |                 | (     |  |  |

|------------------------------------|--------------------------------|------------------------------------|----------------|------------------------------------|-------|-----------------|-------|--|--|

| R/W-x                              | R/W-x                          | R/W-x                              | R/W-x          | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |  |

| SID10                              | SID9                           | SID8                               | SID7           | SID6                               | SID5  | SID4            | SID3  |  |  |

| bit 15                             |                                |                                    |                |                                    |       |                 | bit 8 |  |  |

| R/W-x                              | R/W-x                          | R/W-x                              | U-0            | R/W-x                              | U-0   | R/W-x           | R/W-x |  |  |

| SID2                               | SID1                           | SID0                               | —              | EXIDE                              | _     | EID17           | EID16 |  |  |

| bit 7                              |                                |                                    |                |                                    |       |                 | bit 0 |  |  |

| Legend:                            |                                |                                    |                |                                    |       |                 |       |  |  |

| R = Readable bit W = Writable bit  |                                |                                    |                | U = Unimplemented bit, read as '0' |       |                 |       |  |  |

| -n = Value at POR '1' = Bit is set |                                |                                    |                | '0' = Bit is cle                   | ared  | x = Bit is unkr | nown  |  |  |

|                                    |                                |                                    |                |                                    |       |                 |       |  |  |

| bit 15-5                           | SID<10:0>: S                   | Standard Identifi                  | er bits        |                                    |       |                 |       |  |  |

|                                    |                                | address bit SIE<br>address bit SIE |                |                                    |       |                 |       |  |  |

| bit 4                              | Unimplemen                     | ted: Read as 'd                    | )'             |                                    |       |                 |       |  |  |

| bit 3                              | EXIDE: Exte                    | nded Identifier                    | Enable bit     |                                    |       |                 |       |  |  |

|                                    | If MIDE = 1 th                 | hen:                               |                |                                    |       |                 |       |  |  |

|                                    |                                | ly messages wi                     |                |                                    |       |                 |       |  |  |

|                                    |                                | ly messages wi                     | th standard id | dentifier addres                   | ses   |                 |       |  |  |

|                                    | If MIDE = 0 th<br>Ignore EXIDE |                                    |                |                                    |       |                 |       |  |  |