Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

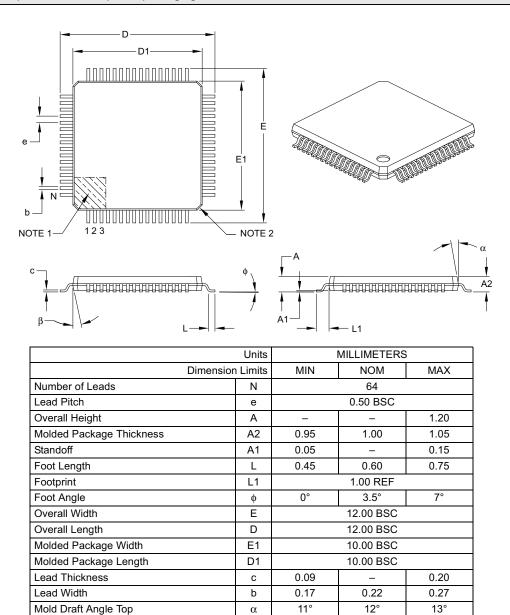

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256mc510-i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                                                                                 |                                                                            | T I/O DESO                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                                                                                        | Pin<br>Type                                                                | Buffer<br>Type                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

| RA0-RA7                                                                                                                                         | I/O                                                                        | ST                                                               | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |

| RA9-RA10                                                                                                                                        | I/O                                                                        | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RA12-RA15                                                                                                                                       | I/O                                                                        | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RB0-RB15                                                                                                                                        | I/O                                                                        | ST                                                               | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |

| RC1-RC4                                                                                                                                         | I/O                                                                        | ST                                                               | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |

| RC12-RC15                                                                                                                                       | I/O                                                                        | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RD0-RD15                                                                                                                                        | I/O                                                                        | ST                                                               | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |

| RE0-RE9                                                                                                                                         | I/O                                                                        | ST                                                               | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |

| RF0-RF8                                                                                                                                         | I/O                                                                        | ST                                                               | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |

| RF12-RF13                                                                                                                                       |                                                                            | _                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RG0-RG3                                                                                                                                         | I/O                                                                        | ST                                                               | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                |

| RG6-RG9                                                                                                                                         | I/O                                                                        | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RG12-RG15                                                                                                                                       | I/O                                                                        | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SCK1                                                                                                                                            | I/O                                                                        | ST                                                               | Synchronous serial clock input/output for SPI1.                                                                                                                                                                                                                                                                                                                                                                   |

| SDI1                                                                                                                                            | I                                                                          | ST                                                               | SPI1 data in.                                                                                                                                                                                                                                                                                                                                                                                                     |

| SDO1                                                                                                                                            | 0                                                                          | _                                                                | SPI1 data out.                                                                                                                                                                                                                                                                                                                                                                                                    |

| SS1                                                                                                                                             | I/O                                                                        | ST                                                               | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                    |

| SCK2                                                                                                                                            | I/O                                                                        | ST                                                               | Synchronous serial clock input/output for SPI2.                                                                                                                                                                                                                                                                                                                                                                   |

| SDI2                                                                                                                                            | I                                                                          | ST                                                               | SPI2 data in.                                                                                                                                                                                                                                                                                                                                                                                                     |

| SDO2                                                                                                                                            | 0                                                                          | -                                                                | SPI2 data out.                                                                                                                                                                                                                                                                                                                                                                                                    |

| SS2                                                                                                                                             | I/O                                                                        | ST                                                               | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                    |

| SCL1                                                                                                                                            | I/O                                                                        | ST                                                               | Synchronous serial clock input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                   |

| SDA1                                                                                                                                            | I/O                                                                        | ST                                                               | Synchronous serial data input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                    |

| SCL2                                                                                                                                            | I/O                                                                        | ST                                                               | Synchronous serial clock input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                   |

| SDA2                                                                                                                                            | I/O                                                                        | ST                                                               | Synchronous serial data input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                    |

| SOSCI                                                                                                                                           |                                                                            | ST/CMOS                                                          | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                                                                                                                                                                                                                                    |

| SOSCO                                                                                                                                           | 0                                                                          |                                                                  | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                                                                                                                                                                                                                                   |

| TMS                                                                                                                                             | I                                                                          | ST                                                               | JTAG Test mode select pin.                                                                                                                                                                                                                                                                                                                                                                                        |

| TCK                                                                                                                                             | I                                                                          | ST                                                               | JTAG test clock input pin.                                                                                                                                                                                                                                                                                                                                                                                        |

| TDI                                                                                                                                             |                                                                            | ST                                                               | JTAG test data input pin.                                                                                                                                                                                                                                                                                                                                                                                         |

| TDO                                                                                                                                             | 0                                                                          | —                                                                | JTAG test data output pin.                                                                                                                                                                                                                                                                                                                                                                                        |

| T1CK                                                                                                                                            |                                                                            |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                 | I                                                                          | ST                                                               | Timer1 external clock input.                                                                                                                                                                                                                                                                                                                                                                                      |

| T2CK                                                                                                                                            |                                                                            | ST                                                               | Timer2 external clock input.                                                                                                                                                                                                                                                                                                                                                                                      |

| T2CK<br>T3CK                                                                                                                                    |                                                                            | ST<br>ST                                                         | Timer2 external clock input.<br>Timer3 external clock input.                                                                                                                                                                                                                                                                                                                                                      |

| T2CK<br>T3CK<br>T4CK                                                                                                                            |                                                                            | ST<br>ST<br>ST                                                   | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                                                                                                                                                                                                                      |

| T2CK<br>T3CK<br>T4CK<br>T5CK                                                                                                                    |                                                                            | ST<br>ST<br>ST<br>ST                                             | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.                                                                                                                                                                                                                                                                                      |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK                                                                                                            |                                                                            | ST<br>ST<br>ST<br>ST<br>ST                                       | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.                                                                                                                                                                                                                                                      |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK                                                                                                    |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST                                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.                                                                                                                                                                                                                      |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK                                                                                            |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST                                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.                                                                                                                                                                                      |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK                                                                                    |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                           | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.                                                                                                                                                      |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br><u>U1CTS</u>                                                                    |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST                                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.                                                                                                                              |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br><u>U1CTS</u><br>U1RTS                                                           |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.                                                                                                                                                      |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX                                                 | <br> <br> <br> <br> <br> <br> <br> <br> <br>                               | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                           | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.                                                                                                      |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX                                         | <br> <br> <br> <br> <br> <br> <br> <br> <br>                               | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.                                                                                    |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS                                | <br>                     | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br>       | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.<br>UART1 transmit.                                                                 |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX                        | <br>                     | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br>       | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 receive.       |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX                        |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br> | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.                               |

| T2CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX<br>U2TX<br>VDD | <br> | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br> | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 receive. |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RX<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX<br>U2TX                 |                                                                            | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br> | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 receive.<br>UART2 transmit.            |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 3. "Data Memory" (DS70202) and Section 4. "Program Memory" (DS70203) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJXXXMCX06/X08/X10 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

### 4.1 Program Address Space

The program address memory space of the dsPIC33FJXXXMCX06/X08/X10 devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.6 "Interfacing Program and Data Memory Spaces".

User access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space. Memory usage for the dsPIC33FJXXXMCX06/X08/X10 family of devices is shown in Figure 4-1.

|                            | dsPIC33FJ64MCXXX                                   | dsPIC33FJ128MCXXX                 | dsPIC33FJ256MCXXX      |                                  |

|----------------------------|----------------------------------------------------|-----------------------------------|------------------------|----------------------------------|

| Ā                          | GOTO Instruction                                   | GOTO Instruction                  |                        | )x000000<br>)x000002             |

|                            | Reset Address                                      | Reset Address                     | - Reset Address        | )x000002                         |

|                            | Interrupt Vector Table                             | Interrupt Vector Table            | Interrupt Vector Table | 0x0000FE                         |

|                            | Reserved                                           | Reserved                          | Reserved               | 0x000100                         |

|                            | Alternate Vector Table                             | Alternate Vector Table            | Alternate vector rable | 0x000104<br>0x0001FE             |

| pace                       | User Program<br>Flash Memory<br>(22K instructions) | User Program<br>Flash Memory      | User Program           | )x000200<br>)x00ABFE             |

| User Memory Space          |                                                    | (44K instructions)                | (88K instructions)     | 0x00AC00                         |

| ser Me                     |                                                    |                                   |                        | 0x0157FE<br>0x015800             |

| Ï                          | Unimplemented<br>(Read '0's)                       | Unimplemented                     |                        | 004555                           |

|                            |                                                    | (Read 'o's)                       |                        | 0x02ABFE<br>0x02AC00             |

|                            |                                                    |                                   | Unimplemented          |                                  |

|                            |                                                    |                                   | (Read '0's)            |                                  |

| •                          |                                                    |                                   | , ,                    | x7FFFFE                          |

|                            |                                                    |                                   |                        | 0x800000                         |

|                            | Reserved                                           | Reserved                          | Reserved               |                                  |

| Space                      | Device Configuration<br>Registers                  | Device Configuration<br>Registers |                        | )xF7FFFE<br>)xF80000<br>)xF80017 |

| emory (                    |                                                    |                                   |                        | )xF80017<br>)xF80010             |

| Configuration Memory Space | Reserved                                           | Reserved                          | Reserved               |                                  |

| Config                     | · · ·                                              |                                   |                        | )xFEFFFE<br>)xFF0000             |

| ₩                          | DEVID (2)                                          | DEVID (2)                         | D = V D (2)            | )xFFFFFE                         |

| Note:                      | Memory areas are not show                          |                                   |                        |                                  |

### FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33FJXXXMCX06/X08/X10 DEVICES

### 4.1.1 PROGRAM MEMORY ORGANIZATION

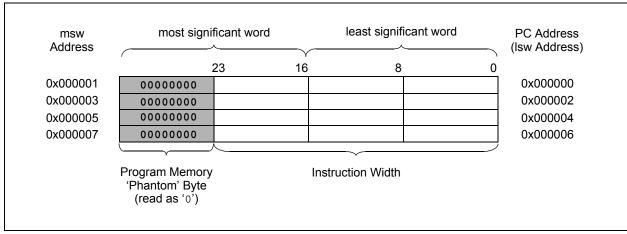

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

## 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJXXXMCX06/X08/X10 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJXXXMCX06/X08/X10 devices also have two interrupt vector tables located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table"**.

### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                           | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7         | Bit 6  | Bit 5     | Bit 4         | Bit 3        | Bit 2        | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|----------------------------------|--------|--------|--------|--------|---------|---------------|---------------|--------|-----------|---------------|--------------|--------------|---------|-------|---------------|

| WREG0    | 0000        |        |                                  |        |        |        |        | •       | Working Re    | gister 0      |        | •         |               |              | •            | •       | •     | 0000          |

| WREG1    | 0002        |        |                                  |        |        |        |        |         | Working Re    | gister 1      |        |           |               |              |              |         |       | 0000          |

| WREG2    | 0004        |        |                                  |        |        |        |        |         | Working Re    | gister 2      |        |           |               |              |              |         |       | 0000          |

| WREG3    | 0006        |        | Working Register 3 0             |        |        |        |        |         |               | 0000          |        |           |               |              |              |         |       |               |

| WREG4    | 8000        |        |                                  |        |        |        |        |         | Working Re    | gister 4      |        |           |               |              |              |         |       | 0000          |

| WREG5    | 000A        |        |                                  |        |        |        |        |         | Working Re    | gister 5      |        |           |               |              |              |         |       | 0000          |

| WREG6    | 000C        |        |                                  |        |        |        |        |         | Working Re    | gister 6      |        |           |               |              |              |         |       | 0000          |

| WREG7    | 000E        |        |                                  |        |        |        |        |         | Working Re    | gister 7      |        |           |               |              |              |         |       | 0000          |

| WREG8    | 0010        |        |                                  |        |        |        |        |         | Working Re    | gister 8      |        |           |               |              |              |         |       | 0000          |

| WREG9    | 0012        |        |                                  |        |        |        |        |         | Working Re    | gister 9      |        |           |               |              |              |         |       | 0000          |

| WREG10   | 0014        |        |                                  |        |        |        |        |         | Working Re    | gister 10     |        |           |               |              |              |         |       | 0000          |

| WREG11   | 0016        |        |                                  |        |        |        |        |         | Working Re    | gister 11     |        |           |               |              |              |         |       | 0000          |

| WREG12   | 0018        |        |                                  |        |        |        |        |         | Working Reg   | gister 12     |        |           |               |              |              |         |       | 0000          |

| WREG13   | 001A        |        |                                  |        |        |        |        |         | Working Reg   | gister 13     |        |           |               |              |              |         |       | 0000          |

| WREG14   | 001C        |        |                                  |        |        |        |        |         | 0000          |               |        |           |               |              |              |         |       |               |

| WREG15   | 001E        |        |                                  |        |        |        |        | 1       | Working Reg   | gister 15     |        |           |               |              |              |         |       | 0800          |

| SPLIM    | 0020        |        |                                  |        |        |        |        | Stac    | k Pointer Li  | mit Register  |        |           |               |              |              |         |       | xxxx          |

| ACCAL    | 0022        |        | Accumulator A Low Word Register  |        |        |        |        |         |               | 0000          |        |           |               |              |              |         |       |               |

| ACCAH    | 0024        |        | Accumulator A High Word Register |        |        |        |        |         |               | 0000          |        |           |               |              |              |         |       |               |

| ACCAU    | 0026        |        |                                  |        |        |        |        | Accumu  | lator A Uppe  | er Word Reg   | ister  |           |               |              |              |         |       | 0000          |

| ACCBL    | 0028        |        |                                  |        |        |        |        | Accum   | ulator B Low  | Word Regi     | ster   |           |               |              |              |         |       | 0000          |

| ACCBH    | 002A        |        |                                  |        |        |        |        | Accumu  | ulator B High | word Regi     | ster   |           |               |              |              |         |       | 0000          |

| ACCBU    | 002C        |        |                                  |        |        |        |        | Accumu  | lator B Uppe  | er Word Reg   | ister  |           |               |              |              |         |       | 0000          |

| PCL      | 002E        |        |                                  |        |        |        |        | Program | Counter Lo    | w Word Reg    | gister |           |               |              |              |         |       | 0000          |

| PCH      | 0030        | _      | _                                | _      | _      | _      | _      | _       | _             |               |        | Progra    | m Counter     | High Byte R  | Register     |         |       | 0000          |

| TBLPAG   | 0032        | _      | _                                | _      | _      | _      | _      | _       | -             |               |        | Table F   | Page Addres   | ss Pointer R | Register     |         |       | 0000          |

| PSVPAG   | 0034        | _      | _                                | _      | _      | _      | _      | —       | _             |               | Progra | am Memory | Visibility Pa | age Addres   | s Pointer Re | egister |       | 0000          |

| RCOUNT   | 0036        |        |                                  |        |        |        |        | Repe    | at Loop Cou   | inter Registe | er     |           |               |              |              |         |       | xxxx          |

| DCOUNT   | 0038        |        |                                  |        |        |        |        |         | DCOUNT        |               |        |           |               |              |              |         |       | xxxx          |

| DOSTARTL | 003A        |        |                                  |        |        |        |        | DOS     | TARTL<15:     | 1>            |        |           |               |              |              |         | 0     | xxxx          |

| DOSTARTH | 003C        | _      | _                                | _      | _      | _      | _      | _       | _             | _             | _      |           |               | DOSTAF       | RTH<5:0>     |         |       | 00xx          |

| DOENDL   | 003E        |        |                                  |        |        |        |        | DOE     | NDL<15:1      | >             |        |           |               |              |              |         | 0     | xxxx          |

| DOENDH   | 0040        | _      | _                                | —      | —      | _      | —      | —       | —             |               | —      |           |               | DOE          | NDH          |         |       | 00xx          |

| SR       | 0042        | OA     | OB                               | SA     | SB     | OAB    | SAB    | DA      | DC            | IPL2          | IPL1   | IPL0      | RA            | Ν            | OV           | Z       | С     | 0000          |

| CORCON   | 0044        |        | _                                | _      | US     | EDT    |        | DL<2:0> |               | SATA          | SATB   | SATDW     | ACCSAT        | IPL3         | PSV          | RND     | IF    | 0020          |

| MODCON   | 0046        | XMODEN | YMODEN                           | _      | —      |        | BWM    | 1<3:0>  |               |               | YWM    | <3:0>     | •             |              | XWM          | <3:0>   |       | 0000          |

| XMODSRT  | 0048        |        |                                  |        |        |        |        | X       | (S<15:1>      |               |        |           |               |              |              |         | 0     | xxxx          |

| XMODEND  | 004A        |        |                                  |        |        |        |        |         | (E<15:1>      |               |        |           |               |              |              |         | 1     | xxxx          |

#### TABLE 4-1. CPU CORE REGISTERS MAP

## 6.0 RESET

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

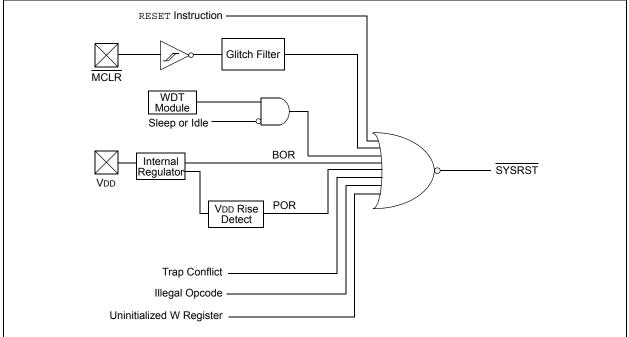

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode and Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Note: Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1). A POR will clear all bits except for the POR bit (RCON<0>), which is set. The user can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

## FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

| Reset Type      | Clock Source  | SYSRST Delay           | System Clock<br>Delay | FSCM<br>Delay | Notes            |

|-----------------|---------------|------------------------|-----------------------|---------------|------------------|

| POR             | EC, FRC, LPRC | TPOR + TSTARTUP + TRST | —                     | _             | 1, 2, 3          |

|                 | ECPLL, FRCPLL | TPOR + TSTARTUP + TRST | TLOCK                 | TFSCM         | 1, 2, 3, 5, 6    |

|                 | XT, HS, SOSC  | Tpor + Tstartup + Trst | Tost                  | TFSCM         | 1, 2, 3, 4, 6    |

|                 | XTPLL, HSPLL  | Tpor + Tstartup + Trst | Tost + Tlock          | TFSCM         | 1, 2, 3, 4, 5, 6 |

| BOR             | EC, FRC, LPRC | TSTARTUP + TRST        |                       | _             | 3                |

|                 | ECPLL, FRCPLL | TSTARTUP + TRST        | TLOCK                 | TFSCM         | 3, 5, 6          |

|                 | XT, HS, SOSC  | TSTARTUP + TRST        | Tost                  | TFSCM         | 3, 4, 6          |

|                 | XTPLL, HSPLL  | TSTARTUP + TRST        | Tost + Tlock          | TFSCM         | 3, 4, 5, 6       |

| MCLR            | Any Clock     | TRST                   | _                     | _             | 3                |

| WDT             | Any Clock     | Trst                   | —                     |               | 3                |

| Software        | Any Clock     | Trst                   | —                     | _             | 3                |

| Illegal Opcode  | Any Clock     | Trst                   | —                     | _             | 3                |

| Uninitialized W | Any Clock     | TRST                   | —                     | _             | 3                |

| Trap Conflict   | Any Clock     | Trst                   | —                     | _             | 3                |

### TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

**Note 1:** TPOR = Power-on Reset delay (10  $\mu$ s nominal).

- **2:** TSTARTUP = Conditional POR delay of 20 μs nominal (if on-chip regulator is enabled) or 64 ms nominal Power-up Timer delay (if regulator is disabled). TSTARTUP is also applied to all returns from powered-down states, including waking from Sleep mode, if the regulator is enabled.

- 3: TRST = Internal state Reset time (20 µs nominal).

- **4:** Tos⊤ = Oscillator Start-up Timer. A 10-bit counter counts 1024 oscillator periods before releasing the oscillator clock to the system.

- **5**: TLOCK = PLL lock time (20  $\mu$ s nominal).

- **6**: TFSCM = Fail-Safe Clock Monitor delay (100 μs nominal).

### 6.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) have a relatively long start-up time. Therefore, <u>one or more of the following conditions</u> is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

### 6.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it begins to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device automatically switches to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine.

### 6.2.2.1 FSCM Delay for Crystal and PLL Clock Sources

When the system clock source is provided by a crystal oscillator and/or the PLL, a small delay, TFSCM, is automatically inserted after the POR and PWRT delay times. The FSCM does not begin to monitor the system clock source until this delay expires. The FSCM delay time is nominally 500  $\mu$ s and provides additional time for the oscillator and/or PLL to stabilize. In most cases, the FSCM delay prevents an oscillator failure trap at a device Reset when the PWRT is disabled.

| U-0           | R/W-1         | R/W-0                                                | R/W-0            | U-0              | R/W-1           | R/W-0           | R/W-0 |

|---------------|---------------|------------------------------------------------------|------------------|------------------|-----------------|-----------------|-------|

| _             |               | IC8IP<2:0>                                           |                  | _                |                 | IC7IP<2:0>      |       |

| bit 15        |               |                                                      |                  |                  |                 |                 | bit   |

|               |               |                                                      |                  |                  |                 |                 |       |

| U-0           | R/W-1         | R/W-0                                                | R/W-0            | U-0              | R/W-1           | R/W-0           | R/W-0 |

|               |               | AD2IP<2:0>                                           |                  | —                |                 | INT1IP<2:0>     | L 14  |

| bit 7         |               |                                                      |                  |                  |                 |                 | bit   |

| Legend:       |               |                                                      |                  |                  |                 |                 |       |

| R = Readabl   | le bit        | W = Writable                                         | bit              | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value at | t POR         | '1' = Bit is set                                     |                  | '0' = Bit is cle | ared            | x = Bit is unkn | own   |

| bit 15        | Unimpleme     | nted: Read as '                                      | כ,               |                  |                 |                 |       |

| bit 14-12     | -             | Input Capture C                                      |                  | rrupt Priority b | its             |                 |       |

|               |               | upt is priority 7 (I                                 |                  |                  |                 |                 |       |

|               | •             |                                                      |                  |                  |                 |                 |       |

|               | •             |                                                      |                  |                  |                 |                 |       |

|               | 001 = Interru | upt is priority 1                                    |                  |                  |                 |                 |       |

|               | 000 = Interro | upt source is dis                                    | abled            |                  |                 |                 |       |

| bit 11        | Unimpleme     | nted: Read as 'o                                     | כ'               |                  |                 |                 |       |

| bit 10-8      |               | Input Capture C                                      |                  |                  | its             |                 |       |

|               | 111 = Interro | upt is priority 7 (I                                 | highest priority | / interrupt)     |                 |                 |       |

|               | •             |                                                      |                  |                  |                 |                 |       |

|               | •             |                                                      |                  |                  |                 |                 |       |

|               |               | upt is priority 1                                    | ablad            |                  |                 |                 |       |

| bit 7         |               | upt source is dis                                    |                  |                  |                 |                 |       |

| bit 6-4       | -             | nted: Read as 'o                                     |                  | Interrunt Drie   | rity bito       |                 |       |

| DIL 0-4       |               | <ul> <li>ADC2 Conversupt is priority 7 (I</li> </ul> | -                | -                | IIIY DIIS       |                 |       |

|               | •             |                                                      | ingricor priorit | ( interrupt)     |                 |                 |       |

|               | •             |                                                      |                  |                  |                 |                 |       |

|               | •             | upt is priority 1                                    |                  |                  |                 |                 |       |

|               |               | upt is phonity i<br>upt source is dis                | abled            |                  |                 |                 |       |

| bit 3         |               | nted: Read as 'o                                     |                  |                  |                 |                 |       |

| bit 2-0       | -             | External Interr                                      |                  | bits             |                 |                 |       |

|               |               | upt is priority 7 (I                                 |                  |                  |                 |                 |       |

|               | •             |                                                      |                  |                  |                 |                 |       |

|               | •             |                                                      |                  |                  |                 |                 |       |

|               | 001 = Interri | upt is priority 1                                    |                  |                  |                 |                 |       |

|               | 000 = Interru |                                                      |                  |                  |                 |                 |       |

| U-0           | R/W-1                                                                                                                                   | R/W-0                              | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|-------------------|------------------|-----------------|-------|--|--|--|--|--|--|

| —             |                                                                                                                                         | T4IP<2:0>                          |                |                   |                  | OC4IP<2:0>      |       |  |  |  |  |  |  |

| bit 15        |                                                                                                                                         |                                    |                |                   |                  |                 | bit   |  |  |  |  |  |  |

| U-0           | R/W-1                                                                                                                                   | R/W-0                              | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |  |  |  |  |  |  |

| _             |                                                                                                                                         | OC3IP<2:0>                         | -              | _                 |                  | DMA2IP<2:0>     | -     |  |  |  |  |  |  |

| bit 7         |                                                                                                                                         |                                    |                |                   |                  |                 | bit   |  |  |  |  |  |  |

| Legend:       |                                                                                                                                         |                                    |                |                   |                  |                 |       |  |  |  |  |  |  |

| R = Readabl   | e bit                                                                                                                                   | W = Writable I                     | oit            | U = Unimple       | mented bit, rea  | ad as '0'       |       |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                     | '1' = Bit is set                   |                | '0' = Bit is cle  | eared            | x = Bit is unkn | own   |  |  |  |  |  |  |

| bit 15        | Unimpleme                                                                                                                               | nted: Read as 'o                   | )'             |                   |                  |                 |       |  |  |  |  |  |  |

| bit 14-12     | T4IP<2:0>:                                                                                                                              | Timer4 Interrupt                   | Priority bits  |                   |                  |                 |       |  |  |  |  |  |  |

|               | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                   |                                    |                |                   |                  |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                                       |                                    |                |                   |                  |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                                       |                                    |                |                   |                  |                 |       |  |  |  |  |  |  |

|               | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                     |                                    |                |                   |                  |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                         | -                                  |                |                   |                  |                 |       |  |  |  |  |  |  |

| bit 11        | -                                                                                                                                       | nted: Read as 'o                   |                |                   |                  |                 |       |  |  |  |  |  |  |

| bit 10-8      | <b>OC4IP&lt;2:0&gt;:</b> Output Compare Channel 4 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                    |                |                   |                  |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                                       | •                                  |                |                   |                  |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                                       |                                    |                |                   |                  |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                                       | 001 = Interrupt is priority 1      |                |                   |                  |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                         | upt is phonty if                   | abled          |                   |                  |                 |       |  |  |  |  |  |  |

| bit 7         |                                                                                                                                         | nted: Read as 'o                   |                |                   |                  |                 |       |  |  |  |  |  |  |

| bit 6-4       | OC3IP<2:0>                                                                                                                              | Output Compa                       | re Channel 3   | 3 Interrupt Prior | rity bits        |                 |       |  |  |  |  |  |  |

|               | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                              |                                    |                |                   |                  |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                                       |                                    |                |                   |                  |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                                       |                                    |                |                   |                  |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                         | •<br>001 = Interrupt is priority 1 |                |                   |                  |                 |       |  |  |  |  |  |  |