## Microchip Technology - <u>DSPIC33FJ256MC510T-I/PF Datasheet</u>

Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                   |

|---------------------------|-----------------------------------------------------------------------------------|

| Product Status            | Obsolete                                                                          |

| Core Processor            | dsPIC                                                                             |

| Core Size                 | 16-Bit                                                                            |

| Speed                     | 40 MIPs                                                                           |

| Connectivity              | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals               | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O             | 85                                                                                |

| Program Memory Size       | 256KB (256K x 8)                                                                  |

| Program Memory Type       | FLASH                                                                             |

| EEPROM Size               | -                                                                                 |

| RAM Size                  | 16K x 8                                                                           |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters           | A/D 24x10/12b                                                                     |

| Oscillator Type           | Internal                                                                          |

| Operating Temperature     | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type             | Surface Mount                                                                     |

| Package / Case            | 100-TQFP                                                                          |

| Supplier Device Package   | 100-TQFP (14x14)                                                                  |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256mc510t-i-pf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **High-Performance, 16-Bit Digital Signal Controllers**

## **Operating Range:**

- Up to 40 MIPS operation (at 3.0-3.6V):

- Industrial temperature range (-40°C to +85°C)

#### **High-Performance DSC CPU:**

- · Modified Harvard architecture

- · C compiler optimized instruction set

- 16-bit wide data path

- · 24-bit wide instructions

- Linear program memory addressing up to 4M instruction words

- · Linear data memory addressing up to 64 Kbytes

- 83 base instructions: mostly 1 word/1 cycle

- Two 40-bit accumulators:

- With rounding and saturation options

- · Flexible and powerful addressing modes:

- Indirect, Modulo and Bit-Reversed

- · Software stack

- 16 x 16 fractional/integer multiply operations

- 32/16 and 16/16 divide operations

- · Single-cycle multiply and accumulate:

- Accumulator write back for DSP operations

- Dual data fetch

- Up to ±16-bit shifts for up to 40-bit data

#### **Direct Memory Access (DMA):**

- · 8-channel hardware DMA

- 2 Kbytes dual ported DMA buffer area (DMA RAM) to store data transferred via DMA:

- Allows data transfer between RAM and a peripheral while CPU is executing code (no cycle stealing)

- Most peripherals support DMA

#### **Interrupt Controller:**

- · 5-cycle latency

- · Up to 67 available interrupt sources

- · Up to five external interrupts

- · Seven programmable priority levels

- · Five processor exceptions

#### Digital I/O:

- Up to 85 programmable digital I/O pins

- · Wake-up/Interrupt-on-Change on up to 24 pins

- · Output pins can drive from 3.0V to 3.6V

- · All digital input pins are 5V tolerant

- · 4 mA sink on all I/O pins

#### On-Chip Flash and SRAM:

- · Flash program memory, up to 256 Kbytes

- Data SRAM, up to 30 Kbytes (includes 2 Kbytes of DMA RAM)

#### **System Management:**

- · Flexible clock options:

- External, crystal, resonator, internal RC

- Fully integrated PLL

- Extremely low jitter PLL

- · Power-up Timer

- · Oscillator Start-up Timer/Stabilizer

- · Watchdog Timer with its own RC oscillator

- · Fail-Safe Clock Monitor

- · Reset by multiple sources

#### **Power Management:**

- · On-chip 2.5V voltage regulator

- · Switch between clock sources in real time

- · Idle, Sleep and Doze modes with fast wake-up

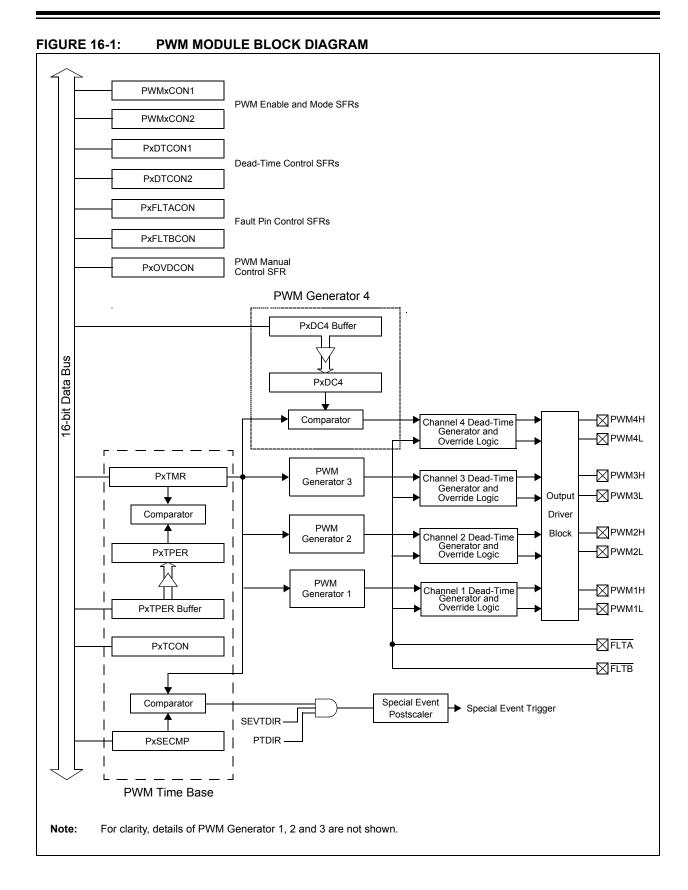

#### Timers/Capture/Compare/PWM:

- Timer/Counters, up to nine 16-bit timers:

- Can pair up to make four 32-bit timers

- 1 timer runs as Real-Time Clock with external 32.768 kHz oscillator

- Programmable prescaler

- · Input Capture (up to eight channels):

- Capture on up, down or both edges

- 16-bit capture input functions

- 4-deep FIFO on each capture

- · Output Compare (up to eight channels):

- Single or Dual 16-Bit Compare mode

- 16-bit Glitchless PWM mode

#### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | U-0 | U-0 | U-0 | U-0 | U-0   |

|-----------------------|----------------------|----------------------|-----|-----|-----|-----|-------|

| WR                    | WREN                 | WRERR                | _   | _   | _   | _   | _     |

| bit 15                |                      |                      |     |     |     |     | bit 8 |

| U-0   | R/W-0 <sup>(1)</sup> | U-0 | U-0 | R/W-0 <sup>(1)</sup>      | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> |

|-------|----------------------|-----|-----|---------------------------|----------------------|----------------------|----------------------|

| _     | ERASE                | _   | _   | NVMOP<3:0> <sup>(2)</sup> |                      |                      |                      |

| bit 7 |                      |     |     |                           |                      |                      | bit 0                |

| Legend:           | SO = Settable-only bit | SO = Settable-only bit   |                    |  |  |  |  |

|-------------------|------------------------|--------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit       | U = Unimplemented bit, ı | read as '0'        |  |  |  |  |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |  |

bit 15 WR: Write Control bit

1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bit is cleared by hardware once operation is complete

0 = Program or erase operation is complete and inactive

bit 14 WREN: Write Enable bit

1 = Enable Flash program/erase operations

0 = Inhibit Flash program/erase operations

bit 13 WRERR: Write Sequence Error Flag bit

1 = An improper program or erase sequence attempt or termination has occurred (bit is set automatically on any set attempt of the WR bit)

0 = The program or erase operation completed normally

bit 12-7 Unimplemented: Read as '0'

bit 6 **ERASE**: Erase/Program Enable bit

1 = Perform the erase operation specified by NVMOP<3:0> on the next WR command

0 = Perform the program operation specified by NVMOP<3:0> on the next WR command

bit 5-4 **Unimplemented:** Read as '0'

bit 3-0 **NVMOP<3:0>:** NVM Operation Select bits<sup>(2)</sup>

If ERASE = 1:

1111 = Memory bulk erase operation

1110 = Reserved

1101 = Erase General Segment

1100 = Erase Secure Segment

1011 = Reserved

0011 = No operation

0010 = Memory page erase operation

0001 = No operation

0000 = Erase a single Configuration register byte

If ERASE = 0:

1111 = No operation

1110 = Reserved

1101 = No operation

1100 = No operation

1011 = Reserved

0011 = Memory word program operation

0010 = No operation

0001 = Memory row program operation

0000 = Program a single Configuration register byte

Note 1: These bits can only be reset on POR.

2: All other combinations of NVMOP<3:0> are unimplemented.

#### 6.0 RESET

Note:

This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8**. "**Reset**" (DS70192) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

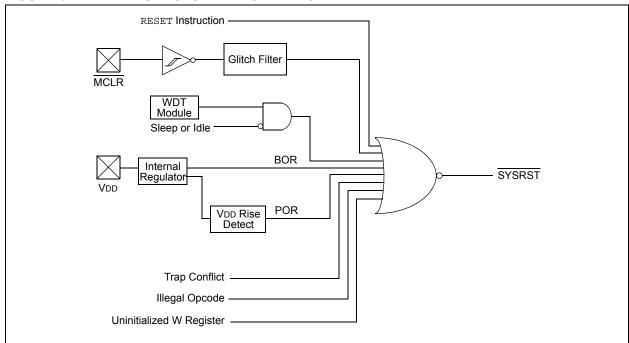

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

· POR: Power-on Reset

· BOR: Brown-out Reset

MCLR: Master Clear Pin Reset

• SWR: RESET Instruction

· WDT: Watchdog Timer Reset

· TRAPR: Trap Conflict Reset

IOPUWR: Illegal Opcode and Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Note: Refer to the specific peripheral or CPU section of this manual for register Reset states

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1). A POR will clear all bits except for the POR bit (RCON<0>), which is set. The user can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

#### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

## REGISTER 8-5: DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PAD<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15    |       |       |       |       |       |       |       |  |  |

| R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|----------|-------|-------|-------|-------|-------|-------|--|--|

|       | PAD<7:0> |       |       |       |       |       |       |  |  |

| bit 7 |          |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

## REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                   | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------------------------|-------|

| _      | _   | _   | _   | _   | _   | CNT<9:8> <sup>(2)</sup> |       |

| bit 15 |     |     |     |     |     |                         | bit 8 |

| R/W-0 | R/W-0                   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-------------------------|-------|-------|-------|-------|-------|-------|--|--|--|

|       | CNT<7:0> <sup>(2)</sup> |       |       |       |       |       |       |  |  |  |

| bit 7 |                         |       |       |       |       |       |       |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **Unimplemented:** Read as '0'

bit 9-0 CNT<9:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

2: Number of DMA transfers = CNT<9:0> + 1.

### REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0 (CONTINUED)

bit 3 XWCOL3: Channel 3 DMA RAM Write Collision Flag bit

1 = Write collision detected0 = No write collision detected

bit 2 XWCOL2: Channel 2 DMA RAM Write Collision Flag bit

1 = Write collision detected0 = No write collision detected

bit 1 XWCOL1: Channel 1 DMA RAM Write Collision Flag bit

1 = Write collision detected0 = No write collision detected

bit 0 XWCOL0: Channel 0 DMA RAM Write Collision Flag bit

1 = Write collision detected0 = No write collision detected

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

bit 1 LPOSCEN: Secondary (LP) Oscillator Enable bit

1 = Enable secondary oscillator0 = Disable secondary oscillatorOSWEN: Oscillator Switch Enable bit

1 = Request oscillator switch to selection specified by NOSC<2:0> bits

0 = Oscillator switch is complete

bit 0

**Note 1:** Writes to this register require an unlock sequence. Refer to **Section 7. "Oscillator"** (DS70186) in the "dsPIC33F Family Reference Manual" (available from the Microchip website) for details.

2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

#### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 <sup>(1)</sup> |

|--------|-----|-----|-----|-----|-----|-----|----------------------|

| _      | _   | _   | _   | _   | _   | _   | PLLDIV<8>            |

| bit 15 |     |     |     |     |     |     | bit 8                |

| R/W-0       | R/W-0 | R/W-1 | R/W-1 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| PLLDIV<7:0> |       |       |       |       |       |       |       |  |

| bit 7       |       |       |       |       |       |       |       |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-9 **Unimplemented:** Read as '0'

bit 8-0 PLLDIV<8:0>: PLL Feedback Divisor bits (also denoted as 'M', PLL multiplier)

000000000 = 2 000000001 = 3 000000010 = 4

•

•

•

000110000 = 50 (default)

•

•

111111111 = 513

### 9.2 Clock Switching Operation

Applications are free to switch between any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects that could result from this flexibility, dsPIC33FJXXXMCX06/X08/X10 devices have a safeguard lock built into the switch process.

ote: Primary Oscillator mode has three different submodes (XT, HS and EC) which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

#### 9.2.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to 'o'. (Refer to **Section 23.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

#### 9.2.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires the following basic sequence:

- If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC control bits (OSCCON<10:8>) for the new oscillator source.

- Perform the unlock sequence to allow a write to the OSCCON register low byte.

- Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

The clock switching hardware compares the COSC status bits with the new value of the NOSC control bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and the CF (OSCCON<3>) status bits are cleared.

- 3. The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred to the COSC status bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- Refer to 7. "Oscillator" (DS70186) in the "dsPIC33F Family Reference Manual" for details.

#### 9.3 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

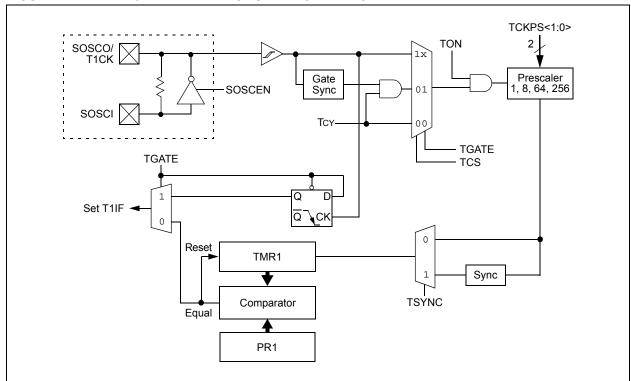

### 12.0 TIMER1

Note:

This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 11.** "Timers" (DS70205) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- · 16-bit Timer

- · 16-bit Synchronous Counter

- · 16-bit Asynchronous Counter

Timer1 also supports the following features:

- · Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 12-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation, do the following:

- Set the TON bit (= 1) in the T1CON register.

- Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- 4. Set or clear the TSYNC bit in T1CON to select synchronous or asynchronous operation.

- Load the timer period value into the PR1 register.

- If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

#### REGISTER 13-1: TxCON (T2CON, T4CON, T6CON OR T8CON) CONTROL REGISTER

| R/W-0  | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-------|-----|-----|-----|-----|-------|

| TON    | _   | TSIDL | _   | _   | _   | _   |       |

| bit 15 |     |       |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0      | R/W-0 | R/W-0 | U-0 | R/W-0              | U-0   |

|-------|-------|------------|-------|-------|-----|--------------------|-------|

| _     | TGATE | TCKPS<1:0> |       | T32   | _   | TCS <sup>(1)</sup> | _     |

| bit 7 |       |            |       |       |     |                    | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 TON: Timerx On bit

When T32 = 1:

1 = Starts 32-bit Timerx/y

0 = Stops 32-bit Timerx/y

When T32 = 0:

1 = Starts 16-bit Timerx

0 = Stops 16-bit Timerx

bit 14 **Unimplemented:** Read as '0'

bit 13 TSIDL: Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12-7 Unimplemented: Read as '0'

bit 6 TGATE: Timerx Gated Time Accumulation Enable bit

When TCS = 1: This bit is ignored When TCS = 0:

1 = Gated time accumulation enabled

0 = Gated time accumulation disabled

bit 5-4 TCKPS<1:0>: Timerx Input Clock Prescale Select bits

11 = 1:256 10 = 1:64 01 = 1:8 00 = 1:1

bit 3 T32: 32-bit Timer Mode Select bit

1 = Timerx and Timery form a single 32-bit timer0 = Timerx and Timery act as two 16-bit timers

bit 2 **Unimplemented:** Read as '0'

bit 1 TCS: Timerx Clock Source Select bit<sup>(1)</sup>

1 = External clock from pin TxCK (on the rising edge)

0 = Internal clock (Fcy)

bit 0 **Unimplemented:** Read as '0'

Note 1: The TxCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

### REGISTER 16-10: PxFLTBCON: FAULT B CONTROL REGISTER

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FBOV4H | FBOV4L | FBOV3H | FBOV3L | FBOV2H | FBOV2L | FBOV1H | FBOV1L |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0 | U-0 | U-0 | U-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|-----|-----|-----|----------------------|----------------------|----------------------|----------------------|

| FLTBM | _   | _   | _   | FBEN4 <sup>(1)</sup> | FBEN3 <sup>(1)</sup> | FBEN2 <sup>(1)</sup> | FBEN1 <sup>(1)</sup> |

| bit 7 |     |     |     |                      |                      |                      | bit 0                |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| FBOVxH<4:1>:FBOVxL<4:1>: Fault Input B PWM Override Value bits                               |

|----------------------------------------------------------------------------------------------|

| 1 = The PWM output pin is driven active on an external Fault input event                     |

| 0 = The PWM output pin is driven inactive on an external Fault input event                   |

| FLTBM: Fault B Mode bit                                                                      |

| 1 = The Fault B input pin functions in the Cycle-by-Cycle mode                               |

| 0 = The Fault B input pin latches all control pins to the states programmed in FLTBCON<15:8> |

| Unimplemented: Read as '0'                                                                   |

| FBEN4: Fault Input B Enable bit <sup>(1)</sup>                                               |

| 1 = PWM4H/PWM4L pin pair is controlled by Fault Input B                                      |

| 0 = PWM4H/PWM4L pin pair is not controlled by Fault Input B                                  |

| FBEN3: Fault Input B Enable bit <sup>(1)</sup>                                               |

| 1 = PWM3H/PWM3L pin pair is controlled by Fault Input B                                      |

| 0 = PWM3H/PWM3L pin pair is not controlled by Fault Input B                                  |

| FBEN2: Fault Input B Enable bit <sup>(1)</sup>                                               |

| 1 = PWM2H/PWM2L pin pair is controlled by Fault Input B                                      |

| 0 = PWM2H/PWM2L pin pair is not controlled by Fault Input B                                  |

| FBEN1: Fault Input B Enable bit <sup>(1)</sup>                                               |

| 1 = PWM1H/PWM1L pin pair is controlled by Fault Input B                                      |

| 0 = PWM1H/PWM1L pin pair is not controlled by Fault Input B                                  |

|                                                                                              |

Note 1: Fault A pin has priority over Fault B pin, if enabled.

#### REGISTER 18-1: SPIXSTAT: SPIX STATUS AND CONTROL REGISTER

| R/W-0  | U-0 | R/W-0   | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|---------|-----|-----|-----|-----|-------|

| SPIEN  | _   | SPISIDL | _   | _   | _   | _   | _     |

| bit 15 |     |         |     |     |     |     | bit 8 |

| U-0   | R/C-0  | U-0 | U-0 | U-0 | U-0 | R-0    | R-0    |

|-------|--------|-----|-----|-----|-----|--------|--------|

| _     | SPIROV | _   | _   | _   | _   | SPITBF | SPIRBF |

| bit 7 |        |     |     |     |     |        | bit 0  |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 SPIEN: SPIx Enable bit

1 = Enables module and configures SCKx, SDOx, SDIx and SSx as serial port pins

0 = Disables module

bit 14 **Unimplemented:** Read as '0' bit 13 **SPISIDL:** Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12-7 Unimplemented: Read as '0'

bit 6 SPIROV: Receive Overflow Flag bit

1 = A new byte/word is completely received and discarded. The user software has not read the

previous data in the SPIxBUF register

0 = No overflow has occurred

bit 5-2 **Unimplemented:** Read as '0'

bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

1 = Transmit not yet started; SPIxTXB is full 0 = Transmit started; SPIxTXB is empty

Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB.

Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.

bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive complete; SPIxRXB is full

0 = Receive is not complete; SPIxRXB is empty

Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB.

Automatically cleared in hardware when core reads SPIxBUF location, reading SPIxRXB.

# 19.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

Note:

This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Inter-Integrated Circuit<sup>TM</sup> ( $I^2C^{TM}$ )" (DS70195) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

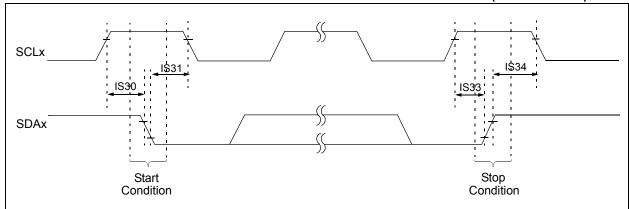

The Inter-Integrated Circuit ( $I^2C$ ) module, with its 16-bit interface, provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard.

The dsPIC33FJXXXMCX06/X08/X10 devices have up to two  $I^2C$  interface modules, denoted as I2C1 and I2C2. Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each  $I^2C$  module 'x' (x = 1 or 2) offers the following key features:

- I<sup>2</sup>C interface supports both master and slave operation.

- I<sup>2</sup>C Slave mode supports 7- and 10-bit addresses.

- I<sup>2</sup>C Master mode supports 7- and 10-bit addresses.

- I<sup>2</sup>C Port allows bidirectional transfers between master and slaves.

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control).

- I<sup>2</sup>C supports multi-master operation; it detects bus collision and will arbitrate accordingly.

### 19.1 Operating Modes

The hardware fully implements all the master and slave functions of the I<sup>2</sup>C Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The  $I^2C$  module can operate either as a slave or a master on an  $I^2C$  bus.

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit address

- I<sup>2</sup>C slave operation with 10-bit address

- I<sup>2</sup>C master operation with 7 or 10-bit address

For details about the communication sequence in each of these modes, please refer to the "dsPIC30F Family Reference Manual".

## 19.2 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CSTAT are read/write.

I2CxRSR is the shift register used for shifting data, whereas I2CxRCV is the buffer register to which data bytes are written, or from which data bytes are read. I2CxRCV is the receive buffer. I2CxTRN is the transmit register to which bytes are written during a transmit operation.

The I2CxADD register holds the slave address. A status bit, ADD10, indicates 10-bit Address mode. The I2CxBRG acts as the Baud Rate Generator (BRG) reload value.

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV and an interrupt pulse is generated.

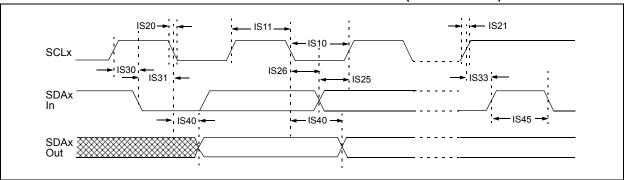

### FIGURE 26-20: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (SLAVE MODE)

## FIGURE 26-21: I2Cx BUS DATA TIMING CHARACTERISTICS (SLAVE MODE)

TABLE 26-37: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

| AC CHA       | RACTERIS         | STICS                     |                           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industr |       |            |                                             |

|--------------|------------------|---------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|---------------------------------------------|

| Param<br>No. | Symbol           | Charact                   | Min                       | Max                                                                                                                                                                      | Units | Conditions |                                             |

| IS10         | TLO:SCL          | Clock Low Time            | 100 kHz mode              | 4.7                                                                                                                                                                      | _     | μs         | Device must operate at a minimum of 1.5 MHz |

|              |                  |                           | 400 kHz mode              | 1.3                                                                                                                                                                      | _     | μs         | Device must operate at a minimum of 10 MHz  |

|              |                  |                           | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                      | _     | μs         | _                                           |

| IS11         | THI:SCL          | Clock High Time           | 100 kHz mode              | 4.0                                                                                                                                                                      |       | μs         | Device must operate at a minimum of 1.5 MHz |

|              |                  |                           | 400 kHz mode              | 0.6                                                                                                                                                                      | _     | μs         | Device must operate at a minimum of 10 MHz  |

|              |                  |                           | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                      | _     | μs         | _                                           |

| IS20         | TF:SCL           | SDAx and SCLx             | 100 kHz mode              | _                                                                                                                                                                        | 300   | ns         | CB is specified to be from                  |

|              |                  | Fall Time                 | 400 kHz mode              | 20 + 0.1 CB                                                                                                                                                              | 300   | ns         | 10 to 400 pF                                |

|              |                  |                           | 1 MHz mode <sup>(1)</sup> | _                                                                                                                                                                        | 100   | ns         |                                             |

| IS21         | TR:SCL           | SDAx and SCLx             | 100 kHz mode              | _                                                                                                                                                                        | 1000  | ns         | CB is specified to be from                  |

|              |                  | Rise Time                 | 400 kHz mode              | 20 + 0.1 CB                                                                                                                                                              | 300   | ns         | 10 to 400 pF                                |

|              |                  | 1 MHz mode <sup>(1)</sup> | _                         | 300                                                                                                                                                                      | ns    |            |                                             |

|              | Data Input       | 100 kHz mode              | 250                       | _                                                                                                                                                                        | ns    | _          |                                             |

|              | Setup Time       | 400 kHz mode              | 100                       | _                                                                                                                                                                        | ns    |            |                                             |

|              |                  | 1 MHz mode <sup>(1)</sup> | 100                       | _                                                                                                                                                                        | ns    |            |                                             |

| IS26         | S26 THD:DAT Data | Data Input                | 100 kHz mode              | 0                                                                                                                                                                        | _     | μs         | _                                           |

|              | Hold Time        | 400 kHz mode              | 0                         | 0.9                                                                                                                                                                      | μs    |            |                                             |

|              |                  |                           | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                                                        | 0.3   | μs         |                                             |

| IS30         | Tsu:sta          | Start Condition           | 100 kHz mode              | 4.7                                                                                                                                                                      | _     | μs         | Only relevant for Repeated                  |

|              |                  | Setup Time                | 400 kHz mode              | 0.6                                                                                                                                                                      | _     | μs         | Start condition                             |

|              |                  |                           | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                                                     | _     | μs         |                                             |

| IS31         | THD:STA          | Start Condition           | 100 kHz mode              | 4.0                                                                                                                                                                      | _     | μs         | After this period, the first                |

|              |                  | Hold Time                 | 400 kHz mode              | 0.6                                                                                                                                                                      | _     | μs         | clock pulse is generated                    |

|              |                  |                           | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                                                     | _     | μs         |                                             |

| IS33         | Tsu:sto          | Stop Condition            | 100 kHz mode              | 4.7                                                                                                                                                                      | _     | μs         | _                                           |

|              |                  | Setup Time                | 400 kHz mode              | 0.6                                                                                                                                                                      | _     | μs         |                                             |

|              |                  |                           | 1 MHz mode <sup>(1)</sup> | 0.6                                                                                                                                                                      | _     | μs         |                                             |

| IS34         | THD:STO          | Stop Condition            | 100 kHz mode              | 4000                                                                                                                                                                     | _     | ns         | _                                           |

|              |                  | Hold Time                 | 400 kHz mode              | 600                                                                                                                                                                      | _     | ns         |                                             |

|              |                  |                           | 1 MHz mode <sup>(1)</sup> | 250                                                                                                                                                                      |       | ns         |                                             |

| IS40         | TAA:SCL          | Output Valid              | 100 kHz mode              | 0                                                                                                                                                                        | 3500  | ns         |                                             |

|              |                  | From Clock                | 400 kHz mode              | 0                                                                                                                                                                        | 1000  | ns         |                                             |

|              | <u> </u>         |                           | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                                                        | 350   | ns         |                                             |

| IS45         | TBF:SDA          | Bus Free Time             | 100 kHz mode              | 4.7                                                                                                                                                                      |       | μs         | Time the bus must be free                   |

|              |                  |                           | 400 kHz mode              | 1.3                                                                                                                                                                      |       | μs         | before a new transmission                   |

|              |                  |                           | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                      | _     | μs         | can start                                   |

| IS50         | Св               | Bus Capacitive Lo         | ading                     | _                                                                                                                                                                        | 400   | pF         |                                             |

Note 1: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**TABLE 26-39: ADC MODULE SPECIFICATIONS**

| AC CHARACTERISTICS |        |                                                | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |            |                                  |          |                                                                                         |

|--------------------|--------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------|----------|-----------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                 | Min.                                                                                                                                                                   | Тур        | Max.                             | Units    | Conditions                                                                              |

|                    |        |                                                | Device                                                                                                                                                                 | Supply     | /                                |          |                                                                                         |

| AD01               | AVDD   | Module VDD Supply                              | Greater of VDD – 0.3 or 3.0                                                                                                                                            |            | Lesser of<br>VDD + 0.3<br>or 3.6 | V        | _                                                                                       |

| AD02               | AVss   | Module Vss Supply                              | Vss - 0.3                                                                                                                                                              | _          | Vss + 0.3                        | V        | _                                                                                       |

|                    |        |                                                | Reference                                                                                                                                                              | ce Inpu    | ts                               |          |                                                                                         |

| AD05               | VREFH  | Reference Voltage High                         | AVss + 2.7                                                                                                                                                             | _          | AVDD                             | V        | See Note 1                                                                              |

| AD05a              |        |                                                | 3.0                                                                                                                                                                    | l          | 3.6                              | V        | VREFH = AVDD<br>VREFL = AVSS = 0                                                        |

| AD06               | VREFL  | Reference Voltage Low                          | AVss                                                                                                                                                                   | l          | AVDD - 2.7                       | V        | See Note 1                                                                              |

| AD06a              |        |                                                | 0                                                                                                                                                                      | 1          | 0                                | V        | VREFH = AVDD<br>VREFL = AVSS = 0                                                        |

| AD07               | VREF   | Absolute Reference<br>Voltage                  | 2.7                                                                                                                                                                    | _          | 3.6                              | V        | VREF = VREFH - VREFL                                                                    |

| AD08               | IREF   | Current Drain                                  |                                                                                                                                                                        | 250<br>—   | 550<br>10                        | μA<br>μA | ADC operating, see Note 1 ADC off, see Note 1                                           |

| AD08a              | IAD    | Operating Current                              | _                                                                                                                                                                      | 7.0<br>2.7 | 9.0<br>3.2                       | mA<br>mA | 10-bit ADC mode, See <b>Note 2</b> 12-bit ADC mode, See <b>Note 2</b>                   |

|                    |        |                                                | Analo                                                                                                                                                                  | g Input    |                                  |          |                                                                                         |

| AD12               | VINH   | Input Voltage Range Vілн                       | VINL                                                                                                                                                                   | 1          | VREFH                            | V        | This voltage reflects Sample and Hold Channels 0, 1, 2 and 3 (CH0-CH3), positive input  |

| AD13               | VINL   | Input Voltage Range VINL                       | VREFL                                                                                                                                                                  | _          | AVss + 1V                        | V        | This voltage reflects Sample and Hold Channels 0, 1, 2, and 3 (CH0-CH3), negative input |

| AD17               | RIN    | Recommended Impedance of Analog Voltage Source | _                                                                                                                                                                      | _          | 200<br>200                       | $\Omega$ | 10-bit ADC<br>12-bit ADC                                                                |

Note 1: These parameters are not characterized or tested in manufacturing.

<sup>2:</sup> These parameters are characterized; but not tested in manufacturing

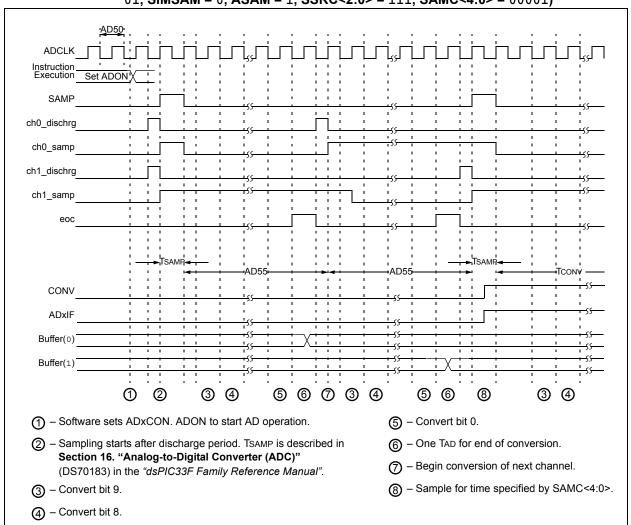

FIGURE 26-25: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

### 80-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |           |           |      |

|--------------------------|------------------|-----------|-----------|------|

| Din                      | Dimension Limits |           | NOM       | MAX  |

| Number of Leads          | N                |           | 80        |      |

| Lead Pitch               | е                |           | 0.50 BSC  |      |

| Overall Height           | Α                | _         | _         | 1.20 |

| Molded Package Thickness | A2               | 0.95      | 1.00      | 1.05 |

| Standoff                 | A1               | 0.05      | _         | 0.15 |

| Foot Length              | L                | 0.45      | 0.60      | 0.75 |

| Footprint                | L1               | 1.00 REF  |           |      |

| Foot Angle               | ф                | 0°        | 3.5°      | 7°   |

| Overall Width            | E                |           | 14.00 BSC |      |

| Overall Length           | D                |           | 14.00 BSC |      |

| Molded Package Width     | E1               |           | 12.00 BSC |      |

| Molded Package Length    | D1               | 12.00 BSC |           |      |

| Lead Thickness           | С                | 0.09      | _         | 0.20 |

| Lead Width               | b                | 0.17      | 0.22      | 0.27 |

| Mold Draft Angle Top     | α                | 11°       | 12°       | 13°  |

| Mold Draft Angle Bottom  |                  | 11°       | 12°       | 13°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-092B

## **INDEX**

| Α                                         |          | CPU Clocking System                              | . 144        |

|-------------------------------------------|----------|--------------------------------------------------|--------------|

| A/D Converter                             | 241      | Options                                          | . 144        |

| DMA                                       |          | Selection                                        | . 144        |

| Initialization                            |          | Customer Change Notification Service             | 335          |

|                                           |          | Customer Notification Service                    | 335          |

| Key Features                              |          | Customer Support                                 | 335          |

| AC Characteristics                        |          | _                                                |              |

| Internal RC Accuracy                      |          | D                                                |              |

| Load Conditions                           | 282      | Data Accumulators and Adder/Subtractor           | 31           |

| ADC Module                                | 50       | Data Space Write Saturation                      | 33           |

| ADC11 Register Map                        |          | Overflow and Saturation                          | 31           |

| ADC2 Register Map                         |          | Round Logic                                      |              |

| Alternate Interrupt Vector Table (AIVT)   |          | Write Back                                       |              |

| Arithmetic Logic Unit (ALU)               | 29       | Data Address Space                               |              |

| Assembler                                 |          | Alignment                                        |              |

| MPASM Assembler                           | 270      | Memory Map for dsPIC33FJXXXMCX06/X08/X10         |              |

| В                                         |          | vices with 16 KB RAM                             |              |

|                                           |          | Memory Map for dsPIC33FJXXXMCX06/X08/X10         |              |

| Barrel Shifter                            |          | vices with 30 KB RAM                             |              |

| Bit-Reversed Addressing                   |          | Memory Map for dsPIC33FJXXXMCX06/X08/X10         |              |

| Example                                   |          | vices with 8 KB RAM                              |              |

| Implementation                            |          | Near Data Space                                  |              |

| Sequence Table (16-Entry)                 | 67       | Software Stack                                   |              |

| Block Diagrams                            |          | Width                                            |              |

| 16-bit Timer1 Module                      | 163      |                                                  |              |

| A/D Module                                |          | DC Characteristics                               |              |

| Connections for On-Chip Voltage Regulator | 258      | I/O Pin Input Specifications                     |              |

| Device Clock                              | 143, 145 | I/O Pin Output Specifications                    |              |

| DSP Engine                                | 30       | Idle Current (IIDLE)                             |              |

| dsPIC33F                                  | 14       | Operating Current (IDD)                          |              |

| dsPIC33F CPU Core                         | 24       | Power-Down Current (IPD)                         |              |

| ECAN Module                               | 216      | Program Memory                                   |              |

| Input Capture                             | 171      | Temperature and Voltage Specifications           |              |

| Output Compare                            |          | Development Support                              | . 269        |

| PLL                                       |          | DMA Module                                       |              |

| PWM Module                                |          | DMA Register Map                                 |              |

| Quadrature Encoder Interface              |          | DMAC Registers                                   | . 134        |

| Reset System                              |          | DMAxCNT                                          | . 134        |

| Shared Port Structure                     |          | DMAxCON                                          | . 134        |

| SPI                                       |          | DMAxPAD                                          | . 134        |

| Timer2 (16-bit)                           |          | DMAxREQ                                          | . 134        |

| Timer2/3 (32-bit)                         |          | DMAxSTA                                          | . 134        |

| UART                                      |          | DMAxSTB                                          | . 134        |

| Watchdog Timer (WDT)                      |          | DSP Engine                                       | 29           |

| watchdog filler (wb1)                     | 239      | Multiplier                                       | 31           |

| C                                         |          | _                                                |              |

| C Compilers                               |          | E                                                |              |

| MPLAB C18                                 | 270      | ECAN Module                                      |              |

| MPLAB C30                                 |          | CiFMSKSEL2 register                              | 233          |

| Clock Switching                           |          | ECAN1 Register Map (C1CTRL1.WIN = 0 or 1)        | 55           |

|                                           |          | ECAN1 Register Map (C1CTRL1.WIN = 0)             | 55           |

| Enabling                                  |          | ECAN1 Register Map (C1CTRL1.WIN = 1)             |              |

| Sequence                                  | 131      | ECAN2 Register Map (C2CTRL1.WIN = 0 or 1)        |              |

| Code Examples                             | 70       | ECAN2 Register Map (C2CTRL1.WIN = 0) 58          |              |

| Erasing a Program Memory Page             |          | Frame Types                                      |              |

| Initiating a Programming Sequence         |          | Modes of Operation                               |              |

| Loading Write Buffers                     |          | Overview                                         |              |

| Port Write/Read                           |          | ECAN Registers                                   |              |

| PWRSAV Instruction Syntax                 |          | Filter 15-8 Mask Selection Register (CiFMSKSEL2) | 233          |

| Code Protection                           |          | Electrical Characteristics                       |              |

| Configuration Bits                        |          | AC                                               |              |

| Configuration Register Map                |          | Enhanced CAN Module                              |              |

| Configuring Analog Port Pins              | 162      | Equations                                        | <u>د ا د</u> |

| CPU                                       |          | Device Operating Frequency                       | 1//          |

| Control Register                          | 26       |                                                  |              |

|                                           |          | Errata                                           | 1            |