Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256КВ (256К х 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256mc510t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-0              | U-0                            | U-0                                    | R/W-0           | R/W-0               | R-0              | R-0              | R-0   |

|------------------|--------------------------------|----------------------------------------|-----------------|---------------------|------------------|------------------|-------|

|                  |                                |                                        | US              | EDT <sup>(1)</sup>  |                  | DL<2:0>          |       |

| bit 15           |                                |                                        |                 |                     |                  |                  | bit   |

| R/W-0            | R/W-0                          | R/W-1                                  | R/W-0           | R/C-0               | R/W-0            | R/W-0            | R/W-0 |

| SATA             | SATB                           | SATDW                                  | ACCSAT          | IPL3 <sup>(2)</sup> | PSV              | RND              | IF    |

| bit 7            | •                              | ÷                                      |                 | •                   |                  |                  | bit   |

| Legend:          |                                | C = Clear on                           | y bit           |                     |                  |                  |       |

| R = Readable     | e bit                          | W = Writable                           | bit             | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is clea | ared                           | ʻx = Bit is unk                        | nown            | U = Unimplei        | mented bit, read | d as '0'         |       |

| bit 15-13        | Unimplemen                     | ted: Read as '                         | 0'              |                     |                  |                  |       |

| bit 12           | US: DSP Mul                    | tiply Unsigned                         | Signed Contro   | ol bit              |                  |                  |       |

|                  | Ų                              | ne multiplies a<br>ne multiplies a     | Ų               |                     |                  |                  |       |

| bit 11           | EDT: Early DO                  | Loop Termina                           | ation Control b | it(1)               |                  |                  |       |

|                  | 1 = Terminate<br>0 = No effect | e executing DO                         | loop at end of  | current loop it     | eration          |                  |       |

| bit 10-8         | DL<2:0>: DO                    | Loop Nesting                           | Level Status bi | ts                  |                  |                  |       |

|                  | 111 <b>= 7</b> DO <b>lo</b>    | ops active                             |                 |                     |                  |                  |       |

|                  | •                              |                                        |                 |                     |                  |                  |       |

|                  | 001 = 1 DO lo                  | on active                              |                 |                     |                  |                  |       |

|                  | 000 = 0 DO lo                  |                                        |                 |                     |                  |                  |       |

| bit 7            | SATA: AccA                     | Saturation Ena                         | ble bit         |                     |                  |                  |       |

|                  |                                | tor A saturatio                        |                 |                     |                  |                  |       |

| bit 6            |                                | itor A saturatio<br>Saturation Ena     |                 |                     |                  |                  |       |

|                  |                                | tor B saturatio                        |                 |                     |                  |                  |       |

|                  |                                | itor B saturatio                       |                 |                     |                  |                  |       |

| bit 5            | SATDW: Data                    | a Space Write                          | from DSP Eng    | ine Saturation      | Enable bit       |                  |       |

|                  |                                | ce write satura<br>ce write satura     |                 |                     |                  |                  |       |

| bit 4            | -                              | cumulator Satu                         |                 | elect bit           |                  |                  |       |

|                  |                                | ration (super s                        |                 |                     |                  |                  |       |

|                  |                                | ration (normal                         |                 |                     |                  |                  |       |

| bit 3            |                                | terrupt Priority                       |                 |                     |                  |                  |       |

|                  |                                | rupt priority lev<br>rupt priority lev | -               | nan 7               |                  |                  |       |

| bit 2            | PSV: Progran                   | n Space Visibil                        | ity in Data Spa | ice Enable bit      |                  |                  |       |

|                  |                                | space visible i                        |                 |                     |                  |                  |       |

| bit 1            | •                              | space not visib                        | •               | ce                  |                  |                  |       |

|                  |                                | ng Mode Seleo<br>onventional) ro       |                 | èd                  |                  |                  |       |

|                  | •                              | (convergent)                           | •               |                     |                  |                  |       |

| bit 0            | IF: Integer or                 | Fractional Mul                         | tiplier Mode Se | elect bit           |                  |                  |       |

|                  |                                | ode enabled fo<br>I mode enable        |                 |                     |                  |                  |       |

### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

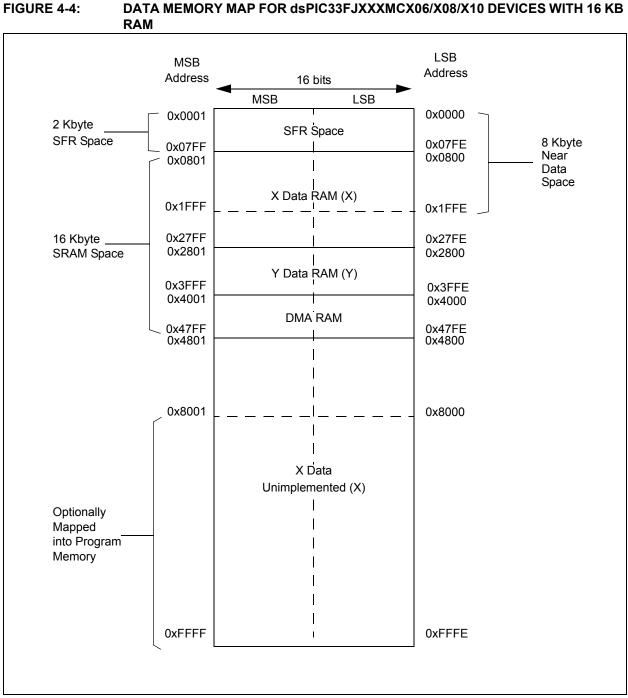

## 4.2 Data Address Space

The dsPIC33FJXXXMCX06/X08/X10 CPU has a separate 16-bit wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. Data memory maps of devices with different RAM sizes are shown in Figure 4-3 through Figure 4-5.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

dsPIC33FJXXXMCX06/X08/X10 devices implement a total of up to 30 Kbytes of data memory. Should an EA point to a location outside of this area, an all-zero word or byte will be returned.

### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes of each word have even addresses, while the Most Significant Bytes have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> microcontrollers and improve data space memory usage efficiency, the dsPIC33FJXXXMCX06/X08/X10 instruction set supports both word and byte operations. As a consequence of byte accessibility, all effective address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSb of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A sign-extend instruction (SE) is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSb of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

## 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33FJXXXMCX06/X08/X10 core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Please refer to the corresponding device tables and pinout diagrams for device-specific information.

### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area between 0x0000 and 0x1FFF is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

## DATA MEMORY MAP FOR dsPIC33FJXXXMCX06/X08/X10 DEVICES WITH 16 KB

## TABLE 4-22: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1

| File Name  | Addr          | Bit 15    | Bit 14                | Bit 13 | Bit 12 | Bit 11 | Bit 10                        | Bit 9                        | Bit 8                         | Bit 7                         | Bit 6    | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|-----------|-----------------------|--------|--------|--------|-------------------------------|------------------------------|-------------------------------|-------------------------------|----------|-------|--------|--------|--------|--------|--------|---------------|

|            | 0400-<br>041E |           | -                     | -      | -      |        |                               |                              | See definit                   | ion when V                    | VIN = x  |       | ·      |        |        | -      | -      |               |

| C1BUFPNT1  | 0420          |           | F3BF                  | P<3:0> |        |        | F2BF                          | P<3:0>                       |                               | F1BP<3:0> F0BP<3:0>           |          |       |        |        |        |        | 0000   |               |

| C1BUFPNT2  | 0422          |           | F7BP<3:0> F6BP<3:0>   |        |        |        |                               |                              | F5BP                          | <3:0>                         |          |       | F4BP   | <3:0>  |        | 0000   |        |               |

| C1BUFPNT3  | 0424          |           | F11B                  | P<3:0> |        |        | F10B                          | P<3:0>                       |                               |                               | F9BP     | <3:0> |        |        | F8BP   | <3:0>  |        | 0000          |

| C1BUFPNT4  | 0426          |           | F15BP<3:0> F14BP<3:0> |        |        |        |                               |                              |                               | F13BF                         | P<3:0>   |       |        | F12BF  | P<3:0> |        | 0000   |               |

| C1RXM0SID  | 0430          |           |                       |        | SID<   | 10:3>  |                               |                              |                               |                               | SID<2:0> |       | —      | MIDE   | _      | EID<'  | 17:16> | xxxx          |

| C1RXM0EID  | 0432          |           |                       |        | EID<   | 15:8>  |                               |                              |                               |                               |          |       | EID<   | 7:0>   | _      | -      |        | xxxx          |

| C1RXM1SID  | 0434          |           | SID<10:3>             |        |        |        |                               |                              |                               | SID<2:0>                      |          | —     | MIDE   | _      | EID<   | 17:16> | xxxx   |               |

| C1RXM1EID  | 0436          |           | EID<15:8>             |        |        |        |                               |                              |                               |                               |          | EID<  | 7:0>   |        |        |        | xxxx   |               |

| C1RXM2SID  | 0438          |           | SID<10:3>             |        |        |        |                               | SID<2:0> — MIDE — EID<17:16> |                               |                               |          |       |        | 17:16> | xxxx   |        |        |               |

| C1RXM2EID  | 043A          | EID<15:8> |                       |        |        |        |                               |                              |                               | EID<                          | 7:0>     | _     | -      |        | xxxx   |        |        |               |

| C1RXF0SID  | 0440          | SID<10:3> |                       |        |        |        | SID<2:0> — EXIDE — EID<17:16> |                              |                               |                               |          |       | 17:16> | xxxx   |        |        |        |               |

| C1RXF0EID  | 0442          |           | EID<15:8>             |        |        |        |                               |                              |                               |                               | EID<     | 7:0>  | _      | -      |        | xxxx   |        |               |

| C1RXF1SID  | 0444          |           | SID<10:3>             |        |        |        |                               |                              | SID<2:0>                      |                               | —        | EXIDE | _      | EID<   | 17:16> | xxxx   |        |               |

| C1RXF1EID  | 0446          |           | EID<15:8>             |        |        |        |                               |                              |                               |                               | EID<     | 7:0>  | _      | -      |        | xxxx   |        |               |

| C1RXF2SID  | 0448          |           |                       |        | SID<   | 10:3>  |                               |                              |                               |                               | SID<2:0> |       | —      | EXIDE  | _      | EID<   | 17:16> | xxxx          |

| C1RXF2EID  | 044A          |           |                       |        | EID<   | 15:8>  |                               |                              |                               |                               |          |       | EID<   | 7:0>   |        | •      |        | xxxx          |

| C1RXF3SID  | 044C          |           |                       |        | SID<   | :10:3> |                               |                              |                               | SID<2:0> — EXIDE — EID<17:16> |          |       |        |        | 17:16> | xxxx   |        |               |

| C1RXF3EID  | 044E          |           |                       |        | EID<   | 15:8>  |                               |                              |                               | EID<7:0>                      |          |       |        |        |        |        | xxxx   |               |

| C1RXF4SID  | 0450          |           |                       |        | SID<   | :10:3> |                               |                              |                               | SID<2:0> — EXIDE — EID<17:16> |          |       |        |        |        | 17:16> | xxxx   |               |

| C1RXF4EID  | 0452          |           |                       |        | EID<   | 15:8>  |                               |                              |                               | EID<7:0>                      |          |       |        |        |        |        | xxxx   |               |

| C1RXF5SID  | 0454          |           |                       |        | SID<   | :10:3> |                               |                              |                               | SID<2:0> — EXIDE — EID<17:16> |          |       |        |        |        | 17:16> | xxxx   |               |

| C1RXF5EID  | 0456          |           |                       |        | EID<   | :15:8> |                               |                              |                               |                               |          |       | EID<   | 7:0>   |        |        |        | xxxx          |

| C1RXF6SID  | 0458          |           |                       |        | SID<   | :10:3> |                               |                              |                               |                               | SID<2:0> |       | —      | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |           |                       |        | EID<   | 15:8>  |                               |                              |                               |                               |          |       | EID<   | 7:0>   |        |        |        | xxxx          |

| C1RXF7SID  | 045C          |           |                       |        | SID<   | :10:3> |                               |                              |                               |                               | SID<2:0> |       | —      | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |           |                       |        | EID<   | 15:8>  |                               |                              |                               |                               |          |       | EID<   | 7:0>   |        |        |        | xxxx          |

| C1RXF8SID  | 0460          |           | SID<10:3>             |        |        |        |                               |                              | SID<2:0> — EXIDE — EID<17:16> |                               |          |       |        | 17:16> | xxxx   |        |        |               |

| C1RXF8EID  | 0462          |           | EID<15:8>             |        |        |        |                               |                              |                               | EID<7:0>                      |          |       |        |        |        |        | xxxx   |               |

| C1RXF9SID  | 0464          |           |                       |        | SID<   | 10:3>  |                               |                              |                               | SID<2:0> — EXIDE — EID<17:16> |          |       |        |        | 17:16> | xxxx   |        |               |

| C1RXF9EID  | 0466          |           |                       |        | EID<   | 15:8>  |                               |                              |                               | EID<7:0>                      |          |       |        |        |        | xxxx   |        |               |

| C1RXF10SID | 0468          |           |                       |        | SID<   | 10:3>  |                               |                              |                               | SID<2:0> — EXIDE — EID<17:16> |          |       |        |        | 17:16> | xxxx   |        |               |

| C1RXF10EID | 046A          |           |                       |        | EID<   | 15:8>  |                               |                              |                               |                               |          |       | EID<   | 7:0>   |        |        |        | xxxx          |

dsPIC33FJXXXMCX06/X08/X10

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-22: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1(CONTINUED)

| File Name  | Addr | Bit 15    | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                      | Bit 7                         | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------|------|-----------|-----------|--------|--------|--------|--------|-------|----------------------------|-------------------------------|----------|-------|-------|-------|-------|-------|-------|---------------|

| C1RXF11SID | 046C |           |           |        | SID<   | 10:3>  |        |       |                            |                               | SID<2:0> | •     | _     | EXIDE | —     | EID<1 | 7:16> | xxxx          |

| C1RXF11EID | 046E |           |           |        | EID<   | 15:8>  |        |       |                            |                               |          |       | EID<  | 7:0>  |       |       |       | xxxx          |

| C1RXF12SID | 0470 |           | SID<10:3> |        |        |        |        |       |                            | SID<2:0> — EXIDE — EID<17:16> |          |       |       |       | 7:16> | xxxx  |       |               |

| C1RXF12EID | 0472 |           | EID<15:8> |        |        |        |        |       |                            |                               |          |       | EID<  | 7:0>  |       |       |       | xxxx          |

| C1RXF13SID | 0474 |           |           |        | SID<   | 10:3>  |        |       |                            |                               | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C1RXF13EID | 0476 |           |           |        | EID<   | 15:8>  |        |       |                            |                               |          |       | EID<  | 7:0>  |       |       |       | xxxx          |

| C1RXF14SID | 0478 |           |           |        | SID<   | 10:3>  |        |       |                            |                               | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A | EID<15:8> |           |        |        |        |        |       | EID<7:0>                   |                               |          |       |       |       | xxxx  |       |       |               |

| C1RXF15SID | 047C | SID<10:3> |           |        |        |        |        |       | SID<2:0> — EXIDE — EID<17: |                               |          |       |       | 7:16> | xxxx  |       |       |               |

| C1RXF15EID | 047E |           |           |        | EID<   | 15:8>  |        |       |                            | EID<7:0>                      |          |       |       |       |       | xxxx  |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 6.** "Interrupts" (DS70184) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The interrupt controller for the dsPIC33FJXXXMCX06/ X08/X10 family of devices reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33FJXXXMCX06/X08/X10 CPU. It has the following features:

- Up to eight processor exceptions and software traps

- Seven user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- · Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 7-1. The IVT resides in program memory, starting at location 000004h. The IVT contains 126 vectors consisting of eight nonmaskable trap vectors plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this priority is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with vector 0 will take priority over interrupts at any other vector address.

The dsPIC33FJXXXMCX06/X08/X10 family of devices implement up to 67 unique interrupts and five nonmaskable traps. These are summarized in Table 7-1 and Table 7-2.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33FJXXXMCX06/X08/X10 device clears its registers in response to a Reset, which forces the PC to zero. The digital signal controller then begins program execution at location 0x000000. The user programs a GOTO instruction at the Reset address, which redirects program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| U-0           | R/W-0           | R/W-0                           | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|-----------------|---------------------------------|----------------|------------------|------------------|-----------------|--------|

|               | DMA1IE          | AD1IE                           | U1TXIE         | U1RXIE           | SPI1IE           | SPI1EIE         | T3IE   |

| bit 15        |                 | ·                               |                |                  | •                | ÷               | bit 8  |

| R/W-0         | R/W-0           | R/W-0                           | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| T2IE          | OC2IE           | IC2IE                           | DMA0IE         | T1IE             | OC1IE            | IC1IE           | INTOIE |

| bit 7         | UC2IE           | ICZIE                           | DIVIAULE       |                  | OCTIE            | ICTIE           | bit 0  |

| Legend:       |                 |                                 |                |                  |                  |                 |        |

| R = Readable  | e bit           | W = Writable                    | bit            | U = Unimpler     | mented bit, read | d as '0'        |        |

| -n = Value at |                 | '1' = Bit is set                |                | '0' = Bit is cle |                  | x = Bit is unkr | iown   |

| iii valao at  |                 | 1 Bitle co                      | •              | o Dicio dia      |                  |                 |        |

| bit 15        | Unimplemen      | ted: Read as '                  | 0'             |                  |                  |                 |        |

| bit 14        | DMA1IE: DM      | A Channel 1 D                   | ata Transfer C | Complete Interi  | rupt Enable bit  |                 |        |

|               |                 | equest enable                   |                |                  |                  |                 |        |

|               |                 | equest not en                   |                |                  |                  |                 |        |

| bit 13        |                 |                                 |                | rupt Enable bit  |                  |                 |        |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |        |

| bit 12        | •               | RT1 Transmitte                  |                | able bit         |                  |                 |        |

|               |                 | equest enable                   | •              |                  |                  |                 |        |

|               | 0 = Interrupt r | equest not en                   | abled          |                  |                  |                 |        |

| bit 11        |                 | RT1 Receiver I                  | •              | le bit           |                  |                 |        |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |        |

| bit 10        | -               | Event Interrup                  |                |                  |                  |                 |        |

|               |                 | equest enable                   |                |                  |                  |                 |        |

|               |                 | equest not en                   |                |                  |                  |                 |        |

| bit 9         | SPI1EIE: SPI    | 1 Error Interru                 | pt Enable bit  |                  |                  |                 |        |

|               |                 | equest enable                   |                |                  |                  |                 |        |

|               | •               | equest not en                   |                |                  |                  |                 |        |

| bit 8         |                 | Interrupt Enab                  |                |                  |                  |                 |        |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |        |

| bit 7         | -               | Interrupt Enab                  |                |                  |                  |                 |        |

|               |                 | equest enable                   |                |                  |                  |                 |        |

|               | 0 = Interrupt r | equest not en                   | abled          |                  |                  |                 |        |

| bit 6         | •               | ut Compare Ch                   |                | upt Enable bit   |                  |                 |        |

|               |                 | equest enable                   |                |                  |                  |                 |        |

| bit 5         | •               | equest not en<br>Capture Chann  |                | Enabla bit       |                  |                 |        |

| DIL 5         | •               | equest enable                   | •              |                  |                  |                 |        |

|               |                 | request not en                  |                |                  |                  |                 |        |

| bit 4         | DMA0IE: DM      | A Channel 0 D                   | ata Transfer C | Complete Interi  | rupt Enable bit  |                 |        |

|               |                 | equest enable                   |                |                  |                  |                 |        |

|               |                 | equest not en                   |                |                  |                  |                 |        |

| bit 3         |                 | Interrupt Enab                  |                |                  |                  |                 |        |

|               |                 | equest enable<br>equest not en  |                |                  |                  |                 |        |

|               |                 |                                 |                |                  |                  |                 |        |

### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 3 | CNIE: Input Change Notification Interrupt Enable bit |

|-------|------------------------------------------------------|

|       | 1 = Interrupt request enabled                        |

|       | 0 = Interrupt request not enabled                    |

| bit 2 | Unimplemented: Read as '0'                           |

| bit 1 | MI2C1IE: I2C1 Master Events Interrupt Enable bit     |

|       | 1 = Interrupt request enabled                        |

|       | 0 = Interrupt request not enabled                    |

|       |                                                      |

- bit 0 SI2C1IE: I2C1 Slave Events Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

### REGISTER 8-3: DMAXSTA: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER A

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STA   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STA   | <7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

#### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>            |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimplen      | nented bit, rea | id as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unki | nown  |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

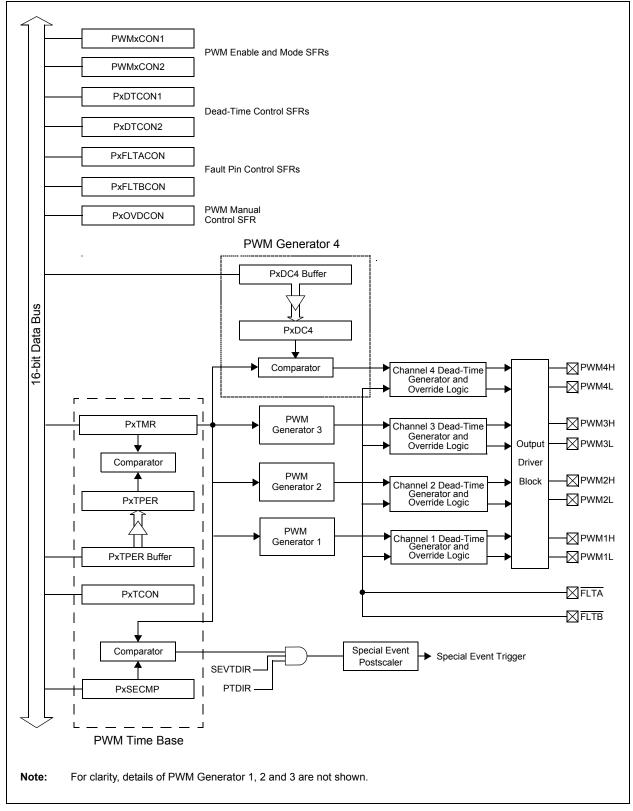

## 16.0 MOTOR CONTROL PWM MODULE

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 14. "Motor Control PWM" (DS70187) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

This module simplifies the task of generating multiple, synchronized Pulse-Width Modulated (PWM) outputs. In particular, the following power and motion control applications are supported by the PWM module:

- · 3-Phase AC Induction Motor

- Switched Reluctance (SR) Motor

- Brushless DC (BLDC) Motor

- Uninterruptible Power Supply (UPS)

- The PWM module has the following features:

- Eight PWM I/O pins with four duty cycle generators

- Up to 16-bit resolution

- 'On-the-fly' PWM frequency changes

- · Edge and Center-Aligned Output modes

- · Single Pulse Generation mode

- Interrupt support for asymmetrical updates in Center-Aligned mode

- Output override control for Electrically Commutative Motor (ECM) operation

- 'Special Event' comparator for scheduling other peripheral events

- Fault pins to optionally drive each of the PWM output pins to a defined state

- Duty cycle updates are configurable to be immediate or synchronized to the PWM time base

This module contains four duty cycle generators, numbered 1 through 4. The module has eight PWM output pins, numbered PWM1H/PWM1L through PWM4H/PWM4L. The eight I/O pins are grouped into high/low numbered pairs, denoted by the suffix H or L, respectively. For complementary loads, the low PWM pins are always the complement of the corresponding high I/O pin.

The PWM module allows several modes of operation which are beneficial for specific power control applications.

## FIGURE 16-1: PWM MODULE BLOCK DIAGRAM

NOTES:

## 21.0 ENHANCED CAN (ECAN™) MODULE

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70185) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

## 21.1 Overview

The Enhanced Controller Area Network (ECAN<sup>™</sup>) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33FJXXXMCX06/X08/X10 devices contain up to two ECAN modules.

The CAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH specification. The module will support CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader may refer to the BOSCH CAN specification for further details.

The module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to eight transmit buffers with application specified prioritization and abort capability (each buffer may contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer may contain up to 8 bytes of data)

- Up to 16 full (standard/extended identifier) acceptance filters

- · Three full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- Programmable clock source

- Programmable link to input capture module (IC2 for both CAN1 and CAN2) for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

## 21.2 Frame Types

The CAN module transmits various types of frames which include data messages, or remote transmission requests initiated by the user, as other frames that are automatically generated for control purposes. The following frame types are supported:

· Standard Data Frame:

A standard data frame is generated by a node when the node wishes to transmit data. It includes an 11-bit Standard Identifier (SID), but not an 18-bit Extended Identifier (EID).

· Extended Data Frame:

An extended data frame is similar to a standard data frame, but includes an extended identifier as well.

· Remote Frame:

It is possible for a destination node to request the data from the source. For this purpose, the destination node sends a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node will then send a data frame as a response to this remote request.

Error Frame:

An error frame is generated by any node that detects a bus error. An error frame consists of two fields: an error flag field and an error delimiter field.

· Overload Frame:

An overload frame can be generated by a node as a result of two conditions. First, the node detects a dominant bit during interframe space which is an illegal condition. Second, due to internal conditions, the node is not yet able to start reception of the next message. A node may generate a maximum of 2 sequential overload frames to delay the start of the next message.

• Interframe Space:

Interframe space separates a proceeding frame (of whatever type) from a following data or remote frame.

## **REGISTER 21-9:** CiCFG1: ECAN<sup>™</sup> BAUD RATE CONFIGURATION REGISTER 1

| U-0           | U-0                            | U-0                             | U-0        | U-0              | U-0              | U-0             | U-0   |

|---------------|--------------------------------|---------------------------------|------------|------------------|------------------|-----------------|-------|

| _             | —                              | _                               | _          | _                | _                | _               | _     |

| bit 15        |                                |                                 |            |                  |                  |                 | bit 8 |

|               |                                |                                 |            |                  |                  |                 |       |

| R/W-0         | R/W-0                          | R/W-0                           | R/W-0      | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| SJ\           | V<1:0>                         |                                 |            | BRF              | P<5:0>           |                 |       |

| bit 7         |                                |                                 |            |                  |                  |                 | bit 0 |

|               |                                |                                 |            |                  |                  |                 |       |

| Legend:       |                                |                                 |            |                  |                  |                 |       |

| R = Readabl   | e bit                          | W = Writable                    | bit        | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at | POR                            | '1' = Bit is set                |            | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|               |                                |                                 |            |                  |                  |                 |       |

| bit 15-8      | Unimplemen                     | ted: Read as '                  | 0'         |                  |                  |                 |       |

| bit 7-6       | <b>SJW&lt;1:0&gt;:</b> S       | synchronization                 | Jump Width | bits             |                  |                 |       |

|               | 11 = Length i                  |                                 |            |                  |                  |                 |       |

|               | 10 = Length i<br>01 = Length i |                                 |            |                  |                  |                 |       |

|               | 00 = Length is                 |                                 |            |                  |                  |                 |       |

| bit 5-0       | C C                            | Baud Rate Pres                  | caler bits |                  |                  |                 |       |

|               | 11 1111 <b>= T</b>             | Q = 2 x 64 x 1/                 | FCAN       |                  |                  |                 |       |

|               | •                              |                                 |            |                  |                  |                 |       |

|               | •                              |                                 |            |                  |                  |                 |       |

|               | •                              |                                 |            |                  |                  |                 |       |

|               |                                | $Q = 2 \times 3 \times 1/F_{0}$ |            |                  |                  |                 |       |

|               |                                | $Q = 2 \times 2 \times 1/F_{0}$ |            |                  |                  |                 |       |

|               | 00 0000 = 1                    | $Q = 2 \times 1 \times 1/Fc$    | CAN        |                  |                  |                 |       |

## REGISTER 21-10: CiCFG2: ECAN™ BAUD RATE CONFIGURATION REGISTER 2

| U-0    | R/W-x  | U-0 | U-0 | U-0 | R/W-x | R/W-x       | R/W-x |

|--------|--------|-----|-----|-----|-------|-------------|-------|

| —      | WAKFIL | —   | _   | —   | :     | SEG2PH<2:0> |       |

| bit 15 |        |     |     |     |       |             | bit 8 |

| R/W-x    | R/W-x | R/W-x | R/W-x       | R/W-x | R/W-x | R/W-x      | R/W-x |

|----------|-------|-------|-------------|-------|-------|------------|-------|

| SEG2PHTS | SAM   | :     | SEG1PH<2:0> |       |       | PRSEG<2:0> |       |

| bit 7    |       |       |             |       |       |            | bit 0 |

| R = Readable bit W = Writable bit |                                           | U = Unimplemented bit,                                   | U = Unimplemented bit, read as '0' |                         |  |  |  |

|-----------------------------------|-------------------------------------------|----------------------------------------------------------|------------------------------------|-------------------------|--|--|--|

| -n = Value at POR                 |                                           | '1' = Bit is set                                         | '0' = Bit is cleared               | x = Bit is unknow       |  |  |  |

| bit 15                            | Unimpleme                                 | ented: Read as '0'                                       |                                    |                         |  |  |  |

| bit 14                            |                                           | elect CAN bus Line Filter<br>N bus line filter for wake- |                                    |                         |  |  |  |

|                                   |                                           | is line filter is not used for                           | -                                  |                         |  |  |  |

| bit 13-11                         | Unimpleme                                 | Unimplemented: Read as '0'                               |                                    |                         |  |  |  |

| bit 10-8                          | SEG2PH<2:0>: Phase Buffer Segment 2 bits  |                                                          |                                    |                         |  |  |  |

|                                   | 111 = Leng<br>000 = Leng                  | th is 8 x TQ<br>th is 1 x TQ                             |                                    |                         |  |  |  |

| bit 7                             | SEG2PHTS: Phase Segment 2 Time Select bit |                                                          |                                    |                         |  |  |  |

|                                   | • •                                       | programmable<br>im of SEG1PH bits or Info                | ormation Processing Time (IPT      | ), whichever is greater |  |  |  |

| bit 6                             | SAM: Sam                                  | ole of the CAN bus Line b                                | it                                 |                         |  |  |  |

|                                   |                                           | e is sampled three times a<br>e is sampled once at the s |                                    |                         |  |  |  |

| bit 5-3                           | SEG1PH<2:0>: Phase Buffer Segment 1 bits  |                                                          |                                    |                         |  |  |  |

|                                   | -                                         | th is 8 x Tq<br>th is 1 x Tq                             |                                    |                         |  |  |  |

| bit 2-0                           | PRSEG<2:                                  | 0>: Propagation Time Seg                                 | gment bits                         |                         |  |  |  |

|                                   | 0                                         | th is 8 x TQ                                             |                                    |                         |  |  |  |

|                                   | 000 = Leng                                | th is 1 x Tq                                             |                                    |                         |  |  |  |

## REGISTER 21-19: CiFMSKSEL2: ECAN™ FILTER 15-8 MASK SELECTION REGISTER

| R/W-0<br>F15MSK<<br>bit 15<br>R/W-0<br>F11MSK<<br>bit 7 | R/W-0                                                                                     | R/W-0<br>F14MS<br>R/W-0<br>F10MS                                                     | R/W-0                                                                                                          | R/W-0<br>F13MS<br>R/W-0<br>F9MSł   | R/W-0                  | R/W-0<br>F12MSI<br>R/W-0 | R/W-0<br>K<1:0><br>bit 8<br>R/W-0 |  |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------|--------------------------|-----------------------------------|--|

| bit 15<br>R/W-0<br>F11MSK<<br>bit 7                     | R/W-0                                                                                     | R/W-0                                                                                | R/W-0                                                                                                          | R/W-0                              | R/W-0                  | R/W-0                    | bit 8                             |  |

| R/W-0<br>F11MSK<<br>bit 7                               |                                                                                           |                                                                                      |                                                                                                                |                                    |                        |                          |                                   |  |

| F11MSK<<br>bit 7                                        |                                                                                           |                                                                                      |                                                                                                                |                                    |                        |                          | R/W-0                             |  |

| F11MSK<<br>bit 7                                        |                                                                                           |                                                                                      |                                                                                                                |                                    |                        |                          | R/W-0                             |  |

| bit 7                                                   | <1:0>                                                                                     | F10MS                                                                                | K<1:0>                                                                                                         | F9MSł                              | (-1:0>                 |                          |                                   |  |

|                                                         |                                                                                           |                                                                                      |                                                                                                                |                                    | <u>\<u></u>\.U&gt;</u> | F8MSK<1:0>               |                                   |  |

|                                                         |                                                                                           |                                                                                      |                                                                                                                |                                    |                        |                          | bit 0                             |  |

|                                                         |                                                                                           |                                                                                      |                                                                                                                |                                    |                        |                          |                                   |  |

| Legend:                                                 |                                                                                           |                                                                                      |                                                                                                                |                                    |                        |                          |                                   |  |

| R = Readable bit                                        |                                                                                           | W = Writable bit                                                                     |                                                                                                                | U = Unimplemented bit, read as '0' |                        |                          |                                   |  |

| -n = Value at POR                                       |                                                                                           | '1' = Bit is set                                                                     |                                                                                                                | '0' = Bit is clea                  | ared                   | x = Bit is unknown       |                                   |  |

| bit 13-12 F<br>bit 11-10 F                              | 11 = Reserve<br>10 = Acceptar<br>11 = Acceptar<br>10 = Acceptar<br>14MSK<1:0<br>13MSK<1:0 | nce Mask 2 reg<br>nce Mask 1 reg<br>nce Mask 0 reg<br>>: Mask Sourc<br>>: Mask Sourc | gisters contain<br>gisters contain<br>gisters contain<br>gisters contain<br>e for Filter 14<br>e for Filter 13 | n mask<br>n mask                   | s as bit 15-14)        |                          |                                   |  |

bit 7-6F11MSK<1:0>: Mask Source for Filter 11 bit (same values as bit 15-14)bit 5-4F10MSK<1:0>: Mask Source for Filter 10 bit (same values as bit 15-14)

bit 3-2 **F9MSK<1:0>:** Mask Source for Filter 9 bit (same values as bit 15-14)

bit 1-0 **F8MSK<1:0>:** Mask Source for Filter 8 bit (same values as bit 15-14)

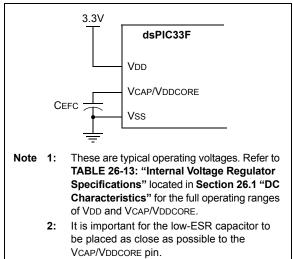

## 23.2 On-Chip Voltage Regulator

All of the dsPIC33FJXXXMCX06/X08/X10 devices power their core digital logic at a nominal 2.5V. This may create an issue for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJXXXMCX06/X08/X10 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. The regulator requires that a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) be connected to the VCAP/VDDCORE pin (Figure 23-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 26-13 of **Section 26.1** "**DC Characteristics**".

| Note: | It is important for the low-ESR capacitor to |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|

|       | be placed as close as possible to the        |  |  |  |  |  |

|       | VCAP/VDDCORE pin.                            |  |  |  |  |  |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 23-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1)</sup>

## 23.3 BOR: Brown-Out Reset

The BOR (Brown-out Reset) module is based on an internal voltage reference circuit that monitors the regulated supply voltage VCAP/VDDCORE. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (i.e., missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR will generate a Reset pulse which will reset the device. The BOR will select the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>). Furthermore, if an oscillator mode is selected, the BOR will activate the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, then the clock will be held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) will be set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and will reset the device should VDD fall below the BOR threshold voltage.

## 26.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC33FJXXXMCX06/X08/X10 AC characteristics and timing parameters.

#### TABLE 26-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V                                 |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------|--|--|--|--|

|                    | (unless otherwise stated)                                                   |  |  |  |  |

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |  |  |  |  |

|                    | Operating voltage VDD range as described in Section 26.0 "Electrical        |  |  |  |  |

|                    | Characteristics".                                                           |  |  |  |  |

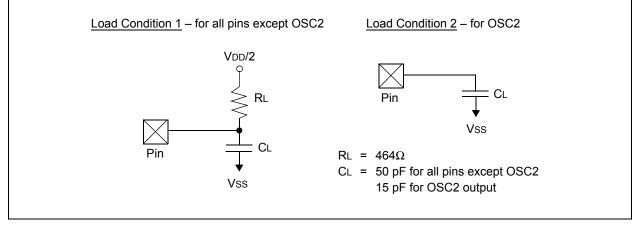

### FIGURE 26-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 26-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Тур | Мах | Units | Conditions                                                         |

|--------------|--------|-----------------------|-----|-----|-----|-------|--------------------------------------------------------------------|

| DO50         | Cosc2  | OSC2/SOSC2 pin        | _   | _   | 15  |       | In XT and HS modes when<br>external clock is used to drive<br>OSC1 |

| DO56         | Cio    | All I/O pins and OSC2 | —   | —   | 50  | pF    | EC mode                                                            |

| DO58         | Св     | SCLx, SDAx            |     | —   | 400 | pF    | In I <sup>2</sup> C™ mode                                          |

NOTES:

Modes of Operation

## F

| Flash Program Memory                                       |            |

|------------------------------------------------------------|------------|

| Control Registers                                          |            |

| Operations                                                 |            |

| Programming Algorithm                                      |            |

| RTSP Operation<br>Table Instructions                       |            |

| Flexible Configuration                                     |            |

| FSCM                                                       | 200        |

| Delay for Crystal and PLL Clock Sources                    |            |

| Device Resets                                              |            |

| 1                                                          |            |

|                                                            |            |

| I/O Ports                                                  |            |

| Parallel I/O (PIO)                                         |            |

| Write/Read Timing                                          | 102        |

| Addresses                                                  | 202        |

| Operating Modes                                            |            |

| Registers                                                  |            |

| I <sup>2</sup> C Module                                    |            |

| I2C1 Register Map                                          |            |

| I2C2 Register Map                                          |            |

| In-Circuit Debugger                                        |            |

| In-Circuit Emulation                                       |            |

| In-Circuit Serial Programming (ICSP)                       | . 253, 260 |

| Input Capture                                              |            |

| Registers                                                  |            |

| Input Change Notification Module                           |            |

| Instruction Addressing Modes<br>File Register Instructions |            |

| Fundamental Modes Supported                                |            |

| MAC Instructions                                           |            |

| MCU Instructions                                           |            |

| Move and Accumulator Instructions                          |            |

| Other Instructions                                         |            |

| Instruction Set                                            |            |

| Overview                                                   |            |

| Summary                                                    |            |

| Instruction-Based Power-Saving Modes                       |            |

| Idle                                                       |            |

| Sleep                                                      |            |

| Internal RC Oscillator<br>Use with WDT                     | 250        |

| Internet Address                                           |            |

| Interrupt Control and Status Registers                     |            |

| IECx                                                       |            |

| IFSx                                                       |            |

| INTCON1                                                    |            |

| INTCON2                                                    |            |

| IPCx                                                       |            |

| Interrupt Setup Procedures                                 |            |

| Initialization                                             |            |

| Interrupt Disable                                          |            |

| Interrupt Service Routine<br>Trap Service Routine          |            |

| Interrupt Vector Table (IVT)                               |            |

| Interrupts Coincident with Power Save Instructions.        |            |

|                                                            |            |

| J                                                          |            |

| JTAG Boundary Scan Interface                               |            |

| Μ                                                          |            |

|                                                            | o-         |

| Memory Organization                                        |            |

| Microchip Internet Web Site                                | 335        |

Power-Saving Features ...... 153 Clock Frequency and Switching ...... 153 Data Access from Program Memory Using Program Data Access from Program Memory Using Table Instructions ...... 70 Data Access from, Address Generation ...... 69 Memory Map...... 35