Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 30K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256mc710-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Pin Diagrams (Continued)

| TABLE 1-1:     PINOUT I/O DESCRIPTIONS (CONTINUED)                                                                                              |                                                        |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                                                                                                        | Pin<br>Type                                            | Buffer<br>Type                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| RA0-RA7                                                                                                                                         | I/O                                                    | ST                                                               | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RA9-RA10                                                                                                                                        | I/O                                                    | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RA12-RA15                                                                                                                                       | I/O                                                    | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RB0-RB15                                                                                                                                        | I/O                                                    | ST                                                               | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RC1-RC4                                                                                                                                         | I/O                                                    | ST                                                               | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RC12-RC15                                                                                                                                       | I/O                                                    | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RD0-RD15                                                                                                                                        | I/O                                                    | ST                                                               | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RE0-RE9                                                                                                                                         | I/O                                                    | ST                                                               | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RF0-RF8                                                                                                                                         | I/O                                                    | ST                                                               | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RF12-RF13                                                                                                                                       |                                                        | _                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RG0-RG3                                                                                                                                         | I/O                                                    | ST                                                               | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RG6-RG9                                                                                                                                         | I/O                                                    | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RG12-RG15                                                                                                                                       | I/O                                                    | ST                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| SCK1                                                                                                                                            | I/O                                                    | ST                                                               | Synchronous serial clock input/output for SPI1.                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| SDI1                                                                                                                                            | I                                                      | ST                                                               | SPI1 data in.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| SDO1                                                                                                                                            | 0                                                      | _                                                                | SPI1 data out.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SS1                                                                                                                                             | I/O                                                    | ST                                                               | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SCK2                                                                                                                                            | I/O                                                    | ST                                                               | Synchronous serial clock input/output for SPI2.                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| SDI2                                                                                                                                            | I                                                      | ST                                                               | SPI2 data in.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| SDO2                                                                                                                                            | 0                                                      | -                                                                | SPI2 data out.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SS2                                                                                                                                             | I/O                                                    | ST                                                               | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SCL1                                                                                                                                            | I/O                                                    | ST                                                               | Synchronous serial clock input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| SDA1                                                                                                                                            | I/O                                                    | ST                                                               | Synchronous serial data input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SCL2                                                                                                                                            | I/O                                                    | ST                                                               | Synchronous serial clock input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| SDA2                                                                                                                                            | I/O                                                    | ST                                                               | Synchronous serial data input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SOSCI                                                                                                                                           |                                                        | ST/CMOS                                                          | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SOSCO                                                                                                                                           | 0                                                      |                                                                  | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| TMS                                                                                                                                             | I                                                      | ST                                                               | JTAG Test mode select pin.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| TCK                                                                                                                                             | I                                                      | ST                                                               | JTAG test clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| TDI                                                                                                                                             |                                                        | ST                                                               | JTAG test data input pin.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| TDO                                                                                                                                             | 0                                                      | —                                                                | JTAG test data output pin.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| T1CK                                                                                                                                            |                                                        |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                                                                                                                                                 | I                                                      | ST                                                               | Timer1 external clock input.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| T2CK                                                                                                                                            |                                                        | ST                                                               | Timer2 external clock input.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| T2CK<br>T3CK                                                                                                                                    |                                                        | ST<br>ST                                                         | Timer2 external clock input.<br>Timer3 external clock input.                                                                                                                                                                                                                                                                                                                                                               |  |  |

| T2CK<br>T3CK<br>T4CK                                                                                                                            |                                                        | ST<br>ST<br>ST                                                   | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                                                                                                                                                                                                                               |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK                                                                                                                    |                                                        | ST<br>ST<br>ST<br>ST                                             | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.                                                                                                                                                                                                                                                                                               |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK                                                                                                            |                                                        | ST<br>ST<br>ST<br>ST<br>ST                                       | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.                                                                                                                                                                                                                                                               |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK                                                                                                    |                                                        | ST<br>ST<br>ST<br>ST<br>ST<br>ST                                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.                                                                                                                                                                                                                               |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK                                                                                            |                                                        | ST<br>ST<br>ST<br>ST<br>ST<br>ST                                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.                                                                                                                                                                                               |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK                                                                                    |                                                        | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                           | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.                                                                                                                                                               |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br><u>U1CTS</u>                                                                    |                                                        | ST<br>ST<br>ST<br>ST<br>ST<br>ST                                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.                                                                                                                                       |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br><u>U1CTS</u><br>U1RTS                                                           |                                                        | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.                                                                                                                                                               |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX                                                 | <br> <br> <br> <br> <br> <br> <br> <br> <br>           | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                           | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.                                                                                                               |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX                                         | <br> <br> <br> <br> <br> <br> <br> <br> <br>           | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>                 | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.                                                                                             |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS                                | <br> | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br>       | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.<br>UART1 transmit.                                                                          |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX                        | <br> | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br>       | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 receive.                                  |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX                        |                                                        | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br> | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.                                        |  |  |

| T2CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX<br>U2TX<br>VDD |                                                        | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br> | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 receive.          |  |  |

| T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RX<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX<br>U2TX                 |                                                        | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br> | Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 receive.<br>UART2 receive.<br>UART2 transmit. |  |  |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

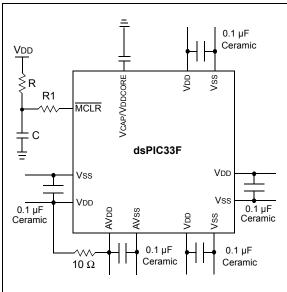

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

#### 2.3 Capacitor on Internal Voltage Regulator (VCAP/VDDCORE)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP/VDDCORE pin, which is used to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD, and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, 16V connected to ground. The type can be ceramic or tantalum. Refer to **Section 26.0** "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP/VDDCORE. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 23.2** "**On-Chip Voltage Regulator**" for details.

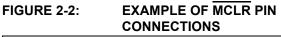

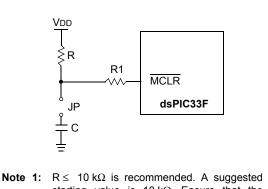

### 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- Device programming and debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

ote 1:  $R \le 10 \text{ k}\Omega$  is recommended. A suggested starting value is  $10 \text{ k}\Omega$ . Ensure that the MCLR pin VIH and VIL specifications are met.

#### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 3. "Data Memory" (DS70202) and Section 4. "Program Memory" (DS70203) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJXXXMCX06/X08/X10 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 Program Address Space

The program address memory space of the dsPIC33FJXXXMCX06/X08/X10 devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.6 "Interfacing Program and Data Memory Spaces".

User access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space. Memory usage for the dsPIC33FJXXXMCX06/X08/X10 family of devices is shown in Figure 4-1.

|                            | dsPIC33FJ64MCXXX                                   | dsPIC33FJ128MCXXX                 | dsPIC33FJ256MCXXX      |                                  |

|----------------------------|----------------------------------------------------|-----------------------------------|------------------------|----------------------------------|

| Ā                          | GOTO Instruction                                   | GOTO Instruction                  |                        | )x000000<br>)x000002             |

|                            | Reset Address                                      | Reset Address                     | - Reset Address        | )x000002                         |

|                            | Interrupt Vector Table                             | Interrupt Vector Table            | Interrupt Vector Table | 0x0000FE                         |

|                            | Reserved                                           | Reserved                          | Reserved               | 0x000100                         |

|                            | Alternate Vector Table                             | Alternate Vector Table            | Alternate vector rable | 0x000104<br>0x0001FE             |

| pace                       | User Program<br>Flash Memory<br>(22K instructions) | User Program<br>Flash Memory      | User Program           | )x000200<br>)x00ABFE             |

| User Memory Space          |                                                    | (44K instructions)                | (88K instructions)     | 0x00AC00                         |

| ser Me                     |                                                    |                                   |                        | 0x0157FE<br>0x015800             |

| Ï                          | Unimplemented<br>(Read '0's)                       | Unimplemented                     |                        | 004555                           |

|                            |                                                    | (Read 'o's)                       |                        | 0x02ABFE<br>0x02AC00             |

|                            |                                                    |                                   | Unimplemented          |                                  |

|                            |                                                    |                                   | (Read '0's)            |                                  |

| •                          |                                                    |                                   | , ,                    | x7FFFFE                          |

|                            |                                                    |                                   |                        | 0x800000                         |

|                            | Reserved                                           | Reserved                          | Reserved               |                                  |

| Space                      | Device Configuration<br>Registers                  | Device Configuration<br>Registers |                        | )xF7FFFE<br>)xF80000<br>)xF80017 |

| emory (                    |                                                    |                                   |                        | )xF80017<br>)xF80010             |

| Configuration Memory Space | Reserved                                           | Reserved                          | Reserved               |                                  |

| Config                     | · · ·                                              |                                   |                        | )xFEFFFE<br>)xFF0000             |

| ¥                          | DEVID (2)                                          | DEVID (2)                         | D = V D (2)            | )xFFFFFE                         |

| Note:                      | Memory areas are not show                          |                                   |                        |                                  |

#### FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33FJXXXMCX06/X08/X10 DEVICES

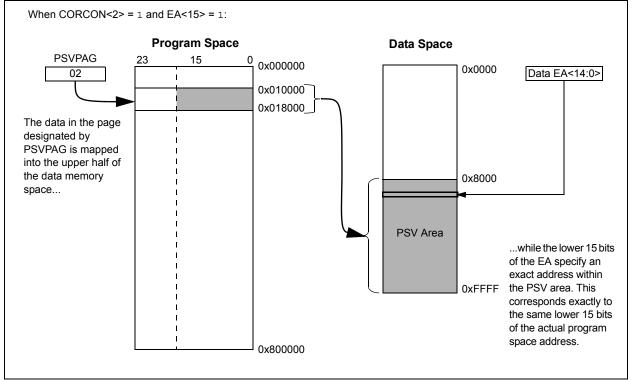

#### 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. Note that by incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

### **Note:** PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV and are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data using PSV to execute in a single cycle.

### FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                                                  | R/W-0 <sup>(1)</sup>              | U-0            | U-0                  | U-0                                 | U-0                  | U-0                  |  |  |  |  |

|-----------------------|-----------------------------------------------------------------------|-----------------------------------|----------------|----------------------|-------------------------------------|----------------------|----------------------|--|--|--|--|

| WR                    | WREN                                                                  | WRERR                             | _              | —                    | —                                   | —                    | _                    |  |  |  |  |

| bit 15                |                                                                       |                                   |                |                      |                                     |                      | bit 8                |  |  |  |  |

| U-0                   | R/W-0 <sup>(1)</sup>                                                  | U-0                               | U-0            | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> |  |  |  |  |

| _                     | ERASE                                                                 | _                                 | _              |                      |                                     | <3:0> <sup>(2)</sup> |                      |  |  |  |  |

| bit 7                 |                                                                       |                                   |                |                      |                                     |                      | bit                  |  |  |  |  |

| Legend:               |                                                                       | SO = Settable                     | only bit       |                      |                                     |                      |                      |  |  |  |  |

| R = Readable I        | bit                                                                   | W = Writable                      | -              | U = Unimpler         | mented bit, read                    | l as '0'             |                      |  |  |  |  |

| -n = Value at P       | OR                                                                    | '1' = Bit is set                  |                | '0' = Bit is cle     |                                     | x = Bit is unkr      | iown                 |  |  |  |  |

| bit 15                | WR: Write Co                                                          | ontrol bit                        |                |                      |                                     |                      |                      |  |  |  |  |

|                       | cleared b                                                             | y hardware on                     | ce operation   | is complete          | on. The operation                   | on is self-timed     | and the bit i        |  |  |  |  |

| bit 14                | 0 = Program<br>WREN: Write                                            | •                                 | tion is compl  | ete and inactive     | 2                                   |                      |                      |  |  |  |  |

| bit 14                | 1 = Enable F                                                          | lash program/e<br>ash program/er  |                |                      |                                     |                      |                      |  |  |  |  |

| bit 13                |                                                                       | te Sequence E                     | •              | 15                   |                                     |                      |                      |  |  |  |  |

| bit 13                | 1 = An impro<br>automatio                                             | per program or<br>cally on any se | erase seque    |                      | termination has                     | s occurred (bit i    | s set                |  |  |  |  |

| bit 12-7              |                                                                       |                                   | -              | pieted normally      | ·                                   |                      |                      |  |  |  |  |

| bit 6                 | Unimplemented: Read as '0'<br>ERASE: Erase/Program Enable bit         |                                   |                |                      |                                     |                      |                      |  |  |  |  |

| bit o                 | 1 = Perform t                                                         | the erase opera                   | ation specifie |                      | 3:0> on the next<br>P<3:0> on the n |                      |                      |  |  |  |  |

| bit 5-4               |                                                                       | ted: Read as '                    | •              |                      | 010 011 110 11                      |                      |                      |  |  |  |  |

| bit 3-0               | -                                                                     |                                   |                | <sub>S</sub> (2)     |                                     |                      |                      |  |  |  |  |

|                       | NVMOP<3:0>: NVM Operation Select bits <sup>(2)</sup><br>If ERASE = 1: |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | 1111 = Memory bulk erase operation                                    |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | 1110 = Reserved                                                       |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | 1101 = Erase General Segment                                          |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | 1100 = Erase Secure Segment                                           |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | 1011 = Reserved                                                       |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | 0011 = No operation<br>0010 = Memory page erase operation             |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | 0010 = Memory page erase operation<br>0001 = No operation             |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | 0000 = Erase a single Configuration register byte                     |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | If ERASE = 0:                                                         |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | 1111 = No operation                                                   |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | 1110 = Reserved<br>1101 = No operation                                |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | 1101 = NO Op<br>1100 = No op                                          |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | 1011 <b>= Rese</b>                                                    |                                   |                |                      |                                     |                      |                      |  |  |  |  |

|                       | 0011 = Memo                                                           | ory word progra                   | m operation    |                      |                                     |                      |                      |  |  |  |  |

|                       | 0010 <b>= No op</b>                                                   | peration                          |                |                      |                                     |                      |                      |  |  |  |  |

|                       |                                                                       | ory row prograr<br>am a single Co |                | egister byte         |                                     |                      |                      |  |  |  |  |

|                       |                                                                       | ly be reset on I                  |                |                      |                                     |                      |                      |  |  |  |  |

NVMCON: FLASH MEMORY CONTROL REGISTER

2: All other combinations of NVMOP<3:0> are unimplemented.

REGISTER 5-1:

| Reset Type      | Clock Source  | SYSRST Delay           | System Clock<br>Delay | FSCM<br>Delay | Notes            |

|-----------------|---------------|------------------------|-----------------------|---------------|------------------|

| POR             | EC, FRC, LPRC | TPOR + TSTARTUP + TRST | —                     | _             | 1, 2, 3          |

|                 | ECPLL, FRCPLL | TPOR + TSTARTUP + TRST | TLOCK                 | TFSCM         | 1, 2, 3, 5, 6    |

|                 | XT, HS, SOSC  | Tpor + Tstartup + Trst | Tost                  | TFSCM         | 1, 2, 3, 4, 6    |

|                 | XTPLL, HSPLL  | Tpor + Tstartup + Trst | Tost + Tlock          | TFSCM         | 1, 2, 3, 4, 5, 6 |

| BOR             | EC, FRC, LPRC | TSTARTUP + TRST        |                       | _             | 3                |

|                 | ECPLL, FRCPLL | TSTARTUP + TRST        | TLOCK                 | TFSCM         | 3, 5, 6          |

|                 | XT, HS, SOSC  | TSTARTUP + TRST        | Tost                  | TFSCM         | 3, 4, 6          |

|                 | XTPLL, HSPLL  | TSTARTUP + TRST        | Tost + Tlock          | TFSCM         | 3, 4, 5, 6       |

| MCLR            | Any Clock     | TRST                   | _                     | _             | 3                |

| WDT             | Any Clock     | Trst                   | —                     |               | 3                |

| Software        | Any Clock     | Trst                   | —                     | _             | 3                |

| Illegal Opcode  | Any Clock     | Trst                   | —                     | _             | 3                |

| Uninitialized W | Any Clock     | TRST                   | —                     | _             | 3                |

| Trap Conflict   | Any Clock     | Trst                   | —                     | _             | 3                |

#### TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

**Note 1:** TPOR = Power-on Reset delay (10  $\mu$ s nominal).

- **2:** TSTARTUP = Conditional POR delay of 20 μs nominal (if on-chip regulator is enabled) or 64 ms nominal Power-up Timer delay (if regulator is disabled). TSTARTUP is also applied to all returns from powered-down states, including waking from Sleep mode, if the regulator is enabled.

- 3: TRST = Internal state Reset time (20 µs nominal).

- **4:** Tos⊤ = Oscillator Start-up Timer. A 10-bit counter counts 1024 oscillator periods before releasing the oscillator clock to the system.

- **5**: TLOCK = PLL lock time (20  $\mu$ s nominal).

- **6**: TFSCM = Fail-Safe Clock Monitor delay (100 μs nominal).

#### 6.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) have a relatively long start-up time. Therefore, <u>one or more of the following conditions</u> is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 6.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it begins to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device automatically switches to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine.

#### 6.2.2.1 FSCM Delay for Crystal and PLL Clock Sources

When the system clock source is provided by a crystal oscillator and/or the PLL, a small delay, TFSCM, is automatically inserted after the POR and PWRT delay times. The FSCM does not begin to monitor the system clock source until this delay expires. The FSCM delay time is nominally 500  $\mu$ s and provides additional time for the oscillator and/or PLL to stabilize. In most cases, the FSCM delay prevents an oscillator failure trap at a device Reset when the PWRT is disabled.

| U-0             | R/W-0                                                                                                                     | R/W-0                                                                                                  | R/W-0                                 | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------|------------------|------------------|-----------------|--------|--|--|--|--|--|

| —               | DMA1IF                                                                                                                    | AD1IF                                                                                                  | U1TXIF                                | U1RXIF           | SPI1IF           | SPI1EIF         | T3IF   |  |  |  |  |  |

| bit 15          |                                                                                                                           |                                                                                                        |                                       |                  |                  |                 | bit 8  |  |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                     | R/W-0                                                                                                  | R/W-0                                 | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

| T2IF            | OC2IF                                                                                                                     | IC2IF                                                                                                  | DMA01IF                               | T1IF             | OC1IF            | IC1IF           | INTOIF |  |  |  |  |  |

| bit 7           |                                                                                                                           | 1                                                                                                      | 1                                     |                  |                  |                 | bit C  |  |  |  |  |  |

| Legend:         |                                                                                                                           |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

| R = Readable    | e bit                                                                                                                     | W = Writable                                                                                           | bit                                   | U = Unimpler     | mented bit, read | d as '0'        |        |  |  |  |  |  |

| -n = Value at I | POR                                                                                                                       | '1' = Bit is se                                                                                        | t                                     | '0' = Bit is cle | ared             | x = Bit is unkn | iown   |  |  |  |  |  |

| bit 15          | Unimplemen                                                                                                                | ted: Read as                                                                                           | ʻ0'                                   |                  |                  |                 |        |  |  |  |  |  |

| bit 14          | DMA1IF: DM                                                                                                                | A Channel 1 D                                                                                          | ata Transfer C                        | omplete Interr   | upt Flag Status  | bit             |        |  |  |  |  |  |

|                 | 1 = Interrupt                                                                                                             | request has oc                                                                                         | curred                                | •                |                  |                 |        |  |  |  |  |  |

|                 |                                                                                                                           | request has no                                                                                         |                                       |                  |                  |                 |        |  |  |  |  |  |

| bit 13          |                                                                                                                           |                                                                                                        | Complete Interr                       | upt Flag Statu   | s bit            |                 |        |  |  |  |  |  |

|                 | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>                    |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

| bit 12          | 0 = Interrupt request has not occurred<br>U1TXIF: UART1 Transmitter Interrupt Flag Status bit                             |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

|                 | 1 = Interrupt request has occurred                                                                                        |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

|                 | 0 = Interrupt request has not occurred                                                                                    |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

| bit 11          | U1RXIF: UART1 Receiver Interrupt Flag Status bit                                                                          |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

|                 |                                                                                                                           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                       |                  |                  |                 |        |  |  |  |  |  |

| bit 10          | SPI1IF: SPI1 Event Interrupt Flag Status bit                                                                              |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

|                 | 1 = Interrupt request has occurred                                                                                        |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

|                 | •                                                                                                                         | request has no                                                                                         |                                       |                  |                  |                 |        |  |  |  |  |  |

| bit 9           |                                                                                                                           | SPI1EIF: SPI1 Fault Interrupt Flag Status bit                                                          |                                       |                  |                  |                 |        |  |  |  |  |  |

|                 | <ol> <li>I = Interrupt request has occurred</li> <li>Interrupt request has not occurred</li> </ol>                        |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

| bit 8           | •                                                                                                                         | •                                                                                                      |                                       |                  |                  |                 |        |  |  |  |  |  |

| bit 0           | <b>T3IF:</b> Timer3 Interrupt Flag Status bit<br>1 = Interrupt request has occurred                                       |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

|                 | 0 = Interrupt request has not occurred                                                                                    |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

| bit 7           | T2IF: Timer2 Interrupt Flag Status bit                                                                                    |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

|                 | 1 = Interrupt request has occurred                                                                                        |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

| bit 6           | <ul> <li>Interrupt request has not occurred</li> <li>OC2IF: Output Compare Channel 2 Interrupt Flag Status bit</li> </ul> |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

|                 | -                                                                                                                         | request has oc                                                                                         |                                       | ipi riay Sialus  | S DIL            |                 |        |  |  |  |  |  |

|                 |                                                                                                                           | request has no                                                                                         |                                       |                  |                  |                 |        |  |  |  |  |  |

| bit 5           | IC2IF: Input Capture Channel 2 Interrupt Flag Status bit                                                                  |                                                                                                        |                                       |                  |                  |                 |        |  |  |  |  |  |

|                 |                                                                                                                           | request has oc<br>request has no                                                                       |                                       |                  |                  |                 |        |  |  |  |  |  |