Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 30K x 8                                                                           |

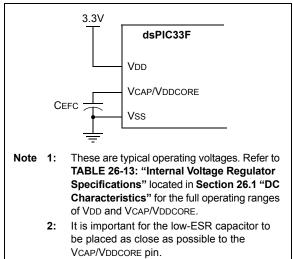

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

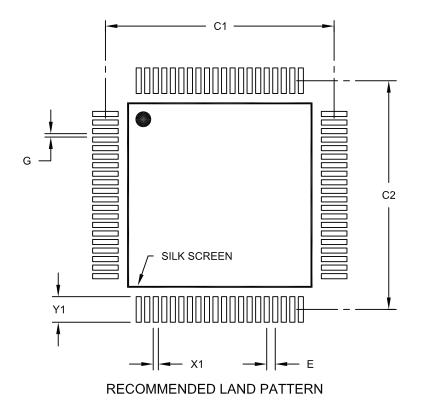

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256mc710t-i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name    | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                       |

|-------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN31    | I           | Analog         | Analog input channels.                                                                                                                                                            |

| AVDD        | Р           | Р              | Positive supply for analog modules. This pin must be connected at all times.                                                                                                      |

| AVss        | Р           | Р              | Ground reference for analog modules.                                                                                                                                              |

| CLKI        | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                            |

| CLKO        | Ö           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associate with OSC2 pin function. |

| CN0-CN23    | I           | ST             | Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                         |

| C1RX        | I           | ST             | ECAN1 bus receive pin.                                                                                                                                                            |

| C1TX        | 0           | _              | ECAN1 bus transmit pin.                                                                                                                                                           |

| C2RX        | I           | ST             | ECAN2 bus receive pin.                                                                                                                                                            |

| C2TX        | 0           | _              | ECAN2 bus transmit pin.                                                                                                                                                           |

| PGED1       | I/O         | ST             | Data I/O pin for programming/debugging communication channel 1.                                                                                                                   |

| PGEC1       | I.          | ST             | Clock input pin for programming/debugging communication channel 1.                                                                                                                |

| PGED2       | I/O         | ST             | Data I/O pin for programming/debugging communication channel 2.                                                                                                                   |

| PGEC2       | I           | ST             | Clock input pin for programming/debugging communication channel 2.                                                                                                                |

| PGED3       | I/O         | ST             | Data I/O pin for programming/debugging communication channel 3.                                                                                                                   |

| PGEC3       |             | ST             | Clock input pin for programming/debugging communication channel 3.                                                                                                                |

| IC1-IC8     | I           | ST             | Capture inputs 1 through 8.                                                                                                                                                       |

| INDX        | I           | ST             | Quadrature Encoder Index Pulse input.                                                                                                                                             |

| QEA         | I           | ST             | Quadrature Encoder Phase A input in QEI mode. Auxiliary Timer External                                                                                                            |

|             |             |                | Clock/Gate input in Timer mode.                                                                                                                                                   |

| QEB         | 1           | ST             | Quadrature Encoder Phase A input in QEI mode. Auxiliary Timer External                                                                                                            |

|             |             |                | Clock/Gate input in Timer mode.                                                                                                                                                   |

| UPDN        | 0           | CMOS           | Position Up/Down Counter Direction State.                                                                                                                                         |

| INT0        | I           | ST             | External interrupt 0.                                                                                                                                                             |

| INT1        | 1           | ST             | External interrupt 1.                                                                                                                                                             |

| INT2        | 1           | ST             | External interrupt 2.                                                                                                                                                             |

| INT3        | 1           | ST             | External interrupt 3.                                                                                                                                                             |

| INT4        | I I         | ST             | External interrupt 4.                                                                                                                                                             |

| FLTA        | I           | ST             | PWM Fault A input.                                                                                                                                                                |

| FLTB        | 1           | ST             | PWM Fault B input.                                                                                                                                                                |

| PWM1L       | 0           | —              | PWM 1 low output.                                                                                                                                                                 |

| PWM1H       | 0           | _              | PWM 1 high output.                                                                                                                                                                |

| PWM2L       | 0           | _              | PWM 2 low output.                                                                                                                                                                 |

| PWM2H       | 0           | _              | PWM 2 high output.                                                                                                                                                                |

| PWM3L       | 0           | —              | PWM 3 low output.                                                                                                                                                                 |

| PWM3H       | 0           | _              | PWM 3 high output.                                                                                                                                                                |

| PWM4L       | 0           | —              | PWM 4 low output.                                                                                                                                                                 |

| PWM4H       | 0           | —              | PWM 4 high output.                                                                                                                                                                |

| MCLR        | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                        |

| OCFA        | I           | ST             | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).                                                                                                                       |

| OCFB        | I           | ST             | Compare Fault B input (for Compare Channels 5, 6, 7 and 8).                                                                                                                       |

| OC1-OC8     | 0           |                | Compare outputs 1 through 8.                                                                                                                                                      |

| OSC1        | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode;<br>CMOS otherwise.                                                                                                |

| OSC2        | I/O         | —              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                          |

| Legend: CMC | S = CMO     | S compatible   | e input or output Analog = Analog input P = Power                                                                                                                                 |

|             |             |                | with CMOS levels $O = Output$ I = Input                                                                                                                                           |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS

© 2009 Microchip Technology Inc.

| U-0              | U-0                            | U-0                                    | R/W-0           | R/W-0               | R-0              | R-0              | R-0   |

|------------------|--------------------------------|----------------------------------------|-----------------|---------------------|------------------|------------------|-------|

|                  |                                |                                        | US              | EDT <sup>(1)</sup>  |                  | DL<2:0>          |       |

| bit 15           |                                |                                        |                 |                     |                  |                  | bit   |

| R/W-0            | R/W-0                          | R/W-1                                  | R/W-0           | R/C-0               | R/W-0            | R/W-0            | R/W-0 |

| SATA             | SATB                           | SATDW                                  | ACCSAT          | IPL3 <sup>(2)</sup> | PSV              | RND              | IF    |

| bit 7            |                                | ·                                      | •               | •                   |                  |                  | bit   |

| Legend:          |                                | C = Clear on                           | y bit           |                     |                  |                  |       |

| R = Readable     | e bit                          | W = Writable                           | bit             | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is clea | ared                           | ʻx = Bit is unk                        | nown            | U = Unimplei        | mented bit, read | d as '0'         |       |

| bit 15-13        | Unimplemen                     | ted: Read as '                         | 0'              |                     |                  |                  |       |

| bit 12           | US: DSP Mul                    | tiply Unsigned                         | Signed Contro   | ol bit              |                  |                  |       |

|                  |                                | ne multiplies a<br>ne multiplies a     |                 |                     |                  |                  |       |

| bit 11           | EDT: Early DO                  | Loop Termina                           | ation Control b | it(1)               |                  |                  |       |

|                  | 1 = Terminate<br>0 = No effect | e executing DO                         | loop at end of  | current loop it     | eration          |                  |       |

| bit 10-8         | DL<2:0>: DO                    | Loop Nesting                           | Level Status bi | ts                  |                  |                  |       |

|                  | 111 <b>= 7</b> DO <b>lo</b>    | ops active                             |                 |                     |                  |                  |       |

|                  | •                              |                                        |                 |                     |                  |                  |       |

|                  | 001 = 1 DO lo                  | on active                              |                 |                     |                  |                  |       |

|                  | 000 = 0 DO lo                  |                                        |                 |                     |                  |                  |       |

| bit 7            | SATA: AccA                     | Saturation Ena                         | ble bit         |                     |                  |                  |       |

|                  |                                | tor A saturatio                        |                 |                     |                  |                  |       |

| bit 6            |                                | itor A saturatio<br>Saturation Ena     |                 |                     |                  |                  |       |

|                  |                                | tor B saturatio                        |                 |                     |                  |                  |       |

|                  |                                | itor B saturatio                       |                 |                     |                  |                  |       |

| bit 5            | SATDW: Data                    | a Space Write                          | from DSP Eng    | ine Saturation      | Enable bit       |                  |       |

|                  |                                | ce write satura<br>ce write satura     |                 |                     |                  |                  |       |

| bit 4            | -                              | cumulator Satu                         |                 | elect bit           |                  |                  |       |

|                  |                                | ration (super s                        |                 |                     |                  |                  |       |

|                  |                                | ration (normal                         |                 |                     |                  |                  |       |

| bit 3            |                                | terrupt Priority                       |                 |                     |                  |                  |       |

|                  |                                | rupt priority lev<br>rupt priority lev | •               | nan 7               |                  |                  |       |

| bit 2            | PSV: Progran                   | n Space Visibil                        | ity in Data Spa | ice Enable bit      |                  |                  |       |

|                  |                                | space visible i                        |                 |                     |                  |                  |       |

| bit 1            | •                              | space not visib                        | •               | ce                  |                  |                  |       |

|                  |                                | ng Mode Seleo<br>onventional) ro       |                 | èd                  |                  |                  |       |

|                  | •                              | (convergent)                           | •               |                     |                  |                  |       |

| bit 0            | IF: Integer or                 | Fractional Mul                         | tiplier Mode Se | elect bit           |                  |                  |       |

|                  |                                | ode enabled fo<br>I mode enable        |                 |                     |                  |                  |       |

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

|         | 1-6:        |                 |                                                            | STER N |        |        |        |             |             |               |                |       |        |       |       |       |       |               |

|---------|-------------|-----------------|------------------------------------------------------------|--------|--------|--------|--------|-------------|-------------|---------------|----------------|-------|--------|-------|-------|-------|-------|---------------|

|         | SFR<br>Addr | Bit 15          | Bit 14                                                     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9       | Bit 8       | Bit 7         | Bit 6          | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1    | 0100        |                 |                                                            |        |        |        |        |             | Timer1      | Register      |                |       |        |       |       |       |       | xxxx          |

| PR1     | 0102        |                 |                                                            |        |        |        |        |             |             |               |                |       | FFFF   |       |       |       |       |               |

| T1CON   | 0104        | TON             | —                                                          | TSIDL  | _      | _      | _      | _           | _           | _             | TGATE          | TCKP  | S<1:0> | _     | TSYNC | TCS   | —     | 0000          |

| TMR2    | 0106        |                 |                                                            |        |        |        |        |             | Timer2      | Register      |                |       |        |       |       |       |       | xxxx          |

| TMR3HLD | 0108        |                 | Timer3 Holding Register (for 32-bit timer operations only) |        |        |        |        |             |             |               |                | xxxx  |        |       |       |       |       |               |

| TMR3    | 010A        |                 |                                                            |        |        |        |        |             | Timer3      | Register      |                |       |        |       |       |       |       | xxxx          |

| PR2     | 010C        |                 |                                                            |        |        |        |        |             | Period F    | Register 2    |                |       |        |       |       |       |       | FFFF          |

| PR3     | 010E        |                 |                                                            |        |        |        |        |             | Period F    | Register 3    |                |       |        |       |       |       |       | FFFF          |

| T2CON   | 0110        | TON             | _                                                          | TSIDL  | —      | —      | _      | _           | _           | _             | TGATE          | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T3CON   | 0112        | TON             | _                                                          | TSIDL  | —      | —      | _      | _           | _           | —             | TGATE          | TCKP  | S<1:0> |       | _     | TCS   | _     | 0000          |

| TMR4    | 0114        |                 |                                                            |        |        |        |        |             | Timer4      | Register      |                |       |        |       |       |       |       | xxxx          |

| TMR5HLD | 0116        |                 |                                                            |        |        |        | -      | Timer5 Hold | ng Register | (for 32-bit o | perations only | /)    |        |       |       |       |       | xxxx          |

| TMR5    | 0118        | Timer5 Register |                                                            |        |        |        |        |             |             | xxxx          |                |       |        |       |       |       |       |               |

| PR4     | 011A        |                 |                                                            |        |        |        |        |             | Period F    | Register 4    |                |       |        |       |       |       |       | FFFF          |

| PR5     | 011C        |                 |                                                            |        |        |        |        |             | Period F    | Register 5    |                |       |        |       |       |       |       | FFFF          |

| T4CON   | 011E        | TON             | _                                                          | TSIDL  | _      | _      | _      | _           | _           | _             | TGATE          | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T5CON   | 0120        | TON             | —                                                          | TSIDL  | _      | _      |        |             |             | —             | TGATE          | TCKP  | S<1:0> | _     | —     | TCS   |       | 0000          |

| TMR6    | 0122        |                 |                                                            |        |        |        |        |             | Timer6      | Register      |                |       |        |       |       |       |       | xxxx          |

| TMR7HLD | 0124        |                 |                                                            |        |        |        | -      | Timer7 Hold | ng Register | (for 32-bit o | perations only | /)    |        |       |       |       |       | xxxx          |

| TMR7    | 0126        |                 |                                                            |        |        |        |        |             | Timer7      | Register      |                |       |        |       |       |       |       | xxxx          |

| PR6     | 0128        |                 |                                                            |        |        |        |        |             | Period F    | Register 6    |                |       |        |       |       |       |       | FFFF          |

| PR7     | 012A        |                 |                                                            |        |        |        |        |             | Period F    | Register 7    |                |       |        |       |       |       |       | FFFF          |

| T6CON   | 012C        | TON             | —                                                          | TSIDL  |        | —      |        |             |             |               | TGATE          | TCKP  | S<1:0> | T32   | —     | TCS   |       | 0000          |

| T7CON   | 012E        | TON             | —                                                          | TSIDL  |        | —      |        |             |             |               | TGATE          | TCKP  | S<1:0> | _     | —     | TCS   |       | 0000          |

| TMR8    | 0130        |                 |                                                            |        |        |        |        |             | Timer8      | Register      |                |       |        |       |       |       |       | xxxx          |

| TMR9HLD | 0132        |                 |                                                            |        |        |        | -      | Timer9 Hold | ng Register | (for 32-bit o | perations only | /)    |        |       |       |       |       | xxxx          |

| TMR9    | 0134        |                 |                                                            |        |        |        |        |             | Timer9      | Register      |                |       |        |       |       |       |       | xxxx          |

| PR8     | 0136        |                 |                                                            |        |        |        |        |             | Period F    | Register 8    |                |       |        |       |       |       |       | FFFF          |

| PR9     | 0138        |                 |                                                            |        |        |        |        |             | Period F    | Register 9    |                |       |        |       |       |       |       | FFFF          |

| T8CON   | 013A        | TON             | —                                                          | TSIDL  | —      | _      | —      | —           | —           | —             | TGATE          | TCKP  | S<1:0> | T32   | —     | TCS   | —     | 0000          |

| T9CON   | 013C        | TON             | —                                                          | TSIDL  | —      | _      | —      | —           | —           | —             | TGATE          | TCKP  | S<1:0> | —     | —     | TCS   | —     | 0000          |

### TABLE 4-6: TIMER REGISTER MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-9: 8-OUTPUT PWM REGISTER MAP

| SFR Name  | Addr. | Bit 15  | Bit 14                                                                    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7       | Bit 6               | Bit 5               | Bit 4               | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset State         |

|-----------|-------|---------|---------------------------------------------------------------------------|--------|--------|--------|--------|--------|-------------|-------------|---------------------|---------------------|---------------------|--------|--------|--------|--------|---------------------|

| P1TCON    | 01C0  | PTEN    | N - PTSIDL PTOPS<3:0> PTCKPS<1:0> PTMOD<1:0>                              |        |        |        |        |        |             |             |                     |                     | 0000 0000 0000 0000 |        |        |        |        |                     |

| P1TMR     | 01C2  | PTDIR   | DIR PWM Timer Count Value Register                                        |        |        |        |        |        |             |             | 0000 0000 0000 0000 |                     |                     |        |        |        |        |                     |

| P1TPER    | 01C4  | _       |                                                                           |        |        |        |        | F      | PWM Time    | Base Perio  | od Registe          | r                   |                     |        |        |        |        | 0000 0000 0000 0000 |

| P1SECMP   | 01C6  | SEVTDIR | PWM Special Event Compare Register                                        |        |        |        |        |        |             |             | 0000 0000 0000 0000 |                     |                     |        |        |        |        |                     |

| PWM1CON1  | 01C8  | _       | PMOD4 PMOD3 PMOD2 PMOD1 PEN4H PEN3H PEN2H PEN1H PEN4L PEN3L PEN2L PEN1L 0 |        |        |        |        |        |             |             |                     | 0000 0000 1111 1111 |                     |        |        |        |        |                     |

| PWM1CON2  | 01CA  | _       |                                                                           | _      | _      |        | SEVOP  | S<3:0> |             | -           | _                   | _                   | _                   | _      | IUE    | OSYNC  | UDIS   | 0000 0000 0000 0000 |

| P1DTCON1  | 01CC  | DTBPS   | i<1:0>                                                                    |        |        | DTB<   | <5:0>  |        |             | DTAPS       | S<1:0>              |                     |                     | DTA    | <5:0>  |        |        | 0000 0000 0000 0000 |

| P1DTCON2  | 01CE  | _       |                                                                           | _      | _      | _      | _      | _      | _           | DTS4A       | DTS4I               | DTS3A               | DTS3I               | DTS2A  | DTS2I  | DTS1A  | DTS1I  | 0000 0000 0000 0000 |

| P1FLTACON | 01D0  | FAOV4H  | FAOV4L                                                                    | FAOV3H | FAOV3L | FAOV2H | FAOV2L | FAOV1H | FAOV1L      | FLTAM       | _                   | _                   | _                   | FAEN4  | FAEN3  | FAEN2  | FAEN1  | 0000 0000 0000 0000 |

| P1FLTBCON | 01D2  | FBOV4H  | FBOV4L                                                                    | FBOV3H | FBOV3L | FBOV2H | FBOV2L | FBOV1H | FBOV1L      | FLTBM       | _                   | _                   | _                   | FBEN4  | FBEN3  | FBEN2  | FBEN1  | 0000 0000 0000 0000 |

| P10VDCON  | 01D4  | POVD4H  | POVD4L                                                                    | POVD3H | POVD3L | POVD2H | POVD2L | POVD1H | POVD1L      | POUT4H      | POUT4L              | POUT3H              | POUT3L              | POUT2H | POUT2L | POUT1H | POUT1L | 1111 1111 0000 0000 |

| P1DC1     | 01D6  |         |                                                                           |        |        |        |        | PWN    | /I Duty Cyc | le #1 Regis | ster                |                     |                     |        |        |        |        | 0000 0000 0000 0000 |

| P1DC2     | 01D8  |         |                                                                           |        |        |        |        | PWN    | / Duty Cyc  | le #2 Regi  | ster                |                     |                     |        |        |        |        | 0000 0000 0000 0000 |

| P1DC3     | 01DA  |         |                                                                           |        |        |        |        | PWN    | / Duty Cyc  | le #3 Regi  | ster                |                     |                     |        |        |        |        | 0000 0000 0000 0000 |

| P1DC4     | 01DC  |         |                                                                           |        |        |        |        | PWN    | / Duty Cyc  | le #4 Regis | ster                |                     |                     |        |        |        |        | 0000 0000 0000 0000 |

Legend: u = uninitialized bit, - = unimplemented, read as '0'

NOTES:

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address | AIVT Address | Interrupt Source                |

|------------------|--------------------------------------|-------------|--------------|---------------------------------|

| 8                | 0                                    | 0x000014    | 0x000114     | INT0 – External Interrupt 0     |

| 9                | 1                                    | 0x000016    | 0x000116     | IC1 – Input Compare 1           |

| 10               | 2                                    | 0x000018    | 0x000118     | OC1 – Output Compare 1          |

| 11               | 3                                    | 0x00001A    | 0x00011A     | T1 – Timer1                     |

| 12               | 4                                    | 0x00001C    | 0x00011C     | DMA0 – DMA Channel 0            |

| 13               | 5                                    | 0x00001E    | 0x00011E     | IC2 – Input Capture 2           |

| 14               | 6                                    | 0x000020    | 0x000120     | OC2 – Output Compare 2          |

| 15               | 7                                    | 0x000022    | 0x000122     | T2 – Timer2                     |

| 16               | 8                                    | 0x000024    | 0x000124     | T3 – Timer3                     |

| 17               | 9                                    | 0x000026    | 0x000126     | SPI1E – SPI1 Error              |

| 18               | 10                                   | 0x000028    | 0x000128     | SPI1 – SPI1 Transfer Done       |

| 19               | 11                                   | 0x00002A    | 0x00012A     | U1RX – UART1 Receiver           |

| 20               | 12                                   | 0x00002C    | 0x00012C     | U1TX – UART1 Transmitter        |

| 21               | 13                                   | 0x00002E    | 0x00012E     | ADC1 – ADC 1                    |

| 22               | 14                                   | 0x000030    | 0x000130     | DMA1 – DMA Channel 1            |

| 23               | 15                                   | 0x000032    | 0x000132     | Reserved                        |

| 24               | 16                                   | 0x000034    | 0x000134     | SI2C1 – I2C1 Slave Events       |

| 25               | 17                                   | 0x000036    | 0x000136     | MI2C1 – I2C1 Master Events      |

| 26               | 18                                   | 0x000038    | 0x000138     | Reserved                        |

| 27               | 19                                   | 0x00003A    | 0x00013A     | Change Notification Interrupt   |

| 28               | 20                                   | 0x00003C    | 0x00013C     | INT1 – External Interrupt 1     |

| 29               | 21                                   | 0x00003E    | 0x00013E     | ADC2 – ADC 2                    |

| 30               | 22                                   | 0x000040    | 0x000140     | IC7 – Input Capture 7           |

| 31               | 23                                   | 0x000042    | 0x000142     | IC8 – Input Capture 8           |

| 32               | 24                                   | 0x000044    | 0x000144     | DMA2 – DMA Channel 2            |

| 33               | 25                                   | 0x000046    | 0x000146     | OC3 – Output Compare 3          |

| 34               | 26                                   | 0x000048    | 0x000148     | OC4 – Output Compare 4          |

| 35               | 27                                   | 0x00004A    | 0x00014A     | T4 – Timer4                     |

| 36               | 28                                   | 0x00004C    | 0x00014C     | T5 – Timer5                     |

| 37               | 29                                   | 0x00004E    | 0x00014E     | INT2 – External Interrupt 2     |

| 38               | 30                                   | 0x000050    | 0x000150     | U2RX – UART2 Receiver           |

| 39               | 31                                   | 0x000052    | 0x000152     | U2TX – UART2 Transmitter        |

| 40               | 32                                   | 0x000054    | 0x000154     | SPI2E – SPI2 Error              |

| 41               | 33                                   | 0x000056    | 0x000156     | SPI1 – SPI1 Transfer Done       |

| 42               | 34                                   | 0x000058    | 0x000158     | C1RX – ECAN1 Receive Data Ready |

| 43               | 35                                   | 0x00005A    | 0x00015A     | C1 – ECAN1 Event                |

| 44               | 36                                   | 0x00005C    | 0x00015C     | DMA3 – DMA Channel 3            |

| 45               | 37                                   | 0x00005E    | 0x00015E     | IC3 – Input Capture 3           |

| 46               | 38                                   | 0x000060    | 0x000160     | IC4 – Input Capture 4           |

| 47               | 39                                   | 0x000062    | 0x000162     | IC5 – Input Capture 5           |

| 48               | 40                                   | 0x000064    | 0x000164     | IC6 – Input Capture 6           |

| 49               | 41                                   | 0x000066    | 0x000166     | OC5 – Output Compare 5          |

| 50               | 42                                   | 0x000068    | 0x000168     | OC6 – Output Compare 6          |

| 51               | 43                                   | 0x00006A    | 0x00016A     | OC7 – Output Compare 7          |

| 52               | 44                                   | 0x00006C    | 0x00016C     | OC8 – Output Compare 8          |

| 53               | 45                                   | 0x00006E    | 0x00016E     | Reserved                        |

TABLE 7-1:INTERRUPT VECTORS

## REGISTER 7-22: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

| U-0           | R/W-1             | R/W-0                                  | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|---------------|-------------------|----------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

| _             |                   | U2TXIP<2:0>                            |                 | _                |                 | U2RXIP<2:0>     |       |

| bit 15        |                   |                                        |                 |                  |                 |                 | bit 8 |

|               |                   |                                        |                 |                  |                 |                 |       |

| U-0           | R/W-1             | R/W-0                                  | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|               |                   | INT2IP<2:0>                            |                 | _                |                 | T5IP<2:0>       | L :4  |

| bit 7         |                   |                                        |                 |                  |                 |                 | bit   |

| Legend:       |                   |                                        |                 |                  |                 |                 |       |

| R = Readabl   | e bit             | W = Writable                           | bit             | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at | POR               | '1' = Bit is set                       |                 | '0' = Bit is cle | ared            | x = Bit is unkr | iown  |

| bit 15        | Unimpleme         | ented: Read as '                       | )'              |                  |                 |                 |       |

| bit 14-12     |                   | )>: UART2 Trans                        |                 |                  |                 |                 |       |

|               | 111 = Interr      | upt is priority 7 (I                   | nighest priorit | y interrupt)     |                 |                 |       |

|               | •                 |                                        |                 |                  |                 |                 |       |

|               | •                 |                                        |                 |                  |                 |                 |       |

|               |                   | upt is priority 1<br>upt source is dis | ablad           |                  |                 |                 |       |

| bit 11        |                   | ented: Read as '                       |                 |                  |                 |                 |       |

| bit 10-8      | -                 | 0>: UART2 Rece                         |                 | Priority hits    |                 |                 |       |

|               |                   | upt is priority 7 (I                   | -               | -                |                 |                 |       |

|               | •                 |                                        |                 | ,                |                 |                 |       |

|               | •                 |                                        |                 |                  |                 |                 |       |

|               | •<br>001 = Interr | upt is priority 1                      |                 |                  |                 |                 |       |

|               |                   | upt source is dis                      | abled           |                  |                 |                 |       |

| bit 7         | Unimpleme         | nted: Read as 'o                       | )'              |                  |                 |                 |       |

| bit 6-4       | INT2IP<2:0        | >: External Interr                     | upt 2 Priority  | bits             |                 |                 |       |

|               | 111 = Interr      | upt is priority 7 (I                   | nighest priorit | y interrupt)     |                 |                 |       |

|               | •                 |                                        |                 |                  |                 |                 |       |

|               | •                 |                                        |                 |                  |                 |                 |       |

|               | 001 = Interr      | upt is priority 1                      |                 |                  |                 |                 |       |

|               | 000 = Interr      | upt source is dis                      | abled           |                  |                 |                 |       |

| bit 3         | Unimpleme         | ented: Read as 'o                      | )'              |                  |                 |                 |       |

| bit 2-0       | T5IP<2:0>:        | Timer5 Interrupt                       | Priority bits   |                  |                 |                 |       |

|               | 111 = Interr      | upt is priority 7 (I                   | nighest priorit | y interrupt)     |                 |                 |       |

|               | •                 |                                        |                 |                  |                 |                 |       |

|               | •                 |                                        |                 |                  |                 |                 |       |

|               |                   | upt is priority 1                      |                 |                  |                 |                 |       |

|               | a a a lusta un    | upt source is dis                      |                 |                  |                 |                 |       |

| REGISTER 7-26: IPC11: INTERRUPT PRIORITY CONTROL REGISTER 11 | <b>REGISTER 7-26:</b> |

|--------------------------------------------------------------|-----------------------|

|--------------------------------------------------------------|-----------------------|

| U-0                | R/W-1                   | R/W-0                                  | R/W-0                           | U-0              | R/W-1            | R/W-0           | R/W-0   |

|--------------------|-------------------------|----------------------------------------|---------------------------------|------------------|------------------|-----------------|---------|

| _                  |                         | T6IP<2:0>                              |                                 | —                |                  | DMA4IP<2:0>     |         |

| bit 15             |                         |                                        |                                 |                  |                  |                 | bit 8   |

| U-0                | U-0                     | U-0                                    | U-0                             | U-0              | R/W-1            | R/W-0           | R/W-0   |

|                    |                         |                                        |                                 |                  | 10/00-1          | OC8IP<2:0>      | 10,00-0 |

| bit 7              |                         |                                        |                                 |                  |                  | 00011 32.05     | bit     |

|                    |                         |                                        |                                 |                  |                  |                 |         |

| Legend:            |                         |                                        |                                 |                  |                  |                 |         |

| R = Readab         | le bit                  | W = Writable                           | oit                             | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value a       | It POR                  | '1' = Bit is set                       |                                 | '0' = Bit is cle | ared             | x = Bit is unkr | iown    |

|                    |                         |                                        |                                 |                  |                  |                 |         |

| bit 15             | Unimpleme               | nted: Read as 'o                       | )'                              |                  |                  |                 |         |

| bit 14-12          | T6IP<2:0>:              | Timer6 Interrupt                       | Priority bits                   |                  |                  |                 |         |

|                    | 111 = Interr            | upt is priority 7 (I                   | nighest priorit                 | y interrupt)     |                  |                 |         |

|                    | •                       |                                        |                                 |                  |                  |                 |         |

|                    | •                       |                                        |                                 |                  |                  |                 |         |

|                    | •<br>001 = Interr       | upt is priority 1                      |                                 |                  |                  |                 |         |

|                    |                         | upt is phoney is dis                   | abled                           |                  |                  |                 |         |

| bit 11             |                         | nted: Read as 'o                       |                                 |                  |                  |                 |         |

| bit 10-8           | -                       | 0>: DMA Channe                         |                                 | sfer Complete    | Interrunt Priori | tv hits         |         |

|                    |                         | upt is priority 7 (I                   |                                 | -                | interrupt i non  |                 |         |

|                    | •                       | арт ю р.:от, у (.                      |                                 | ,                |                  |                 |         |

|                    | •                       |                                        |                                 |                  |                  |                 |         |

|                    | •                       |                                        |                                 |                  |                  |                 |         |

|                    |                         | upt is priority 1<br>upt source is dis | ablad                           |                  |                  |                 |         |

|                    |                         | •                                      |                                 |                  |                  |                 |         |

| hit 7 2            | Ilnimnlama              | ntad: Dood on '/                       | `                               |                  |                  |                 |         |

|                    | -                       | nted: Read as '                        |                                 |                  |                  |                 |         |

|                    | OC8IP<2:0>              | : Output Compa                         | re Channel 8                    | -                | ity bits         |                 |         |

|                    | OC8IP<2:0>              |                                        | re Channel 8                    | -                | ity bits         |                 |         |

|                    | OC8IP<2:0>              | : Output Compa                         | re Channel 8                    | -                | ity bits         |                 |         |

|                    | OC8IP<2:0>              | : Output Compa                         | re Channel 8                    | -                | ity bits         |                 |         |

| bit 7-3<br>bit 2-0 | OC8IP<2:0> 111 = Intern | : Output Compa                         | re Channel 8<br>highest priorit | -                | ity bits         |                 |         |

## REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

| U-0           | R/W-1        | R/W-0                                    | R/W-0            | U-0              | R/W-1           | R/W-0           | R/W-0 |

|---------------|--------------|------------------------------------------|------------------|------------------|-----------------|-----------------|-------|

|               |              | T8IP<2:0>                                |                  | —                |                 | MI2C2IP<2:0>    |       |

| bit 15        |              |                                          |                  |                  |                 |                 | bit 8 |

|               |              |                                          |                  |                  |                 |                 |       |

| U-0           | R/W-1        | R/W-0                                    | R/W-0            | U-0              | R/W-1           | R/W-0           | R/W-0 |

| _             |              | SI2C2IP<2:0>                             |                  | —                |                 | T7IP<2:0>       |       |

| bit 7         |              |                                          |                  |                  |                 |                 | bit 0 |

| Legend:       |              |                                          |                  |                  |                 |                 |       |

| R = Readabl   | e bit        | W = Writable                             | bit              | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value at | POR          | '1' = Bit is set                         |                  | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

| bit 15        | Unimpleme    | ented: Read as '                         | 0'               |                  |                 |                 |       |

| bit 14-12     | -            | Timer8 Interrupt                         |                  |                  |                 |                 |       |

|               |              | rupt is priority 7 (                     | •                | y interrupt)     |                 |                 |       |

|               | •            |                                          |                  |                  |                 |                 |       |

|               | •            |                                          |                  |                  |                 |                 |       |

|               | 001 = Interr | rupt is priority 1                       |                  |                  |                 |                 |       |

|               | 000 = Interr | rupt source is dis                       | abled            |                  |                 |                 |       |

| bit 11        | Unimpleme    | ented: Read as '                         | 0'               |                  |                 |                 |       |

| bit 10-8      |              | :0>: I2C2 Master                         |                  |                  | S               |                 |       |

|               | 111 = Interr | rupt is priority 7 (                     | highest priorit  | y interrupt)     |                 |                 |       |

|               | •            |                                          |                  |                  |                 |                 |       |

|               | •            |                                          |                  |                  |                 |                 |       |

|               |              | rupt is priority 1                       | a la la al       |                  |                 |                 |       |

| L:1 7         |              | rupt source is dis                       |                  |                  |                 |                 |       |

| bit 7         | -            | ented: Read as '                         |                  | nt Drievity bite |                 |                 |       |

| bit 6-4       |              | 0>: I2C2 Slave E<br>rupt is priority 7 ( |                  |                  |                 |                 |       |

|               | •            |                                          | nightest priorit | y menupi)        |                 |                 |       |

|               | •            |                                          |                  |                  |                 |                 |       |

|               | •            | runt in priority 1                       |                  |                  |                 |                 |       |

|               |              | rupt is priority 1<br>rupt source is dis | abled            |                  |                 |                 |       |

| bit 3         |              | ented: Read as '                         |                  |                  |                 |                 |       |

| bit 2-0       | -            | Timer7 Interrupt                         |                  |                  |                 |                 |       |

|               |              | rupt is priority 7 (                     | -                | y interrupt)     |                 |                 |       |

|               | •            |                                          |                  |                  |                 |                 |       |

|               | •            |                                          |                  |                  |                 |                 |       |

|               | 001 = Interr | rupt is priority 1                       |                  |                  |                 |                 |       |

|               | 000 = Interr |                                          |                  |                  |                 |                 |       |

## REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PWCOL7 | PWCOL6 | PWCOL5 | PWCOL4 | PWCOL3 | PWCOL2 | PWCOL1 | PWCOL0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| XWCOL7 | XWCOL6 | XWCOL5 | XWCOL4 | XWCOL3 | XWCOL2 | XWCOL1 | XWCOL0 |

| bit 7  | •      |        |        | •      |        |        | bit 0  |

| Legend:      |                             | C = Clear only bit                                                           |                        |                    |

|--------------|-----------------------------|------------------------------------------------------------------------------|------------------------|--------------------|

| R = Readal   | ble bit                     | W = Writable bit                                                             | U = Unimplemented bit  | , read as '0'      |

| -n = Value a | at POR                      | '1' = Bit is set                                                             | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15       | PWCOL7                      | Channel 7 Peripheral Wri                                                     | te Collision Flag bit  |                    |

|              | 1 = Write                   | collision detected<br>rite collision detected                                |                        |                    |

| bit 14       |                             | : Channel 6 Peripheral Wri                                                   | te Collision Flag bit  |                    |

|              |                             | collision detected<br>rite collision detected                                |                        |                    |

| bit 13       | 1 = Write                   | Channel 5 Peripheral Wri<br>collision detected<br>rite collision detected    | te Collision Flag bit  |                    |

| bit 12       | 1 = Write                   | I: Channel 4 Peripheral Wri<br>collision detected<br>rite collision detected | te Collision Flag bit  |                    |

| bit 11       |                             |                                                                              | te Collision Flag bit  |                    |

| bit 10       | 1 = Write                   | 2: Channel 2 Peripheral Wri<br>collision detected<br>rite collision detected | te Collision Flag bit  |                    |

| bit 9        | <b>PWCOL</b> 1<br>1 = Write | I: Channel 1 Peripheral Wri<br>collision detected<br>rite collision detected | te Collision Flag bit  |                    |

| bit 8        |                             |                                                                              | te Collision Flag bit  |                    |

| bit 7        | 1 = Write                   | 7: Channel 7 DMA RAM Wri<br>collision detected<br>rite collision detected    | ite Collision Flag bit |                    |

| bit 6        | 1 = Write                   | Channel 6 DMA RAM Wri<br>collision detected<br>rite collision detected       | ite Collision Flag bit |                    |

| bit 5        | 1 = Write                   | 5: Channel 5 DMA RAM Wri<br>collision detected<br>rite collision detected    | ite Collision Flag bit |                    |

| bit 4        |                             | I: Channel 4 DMA RAM Wri                                                     | ite Collision Flag bit |                    |

|              |                             |                                                                              |                        |                    |

## REGISTER 17-1: QEIXCON: QEI CONTROL REGISTER (CONTINUED)

| bit 4-3 | <b>TQCKPS&lt;1:0&gt;:</b> Timer Input Clock Prescale Select bits<br>11 = 1:256 prescale value                                                                                                                     |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|         |                                                                                                                                                                                                                   |  |  |  |  |  |

|         | 10 = 1:64 prescale value                                                                                                                                                                                          |  |  |  |  |  |

|         | 01 = 1:8 prescale value                                                                                                                                                                                           |  |  |  |  |  |

|         | 00 = 1:1 prescale value                                                                                                                                                                                           |  |  |  |  |  |

|         | (Prescaler utilized for 16-bit timer mode only)                                                                                                                                                                   |  |  |  |  |  |

| bit 2   | POSRES: Position Counter Reset Enable bit                                                                                                                                                                         |  |  |  |  |  |

|         | 1 = Index Pulse resets Position Counter                                                                                                                                                                           |  |  |  |  |  |

|         | 0 = Index Pulse does not reset Position Counter                                                                                                                                                                   |  |  |  |  |  |

|         | (Bit only applies when QEIM<2:0> = 100 or 110)                                                                                                                                                                    |  |  |  |  |  |

| bit 1   | TQCS: Timer Clock Source Select bit                                                                                                                                                                               |  |  |  |  |  |

|         | 1 = External clock from pin QEA (on the rising edge)                                                                                                                                                              |  |  |  |  |  |

|         | 0 = Internal clock Tcy)                                                                                                                                                                                           |  |  |  |  |  |

| bit 0   | <b>UPDN_SRC:</b> Position Counter Direction Selection Control bit<br>1 = QEB pin state defines Position Counter direction<br>0 = Control/status bit UPDN (QEICON<11>) defines Position Counter (POSCNT) direction |  |  |  |  |  |

|         | Note: When configured for QEI mode, control bit is a 'don't care'.                                                                                                                                                |  |  |  |  |  |

| R/W-0                                                                                                                     | R/W-0                        | R/W-0                                                                 | U-0                                 | U-0                            | U-0              | U-0                | U-0   |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------------------|-------------------------------------|--------------------------------|------------------|--------------------|-------|

| FRMEN                                                                                                                     | SPIFSD                       | FRMPOL                                                                | _                                   | _                              | _                | _                  | _     |

| bit 15                                                                                                                    | ·                            | •                                                                     |                                     |                                |                  |                    | bit 8 |

|                                                                                                                           |                              |                                                                       |                                     |                                |                  | DAMO               |       |

| U-0                                                                                                                       | U-0                          | U-0                                                                   | U-0                                 | U-0                            | U-0              | R/W-0              | U-0   |

|                                                                                                                           | _                            |                                                                       | —                                   |                                | _                | FRMDLY             |       |

| oit 7                                                                                                                     |                              |                                                                       |                                     |                                |                  |                    | bit C |

| Legend:                                                                                                                   |                              |                                                                       |                                     |                                |                  |                    |       |

| R = Readabl                                                                                                               | e bit                        | W = Writable I                                                        | oit                                 | U = Unimplen                   | nented bit, read | d as '0'           |       |

| -n = Value at                                                                                                             | POR                          | '1' = Bit is set                                                      |                                     | '0' = Bit is clea              | ared             | x = Bit is unknown |       |

| bit 15<br>bit 14                                                                                                          | 1 = Framed S<br>0 = Framed S | med SPIx Supp<br>SPIx support en<br>SPIx support dis<br>me Sync Pulse | abled ( <mark>SSx</mark> p<br>abled | oin used as fram<br>ontrol bit | e sync pulse ir  | nput/output)       |       |

|                                                                                                                           |                              | nc pulse input (<br>nc pulse output                                   |                                     |                                |                  |                    |       |

| bit 13 FRMPOL: Frame Sync Pulse Polarity bit<br>1 = Frame sync pulse is active-high<br>0 = Frame sync pulse is active-low |                              |                                                                       |                                     |                                |                  |                    |       |

| bit 12-2                                                                                                                  | Unimplemen                   | Unimplemented: Read as '0'                                            |                                     |                                |                  |                    |       |

| bit 1                                                                                                                     |                              | ame Sync Pulse                                                        | •                                   |                                |                  |                    |       |

|                                                                                                                           |                              | nc pulse coincient nc pulse precee                                    |                                     |                                |                  |                    |       |

### REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

## **REGISTER 21-4:** CIFCTRL: ECAN™ FIFO CONTROL REGISTER

| R/W-0         | R/W-0                                                                                                                                                                                                                                                         | R/W-0                            | U-0   | U-0              | U-0              | U-0             | U-0   |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------|------------------|------------------|-----------------|-------|

|               | DMABS<2:0>                                                                                                                                                                                                                                                    |                                  | _     | _                | _                | _               | —     |

| bit 15        |                                                                                                                                                                                                                                                               |                                  |       |                  |                  |                 | bit 8 |

|               |                                                                                                                                                                                                                                                               |                                  |       |                  |                  |                 |       |

| U-0           | U-0                                                                                                                                                                                                                                                           | U-0                              | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| _             |                                                                                                                                                                                                                                                               |                                  |       |                  | FSA<4:0>         |                 |       |

| bit 7         |                                                                                                                                                                                                                                                               |                                  |       |                  |                  |                 | bit 0 |