Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256КВ (256К х 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 30K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256mc710t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC, SmartShunt and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, nanoWatt XLP, PICkit, PICDEM, PICDEM.net, PICtail, PIC<sup>32</sup> logo, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

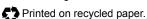

## DATA MEMORY MAP FOR dsPIC33FJXXXMCX06/X08/X10 DEVICES WITH 16 KB

#### TABLE 4-13: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15                        | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                                              | Bit 7 | Bit 6  | Bit 5 | Bit 4       | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|-------------------------------|--------|----------|--------|--------|--------|-------|----------------------------------------------------|-------|--------|-------|-------------|--------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN                        |        | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                                               | WAKE  | LPBACK | ABAUD | URXINV      | BRGH   | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1                      | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT URXISEL<1:0> ADDEN RIDLE PERR FERR OERR URXDA |       |        |       |             |        |       | 0110   |       |               |

| U1TXREG  | 0224        | _                             | _      | _        | _      | _      | _      | —     | UART Transmit Register                             |       |        |       |             |        |       |        | xxxx  |               |

| U1RXREG  | 0226        | _                             | _      | _        | _      | _      | —      | _     |                                                    |       |        | UART  | Receive Reg | gister |       |        |       | 0000          |

| U1BRG    | 0228        | Baud Rate Generator Prescaler |        |          |        |        |        |       |                                                    |       |        |       |             | 0000   |       |        |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: UART2 REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15   | Bit 14                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                  | Bit 7  | Bit 6   | Bit 5 | Bit 4      | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------------|----------|-------------------------------|----------|--------|--------|--------|-------|------------------------|--------|---------|-------|------------|--------|-------|--------|-------|---------------|

| U2MODE      | 0230        | UARTEN   | —                             | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                   | WAKE   | LPBACK  | ABAUD | URXINV     | BRGH   | PDSE  | _<1:0> | STSEL | 0000          |

| U2STA       | 0232        | UTXISEL1 | UTXINV                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXISE | EL<1:0> | ADDEN | RIDLE      | PERR   | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234        | _        | _                             | —        | _      | _      | _      | _     | UART Transmit Register |        |         |       |            |        |       | xxxx   |       |               |

| U2RXREG     | 0236        | _        | _                             | —        | _      | _      | _      | _     |                        |        |         | UART  | Receive Re | gister |       |        |       | 0000          |

| U2BRG       | 0238        |          | Baud Rate Generator Prescaler |          |        |        |        |       |                        |        |         |       |            |        | 0000  |        |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-15: SPI1 REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------------|--------|--------|---------|--------|--------|--------|------------|-------------|--------------|----------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI1STAT    | 0240        | SPIEN  | —      | SPISIDL | _      | _      | —      | —          |             |              | SPIROV   | —     | _     | —         |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1    | 0242        | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE         | SSEN         | CKP      | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2    | 0244        | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _      | _          | _           | _            | _        | _     | -     | _         | _     | FRMDLY | _      | 0000          |

| SPI1BUF     | 0248        |        |        |         |        |        |        | SPI1 Trans | mit and Red | ceive Buffer | Register |       |       |           |       |        |        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-16: SPI2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                                       | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|----------------------------------------------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI2STAT | 0260        | SPIEN  | _                                            | SPISIDL | _      | _      | —      | _     | _     | _     | SPIROV | _     | _     | _         | _     | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262        | _      | _                                            | _       | DISSCK | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264        | FRMEN  | SPIFSD                                       | FRMPOL  | -      | _      | _      | _     | _     | _     | _      | _     | _     | _         | _     | FRMDLY | _      | 0000          |

| SPI2BUF  | 0268        |        | SPI2 Transmit and Receive Buffer Register 00 |         |        |        |        |       |       |       |        |       | 0000  |           |       |        |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

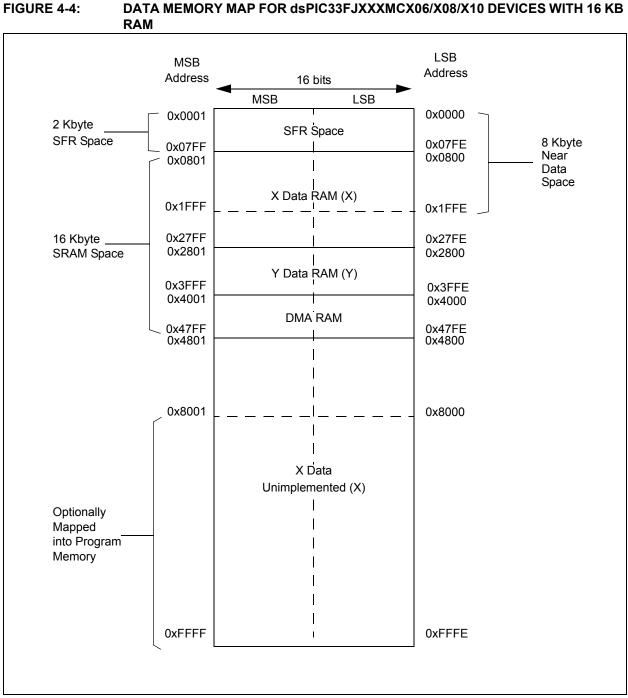

## 4.2.7 SOFTWARE STACK

In addition to its use as a working register, the W15 register in the dsPIC33FJXXXMCX06/X08/X10 devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | concatenates the SRL register to the MSb |

|       | of the PC prior to the push.             |

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### FIGURE 4-6: CALL STACK FRAME

## 4.2.8 DATA RAM PROTECTION FEATURE

The dsPIC33FJXXXMCX06/X08/X10 devices supports Data RAM protection features which enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

## 4.3 Instruction Addressing Modes

The addressing modes in Table 4-36 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions are somewhat different from those in the other instruction types.

### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

### 4.3.2 MCU INSTRUCTIONS

The 3-operand MCU instructions are of the following form:

Operand 3 = Operand 1 < function> Operand 2

where Operand 1 is always a working register (i.e., the addressing mode can only be register direct) which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

#### 5.4.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is as follows:

- 1. Read eight rows of program memory (512 instructions) and store it in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5 using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

### EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| · -          | CON for block erase operation        |                                         |

|--------------|--------------------------------------|-----------------------------------------|

| MOV          | #0x4042, W0                          | i                                       |

| MOV          | W0, NVMCON                           | ; Initialize NVMCON                     |

| ; Init point | er to row to be ERASED               |                                         |

| MOV          | <pre>#tblpage(PROG_ADDR), W0</pre>   | ;                                       |

| MOV          | W0, TBLPAG                           | ; Initialize PM Page Boundary SFR       |

| MOV          | <pre>#tbloffset(PROG_ADDR), W0</pre> | ; Initialize in-page EA[15:0] pointer   |

| TBLWI        | L WO, [WO]                           | ; Set base address of erase block       |

| DISI         | #5                                   | ; Block all interrupts with priority <7 |

|              |                                      | ; for next 5 instructions               |

| MOV          | #0x55, W0                            |                                         |

| MOV          | W0, NVMKEY                           | ; Write the 55 key                      |

| MOV          | #0xAA, W1                            | ;                                       |

| MOV          | W1, NVMKEY                           | ; Write the AA key                      |

| BSET         | NVMCON, #WR                          | ; Start the erase sequence              |

| NOP          |                                      | ; Insert two NOPs after the erase       |

| NOP          |                                      | ; command is asserted                   |

|              |                                      |                                         |

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit                                                                |

|-------|-------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Address error trap has occurred</li><li>0 = Address error trap has not occurred</li></ul> |

| bit 2 | STKERR: Stack Error Trap Status bit                                                                   |

|       | <ol> <li>Stack error trap has occurred</li> </ol>                                                     |

|       | 0 = Stack error trap has not occurred                                                                 |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit                                                    |

|       | 1 = Oscillator failure trap has occurred                                                              |

|       | 0 = Oscillator failure trap has not occurred                                                          |

| bit 0 | Unimplemented: Read as '0'                                                                            |

## REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 3 | CNIE: Input Change Notification Interrupt Enable bit |

|-------|------------------------------------------------------|

|       | 1 = Interrupt request enabled                        |

|       | 0 = Interrupt request not enabled                    |

| bit 2 | Unimplemented: Read as '0'                           |

| bit 1 | MI2C1IE: I2C1 Master Events Interrupt Enable bit     |

|       | 1 = Interrupt request enabled                        |

|       | 0 = Interrupt request not enabled                    |

|       |                                                      |

- bit 0 SI2C1IE: I2C1 Slave Events Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

## 10.2.2 IDLE MODE

Idle mode has the following features:

- The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device will wake from Idle mode on any of the following events:

- Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

## 10.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLK-DIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLK-DIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

It is also possible to use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is now placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled via the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is only enabled if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

**Note:** If a PMD bit is set, the corresponding module is disabled after a delay of 1 instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of 1 instruction cycle (assuming the module control registers are already configured to enable module operation).

| R/W-0         | U-0                               | R/W-0                                     | U-0           | U-0                     | U-0              | U-0             | U-0 |

|---------------|-----------------------------------|-------------------------------------------|---------------|-------------------------|------------------|-----------------|-----|

| TON           |                                   | TSIDL                                     | —             |                         | _                |                 | —   |

| bit 15        |                                   |                                           |               |                         |                  |                 | bit |

|               | DANO                              |                                           | DAMO          |                         | DAMA             | DAMO            |     |

| U-0           | R/W-0                             | R/W-0                                     | R/W-0         | U-0                     | R/W-0            | R/W-0           | U-0 |

|               | TGATE                             | ICKP                                      | S<1:0>        |                         | TSYNC            | TCS             |     |

| bit 7         |                                   |                                           |               |                         |                  |                 | bit |

| Legend:       |                                   |                                           |               |                         |                  |                 |     |

| R = Readabl   | e bit                             | W = Writable                              | bit           | U = Unimple             | mented bit, read | as '0'          |     |

| -n = Value at | POR                               | '1' = Bit is set                          | t             | '0' = Bit is cle        | eared            | x = Bit is unkn | own |

|               |                                   |                                           |               |                         |                  |                 |     |

| bit 15        | TON: Timer1                       | On bit                                    |               |                         |                  |                 |     |

|               | 1 = Starts 16-                    |                                           |               |                         |                  |                 |     |

|               | 0 = Stops 16-                     |                                           |               |                         |                  |                 |     |

| bit 14        | Unimplemen                        | ted: Read as '                            | 0'            |                         |                  |                 |     |

| bit 13        | TSIDL: Stop                       | in Idle Mode bi                           | t             |                         |                  |                 |     |

|               |                                   | ue module ope<br>module operat            |               | device enters lo<br>ode | dle mode         |                 |     |

| bit 12-7      | Unimplemen                        | ted: Read as                              | 0'            |                         |                  |                 |     |

| bit 6         | TGATE: Time                       | er1 Gated Time                            | Accumulatio   | n Enable bit            |                  |                 |     |

|               | When T1CS :<br>This bit is ign    |                                           |               |                         |                  |                 |     |

|               | When T1CS :                       |                                           |               |                         |                  |                 |     |

|               | 1 = Gated tim                     | ne accumulatio<br>ne accumulatio          |               |                         |                  |                 |     |

| bit 5-4       |                                   | : Timer1 Input                            |               | ale Select bits         |                  |                 |     |

|               | 11 <b>= 1:256</b>                 |                                           |               |                         |                  |                 |     |

|               | 10 <b>= 1:64</b>                  |                                           |               |                         |                  |                 |     |

|               | 01 = 1:8                          |                                           |               |                         |                  |                 |     |

| 1.11.0        | 00 = 1:1                          |                                           | - 1           |                         |                  |                 |     |

| bit 3         | -                                 | ted: Read as '                            |               |                         |                  |                 |     |

| bit 2         |                                   |                                           | ock Input Syr | hchronization S         | elect bit        |                 |     |

|               | <u>When TCS =</u><br>1 = Synchron | <u>1:</u><br>iize external clo            | ock input     |                         |                  |                 |     |

|               |                                   | nchronize external external               |               | out                     |                  |                 |     |

|               | When TCS =                        |                                           |               |                         |                  |                 |     |

|               | This bit is ign                   |                                           |               |                         |                  |                 |     |

| bit 1         | TCS: Timer1                       | Clock Source                              | Select bit    |                         |                  |                 |     |

|               | 1 = External o<br>0 = Internal c  | clock from pin <sup>·</sup><br>lock (Ecy) | T1CK (on the  | rising edge)            |                  |                 |     |

|               |                                   |                                           |               |                         |                  |                 |     |

| R/W-0        | U-0             | R/W-0                               | U-0           | U-0                       | U-0    | U-0                | U-0 |

|--------------|-----------------|-------------------------------------|---------------|---------------------------|--------|--------------------|-----|

| TON          |                 | TSIDL                               |               | —                         |        | —                  |     |

| bit 15       |                 |                                     |               |                           |        |                    | t   |

| U-0          | R/W-0           | R/W-0                               | R/W-0         | R/W-0                     | U-0    | R/W-0              | U-0 |

|              | TGATE           | -                                   | S<1:0>        | T32                       |        | TCS <sup>(1)</sup> | 0-0 |

| bit 7        | TOAL            | TOR                                 | 0 1.02        | 102                       |        | 100                |     |

|              |                 |                                     |               |                           |        |                    |     |

| Legend:      |                 |                                     |               |                           |        |                    |     |

| R = Readab   |                 | W = Writable                        |               | U = Unimplem              |        |                    |     |

| -n = Value a | t POR           | '1' = Bit is set                    |               | '0' = Bit is clea         | ared   | x = Bit is unkn    | own |

| bit 15       | TON: Timer      | ( On hit                            |               |                           |        |                    |     |

| 011 15       | When T32 =      |                                     |               |                           |        |                    |     |

|              |                 | <br>2-bit Timerx/y                  |               |                           |        |                    |     |

|              |                 | 2-bit Timerx/y                      |               |                           |        |                    |     |

|              | When T32 =      |                                     |               |                           |        |                    |     |

|              | 1 = Starts 16   |                                     |               |                           |        |                    |     |

| L:1 4 4      | 0 = Stops 16    |                                     | ~!            |                           |        |                    |     |

| bit 14       | -               | nted: Read as '                     |               |                           |        |                    |     |

| bit 13       |                 | in Idle Mode bi                     |               | device enterne Idl.       | - made |                    |     |

|              |                 | e module operat                     |               | device enters Idle<br>ode | emode  |                    |     |

| bit 12-7     |                 | nted: Read as                       |               |                           |        |                    |     |

| bit 6        | -               | erx Gated Time                      |               | n Enable bit              |        |                    |     |

|              | When TCS =      | = 1:                                |               |                           |        |                    |     |

|              | This bit is igr | nored                               |               |                           |        |                    |     |

|              | When TCS =      |                                     |               |                           |        |                    |     |

|              |                 | ne accumulatio<br>ne accumulatio    |               |                           |        |                    |     |

| bit 5-4      |                 | Timerx Input                        |               | ala Salact hits           |        |                    |     |

| DIL 3-4      | 11 = 1:256      | Timerx input                        | CIUCK I TESCE |                           |        |                    |     |

|              | 10 = 1:64       |                                     |               |                           |        |                    |     |

|              | 01 <b>= 1:8</b> |                                     |               |                           |        |                    |     |

|              | 00 = 1:1        |                                     |               |                           |        |                    |     |

| bit 3        |                 | Timer Mode Sel                      |               |                           |        |                    |     |

|              |                 | and Timery form<br>and Timery act a | Ų             |                           |        |                    |     |

| bit 2        |                 | nted: Read as '                     |               |                           |        |                    |     |

| bit 1        | =               | Clock Source                        |               |                           |        |                    |     |

|              | 1 = External    | clock from pin                      |               | rising edge)              |        |                    |     |

|              | 0 = Internal    |                                     |               |                           |        |                    |     |

#### Note 1: The TxCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

### REGISTER 16-1: PXTCON: PWM TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| PTEN   | —   | PTSIDL | —   | —   | —   | —   | —     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0      | R/W-0 |

|------------|-------|-------|-------|-------------|-------|------------|-------|

| PTOPS<3:0> |       |       |       | PTCKPS<1:0> |       | PTMOD<1:0> |       |

| bit 7      |       |       |       |             |       |            | bit 0 |

| Legend:                           |                                                                                                                                 |                               |                               |  |  |  |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|--|--|--|--|

| R = Readable bit W = Writable bit |                                                                                                                                 | U = Unimplemented bit,        | read as '0'                   |  |  |  |  |

| -n = Value at PC                  | R '1' = Bit is set                                                                                                              | '0' = Bit is cleared          | x = Bit is unknown            |  |  |  |  |

|                                   |                                                                                                                                 |                               |                               |  |  |  |  |

|                                   | PTEN: PWM Time Base Timer Enable                                                                                                | e bit                         |                               |  |  |  |  |

|                                   | <ul> <li>= PWM time base is on</li> <li>= PWM time base is off</li> </ul>                                                       |                               |                               |  |  |  |  |

| bit 14                            | Jnimplemented: Read as '0'                                                                                                      |                               |                               |  |  |  |  |

| bit 13                            | PTSIDL: PWM Time Base Stop in Idle                                                                                              | e Mode bit                    |                               |  |  |  |  |

|                                   | <ul> <li>1 = PWM time base halts in CPU Idle mode</li> <li>0 = PWM time base runs in CPU Idle mode</li> </ul>                   |                               |                               |  |  |  |  |

| bit 12-8                          | Unimplemented: Read as '0'                                                                                                      |                               |                               |  |  |  |  |

| bit 7-4                           | PTOPS<3:0>: PWM Time Base Outp                                                                                                  | ut Postscale Select bits      |                               |  |  |  |  |

|                                   | 1111 = 1:16 postscale                                                                                                           |                               |                               |  |  |  |  |

|                                   | •                                                                                                                               |                               |                               |  |  |  |  |

|                                   | •                                                                                                                               |                               |                               |  |  |  |  |

|                                   | •                                                                                                                               |                               |                               |  |  |  |  |

|                                   | 0001 = 1:2 postscale<br>0000 = 1:1 postscale                                                                                    |                               |                               |  |  |  |  |

| bit 3-2                           | PTCKPS<1:0>: PWM Time Base Inpu                                                                                                 | ut Clock Prescale Select bits |                               |  |  |  |  |

|                                   | 11 = PWM time base input clock period                                                                                           | od is 64 Tcy (1:64 prescale)  |                               |  |  |  |  |

|                                   | L0 = PWM time base input clock period                                                                                           |                               |                               |  |  |  |  |

|                                   | <ul> <li>D1 = PWM time base input clock period</li> <li>D0 = PWM time base input clock period</li> </ul>                        |                               |                               |  |  |  |  |

|                                   | PTMOD<1:0>: PWM Time Base Mod                                                                                                   | ,                             |                               |  |  |  |  |

|                                   | <ul> <li>FINOD (1.02, FWM) Time base model</li> <li>11 = PWM time base operates in a Construction of the pwm updates</li> </ul> |                               | de with interrupts for double |  |  |  |  |

|                                   | L0 = PWM time base operates in a Co                                                                                             | ontinuous Up/Down Count mo    | de                            |  |  |  |  |

|                                   | 1 = PWM time base operates in Sing                                                                                              | -                             |                               |  |  |  |  |

|                                   | 00 = PWM time base operates in a Fr                                                                                             | ee-Running mode               |                               |  |  |  |  |

## REGISTER 16-4: PxSECMP: SPECIAL EVENT COMPARE REGISTER

| R/W-0                                                                                                                                                                                              | R/W-0                                                                        | R/W-0                        | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------|-------|------------------------------------|-------|--------------------|-------|--|--|

| SEVTDIR <sup>(1)</sup>                                                                                                                                                                             |                                                                              | SEVTCMP<14:8> <sup>(2)</sup> |       |                                    |       |                    |       |  |  |

| bit 15                                                                                                                                                                                             | ·                                                                            |                              |       |                                    |       |                    | bit 8 |  |  |

| R/W-0                                                                                                                                                                                              | R/W-0                                                                        | R/W-0                        | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

|                                                                                                                                                                                                    |                                                                              |                              | SEVTC | MP<7:0> <sup>(2)</sup>             |       |                    |       |  |  |

| bit 7                                                                                                                                                                                              |                                                                              |                              |       |                                    |       |                    | bit 0 |  |  |

| Legend:                                                                                                                                                                                            |                                                                              |                              |       |                                    |       |                    |       |  |  |

| •                                                                                                                                                                                                  | R = Readable bit W = Writable bit                                            |                              | it    | U = Unimplemented bit, read as '0' |       |                    |       |  |  |

| -n = Value at POR                                                                                                                                                                                  |                                                                              | '1' = Bit is set             |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |  |

|                                                                                                                                                                                                    |                                                                              |                              |       |                                    |       |                    |       |  |  |

| bit 15                                                                                                                                                                                             | bit 15 SEVTDIR: Special Event Trigger Time Base Direction bit <sup>(1)</sup> |                              |       |                                    |       |                    |       |  |  |

| <ul> <li>1 = A Special Event Trigger will occur when the PWM time base is counting downwards</li> <li>0 = A Special Event Trigger will occur when the PWM time base is counting upwards</li> </ul> |                                                                              |                              |       |                                    |       |                    | s     |  |  |

bit 14-0 SEVTCMP<14:0>: Special Event Compare Value bits<sup>(2)</sup>

Note 1: SEVTDIR is compared with PTDIR (PTMR<15>) to generate the Special Event Trigger.

2: SEVTCMP<14:0> is compared with PTMR<14:0> to generate the Special Event Trigger.

| R/W-0        | R-0                                                                                                                                                                                        | R-0                               | R-0                           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------|------------------|------------------|-----------------|---------|--|--|

| TXENn        | TXABTn                                                                                                                                                                                     | TXLARBn                           | TXERRn                        | TXREQn           | RTRENn           | TXnPR           |         |  |  |

| bit 15       | 170 B H                                                                                                                                                                                    | TYCE/ (I CDI)                     | INERG                         |                  |                  |                 | bit     |  |  |

|              |                                                                                                                                                                                            |                                   |                               |                  |                  |                 |         |  |  |

| R/W-0        | R-0                                                                                                                                                                                        | R-0                               | R-0                           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |

| TXENm        | TXABTm <sup>(1)</sup>                                                                                                                                                                      | TXLARBm <sup>(1)</sup>            | TXERRm <sup>(1)</sup>         | TXREQm           | RTRENm           | TXmPF           | RI<1:0> |  |  |

| bit 7        |                                                                                                                                                                                            | 1                                 |                               |                  |                  |                 | bit     |  |  |

| Legend:      |                                                                                                                                                                                            |                                   |                               |                  |                  |                 |         |  |  |

| R = Readab   | le bit                                                                                                                                                                                     | W = Writable                      | bit                           | U = Unimpler     | nented bit, read | as '0'          |         |  |  |

| -n = Value a | t POR                                                                                                                                                                                      | '1' = Bit is set                  |                               | '0' = Bit is cle | ared             | x = Bit is unkn | iown    |  |  |

|              |                                                                                                                                                                                            |                                   |                               |                  |                  |                 |         |  |  |

| bit 15-8     |                                                                                                                                                                                            | n for Bits 7-0,                   |                               | fer n            |                  |                 |         |  |  |

| bit 7        |                                                                                                                                                                                            | RX Buffer Sele                    |                               |                  |                  |                 |         |  |  |

|              |                                                                                                                                                                                            | Bn is a transm                    |                               |                  |                  |                 |         |  |  |

| bit 6        | <ul> <li>0 = Buffer TRBn is a receive buffer</li> <li>TXABTm: Message Aborted bit<sup>(1)</sup></li> </ul>                                                                                 |                                   |                               |                  |                  |                 |         |  |  |

|              |                                                                                                                                                                                            | 1 = Message was aborted           |                               |                  |                  |                 |         |  |  |

|              | 0                                                                                                                                                                                          | completed tra                     | nsmission suc                 | cessfully        |                  |                 |         |  |  |

| bit 5        | TXLARBm:                                                                                                                                                                                   | Message Lost                      | Arbitration bit <sup>(1</sup> | )                |                  |                 |         |  |  |

|              |                                                                                                                                                                                            | lost arbitration                  |                               |                  |                  |                 |         |  |  |

|              | •                                                                                                                                                                                          | did not lose ar                   |                               | •                |                  |                 |         |  |  |

| bit 4        |                                                                                                                                                                                            | rror Detected D                   |                               |                  | a                |                 |         |  |  |

|              |                                                                                                                                                                                            | or occurred wh<br>or did not occu | •                             | •                |                  |                 |         |  |  |

| bit 3        | <ul> <li>0 = A bus error did not occur while the message was being sent</li> <li>TXREQm: Message Send Request bit</li> </ul>                                                               |                                   |                               |                  |                  |                 |         |  |  |

|              | Setting this bit to '1' requests sending a message. The bit will automatically clear when the messag is successfully sent. Clearing the bit to '0' while set will request a message abort. |                                   |                               |                  |                  |                 |         |  |  |

| bit 2        | <b>RTRENm:</b> Auto-Remote Transmit Enable bit                                                                                                                                             |                                   |                               |                  |                  |                 |         |  |  |

|              | 1 = When a remote transmit is received, TXREQ will be set                                                                                                                                  |                                   |                               |                  |                  |                 |         |  |  |

|              | 0 = When a remote transmit is received, TXREQ will be unaffected                                                                                                                           |                                   |                               |                  |                  |                 |         |  |  |

| bit 1-0      | TXmPRI<1:0                                                                                                                                                                                 | >: Message Tr                     | ransmission Pr                | iority bits      |                  |                 |         |  |  |

|              |                                                                                                                                                                                            | message prior                     |                               |                  |                  |                 |         |  |  |

|              |                                                                                                                                                                                            | ermediate mes                     |                               |                  |                  |                 |         |  |  |

|              |                                                                                                                                                                                            | rmediate mess                     | nan nriarity                  |                  |                  |                 |         |  |  |

REGISTER 21-26: CiTRmnCON: ECAN™ TX/RX BUFFER m CONTROL REGISTER (m = 0,2,4,6; n =

Note 1: This bit is cleared when TXREQ is set.

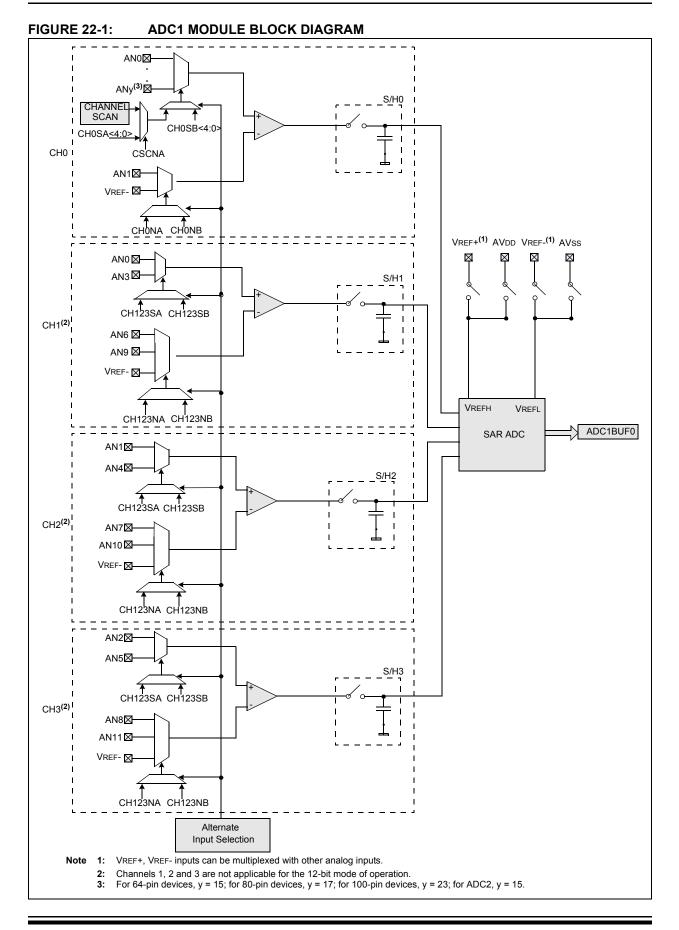

| CH0NB<br>bit 15<br>R/W-0<br>CH0NA | U-0                                                                                                                         | _                                                                                                     |                                                            |                  | CH0SB<4:0>          | >                  |       |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------|---------------------|--------------------|-------|--|

| R/W-0<br>CH0NA                    | U-0                                                                                                                         |                                                                                                       |                                                            |                  |                     |                    |       |  |

| CH0NA                             | U-0                                                                                                                         |                                                                                                       |                                                            |                  |                     |                    | bit 8 |  |

| CHONA                             | 0-0                                                                                                                         |                                                                                                       |                                                            | DAMO             |                     | DAMO               |       |  |

|                                   |                                                                                                                             | U-0                                                                                                   | R/W-0                                                      | R/W-0            | R/W-0<br>CH0SA<4:0> | R/W-0              | R/W-0 |  |

| oit 7                             | —                                                                                                                           | _                                                                                                     |                                                            |                  | CH03A54.02          | -                  | bit ( |  |

|                                   |                                                                                                                             |                                                                                                       |                                                            |                  |                     |                    |       |  |

| Legend:                           |                                                                                                                             |                                                                                                       |                                                            |                  |                     |                    |       |  |

| R = Readable                      | e bit                                                                                                                       | W = Writable b                                                                                        | bit                                                        | U = Unimpler     | mented bit, rea     | ad as '0'          |       |  |

| -n = Value at I                   | POR                                                                                                                         | '1' = Bit is set                                                                                      |                                                            | '0' = Bit is cle | ared                | x = Bit is unknown |       |  |

| bit 12-8<br>bit 7                 |                                                                                                                             | n as bit<4:0>.<br>inel 0 Negative<br>negative input                                                   | Input Select f                                             |                  |                     |                    |       |  |

| bit 6-5                           | 0 = Channel 0<br>Unimplement                                                                                                | negative input                                                                                        |                                                            |                  |                     |                    |       |  |

| bit 4-0                           | CH0SA<4:0>:                                                                                                                 |                                                                                                       |                                                            | lect for Sample  | e A bits            |                    |       |  |

|                                   | 11111 = Char<br>11110 = Char<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | anel 0 positive i<br>anel 0 positive i<br>anel 0 positive i<br>anel 0 positive i<br>anel 0 positive i | nput is AN31<br>nput is AN30<br>nput is AN2<br>nput is AN1 |                  |                     |                    |       |  |

## REGISTER 22-6: ADxCHS0: ADCx INPUT CHANNEL 0 SELECT REGISTER

**Note:** ADC2 can only select AN0-AN15 as positive inputs.

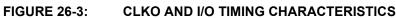

| AC CHARACTERISTICS |        |                         | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                    |     |       |            |   |  |

|--------------------|--------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|---|--|

| Param<br>No.       | Symbol | Characterist            | Min                                                                                                                                                 | Typ <sup>(1)</sup> | Max | Units | Conditions |   |  |

| DO31               | TIOR   | Port Output Rise Time   | Port Output Rise Time                                                                                                                               |                    |     | 25    | ns         | _ |  |

| DO32               | TIOF   | Port Output Fall Time   |                                                                                                                                                     | 10                 | 25  | ns    | _          |   |  |

| DI35               | TINP   | INTx Pin High or Low Ti | 20                                                                                                                                                  |                    |     | ns    | _          |   |  |

| DI40               | Trbp   | CNx High or Low Time (  | 2                                                                                                                                                   | _                  | _   | TCY   | _          |   |  |

## TABLE 26-20: I/O TIMING REQUIREMENTS

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

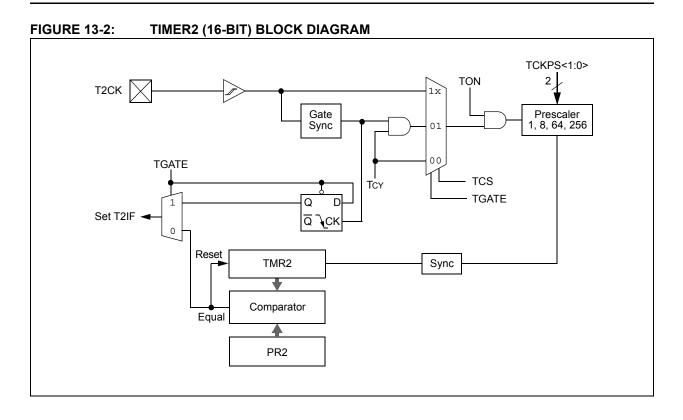

## TABLE 26-23: TIMER2, TIMER4, TIMER6 AND TIMER8 EXTERNAL CLOCK TIMING REQUIREMENTS

|              |                |                                          |                                                                | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                                         |     |         |       |                               |

|--------------|----------------|------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|---------|-------|-------------------------------|

| Param<br>No. | Symbol         | Charact                                  | eristic                                                        |                                                                                                                                                 | Min                                     | Тур | Мах     | Units | Conditions                    |

| TB10         | TtxH           | TxCK High Time                           | Synchronous,<br>no prescaler<br>Synchronous,<br>with prescaler |                                                                                                                                                 | 0.5 TCY + 20                            |     | _       | ns    | Must also meet parameter TB15 |

|              |                |                                          |                                                                |                                                                                                                                                 | 10                                      | _   | —       | ns    |                               |

| TB11         | TtxL           | TxCK Low Time                            | Synchronous,<br>no prescaler<br>Synchronous,<br>with prescaler |                                                                                                                                                 | 0.5 TCY + 20                            | _   | —       | ns    | Must also meet parameter TB15 |

|              |                |                                          |                                                                |                                                                                                                                                 | 10                                      | _   | —       | ns    |                               |

| TB15         | TtxP           | TxCK Input<br>Period                     | Synchronous,<br>no prescaler<br>Synchronous,<br>with prescaler |                                                                                                                                                 | TCY + 40                                | _   | —       | ns    | N = prescale<br>value         |

|              |                |                                          |                                                                |                                                                                                                                                 | Greater of:<br>20 ns or<br>(Tcy + 40)/N |     |         |       | (1, 8, 64, 256)               |

| TB20         | TCKEXT-<br>MRL | Delay from Externa<br>Edge to Timer Incr |                                                                |                                                                                                                                                 | 0.5 TCY                                 | _   | 1.5 TCY |       | —                             |

## TABLE 26-24:TIMER3, TIMER5, TIMER7 AND TIMER9 EXTERNAL CLOCK TIMING<br/>REQUIREMENTS

|              |           |                                           |                              | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                                         |     |            |       |                               |

|--------------|-----------|-------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|------------|-------|-------------------------------|

| Param<br>No. | Symbol    | Characte                                  | Characteristic               |                                                                                                                                                         |                                         | Тур | Max        | Units | Conditions                    |