Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

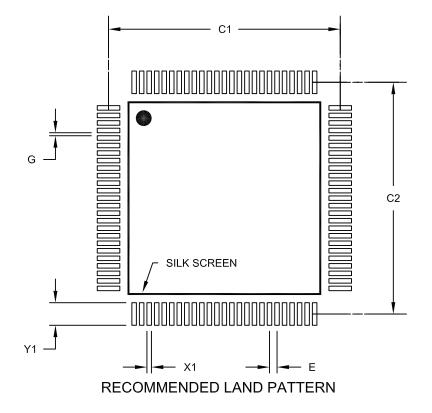

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc506-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

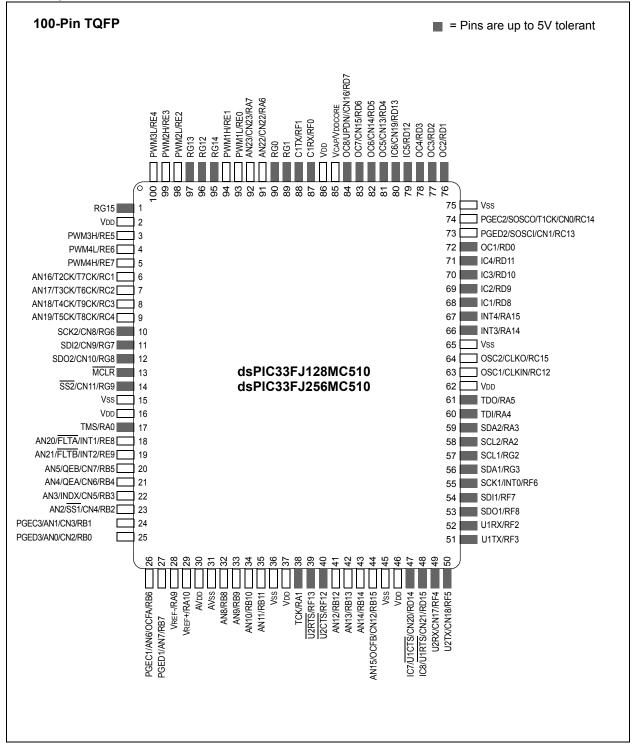

### Pin Diagrams (Continued)

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                             |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                           |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                   |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                     |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = An operation which affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation which affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                   |

| bit 0   | <b>C:</b> MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                        |

- Note 1: This bit may be read or cleared (not set).

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 3. "Data Memory" (DS70202) and Section 4. "Program Memory" (DS70203) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJXXXMCX06/X08/X10 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 Program Address Space

The program address memory space of the dsPIC33FJXXXMCX06/X08/X10 devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.6 "Interfacing Program and Data Memory Spaces".

User access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space. Memory usage for the dsPIC33FJXXXMCX06/X08/X10 family of devices is shown in Figure 4-1.

|                            | dsPIC33FJ64MCXXX                                   | dsPIC33FJ128MCXXX                 | dsPIC33FJ256MCXXX      |                                  |

|----------------------------|----------------------------------------------------|-----------------------------------|------------------------|----------------------------------|

| Ā                          | GOTO Instruction                                   | GOTO Instruction                  |                        | )x000000<br>)x000002             |

|                            | Reset Address                                      | Reset Address                     | - Reset Address        | )x000002                         |

|                            | Interrupt Vector Table                             | Interrupt Vector Table            | Interrupt Vector Table | 0x0000FE                         |

|                            | Reserved                                           | Reserved                          | Reserved               | 0x000100                         |

|                            | Alternate Vector Table                             | Alternate Vector Table            | Alternate vector rable | 0x000104<br>0x0001FE             |

| pace                       | User Program<br>Flash Memory<br>(22K instructions) | User Program<br>Flash Memory      | User Program           | )x000200<br>)x00ABFE             |

| User Memory Space          |                                                    | (44K instructions)                | (88K instructions)     | 0x00AC00                         |

| ser Me                     |                                                    |                                   |                        | 0x0157FE<br>0x015800             |

| Ï                          | Unimplemented<br>(Read '0's)                       | Unimplemented                     |                        | 004555                           |

|                            |                                                    | (Read 'o's)                       |                        | 0x02ABFE<br>0x02AC00             |

|                            |                                                    |                                   | Unimplemented          |                                  |

|                            |                                                    |                                   | (Read '0's)            |                                  |

| •                          |                                                    |                                   | , ,                    | x7FFFFE                          |

|                            |                                                    |                                   |                        | 0x800000                         |

|                            | Reserved                                           | Reserved                          | Reserved               |                                  |

| Space                      | Device Configuration<br>Registers                  | Device Configuration<br>Registers |                        | )xF7FFFE<br>)xF80000<br>)xF80017 |

| emory (                    |                                                    |                                   |                        | )xF80017<br>)xF80010             |

| Configuration Memory Space | Reserved                                           | Reserved                          | Reserved               |                                  |

| Config                     | · · ·                                              |                                   |                        | )xFEFFFE<br>)xFF0000             |

| ₩                          | DEVID (2)                                          | DEVID (2)                         | D = V D (2)            | )xFFFFFE                         |

| Note:                      | Memory areas are not show                          |                                   |                        |                                  |

#### FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33FJXXXMCX06/X08/X10 DEVICES

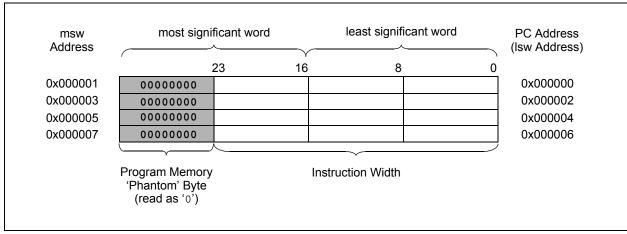

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJXXXMCX06/X08/X10 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJXXXMCX06/X08/X10 devices also have two interrupt vector tables located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table"**.

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| Addressing Mode                        | Description                                                                                            |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| File Register Direct                   | The address of the file register is specified explicitly.                                              |  |  |

| Register Direct                        | The contents of a register are accessed directly.                                                      |  |  |

| Register Indirect                      | The contents of Wn forms the EA.                                                                       |  |  |

| Register Indirect Post-Modified        | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |  |  |

| Register Indirect Pre-Modified         | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |  |  |

| Register Indirect with Register Offset | The sum of Wn and Wb forms the EA.                                                                     |  |  |

| Register Indirect with Literal Offset  | The sum of Wn and a literal forms the EA.                                                              |  |  |

#### TABLE 4-36: FUNDAMENTAL ADDRESSING MODES SUPPORTED

#### 4.3.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the Addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the Addressing     |

|-------|----------------------------------------------|

|       | mode specified in the instruction can differ |

|       | for the source and destination EA.           |

|       | However, the 4-bit Wb (Register Offset)      |

|       | field is shared between both source and      |

|       | destination (but typically only used by      |

|       | one).                                        |

In summary, the following Addressing modes are supported by move and accumulator instructions:

- Register Direct

- · Register Indirect

- Register Indirect Post-modified

- · Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

| Note: | Not    | all   | instructions  | support     | all   | the   |

|-------|--------|-------|---------------|-------------|-------|-------|

|       | Addr   | essii | ng modes give | n above. I  | ndivi | idual |

|       | instru | uctio | ns may suppo  | rt differen | t sub | sets  |

|       | of the | ese / | Addressing mo | odes.       |       |       |

#### 4.3.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of addressing modes to allow the user to effectively manipulate the data pointers through register indirect tables.

The 2-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU and W10 and W11 will always be directed to the Y AGU. The effective addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

| Note: | Register   | Indirect  | with    | Register  | Offset |

|-------|------------|-----------|---------|-----------|--------|

|       | Addressir  | ng mode i | s only  | available | for W9 |

|       | (in X spac | ce) and W | /11 (in | Y space). |        |

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- · Register Indirect with Register Offset (Indexed)

#### 4.3.5 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

### 4.4 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing

| FIGURE 7-1: | dsPIC33FJXXXMCX06/X08/X10 INTERRUPT VECTOR TABLE |

|-------------|--------------------------------------------------|

|             |                                                  |

| 1                                 |                                      | -                    |                                                        |

|-----------------------------------|--------------------------------------|----------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction             | 0x000000             |                                                        |

|                                   | Reset – GOTO Address                 | 0x000002             |                                                        |

|                                   | Reserved                             | 0x000004             |                                                        |

|                                   | Oscillator Fail Trap Vector          |                      |                                                        |

|                                   | Address Error Trap Vector            |                      |                                                        |

|                                   | Stack Error Trap Vector              |                      |                                                        |

|                                   | Math Error Trap Vector               |                      |                                                        |

|                                   | DMA Error Trap Vector                | _                    |                                                        |

|                                   | Reserved                             | _                    |                                                        |

|                                   | Reserved                             |                      |                                                        |

|                                   | Interrupt Vector 0                   | 0x000014 —           | 1                                                      |

|                                   | Interrupt Vector 1                   | _                    |                                                        |

|                                   | ~                                    | _                    |                                                        |

|                                   | ~                                    | -                    |                                                        |

|                                   | ~                                    |                      |                                                        |

|                                   | Interrupt Vector 52                  | 0x00007C             | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| >                                 | Interrupt Vector 53                  | 0x00007E             |                                                        |

| orit                              | Interrupt Vector 54                  | 0x000080             |                                                        |

| Dric                              | ~                                    | _                    |                                                        |

| er                                | ~                                    | -                    |                                                        |

| Decreasing Natural Order Priority |                                      |                      |                                                        |

| a                                 | Interrupt Vector 116                 | 0x0000FC<br>0x0000FE |                                                        |

| tura                              | Interrupt Vector 117                 | 0x0000FE             | _                                                      |

| Nai                               | Reserved<br>Reserved                 | 0x000100<br>0x000102 |                                                        |

| βĽ                                | Reserved                             | 0000102              |                                                        |

| asii                              | Oscillator Fail Trap Vector          | -                    |                                                        |

| crea                              | Address Error Trap Vector            | -                    |                                                        |

| Oec                               | Stack Error Trap Vector              | -                    |                                                        |

| -                                 | Math Error Trap Vector               | -                    |                                                        |

|                                   | DMA Error Trap Vector                | -                    |                                                        |

|                                   | Reserved                             | -                    |                                                        |

|                                   | Reserved                             | -                    |                                                        |

|                                   | Interrupt Vector 0                   | 0x000114 —           | -                                                      |

|                                   | Interrupt Vector 1                   |                      |                                                        |

|                                   | ~                                    |                      |                                                        |

|                                   | ~                                    | 1                    |                                                        |

|                                   | ~                                    | 1                    | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52                  | 0x00017C             | , ,                                                    |

|                                   | Interrupt Vector 53                  | 0x00017E             |                                                        |

|                                   | Interrupt Vector 54                  | 0x000180             |                                                        |

|                                   | ~                                    |                      |                                                        |

|                                   | ~                                    | 1                    |                                                        |

|                                   | ~                                    | 1                    |                                                        |

|                                   | Interrupt Vector 116                 | ]                    |                                                        |

| ↓ U                               | Interrupt Vector 117                 | 0x0001FE -           | 1                                                      |

| V                                 | Start of Code                        | 0x000200             |                                                        |

|                                   |                                      |                      |                                                        |

|                                   |                                      |                      |                                                        |

| Note 1: S                         | ee Table 7-1 for the list of impleme | anted interrupt      | (ectors                                                |

| Note T: S                         |                                      | enteu interrupt v    |                                                        |

|                                   |                                      |                      |                                                        |

### 7.3 Interrupt Control and Status Registers

dsPIC33FJXXXMCX06/X08/X10 devices implement a total of 30 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS4

- IEC0 through IEC4

- IPC0 through IPC17

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

The IFS registers maintain all of the interrupt request flags. Each source of interrupt has a Status bit, which is set by the respective peripherals or external signal and is cleared via software.

The IEC registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals. The IPC registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into vector number (VECNUM<6:0>) and Interrupt level (ILR<3:0>) bit fields in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having vector number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The CPU STATUS register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU interrupt priority level. The user can change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-32 in the following pages.

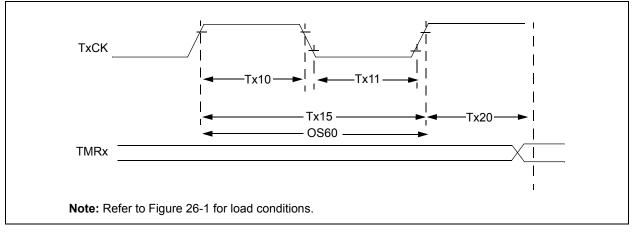

#### REGISTER 13-2: TyCON (T3CON, T5CON, T7CON OR T9CON) CONTROL REGISTER

| R/W-0              | U-0 | R/W-0                | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|----------------------|-----|-----|-----|-----|-------|

| TON <sup>(1)</sup> | —   | TSIDL <sup>(2)</sup> | _   | —   | —   | —   | —     |

| bit 15             |     |                      |     |     |     |     | bit 8 |

| U-0   | R/W-0                | R/W-0 | R/W-0                | U-0 | U-0 | R/W-0                | U-0   |

|-------|----------------------|-------|----------------------|-----|-----|----------------------|-------|

| —     | TGATE <sup>(1)</sup> | TCKPS | <1:0> <sup>(1)</sup> | —   | —   | TCS <sup>(1,3)</sup> | —     |

| bit 7 |                      |       |                      |     |     |                      | bit 0 |

| Legend:                                                           |                                           |                                              |                                      |               |

|-------------------------------------------------------------------|-------------------------------------------|----------------------------------------------|--------------------------------------|---------------|

| R = Readable bitW = Writable bit-n = Value at POR'1' = Bit is set |                                           | W = Writable bit                             | U = Unimplemented bit,               | , read as '0' |

|                                                                   |                                           | '0' = Bit is cleared                         | x = Bit is unknown                   |               |

| bit 15                                                            | TON: Tim                                  | ery On bit <sup>(1)</sup>                    |                                      |               |

|                                                                   |                                           | 16-bit Timery<br>16-bit Timery               |                                      |               |

| bit 14                                                            | Unimpler                                  | nented: Read as '0'                          |                                      |               |

| bit 13                                                            | TSIDL: St                                 | op in Idle Mode bit <sup>(2)</sup>           |                                      |               |

|                                                                   |                                           | ntinue module operation who                  | en device enters Idle mode<br>e mode |               |

| bit 12-7                                                          | Unimpler                                  | nented: Read as '0'                          |                                      |               |

| bit 6                                                             | TGATE: 1                                  | imery Gated Time Accumu                      | lation Enable bit <sup>(1)</sup>     |               |

|                                                                   | When TC<br>This bit is                    |                                              |                                      |               |

|                                                                   | $\frac{\text{When TC}}{1 = \text{Gates}}$ | <u>S = 0:</u><br>I time accumulation enabled | 4                                    |               |

|                                                                   |                                           | time accumulation disable                    |                                      |               |

| bit 5-4                                                           | TCKPS<1                                   | I:0>: Timer3 Input Clock Pr                  | escale Select bits <sup>(1)</sup>    |               |

|                                                                   | 11 <b>= 1:25</b>                          | 6                                            |                                      |               |

|                                                                   | 10 <b>= 1:64</b>                          |                                              |                                      |               |

|                                                                   | 01 = 1:8<br>00 = 1:1                      |                                              |                                      |               |

| bit 3-2                                                           |                                           | nented: Read as '0'                          |                                      |               |

| bit 1                                                             | •                                         | ery Clock Source Select bit                  | (1.3)                                |               |

|                                                                   |                                           | nal clock from pin TyCK (on                  |                                      |               |

|                                                                   |                                           | al clock (FCY)                               | the hong edge                        |               |

| bit 0                                                             | Unimpler                                  |                                              |                                      |               |

- 2: When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

- 3: The TyCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

## 14.1 Input Capture Registers

#### REGISTER 14-1: ICxCON: INPUT CAPTURE x CONTROL REGISTER

| U-0                  | U-0                                                                                                    | R/W-0                                                                                                                                         | U-0                                                                                                               | U-0                           | U-0             | U-0                    | U-0   |

|----------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------|------------------------|-------|

| —                    | _                                                                                                      | ICSIDL                                                                                                                                        |                                                                                                                   |                               | _               | _                      | —     |

| bit 15               |                                                                                                        |                                                                                                                                               |                                                                                                                   |                               |                 |                        | bit   |

|                      |                                                                                                        |                                                                                                                                               |                                                                                                                   |                               |                 |                        |       |

| R/W-0                | R/W-0                                                                                                  | R/W-0                                                                                                                                         | R-0, HC                                                                                                           | R-0, HC                       | R/W-0           | R/W-0                  | R/W-0 |

| ICTMR <sup>(1)</sup> | ICI<                                                                                                   | <1:0>                                                                                                                                         | ICOV                                                                                                              | ICBNE                         |                 | ICM<2:0>               |       |

| bit 7                |                                                                                                        |                                                                                                                                               |                                                                                                                   |                               |                 |                        | bit   |

| Legend:              |                                                                                                        |                                                                                                                                               |                                                                                                                   |                               |                 |                        |       |

| R = Readable         | e bit                                                                                                  | W = Writable                                                                                                                                  | bit                                                                                                               | U = Unimplen                  | nented bit, rea | d as '0'               |       |

| -n = Value at        | POR                                                                                                    | '1' = Bit is set                                                                                                                              | :                                                                                                                 | '0' = Bit is clea             | ared            | x = Bit is unkn        | own   |

|                      |                                                                                                        |                                                                                                                                               |                                                                                                                   |                               |                 |                        |       |

| bit 15-14            | Unimplemer                                                                                             | nted: Read as '                                                                                                                               | 0'                                                                                                                |                               |                 |                        |       |

| bit 13               | ICSIDL: Inpu                                                                                           | t Capture Mod                                                                                                                                 | ule Stop in Idle                                                                                                  | e Control bit                 |                 |                        |       |

|                      |                                                                                                        | ture module wi                                                                                                                                |                                                                                                                   |                               |                 |                        |       |

|                      | • •                                                                                                    |                                                                                                                                               |                                                                                                                   | operate in CPU                | Idle mode       |                        |       |

| bit 12-8             | -                                                                                                      | ted: Read as                                                                                                                                  |                                                                                                                   |                               |                 |                        |       |

| bit 7                |                                                                                                        | t Capture Time                                                                                                                                |                                                                                                                   |                               |                 |                        |       |

|                      |                                                                                                        | ntents are capt<br>ntents are capt                                                                                                            | •                                                                                                                 |                               |                 |                        |       |

| bit 6-5              | ICI<1:0>: Se                                                                                           | lect Number of                                                                                                                                | Captures per                                                                                                      | Interrupt bits                |                 |                        |       |

|                      | 10 = Interrup                                                                                          | t on every four<br>t on every third<br>t on every seco                                                                                        | capture even                                                                                                      | t                             |                 |                        |       |

|                      |                                                                                                        | t on every capt                                                                                                                               |                                                                                                                   |                               |                 |                        |       |

| bit 4                | ICOV: Input (                                                                                          | Capture Overflo                                                                                                                               | ow Status Flag                                                                                                    | bit (read-only)               |                 |                        |       |

|                      |                                                                                                        | ture overflow c<br>capture overflo                                                                                                            |                                                                                                                   |                               |                 |                        |       |

| bit 3                | ICBNE: Input                                                                                           | t Capture Buffe                                                                                                                               | r Empty Statu                                                                                                     | s bit (read-only              | )               |                        |       |

|                      |                                                                                                        | ture buffer is n<br>ture buffer is e                                                                                                          |                                                                                                                   | ast one more c                | apture value o  | an be read             |       |

| bit 2-0              | ICM<2:0>: In                                                                                           | put Capture M                                                                                                                                 | ode Select bits                                                                                                   | 6                             |                 |                        |       |

|                      | (Risin,<br>110 = Unuse<br>101 = Captur<br>100 = Captur<br>011 = Captur<br>010 = Captur<br>001 = Captur | g edge detect o<br>d (module disa<br>re mode, every<br>re mode, every<br>re mode, every<br>re mode, every<br>re mode, every<br>re mode, every | only, all other o<br>bled)<br>16th rising edg<br>4th rising edge<br>rising edge<br>falling edge<br>edge (rising a | control bits are<br>lge<br>le | not applicable  | eep or Idle mode<br>.) | •     |

Note 1: Timer selections may vary. Refer to the device data sheet for details.

#### REGISTER 16-1: PXTCON: PWM TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| PTEN   | —   | PTSIDL | —   | —   | —   | —   | —     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0    | R/W-0   | R/W-0 | R/W-0  |

|-------|-------|---------|-------|----------|---------|-------|--------|

|       | PTOPS | \$<3:0> |       | PTCK     | PS<1:0> | PTMO  | D<1:0> |

| bit 7 |       |         |       | <u>.</u> |         |       | bit 0  |

| Legend:       |                   |                                                                  |                               |                               |

|---------------|-------------------|------------------------------------------------------------------|-------------------------------|-------------------------------|

| R = Readabl   | e bit             | W = Writable bit                                                 | U = Unimplemented bit,        | read as '0'                   |

| -n = Value at | POR               | '1' = Bit is set                                                 | '0' = Bit is cleared          | x = Bit is unknown            |

|               |                   |                                                                  |                               |                               |

| bit 15        |                   | WM Time Base Timer Enable                                        | e bit                         |                               |

|               |                   | time base is on time base is off                                 |                               |                               |

| bit 14        | Unimpler          | mented: Read as '0'                                              |                               |                               |

| bit 13        | PTSIDL:           | PWM Time Base Stop in Idle                                       | e Mode bit                    |                               |

|               |                   | time base halts in CPU Idle time base runs in CPU Idle           |                               |                               |

| bit 12-8      | Unimpler          | mented: Read as '0'                                              |                               |                               |

| bit 7-4       | PTOPS<3           | 3:0>: PWM Time Base Outp                                         | ut Postscale Select bits      |                               |

|               | 1111 <b>= 1</b> : | :16 postscale                                                    |                               |                               |

|               | •                 |                                                                  |                               |                               |

|               | •                 |                                                                  |                               |                               |

|               | •                 |                                                                  |                               |                               |

|               |                   | 2 postscale<br>1 postscale                                       |                               |                               |

| bit 3-2       | PTCKPS            | <1:0>: PWM Time Base Inpu                                        | ut Clock Prescale Select bits |                               |

|               | 11 = PWN          | M time base input clock perio                                    | od is 64 Tcy (1:64 prescale)  |                               |

|               |                   | I time base input clock perio                                    |                               |                               |

|               |                   | M time base input clock period<br>M time base input clock period |                               |                               |

| bit 1-0       |                   | 1:0>: PWM Time Base Mode                                         |                               |                               |

|               | 11 <b>= PW</b>    |                                                                  | ontinuous Up/Down Count mo    | de with interrupts for double |

|               |                   |                                                                  | ontinuous Up/Down Count mo    | de                            |

|               |                   | I time base operates in Sing                                     | -                             |                               |

|               | 00 <b>= PW</b>    | I time base operates in a Fr                                     | ee-Running mode               |                               |

#### REGISTER 16-2: PxTMR: PWM TIMER COUNT VALUE REGISTER

| R-0                                                                       | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|---------------------------------------------------------------------------|-------|--------------|-------|--------------|-----------------|-----------|-------|

| PTDIR                                                                     |       |              |       | PTMR<14:8>   | >               |           |       |

| bit 15                                                                    |       |              |       |              |                 |           | bit 8 |

| R/W-0                                                                     | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|                                                                           |       |              | PTM   | R<7:0>       |                 |           |       |

| bit 7                                                                     |       |              |       |              |                 |           | bit 0 |

|                                                                           |       |              |       |              |                 |           |       |

| Legend:                                                                   |       |              |       |              |                 |           |       |

| R = Readable                                                              | bit   | W = Writable | bit   | U = Unimpler | mented bit, rea | id as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow |       |              |       |              |                 | nown      |       |

bit 15 **PTDIR:** PWM Time Base Count Direction Status bit (read-only)

- 1 = PWM time base is counting down

- 0 = PWM time base is counting up

bit 14-0 **PTMR <14:0>:** PWM Time Base Register Count Value bits

#### REGISTER 16-3: PxTPER: PWM TIME BASE PERIOD REGISTER

| U-0                                | R/W-0 | R/W-0        | R/W-0 | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

|------------------------------------|-------|--------------|-------|-------------------|-----------------|--------------------|-------|--|

| _                                  |       |              |       | PTPER<14:8>       | >               |                    |       |  |

| bit 15                             |       |              |       |                   |                 |                    | bit 8 |  |

|                                    |       |              |       |                   |                 |                    |       |  |

| R/W-0                              | R/W-0 | R/W-0        | R/W-0 | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

|                                    |       |              | PTPE  | R<7:0>            |                 |                    |       |  |

| bit 7                              |       |              |       |                   |                 |                    | bit 0 |  |

|                                    |       |              |       |                   |                 |                    |       |  |

| Legend:                            |       |              |       |                   |                 |                    |       |  |

| R = Readable I                     | bit   | W = Writable | bit   | U = Unimplen      | nented bit, rea | d as '0'           |       |  |

| -n = Value at POR '1' = Bit is set |       |              |       | '0' = Bit is clea | ared            | x = Bit is unknown |       |  |

bit 15 Unimplemented: Read as '0'

bit 14-0 **PTPER<14:0>:** PWM Time Base Period Value bits

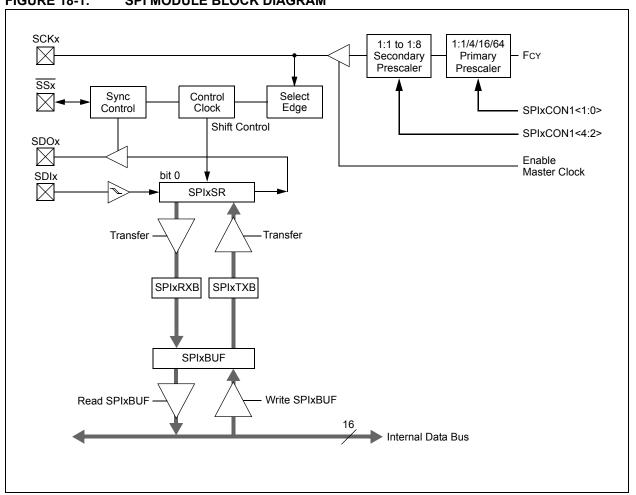

#### 18.0 SERIAL PERIPHERAL **INTERFACE (SPI)**

This data sheet summarizes the features Note: of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) in the "dsPIC33F Family Reference Manual", which is available the from Microchip web site (www.microchip.com)

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, ADC, etc. The SPI module is compatible with SPI and SIOP from Motorola®.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 or SPI2 module.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates various status conditions.

The serial interface consists of 4 pins: SDIx (serial data input), SDOx (serial data output), SCKx (shift clock input or output) and SSx (active-low slave select).

In Master mode operation, SCK is a clock output, but in Slave mode, it is a clock input.

#### SPI MODULE BLOCK DIAGRAM **FIGURE 18-1:**

#### **REGISTER 21-8:** CIEC: ECAN<sup>™</sup> TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0             | R-0 | R-0              | R-0  | R-0                | R-0           | R-0             | R-0   |

|-----------------|-----|------------------|------|--------------------|---------------|-----------------|-------|

|                 |     |                  | TERR | CNT<7:0>           |               |                 |       |

| bit 15          |     |                  |      |                    |               |                 | bit 8 |

|                 |     |                  |      |                    |               |                 |       |

| R-0             | R-0 | R-0              | R-0  | R-0                | R-0           | R-0             | R-0   |

|                 |     |                  | RERR | RCNT<7:0>          |               |                 |       |

| bit 7           |     |                  |      |                    |               |                 | bit 0 |

| Legend:         |     |                  |      |                    |               |                 |       |

| R = Readable b  | oit | W = Writable bit |      | U = Unimpleme      | ented bit, re | ad as '0'       |       |

| -n = Value at P | OR  | '1' = Bit is set |      | '0' = Bit is clear | red           | x = Bit is unkr | nown  |

bit 15-8 TERRCNT<7:0>: Transmit Error Count bits

bit 7-0 RERRCNT<7:0>: Receive Error Count bits

# 22.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Analog-to-Digital Converter (ADC)" (DS70183) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

The dsPIC33FJXXXMCX06/X08/X10 devices have up to 32 ADC input channels. These devices also have up to 2 ADC modules (ADCx, where 'x' = 1 or 2), each with its own set of Special Function Registers.

The AD12B bit (ADxCON1<10>) allows each of the ADC modules to be configured by the user as either a 10-bit, 4-sample/hold ADC (default configuration) or a 12-bit, 1-sample/hold ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

### 22.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- Up to 32 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only 1 sample/hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 32 analog input pins, designated AN0 through AN31. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other ana-

log input pins. The actual number of analog input pins and external voltage reference input configuration will depend on the specific device. Refer to the device data sheet for further details.

A block diagram of the ADC is shown in Figure 22-1.

# 22.2 ADC Initialization

The following configuration steps should be performed.

- 1. Configure the ADC module:

- a) Select port pins as analog inputs (ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- b) Select voltage reference source to match expected range on analog inputs (ADxCON2<15:13>)

- c) Select the analog conversion clock to match desired data rate with processor clock (ADxCON3<7:0>)

- d) Determine how many S/H channels will be used (ADxCON2<9:8> and ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- e) Select the appropriate sample/conversion sequence (ADxCON1<7:5> and ADxCON3<12:8>)

- f) Select how conversion results are presented in the buffer (ADxCON1<9:8>)

- g) Turn on ADC module (ADxCON1<15>)

- Configure ADC interrupt (if required):

- a) Clear the ADxIF bit

2.

b) Select ADC interrupt priority

# 22.3 ADC and DMA

If more than one conversion result needs to be buffered before triggering an interrupt, DMA data transfers can be used. Both ADC1 and ADC2 can trigger a DMA data transfer. If ADC1 or ADC2 is selected as the DMA IRQ source, a DMA transfer occurs when the AD1IF or AD2IF bit gets set as a result of an ADC1 or ADC2 sample conversion sequence.

The SMPI<3:0> bits (ADxCON2<5:2>) are used to select how often the DMA RAM buffer pointer is incremented.

The ADDMABM bit (ADxCON1<12>) determines how the conversion results are filled in the DMA RAM buffer area being used for ADC. If this bit is set, DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer. If the ADDMABM bit is cleared, then DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer.

| Bit Field   | Register | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GWRP        | FGS      | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                   |

| IESO        | FOSCSEL  | <ul> <li>Two-speed Oscillator Start-up Enable bit</li> <li>1 = Start-up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start-up device with user-selected oscillator source</li> </ul>                                                                                                                                                   |

| FNOSC<2:0>  | FOSCSEL  | Initial Oscillator Source Selection bits<br>111 = Internal Fast RC (FRC) oscillator with postscaler<br>110 = Internal Fast RC (FRC) oscillator with divide-by-16<br>101 = LPRC oscillator<br>100 = Secondary (LP) oscillator<br>011 = Primary (XT, HS, EC) oscillator with PLL<br>010 = Primary (XT, HS, EC) oscillator<br>001 = Internal Fast RC (FRC) oscillator with PLL<br>000 = FRC oscillator |

| FCKSM<1:0>  | FOSC     | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                   |

| OSCIOFNC    | FOSC     | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is clock output<br>0 = OSC2 is general purpose digital I/O pin                                                                                                                                                                                                                                                                        |

| POSCMD<1:0> | FOSC     | Primary Oscillator Mode Select bits<br>11 = Primary oscillator disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                      |

| FWDTEN      | FWDT     | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer always enabled (LPRC oscillator cannot be disabled.<br/>Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                           |

| WINDIS      | FWDT     | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                      |

| WDTPRE      | FWDT     | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                                                                                                                                                                                                                               |

| WDTPOST     | FWDT     | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384                                                                                                                                                                                                                                                                                                                                |

| PWMPIN      | FPOR     | <ul> <li>Motor Control PWM Module Pin Mode bit</li> <li>1 = PWM module pins controlled by PORT register at device Reset (tri-stated)</li> <li>0 = PWM module pins controlled by PWM module at device Reset (configured as output pins)</li> </ul>                                                                                                                                                   |

#### TABLE 23-2: dsPIC33FJXXXMCX06/X08/X10 CONFIGURATION BITS DESCRIPTION (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |                                     | Assembly Syntax                          | Description                                                           | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-------------------------------------|------------------------------------------|-----------------------------------------------------------------------|---------------|----------------|--------------------------|

| 48                 | MPY                  | MPY<br>Wm*Wn,Acc,Wx,Wxd,Wy,Wyd      |                                          | Multiply Wm by Wn to Accumulator                                      | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY<br>Wm*Wm,Ac                     | cc,Wx,Wxd,Wy,Wyd                         | Square Wm to Accumulator                                              | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 49                 | MPY.N                | MPY.N<br>Wm*Wn,Ac                   | cc,Wx,Wxd,Wy,Wyd                         | -(Multiply Wm by Wn) to Accumulator                                   | 1             | 1              | None                     |

| 50                 | MSC                  | MSC                                 | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd<br>,<br>AWB | Multiply and Subtract from Accumulator                                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 51                 | MUL                  | MUL.SS                              | Wb,Ws,Wnd                                | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)                              | 1             | 1              | None                     |

|                    |                      | MUL.SU                              | Wb,Ws,Wnd                                | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)                            | 1             | 1              | None                     |

|                    |                      | MUL.US                              | Wb,Ws,Wnd                                | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)                            | 1             | 1              | None                     |

|                    |                      | MUL.UU                              | Wb,Ws,Wnd                                | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)                       | 1             | 1              | None                     |

|                    |                      | MUL.SU                              | Wb,#lit5,Wnd                             | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)                          | 1             | 1              | None                     |

|                    |                      | MUL.UU                              | Wb,#lit5,Wnd                             | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5)                     | 1             | 1              | None                     |

|                    |                      | MUL                                 | f                                        | W3:W2 = f * WREG                                                      | 1             | 1              | None                     |

| 52                 | NEG                  | NEG                                 | Acc                                      | Negate Accumulator                                                    | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG                                 | f                                        | $f = \overline{f} + 1$                                                | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG                                 | f,WREG                                   | WREG = $\overline{f}$ + 1                                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG                                 | Ws,Wd                                    | $Wd = \overline{Ws} + 1$                                              | 1             | 1              | C,DC,N,OV,Z              |