Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · ·                                                                              |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc506t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

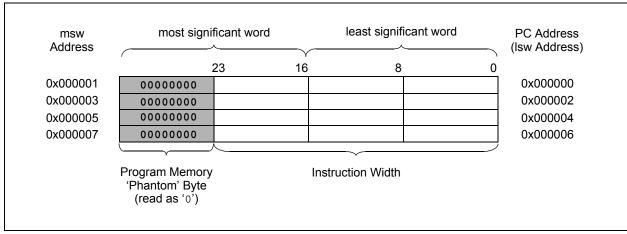

### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJXXXMCX06/X08/X10 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJXXXMCX06/X08/X10 devices also have two interrupt vector tables located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table"**.

### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

### 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X data space is used by all instructions and supports all addressing modes. There are separate read and write data buses for X data space. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All effective addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

### 4.2.6 DMA RAM

Every dsPIC33FJXXXMCX06/X08/X10 device contains 2 Kbytes of dual ported DMA RAM located at the end of Y data space. Memory locations is part of Y data RAM and is in the DMA RAM space are accessible simultaneously by the CPU and the DMA controller module. DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU.

When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

### TABLE 4-22: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1

| File Name  | Addr          | Bit 15    | Bit 14                | Bit 13 | Bit 12 | Bit 11   | Bit 10   | Bit 9    | Bit 8       | Bit 7                         | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0  | All<br>Resets |

|------------|---------------|-----------|-----------------------|--------|--------|----------|----------|----------|-------------|-------------------------------|----------|--------|--------|--------|--------|-------|--------|---------------|

|            | 0400-<br>041E |           | -                     | -      | -      |          |          |          | See definit | ion when V                    | VIN = x  |        | ·      |        |        | -     | -      |               |

| C1BUFPNT1  | 0420          |           | F3BF                  | P<3:0> |        |          | F2BF     | P<3:0>   |             | F1BP<3:0> F0BP<3:0>           |          |        |        |        |        | 0000  |        |               |

| C1BUFPNT2  | 0422          |           | F7BF                  | P<3:0> |        |          | F6BF     | P<3:0>   |             |                               | F5BP     | <3:0>  |        |        | F4BP   | <3:0> |        | 0000          |

| C1BUFPNT3  | 0424          |           | F11B                  | P<3:0> |        |          | F10B     | P<3:0>   |             |                               | F9BP     | <3:0>  |        |        | F8BP   | <3:0> |        | 0000          |

| C1BUFPNT4  | 0426          |           | F15BP<3:0> F14BP<3:0> |        |        |          | F13BF    | P<3:0>   |             |                               | F12BF    | P<3:0> |        | 0000   |        |       |        |               |

| C1RXM0SID  | 0430          |           |                       |        | SID<   | 10:3>    |          |          |             |                               | SID<2:0> |        | —      | MIDE   | _      | EID<' | 17:16> | xxxx          |

| C1RXM0EID  | 0432          |           |                       |        | EID<   | 15:8>    |          |          |             |                               |          |        | EID<   | 7:0>   | _      | -     |        | xxxx          |

| C1RXM1SID  | 0434          | SID<10:3> |                       |        |        |          | SID<2:0> |          | —           | MIDE                          | _        | EID<   | 17:16> | xxxx   |        |       |        |               |

| C1RXM1EID  | 0436          |           | EID<15:8>             |        |        |          |          |          |             | EID<                          | 7:0>     |        |        |        | xxxx   |       |        |               |

| C1RXM2SID  | 0438          |           | SID<10:3>             |        |        |          |          | SID<2:0> |             | —                             | MIDE     | _      | EID<   | 17:16> | xxxx   |       |        |               |

| C1RXM2EID  | 043A          |           | EID<15:8>             |        |        |          |          |          |             | EID<                          | 7:0>     | _      | -      |        | xxxx   |       |        |               |

| C1RXF0SID  | 0440          | SID<10:3> |                       |        |        |          | SID<2:0> |          | —           | EXIDE                         | _        | EID<   | 17:16> | xxxx   |        |       |        |               |

| C1RXF0EID  | 0442          | EID<15:8> |                       |        |        | EID<7:0> |          |          |             |                               |          | xxxx   |        |        |        |       |        |               |

| C1RXF1SID  | 0444          | SID<10:3> |                       |        |        |          | SID<2:0> |          | —           | EXIDE                         | _        | EID<   | 17:16> | xxxx   |        |       |        |               |

| C1RXF1EID  | 0446          | EID<15:8> |                       |        |        |          |          |          | EID<        | 7:0>                          | _        | -      |        | xxxx   |        |       |        |               |

| C1RXF2SID  | 0448          | SID<10:3> |                       |        |        |          | SID<2:0> |          | —           | EXIDE                         | _        | EID<   | 17:16> | xxxx   |        |       |        |               |

| C1RXF2EID  | 044A          |           |                       |        | EID<   | 15:8>    |          |          |             | EID<7:0>                      |          |        |        |        |        | xxxx  |        |               |

| C1RXF3SID  | 044C          |           |                       |        | SID<   | :10:3>   |          |          |             | SID<2:0> — EXIDE — EID<17:16> |          |        |        |        | 17:16> | xxxx  |        |               |

| C1RXF3EID  | 044E          |           |                       |        | EID<   | 15:8>    |          |          |             | EID<7:0>                      |          |        |        |        |        | xxxx  |        |               |

| C1RXF4SID  | 0450          |           |                       |        | SID<   | :10:3>   |          |          |             | SID<2:0> — EXIDE — EID<1      |          |        |        | 17:16> | xxxx   |       |        |               |

| C1RXF4EID  | 0452          |           |                       |        | EID<   | 15:8>    |          |          |             | EID<7:0>                      |          |        |        |        |        | xxxx  |        |               |

| C1RXF5SID  | 0454          |           |                       |        | SID<   | :10:3>   |          |          |             |                               | SID<2:0> |        | —      | EXIDE  | —      | EID<  | 17:16> | xxxx          |

| C1RXF5EID  | 0456          |           |                       |        | EID<   | :15:8>   |          |          |             |                               |          |        | EID<   | 7:0>   |        |       |        | xxxx          |

| C1RXF6SID  | 0458          |           |                       |        | SID<   | :10:3>   |          |          |             |                               | SID<2:0> |        | —      | EXIDE  | —      | EID<  | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |           |                       |        | EID<   | 15:8>    |          |          |             |                               |          |        | EID<   | 7:0>   |        |       |        | xxxx          |

| C1RXF7SID  | 045C          |           |                       |        | SID<   | :10:3>   |          |          |             |                               | SID<2:0> |        | —      | EXIDE  | —      | EID<  | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |           |                       |        | EID<   | 15:8>    |          |          |             |                               |          |        | EID<   | 7:0>   |        |       |        | xxxx          |

| C1RXF8SID  | 0460          |           |                       |        | SID<   | 10:3>    |          |          |             |                               | SID<2:0> |        | —      | EXIDE  | —      | EID<  | 17:16> | xxxx          |

| C1RXF8EID  | 0462          |           |                       |        | EID<   | 15:8>    |          |          |             |                               |          |        | EID<   | 7:0>   |        |       |        | xxxx          |

| C1RXF9SID  | 0464          |           |                       |        | SID<   | 10:3>    |          |          |             |                               | SID<2:0> |        | —      | EXIDE  | —      | EID<  | 17:16> | xxxx          |

| C1RXF9EID  | 0466          |           |                       |        | EID<   | 15:8>    |          |          |             | EID<7:0>                      |          |        |        |        |        | xxxx  |        |               |

| C1RXF10SID | 0468          |           |                       |        | SID<   | 10:3>    |          |          |             |                               | SID<2:0> |        | -      | EXIDE  | _      | EID<' | 17:16> | xxxx          |

| C1RXF10EID | 046A          |           |                       |        | EID<   | 15:8>    |          |          |             |                               |          |        | EID<   | 7:0>   |        |       |        | xxxx          |

dsPIC33FJXXXMCX06/X08/X10

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0           | R/W-0                                                                                        | R/W-0                           | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------|---------------------------------|----------------|------------------|------------------|-----------------|--------|--|--|--|--|

|               | DMA1IE                                                                                       | AD1IE                           | U1TXIE         | U1RXIE           | SPI1IE           | SPI1EIE         | T3IE   |  |  |  |  |

| bit 15        |                                                                                              | ·                               |                |                  | •                | ÷               | bit 8  |  |  |  |  |

| R/W-0         | R/W-0                                                                                        | R/W-0                           | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| T2IE          | OC2IE                                                                                        | IC2IE                           | DMA0IE         | T1IE             | OC1IE            | IC1IE           | INTOIE |  |  |  |  |

| bit 7         | UC2IE                                                                                        | ICZIE                           | DIVIAULE       |                  | OCTIE            | ICTIE           | bit 0  |  |  |  |  |

| Legend:       |                                                                                              |                                 |                |                  |                  |                 |        |  |  |  |  |

| R = Readable  | e bit                                                                                        | W = Writable                    | bit            | U = Unimpler     | mented bit, read | d as '0'        |        |  |  |  |  |

| -n = Value at |                                                                                              | '1' = Bit is set                |                | '0' = Bit is cle |                  | x = Bit is unkr | iown   |  |  |  |  |

| iii valao at  |                                                                                              | 1 Bitle co                      | •              | o Dicio dia      |                  |                 |        |  |  |  |  |

| bit 15        | Unimplemen                                                                                   | ted: Read as '                  | 0'             |                  |                  |                 |        |  |  |  |  |

| bit 14        | DMA1IE: DM                                                                                   | A Channel 1 D                   | ata Transfer C | Complete Interi  | rupt Enable bit  |                 |        |  |  |  |  |

|               |                                                                                              | equest enable                   |                |                  |                  |                 |        |  |  |  |  |

|               |                                                                                              | equest not en                   |                |                  |                  |                 |        |  |  |  |  |

| bit 13        |                                                                                              |                                 |                | rupt Enable bit  |                  |                 |        |  |  |  |  |

|               |                                                                                              | equest enable<br>equest not ena |                |                  |                  |                 |        |  |  |  |  |

| bit 12        | •                                                                                            | RT1 Transmitte                  |                | able bit         |                  |                 |        |  |  |  |  |

|               | 1 = Interrupt request enabled                                                                |                                 |                |                  |                  |                 |        |  |  |  |  |

|               | 0 = Interrupt r                                                                              | equest not en                   | abled          |                  |                  |                 |        |  |  |  |  |

| bit 11        | U1RXIE: UART1 Receiver Interrupt Enable bit                                                  |                                 |                |                  |                  |                 |        |  |  |  |  |

|               |                                                                                              | equest enable<br>equest not ena |                |                  |                  |                 |        |  |  |  |  |

| bit 10        | -                                                                                            | Event Interrup                  |                |                  |                  |                 |        |  |  |  |  |

|               |                                                                                              | equest enable                   |                |                  |                  |                 |        |  |  |  |  |

|               |                                                                                              | equest not en                   |                |                  |                  |                 |        |  |  |  |  |

| bit 9         | SPI1EIE: SPI                                                                                 | 1 Error Interru                 | pt Enable bit  |                  |                  |                 |        |  |  |  |  |

|               |                                                                                              | equest enable                   |                |                  |                  |                 |        |  |  |  |  |

|               | •                                                                                            | equest not en                   |                |                  |                  |                 |        |  |  |  |  |

| bit 8         |                                                                                              | Interrupt Enab                  |                |                  |                  |                 |        |  |  |  |  |

|               | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul> |                                 |                |                  |                  |                 |        |  |  |  |  |

| bit 7         | -                                                                                            | Interrupt Enab                  |                |                  |                  |                 |        |  |  |  |  |

|               |                                                                                              | equest enable                   |                |                  |                  |                 |        |  |  |  |  |

|               | 0 = Interrupt r                                                                              | equest not en                   | abled          |                  |                  |                 |        |  |  |  |  |

| bit 6         | •                                                                                            | ut Compare Ch                   |                | upt Enable bit   |                  |                 |        |  |  |  |  |

|               |                                                                                              | equest enable                   |                |                  |                  |                 |        |  |  |  |  |

| bit 5         | •                                                                                            | equest not en<br>Capture Chann  |                | Enabla bit       |                  |                 |        |  |  |  |  |

| DIL 5         | •                                                                                            | equest enable                   | •              |                  |                  |                 |        |  |  |  |  |

|               |                                                                                              | request not en                  |                |                  |                  |                 |        |  |  |  |  |

| bit 4         | DMA0IE: DM                                                                                   | A Channel 0 D                   | ata Transfer C | Complete Interi  | rupt Enable bit  |                 |        |  |  |  |  |

|               |                                                                                              | equest enable                   |                |                  |                  |                 |        |  |  |  |  |

|               |                                                                                              | equest not en                   |                |                  |                  |                 |        |  |  |  |  |

| bit 3         |                                                                                              | Interrupt Enab                  |                |                  |                  |                 |        |  |  |  |  |

|               |                                                                                              | equest enable<br>equest not en  |                |                  |                  |                 |        |  |  |  |  |

|               |                                                                                              |                                 |                |                  |                  |                 |        |  |  |  |  |

### REGISTER 7-13: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3 (CONTINUED)

- bit 1 SI2C2IE: I2C2 Slave Events Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled

- bit 0 T7IE: Timer7 Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| REGISTER 9-1: | OSCCON: OSCILLATOR CONTROL REGISTER <sup>(1)</sup> |

|---------------|----------------------------------------------------|

|               |                                                    |

| U-0             | R-0                                              | R-0                                  | R-0             | U-0              | R/W-y           | R/W-y                    | R/W-y |  |  |  |  |

|-----------------|--------------------------------------------------|--------------------------------------|-----------------|------------------|-----------------|--------------------------|-------|--|--|--|--|

|                 |                                                  | COSC<2:0>                            |                 | <u> </u>         |                 | NOSC<2:0> <sup>(2)</sup> |       |  |  |  |  |

| bit 15          |                                                  |                                      |                 |                  |                 |                          | bit   |  |  |  |  |

| R/W-0           | U-0                                              | R-0                                  | U-0             | R/C-0            | U-0             | R/W-0                    | R/W-0 |  |  |  |  |

| CLKLOCK         |                                                  | LOCK                                 | —               | CF               | —               | LPOSCEN                  | OSWEN |  |  |  |  |

| bit 7           |                                                  |                                      |                 |                  |                 |                          | bit   |  |  |  |  |

| Legend:         |                                                  | y = Value set                        | from Configur   | ation bits on P  | OR              |                          |       |  |  |  |  |

| R = Readable I  | oit                                              | W = Writable                         | bit             | U = Unimpler     | mented bit, rea | id as '0'                |       |  |  |  |  |

| -n = Value at P | OR                                               | '1' = Bit is set                     |                 | '0' = Bit is cle | ared            | x = Bit is unkne         | own   |  |  |  |  |

| bit 15          | Unimplemen                                       | ted: Read as '                       | ∩'              |                  |                 |                          |       |  |  |  |  |

| bit 14-12       | -                                                | Current Oscilla                      |                 | hits (read-only  | )               |                          |       |  |  |  |  |

| 51(17-12        |                                                  | C oscillator (FF                     |                 |                  | )               |                          |       |  |  |  |  |

|                 |                                                  | C oscillator (FF                     | ,               |                  |                 |                          |       |  |  |  |  |

|                 |                                                  | y oscillator (XT                     |                 |                  |                 |                          |       |  |  |  |  |

|                 |                                                  | y oscillator (XT                     |                 | PLL              |                 |                          |       |  |  |  |  |

|                 |                                                  | dary oscillator (                    |                 |                  |                 |                          |       |  |  |  |  |

|                 |                                                  | ower RC oscilla                      | ,               |                  |                 |                          |       |  |  |  |  |

|                 | 110 = Fast RC oscillator (FRC) with Divide-by-16 |                                      |                 |                  |                 |                          |       |  |  |  |  |

|                 | 111 = Fast R                                     | C oscillator (FF                     | RC) with Divide | e-by-n           |                 |                          |       |  |  |  |  |

| bit 11          | Unimplemented: Read as '0'                       |                                      |                 |                  |                 |                          |       |  |  |  |  |

| bit 10-8        | NOSC<2:0>:                                       | New Oscillator                       | Selection bits  | <sub>;</sub> (2) |                 |                          |       |  |  |  |  |

|                 |                                                  | C oscillator (FF                     |                 |                  |                 |                          |       |  |  |  |  |

|                 |                                                  | C oscillator (FF                     | ,               |                  |                 |                          |       |  |  |  |  |

|                 |                                                  | y oscillator (XT                     |                 |                  |                 |                          |       |  |  |  |  |

|                 |                                                  | y oscillator (XT                     |                 | PLL              |                 |                          |       |  |  |  |  |

|                 |                                                  | dary oscillator (                    |                 |                  |                 |                          |       |  |  |  |  |

|                 |                                                  | ower RC oscilla                      |                 | by 16            |                 |                          |       |  |  |  |  |

|                 |                                                  | C oscillator (FF<br>C oscillator (FF |                 |                  |                 |                          |       |  |  |  |  |

| bit 7           |                                                  | Clock Lock Ena                       | -               | 5-Dy-11          |                 |                          |       |  |  |  |  |

|                 |                                                  | M0 = 1), then c                      |                 | configurations   | are locked      |                          |       |  |  |  |  |

|                 |                                                  | M0 = 0), then c                      |                 |                  |                 | ied                      |       |  |  |  |  |

|                 | 0 = Clock and                                    | d PLL selection                      | ns are not lock | ed; configurat   | ions may be m   | odified                  |       |  |  |  |  |

| bit 6           | Unimplemen                                       | ted: Read as '                       | 0'              |                  |                 |                          |       |  |  |  |  |

| bit 5           |                                                  | ock Status bit                       | • • •           |                  |                 |                          |       |  |  |  |  |

|                 |                                                  | that PLL is in that PLL is ou        |                 |                  |                 | L is disabled            |       |  |  |  |  |

| bit 4           | Unimplemen                                       | ted: Read as '                       | 0'              |                  | -               |                          |       |  |  |  |  |

| bit 3           | CF: Clock Fai                                    | il Detect bit (re                    | ad/clear by ap  | plication)       |                 |                          |       |  |  |  |  |

|                 |                                                  | as detected clo<br>as not detected   |                 |                  |                 |                          |       |  |  |  |  |

| bit 2           | Unimplemen                                       |                                      | CIUCK IAIIUIE   |                  |                 |                          |       |  |  |  |  |

**Note 1:** Writes to this register require an unlock sequence. Refer to **Section 7. "Oscillator**" (DS70186) in the *"dsPIC33F Family Reference Manual"* (available from the Microchip website) for details.

2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

NOTES:

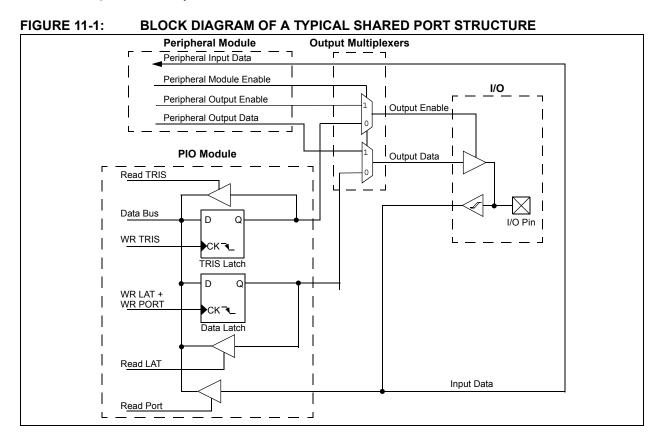

### 11.0 I/O PORTS

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "I/O Ports" (DS70193) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKIN) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 11.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pins will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. An example is the INT4 pin.

**Note:** The voltage on a digital input pin can be between -0.3V to 5.6V.

© 2009 Microchip Technology Inc.

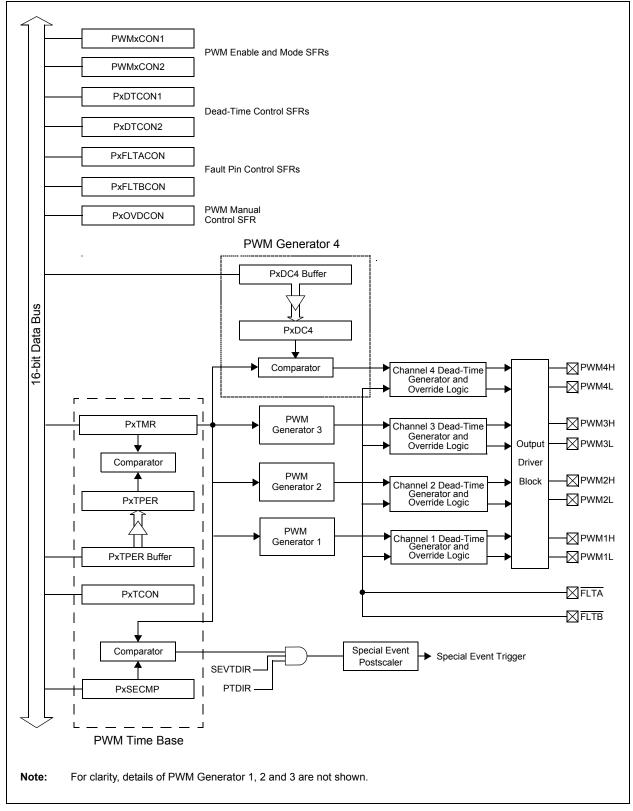

### FIGURE 16-1: PWM MODULE BLOCK DIAGRAM

### REGISTER 17-2: DFLTxCON: DIGITAL FILTER CONTROL REGISTER

| U-0                | U-0                                                                                                                                  | U-0                                                                                                                 | U-0                                                                           | U-0                                                                          | R/W-0                                                                                                          | R/W-0                                                | R/W-0 |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------|--|--|--|--|

|                    | _                                                                                                                                    | _                                                                                                                   |                                                                               | _                                                                            | IMV<                                                                                                           | <1:0>                                                | CEID  |  |  |  |  |

| bit 15             |                                                                                                                                      |                                                                                                                     |                                                                               |                                                                              |                                                                                                                |                                                      | bit 8 |  |  |  |  |

|                    |                                                                                                                                      |                                                                                                                     |                                                                               |                                                                              |                                                                                                                |                                                      |       |  |  |  |  |

| R/W-0              |                                                                                                                                      | R/W-0                                                                                                               |                                                                               | U-0                                                                          | U-0                                                                                                            | U-0                                                  | U-0   |  |  |  |  |

| QEOUT              | QECK<2:0> — — — —                                                                                                                    |                                                                                                                     |                                                                               |                                                                              |                                                                                                                |                                                      |       |  |  |  |  |

| bit 7              |                                                                                                                                      |                                                                                                                     |                                                                               |                                                                              |                                                                                                                |                                                      | bit 0 |  |  |  |  |

| Levende            |                                                                                                                                      |                                                                                                                     |                                                                               |                                                                              |                                                                                                                |                                                      |       |  |  |  |  |

| R = Readable       | Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'                                                            |                                                                                                                     |                                                                               |                                                                              |                                                                                                                |                                                      |       |  |  |  |  |

|                    |                                                                                                                                      | W = Writable k<br>'1' = Bit is set                                                                                  | Л                                                                             | 0 = Onimple<br>'0' = Bit is cle                                              |                                                                                                                | x = Bit is unkr                                      |       |  |  |  |  |

| -n = Value at      | PUR                                                                                                                                  | I = DILIS SEL                                                                                                       |                                                                               |                                                                              | areu                                                                                                           |                                                      | IOWI  |  |  |  |  |

| bit 15-11          | Unimplement                                                                                                                          | ted: Read as '0                                                                                                     | ,                                                                             |                                                                              |                                                                                                                |                                                      |       |  |  |  |  |

| bit 10-9           | QEBx inp<br>In 4X Quadrat<br>IMV1 = F<br>IMV0 = F<br>In 2X Quadrat<br>IMV1 = S                                                       | but pins during a<br>ture Count Mod<br>Required state of<br>Required state of<br>ture Count Mod<br>Selects phase in | an index puls<br>e:<br>of Phase B in<br>of Phase A in<br>e:<br>nput signal fo | se when the PC<br>nput signal for i<br>nput signal for i<br>or index state n | ne user to speci<br>DSxCNT register<br>match on index<br>match on index<br>natch (0 = Phas<br>signal for matcl | r is to be reset<br>pulse<br>pulse<br>e A, 1 = Phase | В)    |  |  |  |  |

| bit 8              | 1 = Interrupts                                                                                                                       | Error Interrupt E<br>due to count er<br>due to count er                                                             | rors are disa                                                                 |                                                                              |                                                                                                                |                                                      |       |  |  |  |  |

| bit 7              | 1 = Digital filte                                                                                                                    | x/QEBx/INDXx<br>er outputs enab<br>er outputs disab                                                                 | led                                                                           | -                                                                            | able bit                                                                                                       |                                                      |       |  |  |  |  |

| bit 6-4<br>bit 3-0 | 111 = 1:256 C<br>110 = 1:128 C<br>101 = 1:64 Cl<br>100 = 1:32 Cl<br>011 = 1:16 Cl<br>010 = 1:4 Clo<br>001 = 1:2 Clo<br>000 = 1:1 Clo | Clock Divide<br>ock Divide<br>ock Divide<br>ock Divide<br>ck Divide<br>ck Divide                                    |                                                                               | Filter Clock Div                                                             | ide Select Bits                                                                                                |                                                      |       |  |  |  |  |

| R/W-0        | U-0                                                                                                                                       | R/W-0                                                                                                                                                                         | U-0            | U-0              | U-0                             | U-0                          | U-0      |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|---------------------------------|------------------------------|----------|--|--|--|--|--|

| SPIEN        | —                                                                                                                                         | SPISIDL                                                                                                                                                                       |                | _                | —                               | _                            | _        |  |  |  |  |  |

| bit 15       |                                                                                                                                           |                                                                                                                                                                               |                |                  |                                 | 4                            | bit 8    |  |  |  |  |  |

|              |                                                                                                                                           |                                                                                                                                                                               |                |                  |                                 |                              |          |  |  |  |  |  |

| U-0          | R/C-0                                                                                                                                     | U-0                                                                                                                                                                           | U-0            | U-0              | U-0                             | R-0                          | R-0      |  |  |  |  |  |

| _            | SPIROV                                                                                                                                    |                                                                                                                                                                               | _              |                  |                                 | SPITBF                       | SPIRBF   |  |  |  |  |  |

| bit 7        |                                                                                                                                           |                                                                                                                                                                               |                |                  |                                 |                              | bit 0    |  |  |  |  |  |

|              |                                                                                                                                           |                                                                                                                                                                               |                |                  |                                 |                              |          |  |  |  |  |  |

| Legend:      |                                                                                                                                           | C = Clearable                                                                                                                                                                 |                |                  |                                 |                              |          |  |  |  |  |  |

| R = Readab   |                                                                                                                                           | W = Writable I                                                                                                                                                                | oit            | -                | mented bit, read                |                              |          |  |  |  |  |  |

| -n = Value a | t POR                                                                                                                                     | '1' = Bit is set                                                                                                                                                              |                | '0' = Bit is cle | ared                            | x = Bit is unkr              | nown     |  |  |  |  |  |

| hit 1E       |                                                                                                                                           | Enchlo hit                                                                                                                                                                    |                |                  |                                 |                              |          |  |  |  |  |  |

| bit 15       | <b>SPIEN:</b> SPIx Enable bit $1 = \text{Enables}$ module and configures SCKx, SDOx, SDIx and $\overline{\text{SSx}}$ as serial port pins |                                                                                                                                                                               |                |                  |                                 |                              |          |  |  |  |  |  |

|              | 0 = Disables module                                                                                                                       |                                                                                                                                                                               |                |                  |                                 |                              |          |  |  |  |  |  |

| bit 14       | Unimplemen                                                                                                                                | Unimplemented: Read as '0'                                                                                                                                                    |                |                  |                                 |                              |          |  |  |  |  |  |

| bit 13       | SPISIDL: Sto                                                                                                                              | p in Idle Mode                                                                                                                                                                | bit            |                  |                                 |                              |          |  |  |  |  |  |

|              |                                                                                                                                           | ue module opei                                                                                                                                                                |                |                  | lle mode                        |                              |          |  |  |  |  |  |

|              |                                                                                                                                           | module operati                                                                                                                                                                |                | de               |                                 |                              |          |  |  |  |  |  |

| bit 12-7     | -                                                                                                                                         | ted: Read as 'o                                                                                                                                                               |                |                  |                                 |                              |          |  |  |  |  |  |

| bit 6        |                                                                                                                                           | eive Overflow I                                                                                                                                                               |                | ed and discard   | ad The user s                   | oftware has not              | read the |  |  |  |  |  |

|              |                                                                                                                                           | data in the SPI                                                                                                                                                               |                |                  | ieu. The user si                | Sitware has not              | reau ine |  |  |  |  |  |

|              | 0 = No overfl                                                                                                                             | ow has occurre                                                                                                                                                                | ed             |                  |                                 |                              |          |  |  |  |  |  |

| bit 5-2      | Unimplemen                                                                                                                                | ted: Read as 'd                                                                                                                                                               | )'             |                  |                                 |                              |          |  |  |  |  |  |

| bit 1        | SPITBF: SPI                                                                                                                               | k Transmit Buffe                                                                                                                                                              | er Full Status | bit              |                                 |                              |          |  |  |  |  |  |

|              |                                                                                                                                           | not yet started;                                                                                                                                                              |                | full             |                                 |                              |          |  |  |  |  |  |

|              |                                                                                                                                           | started; SPIxTX                                                                                                                                                               |                | writes SPIvBLI   | E location load                 | ing SPIvTXB                  |          |  |  |  |  |  |

|              |                                                                                                                                           | Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB.<br>Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR. |                |                  |                                 |                              |          |  |  |  |  |  |

| bit 0        | -                                                                                                                                         | x Receive Buffe                                                                                                                                                               |                |                  |                                 |                              |          |  |  |  |  |  |

|              | 1 = Receive o                                                                                                                             | complete; SPIx                                                                                                                                                                | RXB is full    |                  |                                 |                              |          |  |  |  |  |  |

|              |                                                                                                                                           | s not complete;                                                                                                                                                               |                |                  |                                 |                              |          |  |  |  |  |  |

|              |                                                                                                                                           |                                                                                                                                                                               |                |                  | from SPIxSR to<br>BLIE location | ) SPIxRXB.<br>reading SPIxRX | (B       |  |  |  |  |  |

|              | Automatically                                                                                                                             |                                                                                                                                                                               |                | ore reaus or ix  |                                 | Cauling OF IXRA              | <b>.</b> |  |  |  |  |  |

### REGISTER 18-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

| R-0 HSC         | R-0 HSC                                                                                                                                                                                                                      | U-0                                                              | U-0                              | U-0                      | R/C-0 HS                                        | R-0 HSC                               | R-0 HSC         |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------|--------------------------|-------------------------------------------------|---------------------------------------|-----------------|--|--|--|

| ACKSTAT         | TRSTAT                                                                                                                                                                                                                       | _                                                                | _                                | _                        | BCL                                             | GCSTAT                                | ADD10           |  |  |  |

| bit 15          |                                                                                                                                                                                                                              |                                                                  |                                  |                          |                                                 |                                       | bit 8           |  |  |  |

|                 |                                                                                                                                                                                                                              |                                                                  |                                  |                          |                                                 |                                       |                 |  |  |  |

| R/C-0 HS        | R/C-0 HS                                                                                                                                                                                                                     | R-0 HSC                                                          | R/C-0 HSC                        | R/C-0 HSC                | R-0 HSC                                         | R-0 HSC                               | R-0 HSC         |  |  |  |

| IWCOL           | I2COV                                                                                                                                                                                                                        | D_A                                                              | Р                                | S                        | R_W                                             | RBF                                   | TBF             |  |  |  |

| bit 7           |                                                                                                                                                                                                                              |                                                                  |                                  |                          |                                                 |                                       | bit 0           |  |  |  |

| Legend:         |                                                                                                                                                                                                                              | U = Unimpler                                                     | nented bit rea                   | ad as '0'                |                                                 |                                       |                 |  |  |  |

| R = Readable    |                                                                                                                                                                                                                              |                                                                  |                                  |                          |                                                 |                                       |                 |  |  |  |

| -n = Value at P | OR                                                                                                                                                                                                                           | '1' = Bit is set                                                 |                                  | '0' = Bit is cle         | ared                                            | x = Bit is unkr                       | iown            |  |  |  |

|                 |                                                                                                                                                                                                                              |                                                                  |                                  |                          |                                                 |                                       |                 |  |  |  |

| bit 15          | ACKSTAT: Ac<br>(when operation<br>1 = NACK rec<br>0 = ACK recein<br>Hardware set                                                                                                                                             | ng as I <sup>2</sup> C mas<br>reived from sla<br>ived from slave | ter, applicable<br>ve<br>e       |                          | nsmit operation                                 | )                                     |                 |  |  |  |

| bit 14          |                                                                                                                                                                                                                              |                                                                  |                                  | -                        | ster, applicable                                | to master trans                       | smit operation) |  |  |  |

|                 | <ul> <li>1 = Master transmit is in progress (8 bits + ACK)</li> <li>0 = Master transmit is not in progress</li> <li>Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.</li> </ul> |                                                                  |                                  |                          |                                                 |                                       |                 |  |  |  |

| bit 13-11       | Unimplemented: Read as '0'                                                                                                                                                                                                   |                                                                  |                                  |                          |                                                 |                                       |                 |  |  |  |

| bit 10          | BCL: Master                                                                                                                                                                                                                  | Bus Collision [                                                  | Detect bit                       |                          |                                                 |                                       |                 |  |  |  |

|                 | 1 = A bus coll<br>0 = No collisio<br>Hardware set                                                                                                                                                                            | on                                                               |                                  | ing a master o           | peration                                        |                                       |                 |  |  |  |

| bit 9           | GCSTAT: Ger                                                                                                                                                                                                                  | neral Call Statu                                                 | ıs bit                           |                          |                                                 |                                       |                 |  |  |  |

|                 | 0 = General c                                                                                                                                                                                                                | all address wa<br>all address wa<br>when address                 | s not received                   |                          | ss. Hardware c                                  | lear at Stop det                      | ection.         |  |  |  |

| bit 8           | ADD10: 10-Bi                                                                                                                                                                                                                 | it Address Stat                                                  | us bit                           |                          |                                                 |                                       |                 |  |  |  |

|                 |                                                                                                                                                                                                                              | ress was not r                                                   | natched                          | ched 10-bit ad           | dress. Hardwai                                  | re clear at Stop                      | detection.      |  |  |  |

| bit 7           | IWCOL: Write                                                                                                                                                                                                                 | Collision Dete                                                   | ect bit                          |                          |                                                 |                                       |                 |  |  |  |

|                 | 0 = No collisio                                                                                                                                                                                                              | on                                                               | -                                |                          | ause the I <sup>2</sup> C mo<br>usy (cleared by | -                                     |                 |  |  |  |

| bit 6           | I2COV: Recei                                                                                                                                                                                                                 |                                                                  |                                  |                          |                                                 |                                       |                 |  |  |  |

|                 | 1 = A byte wa<br>0 = No overflo                                                                                                                                                                                              | s received whi                                                   | le the I2CxRC                    | -                        | till holding the j                              | -                                     |                 |  |  |  |

| bit 5           | D_A: Data/Ad                                                                                                                                                                                                                 |                                                                  |                                  |                          | (,                                              | · · · · · · · · · · · · · · · · · · · |                 |  |  |  |

|                 | 1 = Indicates 1<br>0 = Indicates 1                                                                                                                                                                                           | that the last by<br>that the last by                             | rte received w<br>rte received w | as data<br>as device add | ress<br>by reception of                         | slave byte.                           |                 |  |  |  |