Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Becano                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 69                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-TQFP                                                                         |

| Supplier Device Package    | 80-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc508-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

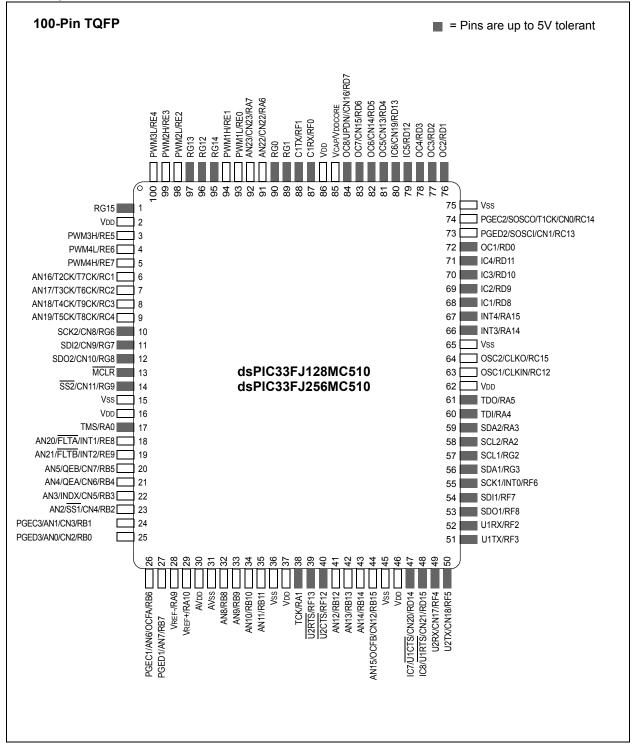

# Pin Diagrams (Continued)

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F Family Reference Manual", which is available from the Microchip website (www.microchip.com).

# 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJXXXMCX06/X08/X10 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

- VCAP/VDDCORE (see Section 2.3 "Capacitor on Internal Voltage Regulator (VCAP/VDDCORE)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

| Note: | The   | AVdd    | and   | AVss    | pins | mus | st be |

|-------|-------|---------|-------|---------|------|-----|-------|

|       | conn  | ected   | indep | endent  | of   | the | ADC   |

|       | volta | ge refe | rence | source. |      |     |       |

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

# 4.2 Data Address Space

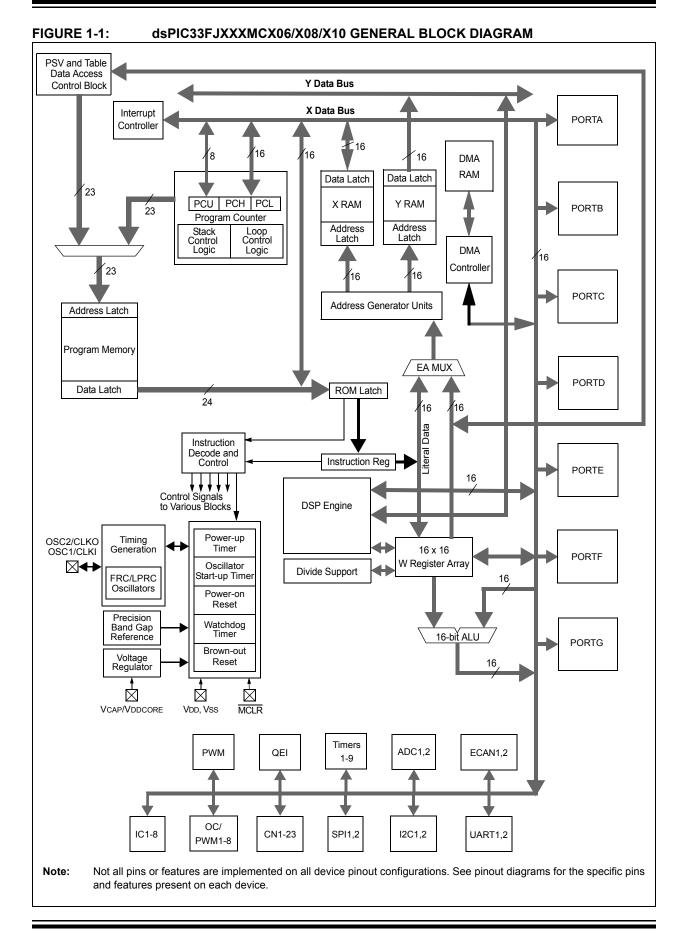

The dsPIC33FJXXXMCX06/X08/X10 CPU has a separate 16-bit wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. Data memory maps of devices with different RAM sizes are shown in Figure 4-3 through Figure 4-5.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

dsPIC33FJXXXMCX06/X08/X10 devices implement a total of up to 30 Kbytes of data memory. Should an EA point to a location outside of this area, an all-zero word or byte will be returned.

### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes of each word have even addresses, while the Most Significant Bytes have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> microcontrollers and improve data space memory usage efficiency, the dsPIC33FJXXXMCX06/X08/X10 instruction set supports both word and byte operations. As a consequence of byte accessibility, all effective address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSb of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A sign-extend instruction (SE) is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSb of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

## 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33FJXXXMCX06/X08/X10 core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Please refer to the corresponding device tables and pinout diagrams for device-specific information.

### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area between 0x0000 and 0x1FFF is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

#### TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXMCX10 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2       | 0062        | _       |         | _       | _       | _       | _       | _      | _      | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2       | 006A        | —       | _       | _       | _       | _       | _       | _      | -      | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXMCX08 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|---------|---------|---------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE         | 0000          |

| CNEN2       | 0062        | —       | _       | —       | _       | _       | —       |        | _      | _      |        | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | —       | _       | _       | _       | _       | _       | _      | _      | _      | -      | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-4: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXMCX06 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|--------|---------|---------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE  | CN2IE   | CN1IE   | CN0IE         | 0000          |

| CNEN2       | 0062        | _       | _       | _       | _       | _       | _       | _      | _      | _      | _      | CN21IE  | CN20IE  | -      | CN18IE  | CN17IE  | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | CN3PUE | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | —       | _       | _       | _       | _       | _       | _      | _      | _      | _      | CN21PUE | CN20PUE | _      | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4-7: INPUT CAPTURE REGISTER MAI |

|---------------------------------------|

|---------------------------------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                   | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9 | Bit 8       | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------------------------|--------|--------|--------|----------|-------|-------------|--------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| IC1BUF   | 0140        |        |                          |        |        |        |          |       | Input 1 Ca  | apture Regis | ter   |       |       |       |       |          |       | xxxx          |

| IC1CON   | 0142        |        | _                        | ICSIDL | _      | _      | _        | _     | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC2BUF   | 0144        |        |                          |        |        |        |          |       | Input 2 Ca  | apture Regis | ter   |       |       |       |       |          |       | xxxx          |

| IC2CON   | 0146        |        | _                        | ICSIDL | —      | _      | _        | _     | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC3BUF   | 0148        |        |                          |        |        |        |          |       | Input 3 Ca  | apture Regis | ter   |       |       |       |       |          |       | xxxx          |

| IC3CON   | 014A        |        | _                        | ICSIDL | _      | _      | _        | _     | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC4BUF   | 014C        |        | Input 4 Capture Register |        |        |        |          |       |             |              |       |       | xxxx  |       |       |          |       |               |

| IC4CON   | 014E        | _      | _                        | ICSIDL | _      | _      | _        | _     | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC5BUF   | 0150        |        |                          |        |        |        |          |       | Input 5 Ca  | apture Regis | ter   |       |       |       |       |          |       | xxxx          |

| IC5CON   | 0152        | _      | _                        | ICSIDL | _      | _      | _        | _     | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC6BUF   | 0154        |        |                          |        |        |        |          |       | Input 6 Ca  | apture Regis | ter   |       |       |       |       |          |       | xxxx          |

| IC6CON   | 0156        | _      | _                        | ICSIDL | _      | _      | _        | _     | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF   | 0158        |        |                          |        |        |        |          |       | Input 7 Ca  | apture Regis | ter   |       |       |       |       |          |       | xxxx          |

| IC7CON   | 015A        | _      | _                        | ICSIDL |        |        | _        | —     | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF   | 015C        |        |                          |        |        |        |          |       | Input 8 Ca  | apture Regis | ter   |       |       |       |       |          |       | xxxx          |

| IC8CON   | 015E        | _      |                          | ICSIDL | _      | _      | _        | _     | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| Logond   |             |        | - Deeet                  |        |        |        | Desetual |       | wn in hovor | d a star al  |       |       |       |       |       |          |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| R/W-0           | R/W-0          | R/W-0                                   | R/W-0            | R/W-0            | R/W-0            | R/W-0          | R/W-0   |

|-----------------|----------------|-----------------------------------------|------------------|------------------|------------------|----------------|---------|

| U2TXIF          | U2RXIF         | INT2IF                                  | T5IF             | T4IF             | OC4IF            | OC3IF          | DMA21IF |

| bit 15          |                |                                         |                  |                  |                  |                | bit 8   |

| R/W-0           | R/W-0          | R/W-0                                   | R/W-0            | R/W-0            | U-0              | R/W-0          | R/W-0   |

| IC8IF           | IC7IF          | AD2IF                                   | INT1IF           | CNIF             |                  | MI2C1IF        | SI2C1IF |

| bit 7           | 10711          | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                  | 0.111            |                  |                | bit C   |

| Legend:         |                |                                         |                  |                  |                  |                |         |

| R = Readable    | bit            | W = Writable                            | bit              | U = Unimple      | mented bit, read | d as '0'       |         |

| -n = Value at P | POR            | '1' = Bit is set                        |                  | '0' = Bit is cle | eared            | x = Bit is unk | nown    |

|                 |                |                                         |                  |                  |                  |                |         |

| bit 15          | U2TXIF: UAF    | RT2 Transmitte                          | r Interrupt Flag | g Status bit     |                  |                |         |

|                 |                | request has oc                          |                  |                  |                  |                |         |

|                 | -              | request has no                          |                  |                  |                  |                |         |

| bit 14          |                | RT2 Receiver I                          |                  | Status bit       |                  |                |         |

|                 | •              | request has oc<br>request has no        |                  |                  |                  |                |         |

| bit 13          | •              | rnal Interrupt 2                        |                  | t                |                  |                |         |

| bit 15          |                | request has oc                          | -                | l                |                  |                |         |

|                 |                | request has no                          |                  |                  |                  |                |         |

| bit 12          | T5IF: Timer5   | Interrupt Flag                          | Status bit       |                  |                  |                |         |

|                 |                | request has oc<br>request has no        |                  |                  |                  |                |         |

| bit 11          | -              | Interrupt Flag                          |                  |                  |                  |                |         |

|                 | 1 = Interrupt  | request has oc<br>request has no        | curred           |                  |                  |                |         |

| bit 10          | •              | ut Compare Ch                           |                  | upt Flag Status  | s bit            |                |         |

|                 | 1 = Interrupt  | request has oc<br>request has no        | curred           |                  |                  |                |         |

| bit 9           | •              | ut Compare Ch                           |                  | upt Flag Status  | s bit            |                |         |

|                 | 1 = Interrupt  | request has oc<br>request has no        | curred           |                  |                  |                |         |

| bit 8           |                |                                         |                  | Complete Inte    | rrupt Flag Statu | ıs bit         |         |

|                 |                | request has oc                          |                  | · · · · ·        |                  |                |         |

|                 | 0 = Interrupt  | request has no                          | t occurred       |                  |                  |                |         |

| bit 7           | IC8IF: Input ( | Capture Chann                           | el 8 Interrupt F | lag Status bit   |                  |                |         |

|                 | •              | request has oc                          |                  |                  |                  |                |         |

| hit 6           | -              | request has no                          |                  | Ing Status bit   |                  |                |         |

| bit 6           | 1 = Interrupt  | Capture Chann<br>request has oc         | curred           | -lag Status bit  |                  |                |         |

|                 | -              | request has no                          |                  |                  |                  |                |         |

| bit 5           |                | 2 Conversion C                          | •                | rupt Flag Statu  | is bit           |                |         |

|                 | 1 = Interrupt  | request has oc                          |                  |                  |                  |                |         |

|                 |                |                                         |                  |                  |                  |                |         |

| bit 4           | -              | rnal Interrupt 1                        |                  | t                |                  |                |         |

# REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

| U-0          | R/W-1                                                                 | R/W-0                                   | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------|-----------------------------------------|----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|

|              |                                                                       | T1IP<2:0>                               |                |                   |                 | OC1IP<2:0>      |       |  |  |  |  |  |

| bit 15       |                                                                       |                                         |                |                   |                 |                 | bit   |  |  |  |  |  |

| U-0          | R/W-1                                                                 | R/W-0                                   | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|              |                                                                       | IC1IP<2:0>                              |                | _                 |                 | INT0IP<2:0>     |       |  |  |  |  |  |

| bit 7        |                                                                       |                                         |                |                   | 1               |                 | bit   |  |  |  |  |  |

| Legend:      |                                                                       |                                         |                |                   |                 |                 |       |  |  |  |  |  |

| R = Readab   | le bit                                                                | W = Writable I                          | oit            | U = Unimple       | mented bit, rea | ad as '0'       |       |  |  |  |  |  |

| -n = Value a | t POR                                                                 | '1' = Bit is set                        |                | '0' = Bit is cle  | eared           | x = Bit is unkn | own   |  |  |  |  |  |

| bit 15       | Unimpleme                                                             | nted: Read as 'o                        | )'             |                   |                 |                 |       |  |  |  |  |  |

| bit 14-12    | T1IP<2:0>:                                                            | Timer1 Interrupt                        | Priority bits  |                   |                 |                 |       |  |  |  |  |  |

|              | 111 = Interr                                                          | upt is priority 7 (I                    | nighest priori | ty interrupt)     |                 |                 |       |  |  |  |  |  |

|              | •                                                                     |                                         |                |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                     |                                         |                |                   |                 |                 |       |  |  |  |  |  |

|              |                                                                       | upt is priority 1<br>upt source is disa | abled          |                   |                 |                 |       |  |  |  |  |  |

| bit 11       |                                                                       | nted: Read as '0                        |                |                   |                 |                 |       |  |  |  |  |  |

| bit 10-8     | -                                                                     | . Output Compa                          |                | 1 Interrupt Prior | rity bits       |                 |       |  |  |  |  |  |

|              | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre> |                                         |                |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                     |                                         |                |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                     |                                         |                |                   |                 |                 |       |  |  |  |  |  |

|              | 001 = Interr                                                          | upt is priority 1                       |                |                   |                 |                 |       |  |  |  |  |  |

|              | 000 <b>= Interr</b>                                                   | upt source is disa                      | abled          |                   |                 |                 |       |  |  |  |  |  |

| bit 7        | Unimpleme                                                             | nted: Read as 'o                        | )'             |                   |                 |                 |       |  |  |  |  |  |

| bit 6-4      |                                                                       | Input Capture C                         |                | • •               | oits            |                 |       |  |  |  |  |  |

|              | 111 = Interr                                                          | upt is priority 7 (I                    | nighest priori | ty interrupt)     |                 |                 |       |  |  |  |  |  |

|              | •                                                                     |                                         |                |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                     |                                         |                |                   |                 |                 |       |  |  |  |  |  |

|              |                                                                       | upt is priority 1<br>upt source is disa | ablad          |                   |                 |                 |       |  |  |  |  |  |

| bit 3        |                                                                       | nted: Read as 'o                        |                |                   |                 |                 |       |  |  |  |  |  |

| bit 3-0      | -                                                                     | External Interr                         |                | , bite            |                 |                 |       |  |  |  |  |  |

| DIL 2-0      |                                                                       | upt is priority 7 (h                    |                |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                     | optio pilotity i (i                     | g. eet p. et   | (j                |                 |                 |       |  |  |  |  |  |

|              | •                                                                     |                                         |                |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                     |                                         |                |                   |                 |                 |       |  |  |  |  |  |

|              | 001 = Interr                                                          | upt is priority 1                       |                |                   |                 |                 |       |  |  |  |  |  |

## REGISTER 7-15: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

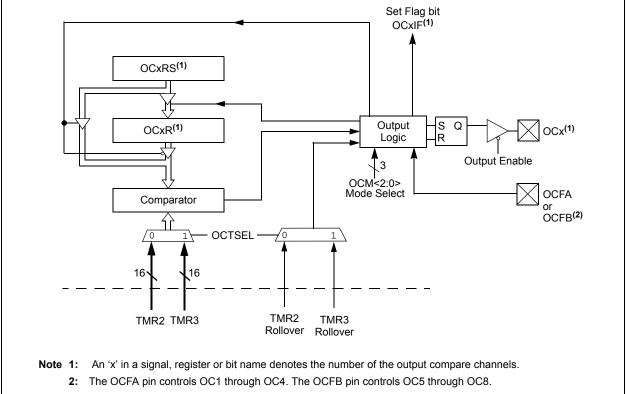

# 15.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F Family Reference Manual", Section 13. "Output Compare" (DS70209), which is available on the Microchip web site (www.microchip.com).

The output compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two Compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

The output compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without Fault Protection

- · PWM mode with Fault Protection

#### REGISTER 20-1: UxMODE: UARTx MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                      |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                              |

- **Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

#### CICTRL1: ECAN™ CONTROL REGISTER 1 REGISTER 21-1: U-0 U-0 R/W-0 R/W-0 r-0 R/W-1 R/W-0 R/W-0 REQOP<2:0> CSIDL ABAT \_\_\_\_ \_\_\_\_ \_\_\_\_ bit 15 bit 8 R-1 R-0 R-0 U-0 R/W-0 U-0 U-0 R/W-0 OPMODE<2:0> CANCAP WIN bit 7 bit 0 Legend: r = Bit is Reserved R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-14 Unimplemented: Read as '0' bit 13 CSIDL: Stop in Idle Mode bit 1 = Discontinue module operation when device enters Idle mode 0 = Continue module operation in Idle mode bit 12 ABAT: Abort All Pending Transmissions bit Signal all transmit buffers to abort transmission. Module will clear this bit when all transmissions are aborted bit 11 Reserved: Do no use bit 10-8 REQOP<2:0>: Request Operation Mode bits 000 = Set Normal Operation mode 001 = Set Disable mode 010 = Set Loopback mode 011 = Set Listen Only Mode 100 = Set Configuration mode 101 = Reserved – do not use 110 = Reserved – do not use 111 = Set Listen All Messages mode bit 7-5 OPMODE<2:0>: Operation Mode bits 000 = Module is in Normal Operation mode 001 = Module is in Disable mode 010 = Module is in Loopback mode 011 = Module is in Listen Only mode 100 = Module is in Configuration mode 101 = Reserved 110 = Reserved 111 = Module is in Listen All Messages mode bit 4 Unimplemented: Read as '0' bit 3 CANCAP: CAN Message Receive Timer Capture Event Enable bit 1 = Enable input capture based on CAN message receive 0 = Disable CAN capture bit 2-1 Unimplemented: Read as '0' bit 0 WIN: SFR Map Window Select bit 1 = Use filter window 0 = Use buffer window

### REGISTER 21-19: CiFMSKSEL2: ECAN™ FILTER 15-8 MASK SELECTION REGISTER

| R/W-0         R/W-0         R/W-0         R/W-0           F15MSK<1:0>         F14MSK<1:0>           bit 15             R/W-0         R/W-0         R/W-0           F11MSK<1:0>         F10MSK<1:0>           bit 7             Legend:             R = Readable bit         W = Writable bit            -n = Value at POR         '1' = Bit is set            bit 15-14         F15MSK<1:0>: Mask Source for Filte            11 = Reserved         10 = Acceptance Mask 2 registers co            01 = Acceptance Mask 1 registers co             00 = Acceptance Mask 0 registers co |                                                                                       |                 |                |         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------|----------------|---------|

| bit 15         R/W-0       R/W-0       R/W-0         F11MSK<1:0>       F10MSK<1:0>         bit 7         Legend:       R = Readable bit       W = Writable bit         -n = Value at POR       '1' = Bit is set         bit 15-14       F15MSK<1:0>: Mask Source for Filte         11 = Reserved       10 = Acceptance Mask 2 registers cc         01 = Acceptance Mask 1 registers cc       00 = Acceptance Mask 0 registers cc                                                                                                                                                       | /-0 R/W-0                                                                             | R/W-0           | R/W-0          | R/W-0   |

| R/W-0       R/W-0       R/W-0       R/W-0         F11MSK<1:0>       F10MSK<1:0>         bit 7         Legend:         R = Readable bit       W = Writable bit         -n = Value at POR       '1' = Bit is set         bit 15-14       F15MSK<1:0>: Mask Source for Filte         11 = Reserved       10 = Acceptance Mask 2 registers co         01 = Acceptance Mask 1 registers co       00 = Acceptance Mask 0 registers co                                                                                                                                                        | F13                                                                                   | /ISK<1:0>       | F12M8          | SK<1:0> |

| F11MSK<1:0>       F10MSK<1:0>         bit 7         Legend:         R = Readable bit       W = Writable bit         -n = Value at POR       '1' = Bit is set         bit 15-14       F15MSK<1:0>: Mask Source for Filte         11 = Reserved       10 = Acceptance Mask 2 registers co         01 = Acceptance Mask 1 registers co       00 = Acceptance Mask 0 registers co                                                                                                                                                                                                          |                                                                                       |                 |                | bit 8   |

| F11MSK<1:0>       F10MSK<1:0>         bit 7         Legend:         R = Readable bit       W = Writable bit         -n = Value at POR       '1' = Bit is set         bit 15-14       F15MSK<1:0>: Mask Source for Filte         11 = Reserved       10 = Acceptance Mask 2 registers co         01 = Acceptance Mask 1 registers co       00 = Acceptance Mask 0 registers co                                                                                                                                                                                                          |                                                                                       |                 |                |         |

| bit 7         Legend:         R = Readable bit       W = Writable bit         -n = Value at POR       '1' = Bit is set         bit 15-14       F15MSK<1:0>: Mask Source for Filte         11 = Reserved       10 = Acceptance Mask 2 registers cc         01 = Acceptance Mask 1 registers cc       00 = Acceptance Mask 0 registers cc                                                                                                                                                                                                                                                | /-0 R/W-0                                                                             | R/W-0           | R/W-0          | R/W-0   |

| Legend:         R = Readable bit       W = Writable bit         -n = Value at POR       '1' = Bit is set         bit 15-14       F15MSK<1:0>: Mask Source for Filte         11 = Reserved       10 = Acceptance Mask 2 registers co         01 = Acceptance Mask 1 registers co       00 = Acceptance Mask 0 registers co                                                                                                                                                                                                                                                              | F91                                                                                   | 1SK<1:0>        | F8MS           | K<1:0>  |

| R = Readable bit       W = Writable bit         -n = Value at POR       '1' = Bit is set         bit 15-14       F15MSK<1:0>: Mask Source for Filte         11 = Reserved       10 = Acceptance Mask 2 registers co         01 = Acceptance Mask 1 registers co       00 = Acceptance Mask 0 registers co         00 = Acceptance Mask 0 registers co       00 = Acceptance Mask 0 registers co                                                                                                                                                                                        |                                                                                       |                 |                | bit 0   |

| R = Readable bit       W = Writable bit         -n = Value at POR       '1' = Bit is set         bit 15-14       F15MSK<1:0>: Mask Source for Filte         11 = Reserved       10 = Acceptance Mask 2 registers co         01 = Acceptance Mask 1 registers co       00 = Acceptance Mask 0 registers co                                                                                                                                                                                                                                                                              |                                                                                       |                 |                |         |

| -n = Value at POR '1' = Bit is set<br>bit 15-14 <b>F15MSK&lt;1:0&gt;:</b> Mask Source for Filte<br>11 = Reserved<br>10 = Acceptance Mask 2 registers co<br>01 = Acceptance Mask 1 registers co<br>00 = Acceptance Mask 0 registers co                                                                                                                                                                                                                                                                                                                                                  |                                                                                       |                 |                |         |

| bit 15-14 <b>F15MSK&lt;1:0&gt;:</b> Mask Source for Filte<br>11 = Reserved<br>10 = Acceptance Mask 2 registers co<br>01 = Acceptance Mask 1 registers co<br>00 = Acceptance Mask 0 registers co                                                                                                                                                                                                                                                                                                                                                                                        | U = Unimp                                                                             | emented bit, re | ead as '0'     |         |

| 11 = Reserved<br>10 = Acceptance Mask 2 registers co<br>01 = Acceptance Mask 1 registers co<br>00 = Acceptance Mask 0 registers co                                                                                                                                                                                                                                                                                                                                                                                                                                                     | '0' = Bit is                                                                          | leared          | x = Bit is unk | nown    |

| bit 13-12F14MSK<1:0>: Mask Source for Filtebit 11-10F13MSK<1:0>: Mask Source for Filtebit 9-8F12MSK<1:0>: Mask Source for Filte                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ontain mask<br>ontain mask<br>ontain mask<br>er 14 bit (same va<br>er 13 bit (same va | lues as bit 15- | 14)            |         |

bit 7-6F11MSK<1:0>: Mask Source for Filter 11 bit (same values as bit 15-14)bit 5-4F10MSK<1:0>: Mask Source for Filter 10 bit (same values as bit 15-14)

bit 3-2 **F9MSK<1:0>:** Mask Source for Filter 9 bit (same values as bit 15-14)

bit 1-0 **F8MSK<1:0>:** Mask Source for Filter 8 bit (same values as bit 15-14)

#### REGISTER 21-24: CIRXOVF1: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXOVF7 | RXOVF6 | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |

| bit 7  | •      |        |        |        |        |        | bit 0  |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **RXOVF<15:0>:** Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

#### REGISTER 21-25: CIRXOVF2: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

### **REGISTER 22-9:** AD1PCFGH: ADC1 PORT CONFIGURATION REGISTER HIGH<sup>(1,2,3)</sup>

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PCFG31 | PCFG30 | PCFG29 | PCFG28 | PCFG27 | PCFG26 | PCFG25 | PCFG24 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

|        |        |        |        |        |        |        |        |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PCFG23 | PCFG22 | PCFG21 | PCFG20 | PCFG19 | PCFG18 | PCFG17 | PCFG16 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0

PCFG<31:16>: ADC Port Configuration Control bits

1 = Port pin in Digital mode, port read input enabled, ADC input multiplexer connected to AVss

- 0 = Port pin in Analog mode, port read input disabled, ADC samples pin voltage

- **Note 1:** On devices without 32 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on device.

- 2: ADC2 only supports analog inputs AN0-AN15; therefore, no ADC2 port Configuration register exists.

- **3:** PCFGx = ANx, where x = 16 through 31.

# **REGISTER 22-10:** ADxPCFGL: ADCx PORT CONFIGURATION REGISTER LOW<sup>(1,2,3)</sup>

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| PCFG15 | PCFG14 | PCFG13 | PCFG12 | PCFG11 | PCFG10 | PCFG9 | PCFG8 |

| bit 15 | •      |        |        |        |        |       | bit 8 |

|        |        |        |        |        |        |       |       |

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

| PCFG7  | PCFG6  | PCFG5  | PCFG4  | PCFG3  | PCFG2  | PCFG1 | PCFG0 |

| bit 7  |        |        |        |        |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PCFG<15:0>:** ADC Port Configuration Control bits

1 = Port pin in Digital mode, port read input enabled, ADC input multiplexer connected to AVss

0 = Port pin in Analog mode, port read input disabled, ADC samples pin voltage

- **Note 1:** On devices without 16 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on device.

- **2:** On devices with two analog-to-digital modules, both AD1PCFGL and AD2PCFGL will affect the configuration of port pins multiplexed with AN0-AN15.

- **3:** PCFGx = ANx, where x = 0 through 15.

| Bit Field  | Register | Description                                                                                                                                                                                                             |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPOL       | FPOR     | Motor Control PWM High Side Polarity bit<br>1 = PWM module high side output pins have active-high output polarity<br>0 = PWM module high side output pins have active-low output polarity                               |

| LPOL       | FPOR     | Motor Control PWM Low Side Polarity bit<br>1 = PWM module low side output pins have active-high output polarity<br>0 = PWM module low side output pins have active-low output polarity                                  |

| FPWRT<2:0> | FPOR     | Power-on Reset Timer Value Select bits<br>111 = PWRT = 128 ms<br>110 = PWRT = 64 ms<br>101 = PWRT = 32 ms<br>100 = PWRT = 16 ms<br>011 = PWRT = 8 ms<br>010 = PWRT = 4 ms<br>001 = PWRT = 2 ms<br>000 = PWRT = Disabled |

| JTAGEN     | FICD     | JTAG Enable bits<br>1 = JTAG enabled<br>0 = JTAG disabled                                                                                                                                                               |

| ICS<1:0>   | FICD     | ICD Communication Channel Select bits<br>11 = Communicate on PGEC1 and PGED1<br>10 = Communicate on PGEC2 and PGED2<br>01 = Communicate on PGEC3 and PGED3<br>00 = Reserved                                             |

#### TABLE 23-2: dsPIC33FJXXXMCX06/X08/X10 CONFIGURATION BITS DESCRIPTION (CONTINUED)

### TABLE 26-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACT       | ERISTICS                   |     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |       |      |                                              |  |

|------------------|----------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|----------------------------------------------|--|

| Parameter<br>No. | Typical <sup>(1)</sup>     | Мах | Units Conditions                                                                                                                                |       |      |                                              |  |

| Power-Down       | Current (IPD) <sup>(</sup> | 2)  |                                                                                                                                                 |       |      |                                              |  |

| DC60d            | 55                         | 500 | μΑ                                                                                                                                              | -40°C |      |                                              |  |

| DC60a            | 211                        | 500 | μΑ                                                                                                                                              | +25°C | 3.3V | Base Power-Down Current <sup>(3,4)</sup>     |  |

| DC60b            | 244                        | 500 | μΑ                                                                                                                                              | +85°C |      |                                              |  |

| DC61d            | 8                          | 13  | μΑ                                                                                                                                              | -40°C |      |                                              |  |

| DC61a            | 10                         | 15  | μΑ                                                                                                                                              | +25°C | 3.3V | Watchdog Timer Current: ΔIWDT <sup>(3)</sup> |  |

| DC61b            | 12                         | 20  | μA                                                                                                                                              | +85°C | 1    |                                              |  |

**Note 1:** Data in the Typical column is at 3.3V, 25°C unless otherwise stated.

2: Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled to Vss. WDT, etc., are all switched off and VREGS (RCON<8>) = 1.

**3:** The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

4: These currents are measured on the device containing the most memory in this family.

| DC CHARACTERISTICS |                        |     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |       |            |      |         |  |  |

|--------------------|------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|---------|--|--|

| Parameter<br>No.   | Typical <sup>(1)</sup> | Мах | Doze Ratio                                                                                                                                      | Units | Conditions |      |         |  |  |

| DC73a              | 11                     | 35  | 1:2                                                                                                                                             | mA    |            |      |         |  |  |

| DC73f              | 11                     | 30  | 1:64                                                                                                                                            | mA    | -40°C      | 3.3V | 40 MIPS |  |  |

| DC73g              | 11                     | 30  | 1:128                                                                                                                                           | mA    |            |      |         |  |  |

| DC70a              | 42                     | 50  | 1:2                                                                                                                                             | mA    |            |      |         |  |  |

| DC70f              | 26                     | 30  | 1:64                                                                                                                                            | mA    | +25°C      | 3.3V | 40 MIPS |  |  |

| DC70g              | 25                     | 30  | 1:128                                                                                                                                           | mA    |            |      |         |  |  |

| DC71a              | 41                     | 50  | 1:2                                                                                                                                             | mA    |            |      |         |  |  |

| DC71f              | 25                     | 30  | 1:64                                                                                                                                            | mA    | +85°C      | 3.3V | 40 MIPS |  |  |

| DC71g              | 24                     | 30  | 1:128                                                                                                                                           | mA    |            |      |         |  |  |

### TABLE 26-8: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

**Note 1:** Data in the Typical column is at 3.3V, 25°C unless otherwise stated.

#### TABLE 26-36: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

|              |         |                               |                           | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |          |       |                                                      |  |

|--------------|---------|-------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|------------------------------------------------------|--|

| Param<br>No. |         | Charac                        | teristic                  | Min <sup>(1)</sup>                                                                                                                              | Max      | Units | Conditions                                           |  |

| IM10         | TLO:SCL | Clock Low Time                | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                 | _        | μs    |                                                      |  |

|              |         |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                 |          | μs    | _                                                    |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                 | _        | μs    |                                                      |  |

| IM11         | THI:SCL | Clock High Time               | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                 | _        | μs    |                                                      |  |

|              |         |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                 | _        | μs    | _                                                    |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                 | <b>—</b> | μs    | _                                                    |  |

| IM20 T       | TF:SCL  | SDAx and SCLx<br>Fall Time    | 100 kHz mode              |                                                                                                                                                 | 300      | ns    | CB is specified to be from 10 to 400 pF              |  |

|              |         |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                     | 300      | ns    |                                                      |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                 | 100      | ns    | -                                                    |  |

| IM21 TR:SCL  | TR:SCL  | SDAx and SCLx                 | 100 kHz mode              |                                                                                                                                                 | 1000     | ns    | CB is specified to be from 10 to 400 pF              |  |

|              |         | Rise Time                     | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                     | 300      | ns    |                                                      |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                 | 300      | ns    |                                                      |  |

| IM25 TSU:DAT | TSU:DAT | Data Input                    | 100 kHz mode              | 250                                                                                                                                             | _        | ns    |                                                      |  |

|              |         | Setup Time                    | 400 kHz mode              | 100                                                                                                                                             | _        | ns    |                                                      |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | 40                                                                                                                                              | _        | ns    | -                                                    |  |

| IM26 TH      | THD:DAT | Data Input<br>Hold Time       | 100 kHz mode              | 0                                                                                                                                               | _        | μs    | _                                                    |  |

|              |         |                               | 400 kHz mode              | 0                                                                                                                                               | 0.9      | μs    |                                                      |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | 0.2                                                                                                                                             | _        | μs    | -                                                    |  |

| IM30 7       | TSU:STA | Start Condition<br>Setup Time | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                 | _        | μs    | Only relevant for<br>Repeated Start<br>condition     |  |

|              |         |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                 | _        | μs    |                                                      |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                 | _        | μs    |                                                      |  |

| IM31         | THD:STA | Start Condition<br>Hold Time  | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                 | —        | μs    | After this period the first clock pulse is generated |  |

|              |         |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                 | —        | μs    |                                                      |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                 | —        | μs    |                                                      |  |

| IM33         | Tsu:sto | Stop Condition<br>Setup Time  | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                 | —        | μs    |                                                      |  |

|              |         |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                 | —        | μs    |                                                      |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                 | —        | μs    |                                                      |  |

| IM34 THD:STO | THD:STO | Stop Condition                | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                 | —        | ns    | _                                                    |  |

|              |         | Hold Time                     | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                 | —        | ns    |                                                      |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                 | —        | ns    |                                                      |  |

| IM40         | TAA:SCL | Output Valid<br>From Clock    | 100 kHz mode              |                                                                                                                                                 | 3500     | μs    | _                                                    |  |

|              |         |                               | 400 kHz mode              | —                                                                                                                                               | 1000     | μs    | —                                                    |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                               | 400      | μs    | _                                                    |  |

| IM45         | TBF:SDA | Bus Free Time                 | 100 kHz mode              | 4.7                                                                                                                                             | —        | μs    | Time the bus must be                                 |  |

|              |         |                               | 400 kHz mode              | 1.3                                                                                                                                             | —        | μs    | free before a new                                    |  |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | 0.5                                                                                                                                             | —        | μs    | transmission can start                               |  |

| IM50         | Св      | Bus Capacitive L              | oading                    | —                                                                                                                                               | 400      | pF    | —                                                    |  |

Note 1: BRG is the value of the I<sup>2</sup>C Baud Rate Generator. Refer to Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195) in the "dsPIC33F Family Reference Manual".

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

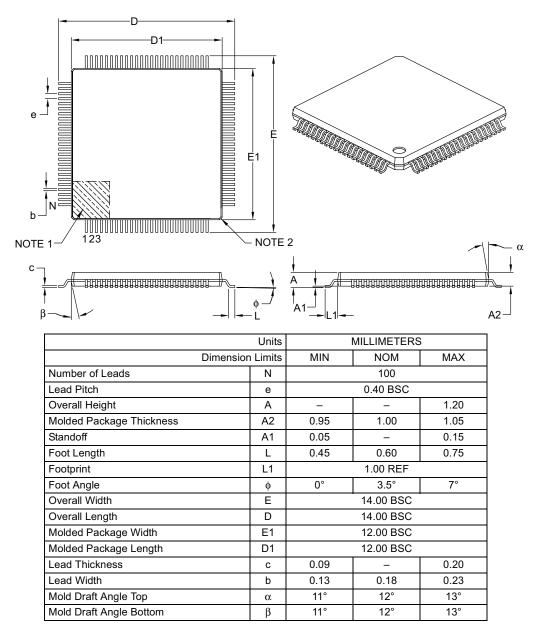

# 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B