Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT               |

| Number of I/O              | 69                                                                               |

| Program Memory Size        | 64KB (64K × 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-TQFP                                                                          |

| Supplier Device Package    | 80-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc508t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### High-Performance, 16-Bit Digital Signal Controllers

#### **Operating Range:**

- Up to 40 MIPS operation (at 3.0-3.6V):

- Industrial temperature range (-40°C to +85°C)

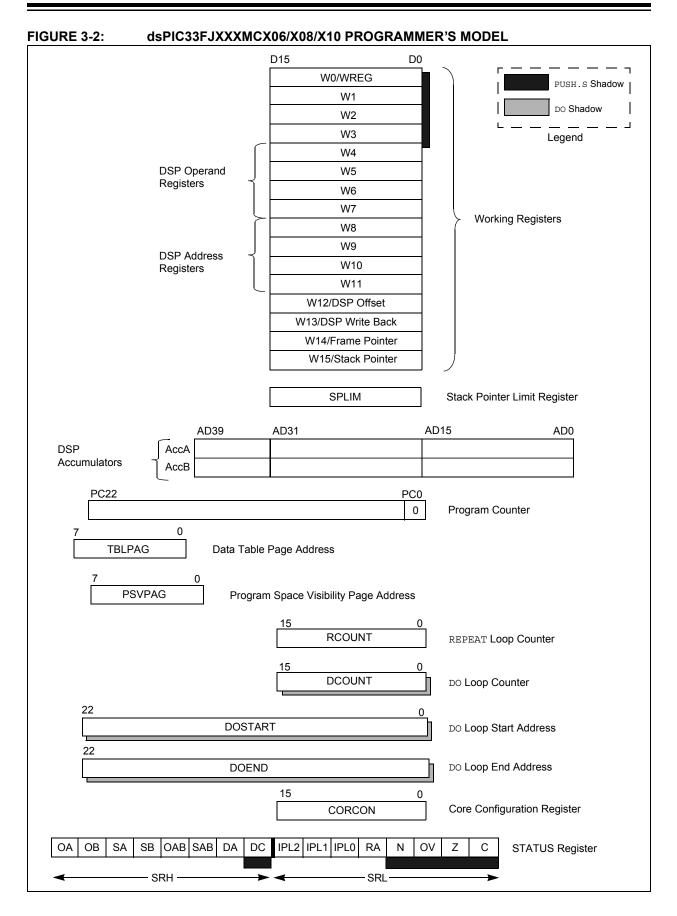

#### **High-Performance DSC CPU:**

- · Modified Harvard architecture

- C compiler optimized instruction set

- · 16-bit wide data path

- 24-bit wide instructions

- Linear program memory addressing up to 4M instruction words

- · Linear data memory addressing up to 64 Kbytes

- 83 base instructions: mostly 1 word/1 cycle

- Two 40-bit accumulators:

- With rounding and saturation options

- · Flexible and powerful addressing modes:

- Indirect, Modulo and Bit-Reversed

- Software stack

- 16 x 16 fractional/integer multiply operations

- · 32/16 and 16/16 divide operations

- · Single-cycle multiply and accumulate:

- Accumulator write back for DSP operations

- Dual data fetch

- Up to ±16-bit shifts for up to 40-bit data

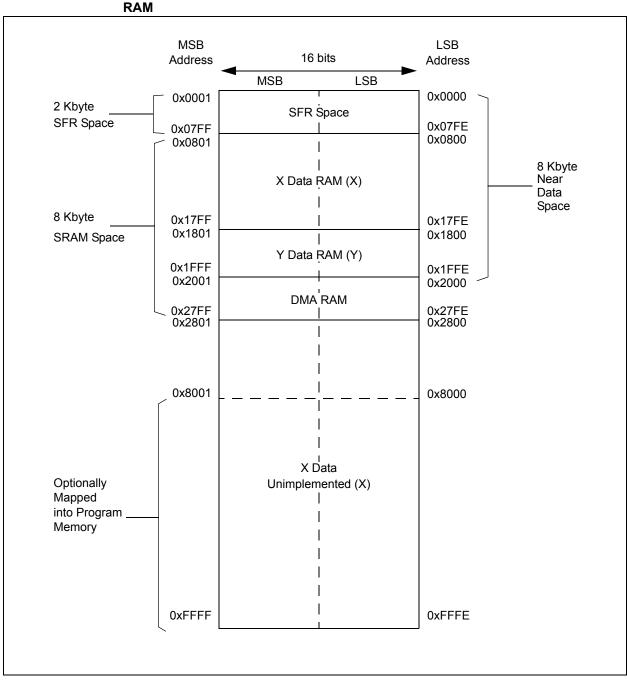

#### **Direct Memory Access (DMA):**

- 8-channel hardware DMA

- 2 Kbytes dual ported DMA buffer area (DMA RAM) to store data transferred via DMA:

- Allows data transfer between RAM and a peripheral while CPU is executing code (no cycle stealing)

- Most peripherals support DMA

#### **Interrupt Controller:**

- 5-cycle latency

- · Up to 67 available interrupt sources

- · Up to five external interrupts

- · Seven programmable priority levels

- · Five processor exceptions

#### Digital I/O:

- · Up to 85 programmable digital I/O pins

- · Wake-up/Interrupt-on-Change on up to 24 pins

- · Output pins can drive from 3.0V to 3.6V

- All digital input pins are 5V tolerant

- 4 mA sink on all I/O pins

#### **On-Chip Flash and SRAM:**

- · Flash program memory, up to 256 Kbytes

- Data SRAM, up to 30 Kbytes (includes 2 Kbytes of DMA RAM)

#### System Management:

- Flexible clock options:

- External, crystal, resonator, internal RC

- Fully integrated PLL

- Extremely low jitter PLL

- Power-up Timer

- Oscillator Start-up Timer/Stabilizer

- · Watchdog Timer with its own RC oscillator

- · Fail-Safe Clock Monitor

- · Reset by multiple sources

#### **Power Management:**

- On-chip 2.5V voltage regulator

- · Switch between clock sources in real time

- · Idle, Sleep and Doze modes with fast wake-up

#### Timers/Capture/Compare/PWM:

- Timer/Counters, up to nine 16-bit timers:

- Can pair up to make four 32-bit timers

- 1 timer runs as Real-Time Clock with external 32.768 kHz oscillator

- Programmable prescaler

- Input Capture (up to eight channels):

- Capture on up, down or both edges

- 16-bit capture input functions

- 4-deep FIFO on each capture

- Output Compare (up to eight channels):

- Single or Dual 16-Bit Compare mode

- 16-bit Glitchless PWM mode

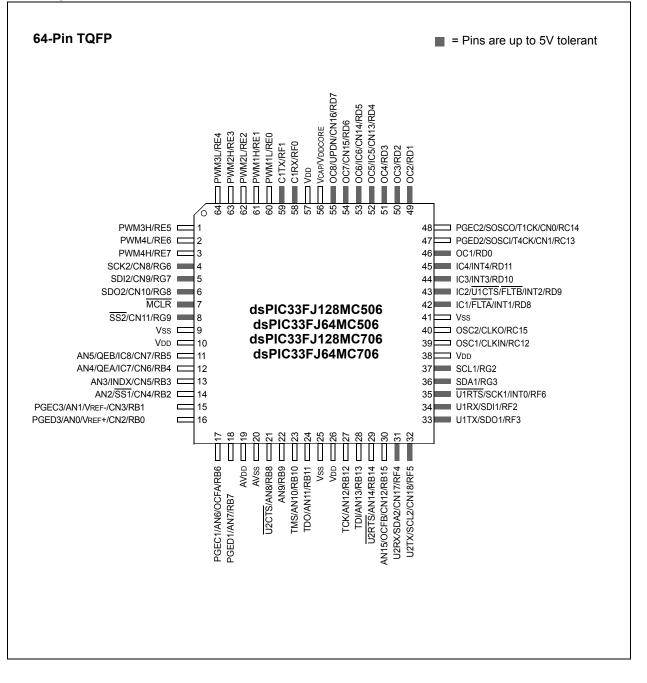

#### **Pin Diagrams**

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 2, MPLAB ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip website.

- *"MPLAB<sup>®</sup> ICD 2 In-Circuit Debugger User's Guide"* DS51331

- *"Using MPLAB<sup>®</sup> ICD 2"* (poster) DS51265

- "MPLAB<sup>®</sup> ICD 2 Design Advisory" DS51566

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™" (poster) DS51749

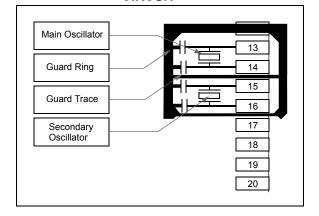

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### FIGURE 2-3: SU OF

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### FIGURE 4-3: DATA MEMORY MAP FOR dsPIC33FJXXXMCX06/X08/X10 DEVICES WITH 8 KBS RAM

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

| IADLE 4     | 4-J.        |        | .NNUF I |            | NOLLLI  | KEGISI  |                     | AF        |             |            |              |             |           |              |             |            |               |               |

|-------------|-------------|--------|---------|------------|---------|---------|---------------------|-----------|-------------|------------|--------------|-------------|-----------|--------------|-------------|------------|---------------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14  | Bit 13     | Bit 12  | Bit 11  | Bit 10              | Bit 9     | Bit 8       | Bit 7      | Bit 6        | Bit 5       | Bit 4     | Bit 3        | Bit 2       | Bit 1      | Bit 0         | All<br>Resets |

| INTCON1     | 0080        | NSTDIS | OVAERR  | OVBERR     | COVAERR | COVBERR | OVATE               | OVBTE     | COVTE       | SFTACERR   | DIV0ERR      | DMACERR     | MATHERR   | ADDRERR      | STKERR      | OSCFAIL    | _             | 0000          |

| INTCON2     | 0082        | ALTIVT | DISI    | _          | _       | _       | _                   | _         | _           | —          | _            | _           | INT4EP    | INT3EP       | INT2EP      | INT1EP     | INT0EP        | 0000          |

| IFS0        | 0084        | —      | DMA1IF  | AD1IF      | U1TXIF  | U1RXIF  | SPI1IF              | SPI1EIF   | T3IF        | T2IF       | OC2IF        | IC2IF       | DMA0IF    | T1IF         | OC1IF       | IC1IF      | <b>INT0IF</b> | 0000          |

| IFS1        | 0086        | U2TXIF | U2RXIF  | INT2IF     | T5IF    | T4IF    | OC4IF               | OC3IF     | DMA2IF      | IC8IF      | IC7IF        | AD2IF       | INT1IF    | CNIF         | _           | MI2C1IF    | SI2C1IF       | 0000          |

| IFS2        | 0088        | T6IF   | DMA4IF  | _          | OC8IF   | OC7IF   | OC6IF               | OC5IF     | IC6IF       | IC5IF      | IC4IF        | IC3IF       | DMA3IF    | C1IF         | C1RXIF      | SPI2IF     | SPI2EIF       | 0000          |

| IFS3        | 008A        | FLTAIF | —       | DMA5IF     | _       | _       | QEIIF               | PWMIF     | C2IF        | C2RXIF     | INT4IF       | INT3IF      | T9IF      | T8IF         | MI2C2IF     | SI2C2IF    | T7IF          | 0000          |

| IFS4        | 008C        | —      | —       | _          | _       | _       | _                   | _         | —           | C2TXIF     | C1TXIF       | DMA7IF      | DMA6IF    | —            | U2EIF       | U1EIF      | FLTBIF        | 0000          |

| IEC0        | 0094        | —      | DMA1IE  | AD1IE      | U1TXIE  | U1RXIE  | SPI1IE              | SPI1EIE   | T3IE        | T2IE       | OC2IE        | IC2IE       | DMA0IE    | T1IE         | OC1IE       | IC1IE      | INT0IE        | 0000          |

| IEC1        | 0096        | U2TXIE | U2RXIE  | INT2IE     | T5IE    | T4IE    | OC4IE               | OC3IE     | DMA2IE      | IC8IE      | IC7IE        | AD2IE       | INT1IE    | CNIE         | _           | MI2C1IE    | SI2C1IE       | 0000          |

| IEC2        | 0098        | T6IE   | DMA4IE  | _          | OC8IE   | OC7IE   | OC6IE               | OC5IE     | IC6IE       | IC5IE      | IC4IE        | IC3IE       | DMA3IE    | C1IE         | C1RXIE      | SPI2IE     | SPI2EIE       | 0000          |

| IEC3        | 009A        | FLTAIE | _       | DMA5IE     | _       | _       | QEIIE               | PWMIE     | C2IE        | C2RXIE     | INT4IE       | INT3IE      | T9IE      | T8IE         | MI2C2IE     | SI2C2IE    | T7IE          | 0000          |

| IEC4        | 009C        | _      | _       | _          | _       | _       | _                   | _         | _           | C2TXIE     | C1TXIE       | DMA7IE      | DMA6IE    | _            | U2EIE       | U1EIE      | FLTBIE        | 0000          |

| IPC0        | 00A4        | _      |         | T1IP<2:0>  | >       | _       | (                   | OC1IP<2:0 | )>          | _          |              | IC1IP<2:0>  |           | _            | INT0IP<2:0> |            | •             | 4444          |

| IPC1        | 00A6        | _      |         | T2IP<2:0>  | >       | —       | (                   | OC2IP<2:0 | )>          | —          |              | IC2IP<2:0>  |           | —            | DMA0IP<2:0> |            | >             | 4444          |

| IPC2        | 00A8        |        | J       | J1RXIP<2:  | 0>      | _       | — SPI1IP<2:0> — SPI |           | SPI1EIP<2:0 | )>         | —            |             | T3IP<2:0> |              | 4444        |            |               |               |

| IPC3        | 00AA        |        |         |            | —       | _       | D                   | MA1IP<2:  | 0>          | —          | AD1IP<2:0>   |             | —         | U1TXIP<2:0>  |             | >          | 0444          |               |

| IPC4        | 00AC        |        |         | CNIP<2:02  | >       | _       |                     | _         | —           | —          | MI2C1IP<2:0> |             | —         | SI2C1IP<2:0> |             | >          | 4044          |               |

| IPC5        | 00AE        |        |         | IC8IP<2:0  | >       | _       | IC7IP<2:0>          |           | —           |            | AD2IP<2:0>   | >           | —         | I            | NT1IP<2:0>  | •          | 4444          |               |

| IPC6        | 00B0        |        |         | T4IP<2:0>  | >       | _       | (                   | OC4IP<2:( | )>          | OC3IP<2:0> |              | —           | D         | MA2IP<2:0    | >           | 4444       |               |               |

| IPC7        | 00B2        |        | ι       | J2TXIP<2:( | )>      | _       | L                   | J2RXIP<2: | 0>          | -          |              | INT2IP<2:0  | >         | —            |             | T5IP<2:0>  |               | 4444          |

| IPC8        | 00B4        |        |         | C1IP<2:0>  | >       | _       | C                   | C1RXIP<2: | 0>          | -          |              | SPI2IP<2:0  | >         | —            | SI          | PI2EIP<2:0 | >             | 4444          |

| IPC9        | 00B6        |        |         | IC5IP<2:0  | >       | _       |                     | IC4IP<2:0 | >           | -          |              | IC3IP<2:0>  |           | —            | D           | MA3IP<2:0  | >             | 4444          |

| IPC10       | 00B8        |        |         | OC7IP<2:0  | >       | _       | (                   | OC6IP<2:0 | )>          | -          |              | OC5IP<2:0   | >         | —            | -           | C6IP<2:0>  |               | 4444          |

| IPC11       | 00BA        | —      |         | T6IP<2:0>  | >       | —       | D                   | MA4IP<2:  | 0>          | —          | —            | —           | —         | —            | C           | )C8IP<2:0> |               | 4404          |

| IPC12       | 00BC        | —      |         | T8IP<2:0>  | >       | —       | N                   | 112C21P<2 | :0>         | —          |              | SI2C2IP<2:0 | >         | —            |             | T7IP<2:0>  |               | 4444          |

| IPC13       | 00BE        | —      | C       | 2RXIP<2:   | 0>      | _       | I                   | NT4IP<2:0 | )>          | _          |              | INT3IP<2:0  | >         | _            |             | T9IP<2:0>  |               | 4444          |

| IPC14       | 00C0        | —      | _       | _          | _       | _       |                     | QEIIP<2:0 | >           | _          |              | PWMIP<2:0   | >         | —            |             | C2IP<2:0>  |               | 0444          |

| IPC15       | 00C2        | —      | I       | FLTAIP<2:( | )>      | _       |                     | —         | _           | —          |              | DMA5IP<2:0  | >         | —            | —           | —          |               | 4040          |

| IPC16       | 00C4        | _      |         | —          | —       | —       |                     | U2EIP<2:0 | )>          | —          |              | U1EIP<2:0>  | >         | —            | F           | LTBIP<2:0  | >             | 0444          |

| IPC17       | 00C6        | —      | (       | C2TXIP<2:  | )>      | —       | C                   | C1TXIP<2: | 0>          | —          |              | DMA7IP<2:0  | >         | —            | D           | MA6IP<2:0  | >             | 4444          |

| INTTREG     | 00E0        | —      | —       | —          | _       |         | ILR<                | 3:0>      |             | —          |              |             | VE        | CNUM<6:0>    |             |            |               | 0000          |

|             |             |        |         |            |         |         |                     |           |             |            |              |             |           |              |             |            |               |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

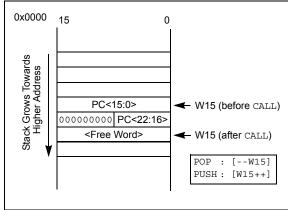

#### 4.2.7 SOFTWARE STACK

In addition to its use as a working register, the W15 register in the dsPIC33FJXXXMCX06/X08/X10 devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | concatenates the SRL register to the MSb |

|       | of the PC prior to the push.             |

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### FIGURE 4-6: CALL STACK FRAME

#### 4.2.8 DATA RAM PROTECTION FEATURE

The dsPIC33FJXXXMCX06/X08/X10 devices supports Data RAM protection features which enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

#### 4.3 Instruction Addressing Modes

The addressing modes in Table 4-36 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions are somewhat different from those in the other instruction types.

#### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

#### 4.3.2 MCU INSTRUCTIONS

The 3-operand MCU instructions are of the following form:

Operand 3 = Operand 1 < function> Operand 2

where Operand 1 is always a working register (i.e., the addressing mode can only be register direct) which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing, since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can only be configured to operate in one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers which have a power-of-2 length. As these buffers satisfy the start and end address criteria, they may operate in a bidirectional mode (i.e., address boundary checks will be performed on both the lower and upper address boundaries).

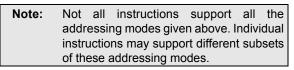

#### 4.4.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.4.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select which registers will operate with Modulo Addressing. If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled. Similarly, if YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM) to which Modulo Addressing is to be applied is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

#### FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

#### **REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2 (CONTINUED)**

| bit 2 | C1RXIF: ECAN1 Receive Data Ready Interrupt Flag Status bit |

|-------|------------------------------------------------------------|

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| bit 1 | SPI2IF: SPI2 Event Interrupt Flag Status bit               |

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| bit 0 | SPI2EIF: SPI2 Error Interrupt Flag Status bit              |

- SPI2EIF: SPI2 Error Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

#### REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3 (CONTINUED)

- bit 1 SI2C2IF: I2C2 Slave Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 T7IF: Timer7 Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| R/W-0           | R/W-0                                                                                                                             | R/W-0                               | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| U2TXIE          | U2RXIE                                                                                                                            | INT2IE                              | T5IE             | T4IE             | OC4IE            | OC3IE           | DMA2IE  |  |  |  |  |

| bit 15          |                                                                                                                                   |                                     |                  |                  |                  |                 | bit 8   |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                             | R/W-0                               | R/W-0            | R/W-0            | U-0              | R/W-0           | R/W-0   |  |  |  |  |

| IC8IE           | IC7IE                                                                                                                             | AD2IE                               | INT1IE           | CNIE             | _                | MI2C1IE         | SI2C1IE |  |  |  |  |

| bit 7           |                                                                                                                                   |                                     |                  |                  |                  | _               | bit 0   |  |  |  |  |

| Legend:         |                                                                                                                                   |                                     |                  |                  |                  |                 |         |  |  |  |  |

| R = Readable    | bit                                                                                                                               | W = Writable                        | bit              | U = Unimplei     | mented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value at F | POR                                                                                                                               | '1' = Bit is set                    |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |

|                 |                                                                                                                                   |                                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 15          | U2TXIE: UAF                                                                                                                       | RT2 Transmitte                      | r Interrupt Ena  | able bit         |                  |                 |         |  |  |  |  |

|                 |                                                                                                                                   | request enable                      |                  |                  |                  |                 |         |  |  |  |  |

| bit 14          | -                                                                                                                                 | request not ena                     |                  | la hit           |                  |                 |         |  |  |  |  |

| DIL 14          | <b>U2RXIE:</b> UART2 Receiver Interrupt Enable bit<br>1 = Interrupt request enabled                                               |                                     |                  |                  |                  |                 |         |  |  |  |  |

|                 |                                                                                                                                   | request not ena                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 13          | INT2IE: External Interrupt 2 Enable bit                                                                                           |                                     |                  |                  |                  |                 |         |  |  |  |  |

|                 | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                      |                                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 12          | T5IE: Timer5 Interrupt Enable bit                                                                                                 |                                     |                  |                  |                  |                 |         |  |  |  |  |

|                 | 1 = Interrupt request enabled                                                                                                     |                                     |                  |                  |                  |                 |         |  |  |  |  |

|                 | 0 = Interrupt request not enabled                                                                                                 |                                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 11          | T4IE: Timer4 Interrupt Enable bit                                                                                                 |                                     |                  |                  |                  |                 |         |  |  |  |  |

|                 | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                      |                                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 10          | <b>OC4IE:</b> Output Compare Channel 4 Interrupt Enable bit                                                                       |                                     |                  |                  |                  |                 |         |  |  |  |  |

|                 | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                      |                                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 9           | -                                                                                                                                 | •                                   |                  | upt Enable bit   |                  |                 |         |  |  |  |  |

|                 | <b>OC3IE:</b> Output Compare Channel 3 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |                                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 8           | -                                                                                                                                 | •                                   |                  | Complete Inter   | rupt Enable bit  |                 |         |  |  |  |  |

|                 |                                                                                                                                   |                                     |                  |                  |                  |                 |         |  |  |  |  |

|                 | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                      |                                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 7           | IC8IE: Input (                                                                                                                    | Capture Chann                       | el 8 Interrupt I | Enable bit       |                  |                 |         |  |  |  |  |

|                 | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                      |                                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 6           | -                                                                                                                                 | •                                   |                  | Enchlo hit       |                  |                 |         |  |  |  |  |

|                 | IC7IE: Input Capture Channel 7 Interrupt Enable bit<br>1 = Interrupt request enabled                                              |                                     |                  |                  |                  |                 |         |  |  |  |  |

|                 | 0 = Interrupt request not enabled                                                                                                 |                                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 5           |                                                                                                                                   | 2 Conversion C                      | -                | rupt Enable bit  | t                |                 |         |  |  |  |  |

|                 |                                                                                                                                   | request enable                      |                  |                  |                  |                 |         |  |  |  |  |

| bit 4           | •                                                                                                                                 | request not ena<br>rnal Interrupt 1 |                  |                  |                  |                 |         |  |  |  |  |

|                 |                                                                                                                                   | mai interiupt T                     |                  |                  |                  |                 |         |  |  |  |  |

|                 | 1 = Interrupt i                                                                                                                   | request enable                      | d                |                  |                  |                 |         |  |  |  |  |

#### REGISTER 7-22: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

| U-0           | R/W-1                                                                             | R/W-0                                                               | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| _             |                                                                                   | U2TXIP<2:0>                                                         |                 | _                |                 | U2RXIP<2:0>     |       |  |  |  |  |  |

| bit 15        |                                                                                   |                                                                     |                 |                  |                 |                 | bit 8 |  |  |  |  |  |

|               |                                                                                   |                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

| U-0           | R/W-1                                                                             | R/W-0                                                               | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|               |                                                                                   | INT2IP<2:0>                                                         |                 | _                |                 | T5IP<2:0>       | L :4  |  |  |  |  |  |

| bit 7         |                                                                                   |                                                                     |                 |                  |                 |                 | bit   |  |  |  |  |  |

| Legend:       |                                                                                   |                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

| R = Readabl   | e bit                                                                             | W = Writable                                                        | bit             | U = Unimpler     | mented bit, rea | d as '0'        |       |  |  |  |  |  |

| -n = Value at | POR                                                                               | '1' = Bit is set                                                    |                 | '0' = Bit is cle | ared            | x = Bit is unkr | iown  |  |  |  |  |  |

| bit 15        | Unimpleme                                                                         | ented: Read as '                                                    | )'              |                  |                 |                 |       |  |  |  |  |  |

| bit 14-12     |                                                                                   | )>: UART2 Trans                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | 111 = Interr                                                                      | upt is priority 7 (I                                                | nighest priorit | y interrupt)     |                 |                 |       |  |  |  |  |  |

|               | •                                                                                 | •                                                                   |                 |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                 | •                                                                   |                 |                  |                 |                 |       |  |  |  |  |  |

|               |                                                                                   | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 11        |                                                                                   | -                                                                   |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 10-8      | Unimplemented: Read as '0'<br>U2RXIP<2:0>: UART2 Receiver Interrupt Priority bits |                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | 111 = Interrupt is priority 7 (highest priority interrupt)                        |                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                 |                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                 |                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | •<br>001 = Interr                                                                 | •<br>001 = Interrupt is priority 1                                  |                 |                  |                 |                 |       |  |  |  |  |  |

|               | 000 = Interrupt source is disabled                                                |                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 7         | Unimpleme                                                                         | nted: Read as 'o                                                    | )'              |                  |                 |                 |       |  |  |  |  |  |

| bit 6-4       | INT2IP<2:0                                                                        | >: External Interr                                                  | upt 2 Priority  | bits             |                 |                 |       |  |  |  |  |  |

|               | 111 = Interr                                                                      | 111 = Interrupt is priority 7 (highest priority interrupt)          |                 |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                 |                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                 |                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | 001 = Interrupt is priority 1                                                     |                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | 000 = Interr                                                                      | upt source is dis                                                   | abled           |                  |                 |                 |       |  |  |  |  |  |

| bit 3         | Unimpleme                                                                         | ented: Read as 'o                                                   | )'              |                  |                 |                 |       |  |  |  |  |  |

| bit 2-0       | T5IP<2:0>:                                                                        | Timer5 Interrupt                                                    | Priority bits   |                  |                 |                 |       |  |  |  |  |  |

|               | 111 = Interr                                                                      | upt is priority 7 (I                                                | nighest priorit | y interrupt)     |                 |                 |       |  |  |  |  |  |

|               | •                                                                                 |                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                 |                                                                     |                 |                  |                 |                 |       |  |  |  |  |  |

|               |                                                                                   | upt is priority 1                                                   |                 |                  |                 |                 |       |  |  |  |  |  |

|               | a a a lusta un                                                                    | upt source is dis                                                   |                 |                  |                 |                 |       |  |  |  |  |  |

| U-0                            | R/W-1                                                                                                       | R/W-0                                                                                                                                | R/W-0                                                                | U-0                             | R/W-1            | R/W-0           | R/W-0 |  |  |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------|------------------|-----------------|-------|--|--|--|--|

| _                              |                                                                                                             | T6IP<2:0>                                                                                                                            |                                                                      | —                               |                  | DMA4IP<2:0>     |       |  |  |  |  |

| bit 15                         |                                                                                                             |                                                                                                                                      |                                                                      |                                 |                  |                 | bit   |  |  |  |  |

| U-0                            | U-0                                                                                                         | U-0                                                                                                                                  | U-0                                                                  | U-0                             | R/W-1            | R/W-0           | R/W-0 |  |  |  |  |

| _                              | _                                                                                                           | _                                                                                                                                    | _                                                                    | _                               |                  | OC8IP<2:0>      |       |  |  |  |  |

| bit 7                          |                                                                                                             |                                                                                                                                      |                                                                      |                                 |                  |                 | bit   |  |  |  |  |

|                                |                                                                                                             |                                                                                                                                      |                                                                      |                                 |                  |                 |       |  |  |  |  |

| Legend:                        |                                                                                                             |                                                                                                                                      |                                                                      |                                 |                  |                 |       |  |  |  |  |

| R = Readab                     |                                                                                                             | W = Writable                                                                                                                         | bit                                                                  | -                               | nented bit, read |                 |       |  |  |  |  |

| -n = Value a                   | It POR                                                                                                      | '1' = Bit is set                                                                                                                     |                                                                      | '0' = Bit is cle                | ared             | x = Bit is unkn | own   |  |  |  |  |

|                                |                                                                                                             |                                                                                                                                      |                                                                      |                                 |                  |                 |       |  |  |  |  |

| bit 15                         | -                                                                                                           | nted: Read as '                                                                                                                      |                                                                      |                                 |                  |                 |       |  |  |  |  |

| bit 14-12                      |                                                                                                             | T6IP<2:0>: Timer6 Interrupt Priority bits                                                                                            |                                                                      |                                 |                  |                 |       |  |  |  |  |

|                                | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                       |                                                                                                                                      |                                                                      |                                 |                  |                 |       |  |  |  |  |

|                                |                                                                                                             |                                                                                                                                      |                                                                      |                                 |                  |                 |       |  |  |  |  |

|                                | •                                                                                                           |                                                                                                                                      |                                                                      |                                 |                  |                 |       |  |  |  |  |

|                                | 001 = Interr                                                                                                | 001 = Interrupt is priority 1                                                                                                        |                                                                      |                                 |                  |                 |       |  |  |  |  |

|                                |                                                                                                             | upt source is dis                                                                                                                    | abled                                                                |                                 |                  |                 |       |  |  |  |  |

| bit 11                         | Unimpleme                                                                                                   | nted: Read as 'o                                                                                                                     | י)                                                                   |                                 |                  |                 |       |  |  |  |  |

|                                | DMA4IP<2:0>: DMA Channel 4 Data Transfer Complete Interrupt Priority bits                                   |                                                                                                                                      |                                                                      |                                 |                  |                 |       |  |  |  |  |

| bit 10-8                       |                                                                                                             | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                           |                                                                      |                                 |                  |                 |       |  |  |  |  |

| bit 10-8                       |                                                                                                             |                                                                                                                                      |                                                                      | •                               | Interrupt Priori |                 |       |  |  |  |  |

| dit 10-8                       |                                                                                                             |                                                                                                                                      |                                                                      | •                               | Interrupt Priori |                 |       |  |  |  |  |

| dit 10-8                       |                                                                                                             |                                                                                                                                      |                                                                      | •                               | Interrupt Priori |                 |       |  |  |  |  |

| dit 10-8                       | 111 = Intern<br>•<br>•                                                                                      | upt is priority 7 (l                                                                                                                 |                                                                      | •                               | Interrupt Priori | ly bits         |       |  |  |  |  |

| dit 10-8                       | 111 = Intern<br>•<br>•<br>•<br>•<br>•<br>•                                                                  | upt is priority 7 (l<br>upt is priority 1                                                                                            | nighest priority                                                     | •                               | Interrupt Priori |                 |       |  |  |  |  |

|                                | 111 = Intern<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis                                                                       | nighest priority<br>abled                                            | •                               | Interrupt Priori |                 |       |  |  |  |  |

| bit 7-3                        | 111 = Intern<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as 'd                                            | nighest priority<br>abled                                            | y interrupt)                    |                  |                 |       |  |  |  |  |

| bit 7-3                        | 111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>OC8IP<2:0>                           | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as 'o<br>•: Output Compa                         | abled<br>o <sup>'</sup>                                              | y interrupt)<br>Interrupt Prior |                  |                 |       |  |  |  |  |

| bit 7-3                        | 111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>OC8IP<2:0>                           | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as 'd                                            | abled<br>o <sup>'</sup>                                              | y interrupt)<br>Interrupt Prior |                  | LY DILS         |       |  |  |  |  |

| bit 7-3                        | 111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>OC8IP<2:0>                           | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as 'o<br>•: Output Compa                         | abled<br>o <sup>'</sup>                                              | y interrupt)<br>Interrupt Prior |                  | LY DILS         |       |  |  |  |  |

| bit 7-3                        | 111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>OC8IP<2:0><br>111 = Intern                     | upt is priority 7 (l<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as 'd<br>•: Output Compa<br>upt is priority 7 (l | abled<br>o <sup>'</sup>                                              | y interrupt)<br>Interrupt Prior |                  | LY DILS         |       |  |  |  |  |

| bit 10-8<br>bit 7-3<br>bit 2-0 | <pre>111 = Intern</pre>                                                                                     | upt is priority 7 (I<br>upt is priority 1<br>upt source is dis<br><b>nted:</b> Read as 'o<br>•: Output Compa                         | nighest priority<br>abled<br>o'<br>ire Channel 8<br>nighest priority | y interrupt)<br>Interrupt Prior |                  | LY DILS         |       |  |  |  |  |

#### **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

| bit 1 | LPOSCEN: Secondary (LP) Oscillator Enable bit       |

|-------|-----------------------------------------------------|

|       | <ol> <li>1 = Enable secondary oscillator</li> </ol> |

|       | 0 = Disable secondary oscillator                    |

bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **Section 7. "Oscillator"** (DS70186) in the *"dsPIC33F Family Reference Manual"* (available from the Microchip website) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

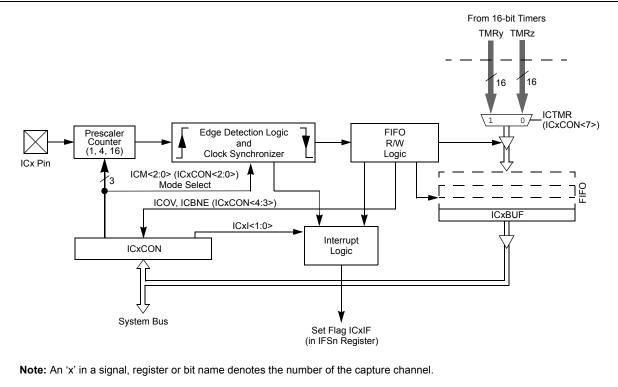

#### 14.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "Input Capture" (DS70198) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33FJXXXMCX06/X08/X10 devices support up to eight input capture channels.

The input capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- Simple Capture Event modes

Capture timer value on every falling edge of

input at ICx pin

- -Capture timer value on every rising edge of input at ICx pin

- 2. Capture timer value on every edge (rising and falling) of input at ICx pin

- 3. Prescaler Capture Event modes

- Capture timer value on every 4th rising edge of input at ICx pin

- -Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include the following:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- Interrupt on input capture event

- · 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

Note: Only IC1 and IC2 can trigger a DMA data transfer. If DMA data transfers are required, the FIFO buffer size must be set to '1' (ICI<1:0> = 00).

#### FIGURE 14-1: INPUT CAPTURE BLOCK DIAGRAM

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode disabled</li> </ul>                                                                         |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                            |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                           |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                       |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                     |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                      |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                                                                        |

|       | 0 = Framing error has not been detected                                                                                                                                                                                         |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read/clear only)                                                                                                                                                                 |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed. Clearing a previously set OERR bit (1 → 0 transition) will reset<br/>the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                                                                            |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                   |

**Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F Family Reference Manual"* for information on enabling the UART module for transmit operation.

**REGISTER 21-3:** CiVEC: ECAN<sup>™</sup> INTERRUPT CODE REGISTER

| U-0          | U-0                                   | U-0                                  | R-0     | R-0              | R-0            | R-0             | R-0   |  |  |  |

|--------------|---------------------------------------|--------------------------------------|---------|------------------|----------------|-----------------|-------|--|--|--|

|              | —                                     | —                                    |         |                  | FILHIT<4:(     | )>              |       |  |  |  |

| bit 15       |                                       |                                      |         |                  |                |                 | bit 8 |  |  |  |

| U-0          | R-1                                   | R-0                                  | R-0     | R-0              | R-0            | R-0             | R-0   |  |  |  |

|              |                                       |                                      |         | ICODE<6:0>       |                |                 |       |  |  |  |

| bit 7        |                                       |                                      |         |                  |                |                 | bit ( |  |  |  |

| Legend:      |                                       |                                      |         |                  |                |                 |       |  |  |  |

| R = Readab   | le bit                                | W = Writable b                       | bit     | U = Unimplen     | nented bit, re | ad as '0'       |       |  |  |  |

| -n = Value a | t POR                                 | R '1' = Bit is set                   |         | '0' = Bit is cle | ared           | x = Bit is unkr | nown  |  |  |  |

| bit 15-13    | Unimplement                           | ed: Read as 'o                       | ,       |                  |                |                 |       |  |  |  |

| bit 12-8     | FILHIT<4:0>:                          | Filter Hit Numb                      | er bits |                  |                |                 |       |  |  |  |

|              | 10000-11111<br>01111 <b>= Filte</b> r |                                      |         |                  |                |                 |       |  |  |  |

|              | 00001 = Filter<br>00000 = Filter      |                                      |         |                  |                |                 |       |  |  |  |

| bit 7        | Unimplement                           | ed: Read as 'o                       | ,       |                  |                |                 |       |  |  |  |

| bit 6-0      | ICODE<6:0>: Interrupt Flag Code bits  |                                      |         |                  |                |                 |       |  |  |  |

|              |                                       | 11111 = Reser                        |         |                  |                |                 |       |  |  |  |

|              |                                       | FO almost full i                     | -       |                  |                |                 |       |  |  |  |

|              |                                       | eceiver overflov<br>ake-up interrup  |         |                  |                |                 |       |  |  |  |

|              | 1000001 = Er                          |                                      |         |                  |                |                 |       |  |  |  |

|              | 1000000 <b>= No</b>                   | o interrupt                          |         |                  |                |                 |       |  |  |  |

|              |                                       | 11111 <b>= Reser</b>                 |         |                  |                |                 |       |  |  |  |

|              |                                       | B15 buffer Inter                     | rupt    |                  |                |                 |       |  |  |  |

|              | <br>0001001 <b>= R</b>                | 39 buffer interr                     | upt     |                  |                |                 |       |  |  |  |

|              |                                       | 38 buffer interr                     |         |                  |                |                 |       |  |  |  |

|              |                                       | RB7 buffer inter                     |         |                  |                |                 |       |  |  |  |

|              |                                       | RB6 buffer inter<br>RB5 buffer inter |         |                  |                |                 |       |  |  |  |

|              |                                       | RB4 buffer inter                     |         |                  |                |                 |       |  |  |  |

|              |                                       | RB3 buffer inter                     |         |                  |                |                 |       |  |  |  |

|              | 0000010 = TF                          | RB2 buffer inter                     | rupt    |                  |                |                 |       |  |  |  |

|              |                                       | RB1 buffer inter                     |         |                  |                |                 |       |  |  |  |

|              | $0000000 = \mathbf{IF}$               | RB0 Buffer inte                      | nupt    |                  |                |                 |       |  |  |  |

### DS70287C-page 220

| R/W-0             | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                                            | U-0                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                                                             | R/W-0                                                                                                            | R/W-0           |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------|