Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

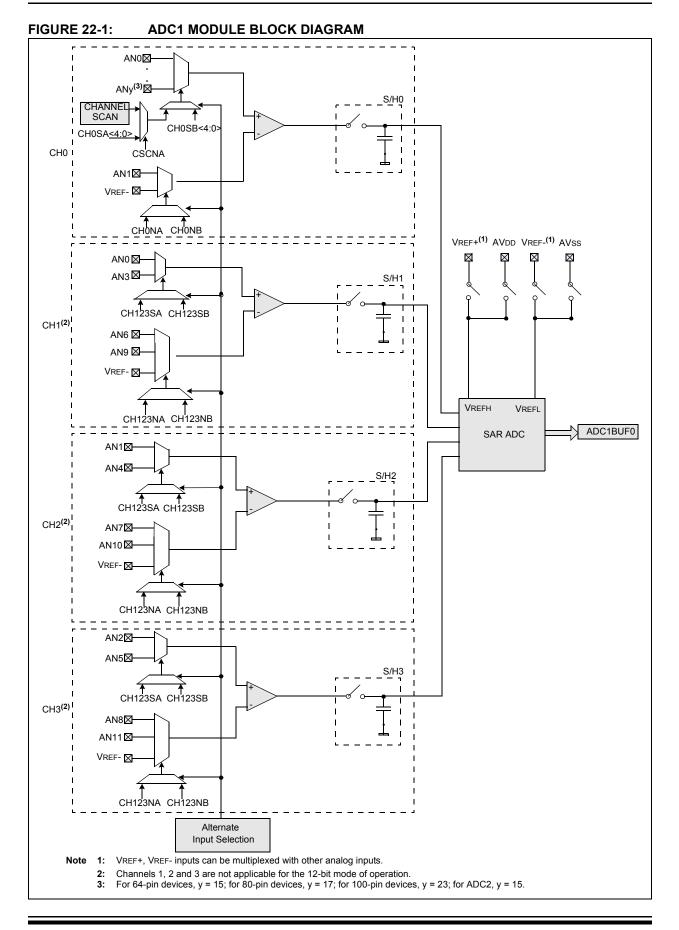

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc510-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz <  $F_{IN}$  < 8 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

#### 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 2, ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in this register that correspond to the A/D pins that are initialized by MPLAB ICD 2, ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 2, ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

#### 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor to Vss on unused pins and drive the output to logic low.

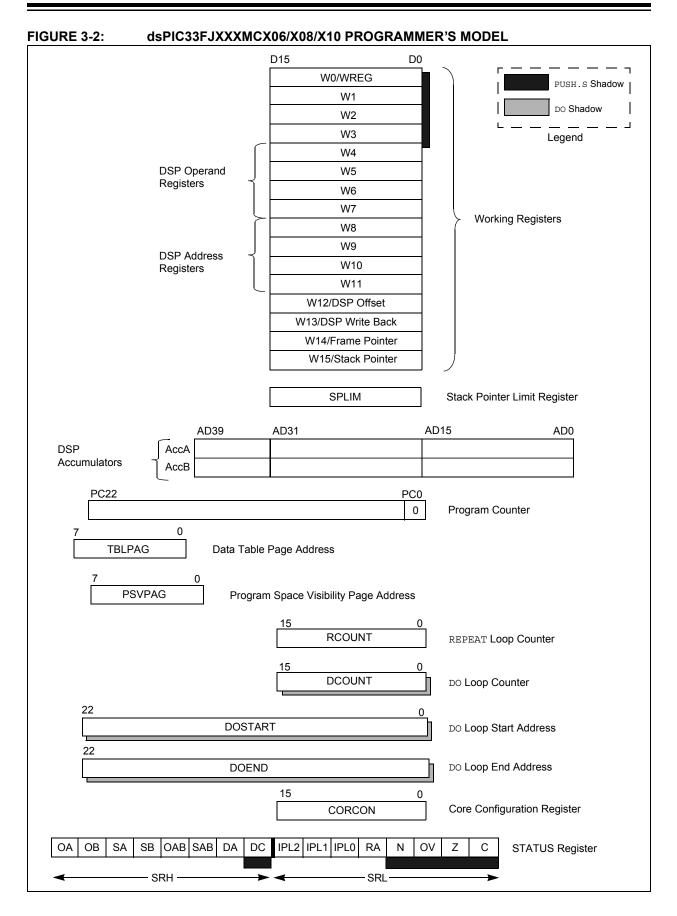

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                             |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                           |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                   |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                     |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = An operation which affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation which affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                   |

| bit 0   | <b>C:</b> MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                        |

- Note 1: This bit may be read or cleared (not set).

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

#### 5.2 RTSP Operation

The dsPIC33FJXXXMCX06/X08/X10 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase a page of memory at a time, which consists of eight rows (512 instructions), and to program one row or one word at a time. Table 26-12 shows typical erase and programming times. The 8-row erase pages and single-row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers in sequential order. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

#### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

The programming time depends on the FRC accuracy (see Table 26-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time and Word Write Cycle Time parameters (see Table 26-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +85°C, the FRC accuracy will be  $\pm 2\%$ . If the TUN<5:0> bits (see Register 9-4) are set to `b111111, the Minimum Row Write Time is:

$$T_{RW} = \frac{11064 \text{ Cycles}}{7.37 \text{ MHz} \times (1 + 0.02) \times (1 - 0.00375)} = 1.48 \text{ms}$$

and, the Maximum Row Write Time is:

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 - 0.02) \times (1 - 0.00375)} = 1.54 ms$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

#### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit                                                                |

|-------|-------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Address error trap has occurred</li><li>0 = Address error trap has not occurred</li></ul> |

| bit 2 | STKERR: Stack Error Trap Status bit                                                                   |

|       | <ol> <li>Stack error trap has occurred</li> </ol>                                                     |

|       | 0 = Stack error trap has not occurred                                                                 |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit                                                    |

|       | 1 = Oscillator failure trap has occurred                                                              |

|       | 0 = Oscillator failure trap has not occurred                                                          |

| bit 0 | Unimplemented: Read as '0'                                                                            |

#### 13.0 TIMER2/3, TIMER4/5, TIMER6/7 AND TIMER8/9

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 11.** "**Timers**" (DS70205) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The Timer2/3, Timer4/5, Timer6/7 and Timer8/9 modules are 32-bit timers that can also be configured as four independent 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3, Timer4/5, Timer6/7 and Timer8/9 operate in three modes:

- Two Independent 16-bit Timers (e.g., Timer2 and Timer3) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit Timer

- Single 32-bit Synchronous Counter

They also support the following features:

- Timer Gate Operation

- Selectable Prescaler Settings

- · Timer Operation during Idle and Sleep modes

- Interrupt on a 32-bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (Timer2/3 only)

- ADC2 Event Trigger (Timer4/5 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON, T5CON, T6CON, T7CON, T8CON and T9CON registers. T2CON, T4CON, T6CON and T8CON are shown in generic form in Register 13-1. T3CON, T5CON, T7CON and T9CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2, Timer4, Timer6 or Timer8 is the least significant word; Timer3, Timer5, Timer7 or Timer9 is the most significant word of the 32-bit timers. Note: For 32-bit operation, T3CON, T5CON, T7CON and T9CON control bits are ignored. Only T2CON, T4CON, T6CON and T8CON control bits are used for setup and control. Timer2, Timer4, Timer6 and Timer8 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3, Timer5, Ttimer7 and Timer9 interrupt flags.

To configure Timer2/3, Timer4/5, Timer6/7 or Timer8/9 for 32-bit operation, do the following:

- 1. Set the corresponding T32 control bit.

- 2. Select the prescaler ratio for Timer2, Timer4, Timer6 or Timer8 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3, PR5, PR7 or PR9 contains the most significant word of the value, while PR2, PR4, PR6 or PR8 contains the least significant word.

- If interrupts are required, set the interrupt enable bit, T3IE, T5IE, T7IE or T9IE. Use the priority bits, T3IP<2:0>, T5IP<2:0>, T7IP<2:0> or T9IP<2:0>, to set the interrupt priority. While Timer2, Timer4, Timer6 or Timer8 control the timer, the interrupt appears as a Timer3, Timer5, Timer7 or Timer9 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair, TMR3:TMR2, TMR5:TMR4, TMR7:TMR6 or TMR9:TMR8. TMR3, TMR5, TMR7 or TMR9 always contain the most significant word of the count, while TMR2, TMR4, TMR6 or TMR8 contain the least significant word.

To configure any of the timers for individual 16-bit operation, do the following:

- 1. Clear the T32 bit corresponding to that timer.

- Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

A block diagram for a 32-bit timer pair (Timer4/5) example is shown in Figure 13-1, and a timer (Timer4) operating in 16-bit mode example is shown in Figure 13-2.

Note: Only Timer2 and Timer3 can trigger a DMA data transfer.

#### REGISTER 13-2: TyCON (T3CON, T5CON, T7CON OR T9CON) CONTROL REGISTER

| R/W-0              | U-0 | R/W-0                | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|----------------------|-----|-----|-----|-----|-------|

| TON <sup>(1)</sup> | —   | TSIDL <sup>(2)</sup> | _   | —   | —   | —   | —     |

| bit 15             |     |                      |     |     |     |     | bit 8 |

| U-0   | R/W-0                | R/W-0 | R/W-0                | U-0 | U-0 | R/W-0                | U-0   |

|-------|----------------------|-------|----------------------|-----|-----|----------------------|-------|

| —     | TGATE <sup>(1)</sup> | TCKPS | <1:0> <sup>(1)</sup> | —   | —   | TCS <sup>(1,3)</sup> | —     |

| bit 7 |                      |       |                      |     |     |                      | bit 0 |

| Legend:      |                                             |                                              |                                      |                    |  |  |

|--------------|---------------------------------------------|----------------------------------------------|--------------------------------------|--------------------|--|--|

| R = Readab   | le bit                                      | W = Writable bit                             | U = Unimplemented bit,               | , read as '0'      |  |  |

| -n = Value a | = Value at POR '1' = Bit is set             |                                              | '0' = Bit is cleared                 | x = Bit is unknown |  |  |

| bit 15       | TON: Tim                                    | ery On bit <sup>(1)</sup>                    |                                      |                    |  |  |

|              |                                             | 16-bit Timery<br>16-bit Timery               |                                      |                    |  |  |

| bit 14       | Unimpler                                    | nented: Read as '0'                          |                                      |                    |  |  |

| bit 13       | TSIDL: Stop in Idle Mode bit <sup>(2)</sup> |                                              |                                      |                    |  |  |

|              |                                             | ntinue module operation who                  | en device enters Idle mode<br>e mode |                    |  |  |

| bit 12-7     | Unimpler                                    | nented: Read as '0'                          |                                      |                    |  |  |

| bit 6        | TGATE: 1                                    | imery Gated Time Accumu                      | lation Enable bit <sup>(1)</sup>     |                    |  |  |

|              | When TC<br>This bit is                      |                                              |                                      |                    |  |  |

|              | $\frac{\text{When TC}}{1 = \text{Gates}}$   | <u>S = 0:</u><br>I time accumulation enabled | 4                                    |                    |  |  |

|              |                                             | time accumulation disable                    |                                      |                    |  |  |

| bit 5-4      | TCKPS<1                                     | I:0>: Timer3 Input Clock Pr                  | escale Select bits <sup>(1)</sup>    |                    |  |  |

|              | 11 <b>= 1:25</b>                            | 6                                            |                                      |                    |  |  |

|              | 10 <b>= 1:64</b>                            |                                              |                                      |                    |  |  |

|              | 01 = 1:8<br>00 = 1:1                        |                                              |                                      |                    |  |  |

| bit 3-2      |                                             | nented: Read as '0'                          |                                      |                    |  |  |

| bit 1        | •                                           | ery Clock Source Select bit                  | (1.3)                                |                    |  |  |

|              |                                             | nal clock from pin TyCK (on                  |                                      |                    |  |  |

|              |                                             | al clock (FCY)                               | the hong edge                        |                    |  |  |

| bit 0        | Unimpler                                    |                                              |                                      |                    |  |  |

- 2: When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

- 3: The TyCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

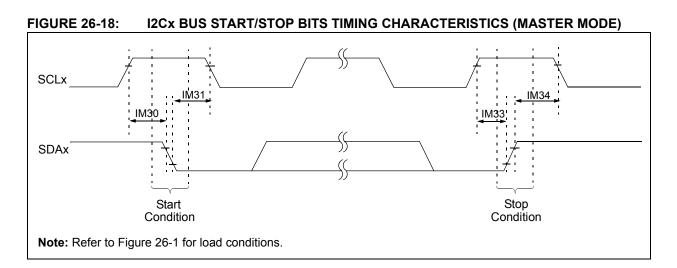

| R-0 HSC         | R-0 HSC                                                                                                                                                                                                                                                             | U-0                                  | U-0                              | U-0                      | R/C-0 HS                | R-0 HSC                               | R-0 HSC         |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------|--------------------------|-------------------------|---------------------------------------|-----------------|

| ACKSTAT         | TRSTAT                                                                                                                                                                                                                                                              | _                                    | _                                | _                        | BCL                     | GCSTAT                                | ADD10           |

| bit 15          |                                                                                                                                                                                                                                                                     |                                      |                                  |                          |                         |                                       | bit 8           |

|                 |                                                                                                                                                                                                                                                                     |                                      |                                  |                          |                         |                                       |                 |

| R/C-0 HS        | R/C-0 HS                                                                                                                                                                                                                                                            | R-0 HSC                              | R/C-0 HSC                        | R/C-0 HSC                | R-0 HSC                 | R-0 HSC                               | R-0 HSC         |

| IWCOL           | I2COV                                                                                                                                                                                                                                                               | D_A                                  | Р                                | S                        | R_W                     | RBF                                   | TBF             |

| bit 7           |                                                                                                                                                                                                                                                                     |                                      |                                  |                          |                         |                                       | bit 0           |

| Legend:         |                                                                                                                                                                                                                                                                     | U = Unimpler                         | nented bit rea                   | ad as '0'                |                         |                                       |                 |

| R = Readable    | bit                                                                                                                                                                                                                                                                 | W = Writable                         |                                  | HS = Set in h            | ardware                 | HSC = Hardwa                          | are set/cleared |

| -n = Value at P | OR                                                                                                                                                                                                                                                                  | '1' = Bit is set                     |                                  | '0' = Bit is cle         | ared                    | x = Bit is unkr                       | iown            |

|                 |                                                                                                                                                                                                                                                                     |                                      |                                  |                          |                         |                                       |                 |

| bit 15          | ACKSTAT: Acknowledge Status bit<br>(when operating as I <sup>2</sup> C master, applicable to master transmit operation)<br>1 = NACK received from slave<br>0 = ACK received from slave<br>Hardware set or clear at end of slave Acknowledge.                        |                                      |                                  |                          |                         |                                       |                 |

| bit 14          |                                                                                                                                                                                                                                                                     |                                      |                                  | -                        | ster, applicable        | to master trans                       | smit operation) |

|                 | <ul> <li>1 = Master transmit is in progress (8 bits + ACK)</li> <li>0 = Master transmit is not in progress</li> <li>Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.</li> </ul>                                        |                                      |                                  |                          |                         |                                       | nowledge.       |

| bit 13-11       | Unimplement                                                                                                                                                                                                                                                         | ted: Read as '                       | 0'                               |                          |                         |                                       |                 |

| bit 10          | BCL: Master                                                                                                                                                                                                                                                         | Bus Collision [                      | Detect bit                       |                          |                         |                                       |                 |

|                 | <ul> <li>1 = A bus collision has been detected during a master operation</li> <li>0 = No collision</li> <li>Hardware set at detection of bus collision.</li> </ul>                                                                                                  |                                      |                                  |                          |                         |                                       |                 |

| bit 9           | GCSTAT: Ger                                                                                                                                                                                                                                                         | neral Call Statu                     | ıs bit                           |                          |                         |                                       |                 |

|                 | <ul> <li>1 = General call address was received</li> <li>0 = General call address was not received</li> <li>Hardware set when address matches general call address. Hardware clear at Stop detection.</li> </ul>                                                     |                                      |                                  |                          |                         |                                       | ection.         |

| bit 8           | ADD10: 10-Bi                                                                                                                                                                                                                                                        | it Address Stat                      | us bit                           |                          |                         |                                       |                 |

|                 | <ul> <li>1 = 10-bit address was matched</li> <li>0 = 10-bit address was not matched</li> <li>Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.</li> </ul>                                                              |                                      |                                  |                          |                         |                                       | detection.      |

| bit 7           | IWCOL: Write                                                                                                                                                                                                                                                        | Collision Dete                       | ect bit                          |                          |                         |                                       |                 |

|                 | <ul> <li>1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> <li>Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).</li> </ul>                               |                                      |                                  |                          |                         |                                       |                 |

| bit 6           |                                                                                                                                                                                                                                                                     |                                      |                                  |                          |                         |                                       |                 |

|                 | <ul> <li>I2COV: Receive Overflow Flag bit</li> <li>1 = A byte was received while the I2CxRCV register is still holding the previous byte</li> <li>0 = No overflow</li> <li>Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).</li> </ul> |                                      |                                  |                          |                         |                                       |                 |

| bit 5           | D_A: Data/Ad                                                                                                                                                                                                                                                        |                                      |                                  |                          | (,,,,                   | · · · · · · · · · · · · · · · · · · · |                 |

|                 | 1 = Indicates 1<br>0 = Indicates 1                                                                                                                                                                                                                                  | that the last by<br>that the last by | rte received w<br>rte received w | as data<br>as device add | ress<br>by reception of | slave byte.                           |                 |

| bit 4           | P: Stop bit                                                                                                                                                                                                                                                         |                                      |                                  |                          |                         |                                       |                 |

|                 | <ul><li>1 = Indicates f</li><li>0 = Stop bit was</li></ul>                                                                                                                                                                                                          |                                      |                                  | ected last               |                         |                                       |                 |

#### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

#### 21.3 Modes of Operation

The CAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization Mode

- Disable Mode

- Normal Operation Mode

- Listen Only Mode

- Listen All Messages Mode

- Loopback Mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module will not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

#### 21.3.1 INITIALIZATION MODE

In the Initialization mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module can not be modified while the module is on-line. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- All Module Control Registers

- Baud Rate and Interrupt Configuration Registers

- Bus Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

#### 21.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits (CiCTRL1<10:8>) = 001, the module will enter the Module Disable mode. If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note: Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set and TXREQ bit is cleared.

#### 21.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins will assume the CAN bus functions. The module will transmit and receive CAN bus messages via the CiTX and CiRX pins.

#### 21.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

#### 21.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting REQOP<2:0> = '111'. In this mode, the data which is in the message assembly buffer, until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

#### 21.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module will connect the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

#### **REGISTER 21-9:** CiCFG1: ECAN<sup>™</sup> BAUD RATE CONFIGURATION REGISTER 1

| U-0                               | U-0                                            | U-0                             | U-0                                | U-0              | U-0    | U-0                | U-0   |

|-----------------------------------|------------------------------------------------|---------------------------------|------------------------------------|------------------|--------|--------------------|-------|

| _                                 | —                                              | _                               | _                                  | _                | _      | _                  | _     |

| bit 15                            |                                                |                                 |                                    |                  |        |                    | bit 8 |

|                                   |                                                |                                 |                                    |                  |        |                    |       |

| R/W-0                             | R/W-0                                          | R/W-0                           | R/W-0                              | R/W-0            | R/W-0  | R/W-0              | R/W-0 |

| SJ\                               | V<1:0>                                         |                                 |                                    | BRF              | P<5:0> |                    |       |

| bit 7                             |                                                |                                 |                                    |                  |        |                    | bit 0 |

|                                   |                                                |                                 |                                    |                  |        |                    |       |

| Legend:                           |                                                |                                 |                                    |                  |        |                    |       |

| R = Readable bit W = Writable bit |                                                | bit                             | U = Unimplemented bit, read as '0' |                  |        |                    |       |

| -n = Value at                     | POR                                            | '1' = Bit is set                |                                    | '0' = Bit is cle | ared   | x = Bit is unknown |       |

|                                   |                                                |                                 |                                    |                  |        |                    |       |

| bit 15-8                          | Unimplemen                                     | ted: Read as '                  | 0'                                 |                  |        |                    |       |

| bit 7-6                           | <b>SJW&lt;1:0&gt;:</b> S                       | synchronization                 | Jump Width                         | bits             |        |                    |       |

|                                   | 11 = Length i                                  |                                 |                                    |                  |        |                    |       |

|                                   | 10 = Length is                                 |                                 |                                    |                  |        |                    |       |

|                                   | 01 = Length is 2 x Tα<br>00 = Length is 1 x Tα |                                 |                                    |                  |        |                    |       |

| bit 5-0                           | C C                                            | Baud Rate Pres                  | caler bits                         |                  |        |                    |       |

|                                   | 11 1111 = $TQ = 2 \times 64 \times 1/FCAN$     |                                 |                                    |                  |        |                    |       |

|                                   | •                                              |                                 |                                    |                  |        |                    |       |

|                                   | •                                              |                                 |                                    |                  |        |                    |       |

|                                   | •                                              |                                 |                                    |                  |        |                    |       |

|                                   |                                                | $Q = 2 \times 3 \times 1/F_{0}$ |                                    |                  |        |                    |       |

|                                   |                                                | $Q = 2 \times 2 \times 1/F_{0}$ |                                    |                  |        |                    |       |

|                                   | 00 0000 = 1                                    | $Q = 2 \times 1 \times 1/Fc$    | CAN                                |                  |        |                    |       |

#### REGISTER 21-13: CIBUFPNT2: ECAN™ FILTER 4-7 BUFFER POINTER REGISTER

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|

| F7BP<3:0> |       |       |       | F6BP  | <3:0> |       |       |

| bit 15    |       |       |       |       |       |       | bit 8 |

|           |       |       |       |       |       |       |       |

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| 10110     | 1010 0 | 10110 | 10110 | 1010 0 | 1010 0 | 10110 | 10110 |

|-----------|--------|-------|-------|--------|--------|-------|-------|

| F5BP<3:0> |        |       |       |        | F4BP   | <3:0> |       |

| bit 7     |        |       |       |        |        |       | bit 0 |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'    |      |

|-------------------------------------------------------------------------|------|

|                                                                         |      |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkn | iown |

| bit 15-12 | F7BP<3:0>: RX Buffer Written when Filter 7 Hits bits |

|-----------|------------------------------------------------------|

| bit 11-8  | F6BP<3:0>: RX Buffer Written when Filter 6 Hits bits |

| bit 7-4   | F5BP<3:0>: RX Buffer Written when Filter 5 Hits bits |

| bit 3-0   | F4BP<3:0>: RX Buffer Written when Filter 4 Hits bits |

#### REGISTER 21-14: CIBUFPNT3: ECAN™ FILTER 8-11 BUFFER POINTER REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0  | R/W-0 |

|--------|-------|-------|-------|-----------|-------|--------|-------|

|        | F11BP | <3:0> |       |           | F10BF | P<3:0> |       |

| bit 15 |       |       |       |           |       |        | bit 8 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0  | R/W-0 |

|        | F9BP< | <3:0> |       | F8BP<3:0> |       |        |       |

| bit 7  |       |       |       |           |       |        | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-12 | F11BP<3:0>: RX Buffer Written when Filter 11 Hits bits |

|-----------|--------------------------------------------------------|

| bit 11-8  | F10BP<3:0>: RX Buffer Written when Filter 10 Hits bits |

| bit 7-4   | F9BP<3:0>: RX Buffer Written when Filter 9 Hits bits   |

| bit 3-0   | F8BP<3:0>: RX Buffer Written when Filter 8 Hits bits   |

#### REGISTER 21-15: CiBUFPNT4: ECAN™ FILTER 12-15 BUFFER POINTER REGISTER

| R/W-0           | R/W-0                                                  | R/W-0            | R/W-0         | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |

|-----------------|--------------------------------------------------------|------------------|---------------|------------------------------------|-------|--------------------|-------|--|

|                 | F15BF                                                  | P<3:0>           |               |                                    | F14B  | SP<3:0>            |       |  |

| bit 15          |                                                        |                  |               |                                    |       |                    | bit 8 |  |

| R/W-0           | R/W-0                                                  | R/W-0            | R/W-0         | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |

|                 | F13BF                                                  | P<3:0>           |               |                                    | F12B  | P<3:0>             |       |  |

| bit 7           |                                                        |                  |               |                                    |       |                    | bit 0 |  |

|                 |                                                        |                  |               |                                    |       |                    |       |  |

| Legend:         |                                                        |                  |               |                                    |       |                    |       |  |

| R = Readable    | bit                                                    | W = Writable     | bit           | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at F | POR                                                    | '1' = Bit is set |               | '0' = Bit is clea                  | ared  | x = Bit is unknown |       |  |

| bit 15-12       | E1588-2.0>                                             | : RX Buffer Wri  | tton whon Fil | tor 15 Hite bite                   |       |                    |       |  |

|                 |                                                        |                  |               |                                    |       |                    |       |  |

| bit 11-8        | F14BP<3:0>                                             | : RX Buffer Wri  | tten when Fil | ter 14 Hits bits                   |       |                    |       |  |

| bit 7-4         | F13BP<3:0>                                             | : RX Buffer Wri  | tten when Fil | ter 13 Hits bits                   |       |                    |       |  |

| bit 3-0         | F12BP<3:0>: RX Buffer Written when Filter 12 Hits bits |                  |               |                                    |       |                    |       |  |

#### REGISTER 21-20: CIRXMnSID: ECAN™ ACCEPTANCE FILTER MASK n STANDARD IDENTIFIER R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x SID10 SID9 SID8 SID7 SID6 SID5 SID4 SID3 bit 15 bit 8

| R/W-x | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-------|-----|-------|-------|

| SID2  | SID1  | SID0  | —   | MIDE  | —   | EID17 | EID16 |

| bit 7 |       |       |     |       |     |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-5 | SID<10:0>: Standard Identifier bits<br>1 = Include bit SIDx in filter comparison<br>0 = Bit SIDx is don't care in filter comparison                                                                                                                                                                |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                         |

| bit 3    | MIDE: Identifier Receive Mode bit                                                                                                                                                                                                                                                                  |

|          | <ul> <li>1 = Match only message types (standard or extended address) that correspond to EXIDE bit in filter</li> <li>0 = Match either standard or extended address message if filters match</li> <li>(i.e., if (Filter SID) = (Message SID) or if (Filter SID/EID) = (Message SID/EID))</li> </ul> |

| bit 2    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                         |

| bit 1-0  | EID<17:16>: Extended Identifier bits                                                                                                                                                                                                                                                               |

|          | <ul> <li>1 = Include bit EIDx in filter comparison</li> <li>0 = Bit EIDx is don't care in filter comparison</li> </ul>                                                                                                                                                                             |

#### REGISTER 21-21: CIRXMnEID: ECAN™ ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER

| R/W-x  | R/W-x | R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x |

|--------|-------|--------|-------|-------|-------|---------|-------|

| EID15  | EID14 | EID13  | EID12 | EID11 | EID10 | EID9    | EID8  |

| bit 15 |       |        |       | •     |       |         | bit 8 |

|        |       |        |       |       |       |         |       |

| R/M-v  | R/M-v | R/\/_v | R/M-v | R/M_v | R/W-x | R/\\/_v | R/W-v |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Include bit EIDx in filter comparison

0 = Bit EIDx is don't care in filter comparison

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| CSS31  | CSS30 | CSS29 | CSS28 | CSS27 | CSS26 | CSS25 | CSS24 |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| CSS23  | CSS22 | CSS21 | CSS20 | CSS19 | CSS18 | CSS17 | CSS16 |

| bit 7  | •     |       | •     |       |       | •     | bit 0 |

#### REGISTER 22-7: ADxCSSH: ADCx INPUT SCAN SELECT REGISTER HIGH<sup>(1,2)</sup>

| Legend:           |                  |                                        |                    |  |  |

|-------------------|------------------|----------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                   | x = Bit is unknown |  |  |

bit 15-0

- CSS<31:16>: ADC Input Scan Selection bits

- 1 =Select ANx for input scan

- 0 = Skip ANx for input scan

- **Note 1:** On devices without 32 analog inputs, all ADxCSSH bits may be selected by user. However, inputs selected for scan without a corresponding input on device will convert VREFL.

- **2:** CSSx = ANx, where x = 16 through 31.

#### **REGISTER 22-8:** ADxCSSL: ADCx INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |  |

|-----------------------------------|-------|------------------|------------------------------------|----------------------------------------|-------|-------|-------|--|

| CSS15                             | CSS14 | CSS13            | CSS12                              | CSS11                                  | CSS10 | CSS9  | CSS8  |  |

| bit 15                            | ·     |                  |                                    |                                        |       |       | bit 8 |  |

|                                   |       |                  |                                    |                                        |       |       |       |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |  |

| CSS7                              | CSS6  | CSS5             | CSS4                               | CSS3                                   | CSS2  | CSS1  | CSS0  |  |

| bit 7                             |       |                  |                                    |                                        |       | •     | bit 0 |  |

|                                   |       |                  |                                    |                                        |       |       |       |  |

| Legend:                           |       |                  |                                    |                                        |       |       |       |  |

| R = Readable bit W = Writable bit |       | oit              | U = Unimplemented bit, read as '0' |                                        |       |       |       |  |

| -n = Value at POR '1' = I         |       | '1' = Bit is set |                                    | '0' = Bit is cleared x = Bit is unknow |       |       | nown  |  |

bit 15-0

**CSS<15:0>:** ADC Input Scan Selection bits 1 = Select ANx for input scan

- 0 = Skip ANx for input scan

- **Note 1:** On devices without 16 analog inputs, all ADxCSSL bits may be selected by user. However, inputs selected for scan without a corresponding input on device will convert VREFL.

- **2:** CSSx = ANx, where x = 0 through 15.

### 24.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33F instruction set is identical to that of the dsPIC30F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- Word or byte-oriented operations

- · Bit-oriented operations

- Literal operations

- · DSP operations

- · Control operations

Table 24-1 shows the general symbols used in describing the instructions.

The dsPIC33F instruction set summary in Table 24-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand which is typically a register 'Wb' without any address modifier

- The second source operand which is typically a register 'Ws' with or without an address modifier

- The destination of the result which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand which is a register 'Wb' without any address modifier

- The second source operand which is a literal value

- The destination of the result (only if not the same as the first source operand) which is typically a register 'Wd' with or without an address modifier

The  ${\tt MAC}$  class of DSP instructions may use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- · The X and Y address space prefetch operations

- · The X and Y address space prefetch destinations

- · The accumulator write back destination

The other DSP instructions do not involve any multiplication and may include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

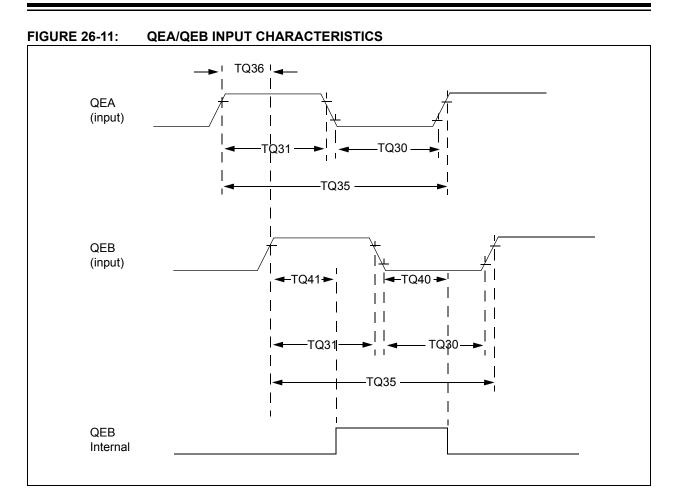

#### TABLE 26-29: QUADRATURE DECODER TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                  | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                    |     |       |                                                  |

|--------------------|--------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                    |                                                                                                                                                 | Тур <sup>(2)</sup> | Max | Units | Conditions                                       |

| TQ30               | TQUL   | Quadrature Input Low Time                        |                                                                                                                                                 | 6 Tcy              | _   | ns    | —                                                |

| TQ31               | ΤουΗ   | Quadrature Input High Time                       |                                                                                                                                                 | 6 Tcy              | _   | ns    | —                                                |

| TQ35               | ΤουΙΝ  | Quadrature Input Period                          |                                                                                                                                                 | 12 TCY             | _   | ns    | —                                                |

| TQ36               | ΤουΡ   | Quadrature Phase Period                          |                                                                                                                                                 | 3 Tcy              | _   | ns    | —                                                |

| TQ40               | TQUFL  | Filter Time to Recognize Low with Digital Filter | V,                                                                                                                                              | 3 * N * Tcy        | _   | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 (Note 3) |

| TQ41               | TQUFH  | Filter Time to Recognize Hig with Digital Filter | h,                                                                                                                                              | 3 * N * Tcy        | _   | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 (Note 3) |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

3: N = Index Channel Digital Filter Clock Divide Select bits. Refer to Section 15. "Quadrature Encoder Interface (QEI)" (DS70208) in the "dsPIC33F Family Reference Manual".

| TABLE 26-43: | ADC CONVERSION ( | 10-BIT MODE | ) TIMING REQUIREMENTS |

|--------------|------------------|-------------|-----------------------|

|              |                  |             |                       |

|                   |        | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ |         |                    |         |       |                                                           |  |

|-------------------|--------|----------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|---------|-------|-----------------------------------------------------------|--|

| Param<br>No.      | Symbol | Characteristic                                                                                                                   | Min.    | Typ <sup>(1)</sup> | Max.    | Units | Conditions                                                |  |

| Clock Parameters  |        |                                                                                                                                  |         |                    |         |       |                                                           |  |

| AD50b             | Tad    | ADC Clock Period                                                                                                                 | 76      |                    |         | ns    | _                                                         |  |

| AD51b             | tRC    | ADC Internal RC Oscillator Period                                                                                                | _       | 250                |         | ns    | —                                                         |  |

| Conversion Rate   |        |                                                                                                                                  |         |                    |         |       |                                                           |  |

| AD55b             | tCONV  | Conversion Time                                                                                                                  | _       | 12 TAD             | _       |       | —                                                         |  |

| AD56b             | FCNV   | Throughput Rate                                                                                                                  | —       |                    | 1.1     | Msps  | —                                                         |  |

| AD57b             | TSAMP  | Sample Time                                                                                                                      | 2 Tad   | —                  | —       | _     | —                                                         |  |

| Timing Parameters |        |                                                                                                                                  |         |                    |         |       |                                                           |  |

| AD60b             | tPCS   | Conversion Start from Sample<br>Trigger <sup>(2)</sup>                                                                           | 2.0 Tad | _                  | 3.0 Tad | _     | Auto-Convert Trigger<br>(SSRC<2:0> = 111) not<br>selected |  |

| AD61b             | tpss   | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2)</sup>                                                                    | 2.0 Tad | —                  | 3.0 Tad |       | _                                                         |  |

| AD62b             | tcss   | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2)</sup>                                                               | -       | 0.5 Tad            | —       | —     | _                                                         |  |

| AD63b             | tdpu   | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2,3)</sup>                                                        | —       | _                  | 20      | μs    | —                                                         |  |

Note 1: These parameters are characterized but not tested in manufacturing.

**2:** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**3:** tDPU is the time required for the ADC module to stabilize when it is turned on (AD1CON1<ADON> = 1). During this time, the ADC result is indeterminate.

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Cleveland Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo, IN Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355

Fax: 86-532-8502-7205 China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049 ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4080

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-572-9526 Fax: 886-3-572-6459

Taiwan - Kaohsiung Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

02/04/09