Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT              |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64mc510-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 2, MPLAB ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip website.

- *"MPLAB<sup>®</sup> ICD 2 In-Circuit Debugger User's Guide"* DS51331

- *"Using MPLAB<sup>®</sup> ICD 2"* (poster) DS51265

- "MPLAB<sup>®</sup> ICD 2 Design Advisory" DS51566

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™" (poster) DS51749

# 2.6 External Oscillator Pins

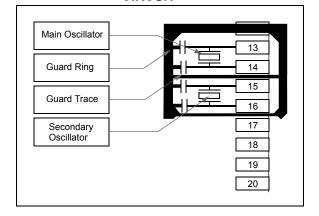

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

# FIGURE 2-3: SU OF

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

# 3.4 CPU Control Registers

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| R-0                  | R-0                                                                                                                                         | R/C-0                                 | R/C-0             | R-0               | R/C-0                             | R -0              | R/W-0          |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------|-------------------|-----------------------------------|-------------------|----------------|--|--|--|

| OA                   | OB                                                                                                                                          | SA <sup>(1)</sup>                     | SB <sup>(1)</sup> | OAB               | SAB                               | DA                | DC             |  |  |  |

| bit 15               |                                                                                                                                             |                                       |                   |                   |                                   |                   | bit 8          |  |  |  |

| R/W-0 <sup>(2)</sup> | D ( A ( 0(3)                                                                                                                                | D 444 o(3)                            |                   | DAVA              | DAA/ 0                            | DANO              |                |  |  |  |

| R/W-0(-)             | R/W-0 <sup>(3)</sup>                                                                                                                        | R/W-0 <sup>(3)</sup>                  | R-0               | R/W-0             | R/W-0                             | R/W-0             | R/W-0          |  |  |  |

|                      | IPL<2:0> <sup>(2)</sup>                                                                                                                     |                                       | RA                | N                 | OV                                | Z                 | C              |  |  |  |

| bit 7                |                                                                                                                                             |                                       |                   |                   |                                   |                   | bit (          |  |  |  |

| Legend:              |                                                                                                                                             |                                       |                   |                   |                                   |                   |                |  |  |  |

| C = Clear only       | bit                                                                                                                                         | R = Readable                          | e bit             | U = Unimple       | mented bit, read                  | l as '0'          |                |  |  |  |

| S = Set only b       | it                                                                                                                                          | W = Writable                          | bit               | -n = Value at     | POR                               |                   |                |  |  |  |

| '1' = Bit is set     |                                                                                                                                             | '0' = Bit is clea                     | ared              | x = Bit is unk    | nown                              |                   |                |  |  |  |

|                      |                                                                                                                                             |                                       |                   |                   |                                   |                   |                |  |  |  |

| bit 15               |                                                                                                                                             | ator A Overflov                       |                   |                   |                                   |                   |                |  |  |  |

|                      |                                                                                                                                             | tor A overflowe                       |                   |                   |                                   |                   |                |  |  |  |

| bit 14               |                                                                                                                                             | ator B Overflov                       |                   |                   |                                   |                   |                |  |  |  |

|                      | 1 = Accumulator B overflowed                                                                                                                |                                       |                   |                   |                                   |                   |                |  |  |  |

|                      |                                                                                                                                             | tor B has not c                       |                   |                   |                                   |                   |                |  |  |  |

| bit 13               | <b>SA:</b> Accumulator A Saturation 'Sticky' Status bit <sup>(1)</sup><br>1 = Accumulator A is saturated or has been saturated at some time |                                       |                   |                   |                                   |                   |                |  |  |  |

|                      |                                                                                                                                             |                                       |                   | en saturated at   | some time                         |                   |                |  |  |  |

| bit 12               |                                                                                                                                             | itor A is not sat<br>ator B Saturatio |                   | tue hit(1)        |                                   |                   |                |  |  |  |

| DIL 12               |                                                                                                                                             | ator B is saturat                     | -                 |                   | some time                         |                   |                |  |  |  |

|                      |                                                                                                                                             | itor B is not sat                     |                   |                   |                                   |                   |                |  |  |  |

| bit 11               | <b>0AB:</b> OA    C                                                                                                                         | B Combined A                          | ccumulator O      | verflow Status    | bit                               |                   |                |  |  |  |

|                      |                                                                                                                                             | tors A or B hav                       |                   | erflowed          |                                   |                   |                |  |  |  |

| bit 10               | SAB: SA    SB Combined Accumulator 'Sticky' Status bit                                                                                      |                                       |                   |                   |                                   |                   |                |  |  |  |

|                      |                                                                                                                                             | itors A or B are<br>ccumulator A c    |                   |                   | urated at some                    | time in the pas   | t              |  |  |  |

|                      | Note: T                                                                                                                                     | his bit may be r                      | ead or cleare     | d (not set). Cle  | aring this bit wil                | ll clear SA and   | SB.            |  |  |  |

| bit 9                | DA: DO Loop Active bit                                                                                                                      |                                       |                   |                   |                                   |                   |                |  |  |  |

|                      |                                                                                                                                             |                                       |                   |                   |                                   |                   |                |  |  |  |

| bit 8                | -                                                                                                                                           | ot in progress<br>U Half Carry/Bo     | orrow bit         |                   |                                   |                   |                |  |  |  |

| bit b                | 1 = A carry-o                                                                                                                               |                                       |                   | for byte sized o  | data) or 8th low-                 | order bit (for wo | ord sized data |  |  |  |

|                      | 0 = No carry-                                                                                                                               |                                       |                   | oit (for byte siz | ed data) or 8th                   | low-order bit (   | for word sized |  |  |  |

| Note 1: Th           | is bit may be re                                                                                                                            | ad or cleared (                       | (not set).        |                   |                                   |                   |                |  |  |  |

| Le                   |                                                                                                                                             |                                       |                   |                   | RCON<3>) to fo<br>3> = 1. User ii |                   |                |  |  |  |

**3:** The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

| R/W-0         | R/W-0                                                     | U-0                            | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |

|---------------|-----------------------------------------------------------|--------------------------------|----------------|------------------|------------------|-----------------|---------|--|--|--|--|

| T6IF          | DMA4IF                                                    | _                              | OC8IF          | OC7IF            | OC6IF            | OC5IF           | IC6IF   |  |  |  |  |

| bit 15        |                                                           |                                |                |                  | •                |                 | bit 8   |  |  |  |  |

| R/W-0         | R/W-0                                                     | R/W-0                          | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |

| IC5IF         | IC4IF                                                     | IC3IF                          | DMA3IF         | C1IF             | C1RXIF           | SPI2IF          | SPI2EIF |  |  |  |  |

| bit 7         | 10411                                                     | 10011                          | Division       | 0111             | Unival           | 01 1211         | bit (   |  |  |  |  |

| Legend:       |                                                           |                                |                |                  |                  |                 |         |  |  |  |  |

| R = Readable  | e bit                                                     | W = Writable                   | bit            | U = Unimple      | mented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value at | POR                                                       | '1' = Bit is set               |                | '0' = Bit is cle | eared            | x = Bit is unki | nown    |  |  |  |  |

| bit 15        | T6IF: Timer6                                              | Interrupt Flag                 | Status bit     |                  |                  |                 |         |  |  |  |  |

|               |                                                           | equest has oc<br>equest has no |                |                  |                  |                 |         |  |  |  |  |

| bit 14        |                                                           | •                              |                | Complete Inter   | rupt Flag Status | bit             |         |  |  |  |  |

|               | 1 = Interrupt r                                           | equest has oc<br>equest has no | curred         | ·                |                  |                 |         |  |  |  |  |

| bit 13        | -                                                         | ted: Read as '                 |                |                  |                  |                 |         |  |  |  |  |

| bit 12        | OC8IF: Output Compare Channel 8 Interrupt Flag Status bit |                                |                |                  |                  |                 |         |  |  |  |  |

|               |                                                           | equest has oc<br>equest has no |                |                  |                  |                 |         |  |  |  |  |

| bit 11        | OC7IF: Output Compare Channel 7 Interrupt Flag Status bit |                                |                |                  |                  |                 |         |  |  |  |  |

|               | •                                                         | equest has oc<br>equest has no |                |                  |                  |                 |         |  |  |  |  |

| bit 10        | OC6IF: Output Compare Channel 6 Interrupt Flag Status bit |                                |                |                  |                  |                 |         |  |  |  |  |

|               |                                                           | equest has oc<br>equest has no |                |                  |                  |                 |         |  |  |  |  |

| bit 9         | OC5IF: Output Compare Channel 5 Interrupt Flag Status bit |                                |                |                  |                  |                 |         |  |  |  |  |

|               |                                                           | equest has oc<br>equest has no |                |                  |                  |                 |         |  |  |  |  |

| bit 8         | IC6IF: Input Capture Channel 6 Interrupt Flag Status bit  |                                |                |                  |                  |                 |         |  |  |  |  |

|               |                                                           | equest has oc<br>equest has no |                |                  |                  |                 |         |  |  |  |  |

| bit 7         | IC5IF: Input Capture Channel 5 Interrupt Flag Status bit  |                                |                |                  |                  |                 |         |  |  |  |  |

|               |                                                           | equest has oc<br>equest has no |                |                  |                  |                 |         |  |  |  |  |

| bit 6         | IC4IF: Input Capture Channel 4 Interrupt Flag Status bit  |                                |                |                  |                  |                 |         |  |  |  |  |

|               |                                                           | equest has oc<br>equest has no |                |                  |                  |                 |         |  |  |  |  |

| bit 5         | IC3IF: Input Capture Channel 3 Interrupt Flag Status bit  |                                |                |                  |                  |                 |         |  |  |  |  |

|               |                                                           | equest has oc<br>equest has no |                |                  |                  |                 |         |  |  |  |  |

| bit 4         | DMA3IF: DM                                                | A Channel 3 D                  | ata Transfer C | Complete Inter   | rupt Flag Status | bit             |         |  |  |  |  |

|               |                                                           | equest has oc<br>equest has no |                |                  |                  |                 |         |  |  |  |  |

| bit 3         | C1IF: ECAN1                                               | Event Interrup                 | ot Flag Status | bit              |                  |                 |         |  |  |  |  |

|               |                                                           | equest has oc<br>equest has no |                |                  |                  |                 |         |  |  |  |  |

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

#### **REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2 (CONTINUED)**

| bit 2 | C1RXIF: ECAN1 Receive Data Ready Interrupt Flag Status bit |

|-------|------------------------------------------------------------|

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| bit 1 | SPI2IF: SPI2 Event Interrupt Flag Status bit               |

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| bit 0 | SPI2EIF: SPI2 Error Interrupt Flag Status bit              |

- SPI2EIF: SPI2 Error Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| R/W-0           | R/W-0                                                                                                     | R/W-0                             | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|------------------|------------------|-----------------|---------|--|--|--|--|--|

| U2TXIE          | U2RXIE                                                                                                    | INT2IE                            | T5IE            | T4IE             | OC4IE            | OC3IE           | DMA2IE  |  |  |  |  |  |

| bit 15          |                                                                                                           |                                   |                 |                  |                  |                 | bit 8   |  |  |  |  |  |

| R/W-0           | R/W-0                                                                                                     | R/W-0                             | R/W-0           | R/W-0            | U-0              | R/W-0           | R/W-0   |  |  |  |  |  |

| IC8IE           | IC7IE                                                                                                     | AD2IE                             | INT1IE          | CNIE             | _                | MI2C1IE         | SI2C1IE |  |  |  |  |  |

| bit 7           |                                                                                                           |                                   |                 |                  |                  | _               | bit 0   |  |  |  |  |  |

| Legend:         |                                                                                                           |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

| R = Readable    | bit                                                                                                       | W = Writable                      | bit             | U = Unimplei     | mented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value at F | POR                                                                                                       | '1' = Bit is set                  |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |  |

|                 |                                                                                                           |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

| bit 15          | U2TXIE: UAF                                                                                               | RT2 Transmitte                    | r Interrupt Ena | able bit         |                  |                 |         |  |  |  |  |  |

|                 |                                                                                                           | request enable                    |                 |                  |                  |                 |         |  |  |  |  |  |

| bit 14          | -                                                                                                         | request not ena<br>RT2 Receiver I |                 | la hit           |                  |                 |         |  |  |  |  |  |

| DIL 14          |                                                                                                           | request enable                    |                 |                  |                  |                 |         |  |  |  |  |  |

|                 |                                                                                                           | request not ena                   |                 |                  |                  |                 |         |  |  |  |  |  |

| bit 13          | INT2IE: External Interrupt 2 Enable bit                                                                   |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

|                 | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>              |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

| bit 12          | <b>T5IE:</b> Timer5 Interrupt Enable bit                                                                  |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

|                 | 1 = Interrupt request enabled                                                                             |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

|                 | -                                                                                                         | request not ena                   |                 |                  |                  |                 |         |  |  |  |  |  |

| bit 11          | T4IE: Timer4 Interrupt Enable bit                                                                         |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

|                 | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul>                 |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

| bit 10          | OC4IE: Output Compare Channel 4 Interrupt Enable bit                                                      |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

|                 | <ol> <li>I = Interrupt request enabled</li> <li>Interrupt request not enabled</li> </ol>                  |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

| bit 9           | OC3IE: Output Compare Channel 3 Interrupt Enable bit                                                      |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

|                 | 1 = Interrupt                                                                                             | request enable                    | d               |                  |                  |                 |         |  |  |  |  |  |

| bit 8           | -                                                                                                         | request not ena                   |                 | Complete Inter   | runt Enable bit  |                 |         |  |  |  |  |  |

|                 | <b>DMA2IE:</b> DMA Channel 2 Data Transfer Complete Interrupt Enable bit<br>1 = Interrupt request enabled |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

|                 | 0 = Interrupt request not enabled                                                                         |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

| bit 7           | IC8IE: Input Capture Channel 8 Interrupt Enable bit                                                       |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

|                 | 1 = Interrupt request enabled                                                                             |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

| bit 6           | 0 = Interrupt request not enabled                                                                         |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

|                 | IC7IE: Input Capture Channel 7 Interrupt Enable bit<br>1 = Interrupt request enabled                      |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

|                 | 0 = Interrupt i                                                                                           | request not ena                   | abled           |                  |                  |                 |         |  |  |  |  |  |

| bit 5           |                                                                                                           | 2 Conversion C                    | -               | rupt Enable bit  | t                |                 |         |  |  |  |  |  |

|                 |                                                                                                           | request enable                    |                 |                  |                  |                 |         |  |  |  |  |  |

| bit 4           | •                                                                                                         | request not ena                   |                 |                  |                  |                 |         |  |  |  |  |  |

|                 |                                                                                                           | mai interiupt T                   |                 |                  |                  |                 |         |  |  |  |  |  |

|                 | INT1IE: External Interrupt 1 Enable bit<br>1 = Interrupt request enabled                                  |                                   |                 |                  |                  |                 |         |  |  |  |  |  |

|  | REGISTER 7-13: | IEC3: INTERRUPT ENABLE CONTROL REGISTER 3 |

|--|----------------|-------------------------------------------|

|--|----------------|-------------------------------------------|

| R/W-0         | U-0                                                   | R/W-0                                                  | U-0   | U-0              | R/W-0            | R/W-0           | R/W-0 |  |  |  |

|---------------|-------------------------------------------------------|--------------------------------------------------------|-------|------------------|------------------|-----------------|-------|--|--|--|

| FLTAIE        |                                                       | DMA5IE                                                 | —     | —                | QEIIE            | PWMIE           | C2IE  |  |  |  |

| bit 15        |                                                       |                                                        |       | ·                |                  |                 | bit 8 |  |  |  |

| R/W-0         | R/W-0                                                 | R/W-0                                                  | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |

| C2RXIE        | INT4IE                                                | INT3IE                                                 | T9IE  | T8IE             | MI2C2IE          | SI2C2IE         | T7IE  |  |  |  |

| bit 7         |                                                       | 1                                                      |       | 1                | 1                | 1               | bit ( |  |  |  |

| Legend:       |                                                       |                                                        |       |                  |                  |                 |       |  |  |  |

| R = Readable  | e bit                                                 | W = Writable                                           | bit   | U = Unimple      | mented bit, read | l as '0'        |       |  |  |  |

| -n = Value at | POR                                                   | '1' = Bit is set                                       |       | '0' = Bit is cle | eared            | x = Bit is unkn | own   |  |  |  |

| bit 15        | 1 = Interrupt r                                       | // Fault A Interr<br>request enable<br>request not ena | d     | t                |                  |                 |       |  |  |  |

| bit 14        | Unimplemen                                            | ted: Read as '                                         | 0'    |                  |                  |                 |       |  |  |  |

| bit 13        | -                                                     |                                                        |       | Complete Inter   | rupt Enable bit  |                 |       |  |  |  |

|               |                                                       | request enable<br>request not ena                      |       |                  |                  |                 |       |  |  |  |

| bit 12-11     | Unimplemen                                            | ted: Read as '                                         | 0'    |                  |                  |                 |       |  |  |  |

| bit 10        | QEIIE: QEI Event Interrupt Enable bit                 |                                                        |       |                  |                  |                 |       |  |  |  |

|               |                                                       | request enable<br>request not ena                      |       |                  |                  |                 |       |  |  |  |

| bit 9         | PWMIE: PWM Error Interrupt Enable bit                 |                                                        |       |                  |                  |                 |       |  |  |  |

|               |                                                       | request enable<br>request not ena                      |       |                  |                  |                 |       |  |  |  |

| bit 8         | C2IE: ECAN2 Event Interrupt Enable bit                |                                                        |       |                  |                  |                 |       |  |  |  |

|               |                                                       | request enable<br>request not ena                      |       |                  |                  |                 |       |  |  |  |

| bit 7         | C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit |                                                        |       |                  |                  |                 |       |  |  |  |

|               | 1 = Interrupt request enabled                         |                                                        |       |                  |                  |                 |       |  |  |  |

| L:1 0         |                                                       | request not ena                                        |       |                  |                  |                 |       |  |  |  |

| bit 6         |                                                       | mal Interrupt 4                                        |       |                  |                  |                 |       |  |  |  |

|               |                                                       | request enable<br>request not ena                      |       |                  |                  |                 |       |  |  |  |

| bit 5         | INT3IE: External Interrupt 3 Enable bit               |                                                        |       |                  |                  |                 |       |  |  |  |

|               |                                                       | request enable<br>request not ena                      |       |                  |                  |                 |       |  |  |  |

| bit 4         | <b>T9IE:</b> Timer9 Interrupt Enable bit              |                                                        |       |                  |                  |                 |       |  |  |  |

|               | 1 = Interrupt r                                       | request enable<br>request not ena                      | d     |                  |                  |                 |       |  |  |  |

| bit 3         | •                                                     | Interrupt Enab                                         |       |                  |                  |                 |       |  |  |  |

|               |                                                       | request enable                                         |       |                  |                  |                 |       |  |  |  |

|               | 0 = Interrupt r                                       | request not ena                                        | abled |                  |                  |                 |       |  |  |  |

| bit 2         |                                                       | 2 Master Ever                                          | -     | nable bit        |                  |                 |       |  |  |  |

|               |                                                       | request enable<br>request not ena                      |       |                  |                  |                 |       |  |  |  |

|               |                                                       |                                                        |       |                  |                  |                 |       |  |  |  |

### REGISTER 7-16: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| U-0           | R/W-1                                                                                                                     | R/W-0                                                                                                                                                | R/W-0 | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| _             |                                                                                                                           | T2IP<2:0>                                                                                                                                            |       | _                |                 | OC2IP<2:0>      |       |  |  |  |  |  |

| bit 15        |                                                                                                                           |                                                                                                                                                      |       |                  |                 |                 | bit   |  |  |  |  |  |

|               |                                                                                                                           |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

| U-0           | R/W-1                                                                                                                     | R/W-0                                                                                                                                                | R/W-0 | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

| —             |                                                                                                                           | IC2IP<2:0>                                                                                                                                           |       | —                |                 | DMA0IP<2:0>     |       |  |  |  |  |  |

| bit 7         |                                                                                                                           |                                                                                                                                                      |       |                  |                 |                 | bit   |  |  |  |  |  |

| Legend:       |                                                                                                                           |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

| R = Readable  | e bit                                                                                                                     | W = Writable I                                                                                                                                       | oit   | U = Unimple      | mented bit, rea | ad as '0'       |       |  |  |  |  |  |

| -n = Value at | POR                                                                                                                       | '1' = Bit is set                                                                                                                                     |       | '0' = Bit is cle | ared            | x = Bit is unkn | own   |  |  |  |  |  |

| bit 15        | Unimpleme                                                                                                                 | nted: Read as 'o                                                                                                                                     | )'    |                  |                 |                 |       |  |  |  |  |  |

| bit 14-12     | T2IP<2:0>: Timer2 Interrupt Priority bits                                                                                 |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

|               | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

|               |                                                                                                                           | upt is priority 1                                                                                                                                    |       |                  |                 |                 |       |  |  |  |  |  |

|               |                                                                                                                           | upt source is disa                                                                                                                                   |       |                  |                 |                 |       |  |  |  |  |  |

| bit 11        | -                                                                                                                         | nted: Read as 'o                                                                                                                                     |       |                  |                 |                 |       |  |  |  |  |  |

| bit 10-8      | <b>OC2IP&lt;2:0&gt;:</b> Output Compare Channel 2 Interrupt Priority bits                                                 |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

|               | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>•</li> </ul>                                 |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

|               | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                       |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

| bit 7         |                                                                                                                           | nted: Read as 'o                                                                                                                                     |       |                  |                 |                 |       |  |  |  |  |  |

| bit 6-4       | -                                                                                                                         |                                                                                                                                                      |       | rrupt Priority b | its             |                 |       |  |  |  |  |  |

|               | IC2IP<2:0>: Input Capture Channel 2 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

|               | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                       |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

| bit 3         |                                                                                                                           | nted: Read as 'o                                                                                                                                     |       |                  |                 |                 |       |  |  |  |  |  |

| bit 2-0       | -                                                                                                                         |                                                                                                                                                      |       | nsfer Complete   | Interrupt Pric  | ority bits      |       |  |  |  |  |  |

|               |                                                                                                                           | <b>DMA0IP&lt;2:0&gt;:</b> DMA Channel 0 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |       |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                         |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

|               | 001 = Interru                                                                                                             | upt is priority 1                                                                                                                                    |       |                  |                 |                 |       |  |  |  |  |  |

|               | 000 = Interri                                                                                                             |                                                                                                                                                      |       |                  |                 |                 |       |  |  |  |  |  |

| U-0           | R/W-1                         | R/W-0                                            | R/W-0           | U-0              | U-0               | U-0             | U-0   |  |  |  |  |

|---------------|-------------------------------|--------------------------------------------------|-----------------|------------------|-------------------|-----------------|-------|--|--|--|--|

| _             |                               | FLTAIP<2:0>                                      |                 |                  | —                 | —               | _     |  |  |  |  |

| bit 15        |                               |                                                  |                 | ·                | •                 | -               | bit 8 |  |  |  |  |

|               |                               |                                                  |                 |                  |                   |                 |       |  |  |  |  |

| U-0           | R/W-1                         | R/W-0                                            | R/W-0           | U-0              | U-0               | U-0             | U-0   |  |  |  |  |

| —             |                               | DMA5IP<2:0>                                      |                 |                  | —                 | —               |       |  |  |  |  |

| bit 7         |                               |                                                  |                 |                  |                   |                 | bit 0 |  |  |  |  |

|               |                               |                                                  |                 |                  |                   |                 |       |  |  |  |  |

| Legend:       |                               |                                                  |                 |                  |                   |                 |       |  |  |  |  |

| R = Readabl   | e bit                         | W = Writable                                     | bit             | U = Unimpler     | mented bit, rea   | d as '0'        |       |  |  |  |  |

| -n = Value at | POR                           | '1' = Bit is set                                 |                 | '0' = Bit is cle | eared             | x = Bit is unkr | nown  |  |  |  |  |

|               |                               |                                                  |                 |                  |                   |                 |       |  |  |  |  |

| bit 15        | Unimpleme                     | nted: Read as '                                  | 0'              |                  |                   |                 |       |  |  |  |  |

| bit 14-12     | FLTAIP<2:0                    | FLTAIP<2:0>: PWM Fault A Interrupt Priority bits |                 |                  |                   |                 |       |  |  |  |  |

|               | 111 = Interr                  | upt is priority 7 (                              | highest priorit | y interrupt)     |                   |                 |       |  |  |  |  |

|               | •                             |                                                  |                 |                  |                   |                 |       |  |  |  |  |

|               | •                             |                                                  |                 |                  |                   |                 |       |  |  |  |  |

|               | 001 = Interrupt is priority 1 |                                                  |                 |                  |                   |                 |       |  |  |  |  |

|               | 000 = Interr                  | upt source is dis                                | abled           |                  |                   |                 |       |  |  |  |  |

| bit 11-7      | Unimpleme                     | nted: Read as '                                  | 0'              |                  |                   |                 |       |  |  |  |  |

| bit 6-4       | DMA5IP<2:                     | 0>: DMA Chann                                    | el 5 Data Tra   | nsfer Complete   | e Interrupt Prior | ity bits        |       |  |  |  |  |

|               | 111 = Interr                  | upt is priority 7 (                              | highest priorit | y interrupt)     |                   |                 |       |  |  |  |  |

|               | •                             |                                                  |                 |                  |                   |                 |       |  |  |  |  |

|               | •                             |                                                  |                 |                  |                   |                 |       |  |  |  |  |

|               | 001 = Interr                  | upt is priority 1                                |                 |                  |                   |                 |       |  |  |  |  |

|               |                               | upt source is dis                                | abled           |                  |                   |                 |       |  |  |  |  |

| bit 3-0       | Unimpleme                     | nted: Read as '                                  | 0'              |                  |                   |                 |       |  |  |  |  |

#### REGISTER 7-30: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0          | U-0                                                                            | U-0               | U-0   | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|--------------|--------------------------------------------------------------------------------|-------------------|-------|------------------|-----------------|-----------------|-------|--|--|--|--|

|              | _                                                                              | _                 | _     | _                |                 | U2EIP<2:0>      |       |  |  |  |  |

| bit 15       |                                                                                |                   |       |                  | •               |                 | bit   |  |  |  |  |

|              |                                                                                |                   |       |                  |                 |                 |       |  |  |  |  |

| U-0          | R/W-1                                                                          | R/W-0             | R/W-0 | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|              |                                                                                | U1EIP<2:0>        |       | —                |                 | FLTBIP<2:0>     |       |  |  |  |  |

| bit 7        |                                                                                |                   |       |                  |                 |                 | bit   |  |  |  |  |

| Legend:      |                                                                                |                   |       |                  |                 |                 |       |  |  |  |  |

| R = Readab   | le bit                                                                         | W = Writable      | bit   | U = Unimpler     | mented bit, rea | ad as '0'       |       |  |  |  |  |

| -n = Value a | t POR                                                                          | '1' = Bit is set  |       | '0' = Bit is cle | eared           | x = Bit is unkn | iown  |  |  |  |  |

|              |                                                                                |                   | .,    |                  |                 |                 |       |  |  |  |  |

| bit 15-11    | -                                                                              | nted: Read as '   |       |                  |                 |                 |       |  |  |  |  |

| bit 10-8     | <b>U2EIP&lt;2:0&gt;:</b> UART2 Error Interrupt Priority bits                   |                   |       |                  |                 |                 |       |  |  |  |  |

|              | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> </ul> |                   |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                                              |                   |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                                              |                   |       |                  |                 |                 |       |  |  |  |  |

|              | 001 = Interrupt is priority 1                                                  |                   |       |                  |                 |                 |       |  |  |  |  |

|              |                                                                                | upt source is dis |       |                  |                 |                 |       |  |  |  |  |

| bit 7        | Unimpleme                                                                      | nted: Read as 'o  | )'    |                  |                 |                 |       |  |  |  |  |

| bit 6-4      | U1EIP<2:0>: UART1 Error Interrupt Priority bits                                |                   |       |                  |                 |                 |       |  |  |  |  |

|              | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>          |                   |       |                  |                 |                 |       |  |  |  |  |

|              |                                                                                |                   |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                                              |                   |       |                  |                 |                 |       |  |  |  |  |

|              | 001 = Interrupt is priority 1                                                  |                   |       |                  |                 |                 |       |  |  |  |  |

|              | 000 = Interrupt source is disabled                                             |                   |       |                  |                 |                 |       |  |  |  |  |

| bit 3        | Unimplemented: Read as '0'                                                     |                   |       |                  |                 |                 |       |  |  |  |  |

| bit 2-0      | FLTBIP<2:0>: PWM Fault B Interrupt Priority bits                               |                   |       |                  |                 |                 |       |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)                     |                   |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                                              |                   |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                                              |                   |       |                  |                 |                 |       |  |  |  |  |

|              |                                                                                |                   |       |                  |                 |                 |       |  |  |  |  |

|              | 001 = Interr                                                                   | upt is priority 1 |       |                  |                 |                 |       |  |  |  |  |

# REGISTER 7-31: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

#### REGISTER 8-8: DMACS1: DMA CONTROLLER STATUS REGISTER 1

| U-0           | U-0                                                                                                    | U-0                             | U-0             | R-1              | R-1              | R-1             | R-1   |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------|---------------------------------|-----------------|------------------|------------------|-----------------|-------|--|--|--|--|--|

| _             | —                                                                                                      | —                               | _               |                  | LSTC             | H<3:0>          |       |  |  |  |  |  |

| bit 15        |                                                                                                        |                                 |                 | ·                |                  |                 | bit 8 |  |  |  |  |  |

|               |                                                                                                        |                                 |                 |                  |                  |                 |       |  |  |  |  |  |

| R-0           | R-0                                                                                                    | R-0                             | R-0             | R-0              | R-0              | R-0             | R-0   |  |  |  |  |  |

| PPST7         | PPST6                                                                                                  | PPST5                           | PPST4           | PPST3            | PPST2            | PPST1           | PPST0 |  |  |  |  |  |

| bit 7         |                                                                                                        |                                 |                 |                  |                  |                 | bit 0 |  |  |  |  |  |

| <u> </u>      |                                                                                                        |                                 |                 |                  |                  |                 |       |  |  |  |  |  |

| Legend:       |                                                                                                        |                                 |                 |                  |                  |                 |       |  |  |  |  |  |

| R = Readable  |                                                                                                        | W = Writable                    |                 | -                | nented bit, read |                 |       |  |  |  |  |  |

| -n = Value at | POR                                                                                                    | '1' = Bit is set                |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 15 10     | Unimplomon                                                                                             | tadi Dood oo '                  | o'              |                  |                  |                 |       |  |  |  |  |  |

| bit 15-12     | -                                                                                                      | ted: Read as '<br>: Last DMA Ch |                 |                  |                  |                 |       |  |  |  |  |  |

| bit 11-8      |                                                                                                        | MA transfer ha                  |                 |                  | sot              |                 |       |  |  |  |  |  |

|               | 1110-1000 =                                                                                            |                                 | S OCCUITED SIII | ice system res   | Set              |                 |       |  |  |  |  |  |

|               |                                                                                                        | data transfer w                 |                 |                  |                  |                 |       |  |  |  |  |  |

|               |                                                                                                        | data transfer w                 | •               |                  |                  |                 |       |  |  |  |  |  |

|               | 0101 = Last data transfer was by DMA Channel 5                                                         |                                 |                 |                  |                  |                 |       |  |  |  |  |  |

|               | 0100 = Last data transfer was by DMA Channel 4<br>0011 = Last data transfer was by DMA Channel 3       |                                 |                 |                  |                  |                 |       |  |  |  |  |  |

|               | 0010 = Last data transfer was by DMA Channel 2                                                         |                                 |                 |                  |                  |                 |       |  |  |  |  |  |

|               | 0001 = Last data transfer was by DMA Channel 1<br>0000 = Last data transfer was by DMA Channel 0       |                                 |                 |                  |                  |                 |       |  |  |  |  |  |

|               |                                                                                                        |                                 | -               |                  |                  |                 |       |  |  |  |  |  |

| bit 7         | <b>PPST7:</b> Channel 7 Ping-Pong Mode Status Flag bit<br>1 = DMA7STB register selected                |                                 |                 |                  |                  |                 |       |  |  |  |  |  |

|               |                                                                                                        |                                 |                 |                  |                  |                 |       |  |  |  |  |  |

| bit 6         | <ul> <li>DMA7STA register selected</li> <li>PPST6: Channel 6 Ping-Pong Mode Status Flag bit</li> </ul> |                                 |                 |                  |                  |                 |       |  |  |  |  |  |

|               | 1 = DMA6STB register selected                                                                          |                                 |                 |                  |                  |                 |       |  |  |  |  |  |

|               |                                                                                                        | A register seled                |                 |                  |                  |                 |       |  |  |  |  |  |

| bit 5         | PPST5: Channel 5 Ping-Pong Mode Status Flag bit                                                        |                                 |                 |                  |                  |                 |       |  |  |  |  |  |