Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                               |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 100MHz                                                                               |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, SD, SPI, UART/USART, USB, USB OTG |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                            |

| Number of I/O              | 100                                                                                  |

| Program Memory Size        | 256КВ (256К × 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 64K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                         |

| Data Converters            | A/D 42x16b; D/A 2x12b                                                                |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 144-LQFP                                                                             |

| Supplier Device Package    | 144-LQFP (20x20)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mk60dn256vlq10               |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Communication interfaces

- Ethernet controller with MII and RMII interface to external PHY and hardware IEEE 1588 capability

- USB full-/low-speed On-the-Go controller with on-chip transceiver

- Two Controller Area Network (CAN) modules

- Three SPI modules

- Two I2C modules

- Five UART modules

- Secure Digital host controller (SDHC)

- I2S module

| 8 | Pine |                                             |

|---|------|---------------------------------------------|

|   | 8.1  | K60 signal multiplexing and pin assignments |

|   | 8.2 K60 pinouts  | 77 |

|---|------------------|----|

| 9 | Revision history | 78 |

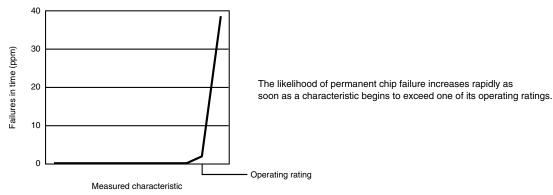

# 3.4 Definition: Rating

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- *Handling ratings* apply when the chip is not powered.

## 3.4.1 Example

This is an example of an operating rating:

| Symbol          | Description                  | Min. | Max. | Unit |

|-----------------|------------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | -0.3 | 1.2  | V    |

# 3.5 Result of exceeding a rating

# 5.2 Nonswitching electrical specifications

### 5.2.1 Voltage and current operating requirements Table 1. Voltage and current operating requirements

|                            |                                                                                                                                                                                                    |                       | •                    |      |       |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|------|-------|

| Symbol                     | Description                                                                                                                                                                                        | Min.                  | Max.                 | Unit | Notes |

| V <sub>DD</sub>            | Supply voltage                                                                                                                                                                                     | 1.71                  | 3.6                  | V    |       |

| V <sub>DDA</sub>           | Analog supply voltage                                                                                                                                                                              | 1.71                  | 3.6                  | V    |       |

| $V_{DD} - V_{DDA}$         | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                                                                                                                          | -0.1                  | 0.1                  | V    |       |

| $V_{\rm SS} - V_{\rm SSA}$ | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage                                                                                                                                          | -0.1                  | 0.1                  | V    |       |

| V <sub>BAT</sub>           | RTC battery supply voltage                                                                                                                                                                         | 1.71                  | 3.6                  | V    |       |

| V <sub>IH</sub>            | Input high voltage                                                                                                                                                                                 |                       |                      |      |       |

|                            | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                                                                                                                        | $0.7 \times V_{DD}$   | _                    | V    |       |

|                            | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                                                                                       | $0.75 \times V_{DD}$  | _                    | V    |       |

| V <sub>IL</sub>            | Input low voltage                                                                                                                                                                                  |                       |                      |      |       |

|                            | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$                                                                                                                                       | _                     | $0.35 \times V_{DD}$ | V    |       |

|                            | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                                                                                       | _                     | $0.3 \times V_{DD}$  | V    |       |

| V <sub>HYS</sub>           | Input hysteresis                                                                                                                                                                                   | $0.06 \times V_{DD}$  | _                    | V    |       |

| I <sub>ICDIO</sub>         | Digital pin negative DC injection current — single pin<br>• V <sub>IN</sub> < V <sub>SS</sub> -0.3V                                                                                                | -5                    | _                    | mA   | 1     |

| I <sub>ICAIO</sub>         | Analog <sup>2</sup> , EXTAL, and XTAL pin DC injection current —<br>single pin<br>• V <sub>IN</sub> < V <sub>SS</sub> -0.3V (Negative current injection)                                           | -5                    |                      | mA   | 3     |

|                            | <ul> <li>V<sub>IN</sub> &gt; V<sub>DD</sub>+0.3V (Positive current injection)</li> </ul>                                                                                                           | —                     | +5                   |      |       |

| I <sub>ICcont</sub>        | Contiguous pin DC injection current —regional limit,<br>includes sum of negative injection currents or sum of<br>positive injection currents of 16 contiguous pins<br>• Negative current injection | -25                   | _                    | mA   |       |

|                            | Positive current injection                                                                                                                                                                         | _                     | +25                  |      |       |

| V <sub>ODPU</sub>          | Open drain pullup voltage level                                                                                                                                                                    | V <sub>DD</sub>       | V <sub>DD</sub>      | V    | 4     |

| V <sub>RAM</sub>           | V <sub>DD</sub> voltage required to retain RAM                                                                                                                                                     | 1.2                   | —                    | V    |       |

| V <sub>RFVBAT</sub>        | $V_{\text{BAT}}$ voltage required to retain the VBAT register file                                                                                                                                 | V <sub>POR_VBAT</sub> | —                    | V    |       |

|                            |                                                                                                                                                                                                    |                       |                      |      |       |

- All 5 V tolerant digital I/O pins are internally clamped to V<sub>SS</sub> through an ESD protection diode. There is no diode connection to V<sub>DD</sub>. If V<sub>IN</sub> is less than V<sub>DIO\_MIN</sub>, a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>DIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICDIO</sub>I.

- 2. Analog pins are defined as pins that do not have an associated general purpose I/O port function. Additionally, EXTAL and XTAL are analog pins.

- 3. All analog pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub> through ESD protection diodes. If V<sub>IN</sub> is less than V<sub>AIO\_MIN</sub> or greater than V<sub>AIO\_MAX</sub>, a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>AIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICAIO</sub>I. The positive injection current limiting resistor is calculated as R=(V<sub>AIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICAIO</sub>I. The positive injection current limiting resistor is calculated to positive and negative injection currents.

- 4. Open drain outputs must be pulled to VDD.

### 5.2.3 Voltage and current operating behaviors Table 4. Voltage and current operating behaviors

| Symbol           | Description                                                                                           | Min.                  | Typ. <sup>1</sup> | Max. | Unit | Notes   |

|------------------|-------------------------------------------------------------------------------------------------------|-----------------------|-------------------|------|------|---------|

| V <sub>OH</sub>  | Output high voltage — high drive strength                                                             |                       |                   |      |      |         |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -9mA                                   | V <sub>DD</sub> – 0.5 | —                 | _    | V    |         |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OH}} = -3\text{mA}$    | V <sub>DD</sub> – 0.5 | —                 | —    | V    |         |

|                  | Output high voltage — low drive strength                                                              |                       |                   |      |      |         |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -2mA                                   | V <sub>DD</sub> – 0.5 | _                 | _    | V    |         |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OH}} = -0.6 \text{mA}$ | V <sub>DD</sub> – 0.5 | _                 | —    | V    |         |

| I <sub>OHT</sub> | Output high current total for all ports                                                               | —                     | _                 | 100  | mA   |         |

| V <sub>OL</sub>  | Output low voltage — high drive strength                                                              |                       |                   |      |      | 2       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 10mA                                   | _                     | _                 | 0.5  | V    |         |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OL}} = 5\text{mA}$     | —                     | _                 | 0.5  | V    |         |

|                  | Output low voltage — low drive strength                                                               |                       |                   |      |      | -       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 2mA                                    | _                     | _                 | 0.5  | V    |         |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OL}} = 1\text{mA}$     | —                     | _                 | 0.5  | V    |         |

| I <sub>OLT</sub> | Output low current total for all ports                                                                | _                     | _                 | 100  | mA   |         |

| I <sub>INA</sub> | Input leakage current, analog pins and digital pins configured as analog inputs                       |                       |                   |      |      | 3, 4    |

|                  | • $V_{SS} \le V_{IN} \le V_{DD}$                                                                      |                       |                   |      |      |         |

|                  | All pins except EXTAL32, XTAL32,     EXTAL XTAL                                                       | _                     | 0.002             | 0.5  | μA   |         |

|                  | • EXTAL, XTAL<br>• EXTAL (PTA18) and XTAL (PTA19)                                                     | _                     | 0.004             | 1.5  | μA   |         |

|                  | <ul> <li>EXTAL (FTAT6) and XTAL (FTAT6)</li> <li>EXTAL32, XTAL32</li> </ul>                           | _                     | 0.075             | 10   | μΑ   |         |

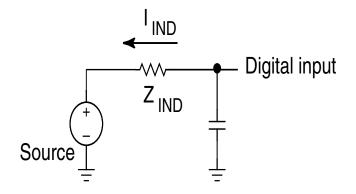

| I <sub>IND</sub> | Input leakage current, digital pins                                                                   |                       |                   |      |      | 4, 5    |

|                  | • $V_{SS} \le V_{IN} \le V_{IL}$                                                                      |                       |                   |      |      |         |

|                  | All digital pins                                                                                      | —                     | 0.002             | 0.5  | μA   |         |

|                  | • V <sub>IN</sub> = V <sub>DD</sub>                                                                   |                       |                   |      |      |         |

|                  | All digital pins except PTD7                                                                          | _                     | 0.002             | 0.5  | μA   |         |

|                  | PTD7                                                                                                  | —                     | 0.004             | 1    | μA   |         |

| I <sub>IND</sub> | Input leakage current, digital pins                                                                   |                       |                   |      |      | 4, 5, 6 |

|                  | • $V_{IL} < V_{IN} < V_{DD}$                                                                          |                       |                   |      |      | , _, _  |

|                  | • $V_{DD} = 3.6 V$                                                                                    | _                     | 18                | 26   | μA   |         |

|                  | • V <sub>DD</sub> = 3.0 V                                                                             | _                     | 12                | 49   | μA   |         |

|                  | • V <sub>DD</sub> = 2.5 V                                                                             | _                     | 8                 | 13   | μA   |         |

|                  | • V <sub>DD</sub> = 1.7 V                                                                             |                       | 3                 | 6    | μA   |         |

Table continues on the next page ...

Symbol Description Min. Typ.<sup>1</sup> Unit Max. Notes Input leakage current, digital pins 4, 5 IIND V<sub>DD</sub> < V<sub>IN</sub> < 5.5 V</li> 1 50 μΑ ZIND Input impedance examples, digital pins 4, 7 • V<sub>DD</sub> = 3.6 V kΩ 48 • V<sub>DD</sub> = 3.0 V kΩ 55 • V<sub>DD</sub> = 2.5 V 57 kΩ • V<sub>DD</sub> = 1.7 V 85 kΩ R<sub>PU</sub> Internal pullup resistors 20 35 50 kΩ 8 Internal pulldown resistors 20 35 50 kΩ 9 R<sub>PD</sub>

### Table 4. Voltage and current operating behaviors (continued)

- 1. Typical values characterized at  $25^{\circ}$ C and VDD = 3.6 V unless otherwise noted.

- 2. Open drain outputs must be pulled to  $V_{\text{DD}}.$

- 3. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

- 4. Digital pins have an associated GPIO port function and have 5V tolerant inputs, except EXTAL and XTAL.

- 5. Internal pull-up/pull-down resistors disabled.

- 6. Characterized, not tested in production.

- 7. Examples calculated using  $V_{IL}$  relation,  $V_{DD}$ , and max  $I_{IND}$ :  $Z_{IND}=V_{IL}/I_{IND}$ . This is the impedance needed to pull a high signal to a level below  $V_{IL}$  due to leakage when  $V_{IL} < V_{IN} < V_{DD}$ . These examples assume signal source low = 0 V.

- 8. Measured at V<sub>DD</sub> supply voltage = V<sub>DD</sub> min and Vinput = V<sub>SS</sub>

- 9. Measured at  $V_{DD}$  supply voltage =  $V_{DD}$  min and Vinput =  $V_{DD}$

### 5.2.4 Power mode transition operating behaviors

All specifications except  $t_{POR}$ , and VLLSx $\rightarrow$ RUN recovery times in the following table assume this clock configuration:

- CPU and system clocks = 100 MHz

- Bus clock = 50 MHz

- FlexBus clock = 50 MHz

- Flash clock = 25 MHz

- MCG mode: FEI

| Symbol               | Description                                             | Min. | Тур. | Max. | Unit | Notes |

|----------------------|---------------------------------------------------------|------|------|------|------|-------|

| I <sub>DD_VBAT</sub> | Average current when CPU is not accessing RTC registers |      |      |      |      | 10    |

|                      | • @ 1.8V                                                |      |      |      |      |       |

|                      | • @ -40 to 25°C                                         | _    | 0.57 | 0.67 | μA   |       |

|                      | • @ 70°C                                                | _    | 0.90 | 1.2  | μA   |       |

|                      | • @ 105°C<br>• @ 3.0V                                   | —    | 2.4  | 3.5  | μA   |       |

|                      | • @ -40 to 25°C                                         |      |      |      |      |       |

|                      |                                                         | —    | 0.67 | 0.94 | μA   |       |

|                      | • @ 70°C                                                | —    | 1.0  | 1.4  | μA   |       |

|                      | • @ 105°C                                               | _    | 2.7  | 3.9  | μA   |       |

#### Table 6. Power consumption operating behaviors (continued)

- 1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

- 2. 100MHz core and system clock, 50MHz bus and FlexBus clock, and 25MHz flash clock . MCG configured for FEI mode. All peripheral clocks disabled.

- 3. 100MHz core and system clock, 50MHz bus and FlexBus clock, and 25MHz flash clock. MCG configured for FEI mode. All peripheral clocks enabled.

- 4. Max values are measured with CPU executing DSP instructions.

- 5. 25MHz core and system clock, 25MHz bus clock, and 12.5MHz FlexBus and flash clock. MCG configured for FEI mode.

- 6. 4 MHz core, system, FlexBus, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled. Code executing from flash.

- 7. 4 MHz core, system, FlexBus, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks enabled but peripherals are not in active operation. Code executing from flash.

- 8. 4 MHz core, system, FlexBus, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled.

- 9. Data reflects devices with 128 KB of RAM. For devices with 64 KB of RAM, power consumption is reduced by 2 µA.

- 10. Includes 32kHz oscillator current and RTC operation.

### 5.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG in FBE mode for 50 MHz and lower frequencies. MCG in FEE mode at greater than 50 MHz frequencies.

- USB regulator disabled

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFL

| Symbol | Description                                  | Min. | Max. | Unit | Notes |

|--------|----------------------------------------------|------|------|------|-------|

|        | Port rise and fall time (low drive strength) |      |      |      | 5     |

|        | Slew disabled                                |      |      |      |       |

|        | • $1.71 \le V_{DD} \le 2.7V$                 | —    | 12   | ns   |       |

|        | • $2.7 \le V_{DD} \le 3.6V$                  | —    | 6    | ns   |       |

|        | Slew enabled                                 |      |      |      |       |

|        | • $1.71 \le V_{DD} \le 2.7V$                 | —    | 36   | ns   |       |

|        | • $2.7 \le V_{DD} \le 3.6V$                  |      | 24   | ns   |       |

### Table 10. General switching specifications (continued)

- 1. This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In Stop, VLPS, LLS, and VLLSx modes, the synchronizer is bypassed so shorter pulses can be recognized in that case.

- 2. The greater synchronous and asynchronous timing must be met.

- 3. This is the minimum pulse width that is guaranteed to be recognized as a pin interrupt request in Stop, VLPS, LLS, and VLLSx modes.

- 4. 75 pF load

- 5. 15 pF load

# 5.4 Thermal specifications

### 5.4.1 Thermal operating requirements

### Table 11. Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit |

|----------------|--------------------------|------|------|------|

| TJ             | Die junction temperature | -40  | 125  | °C   |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   |

### 5.4.2 Thermal attributes

| Board type        | Symbol           | Description                                                           | 100 LQFP | Unit | Notes |

|-------------------|------------------|-----------------------------------------------------------------------|----------|------|-------|

| Single-layer (1s) | R <sub>eJA</sub> | Thermal<br>resistance, junction<br>to ambient (natural<br>convection) | 47       | °C/W | 1     |

| Four-layer (2s2p) | R <sub>ejA</sub> | Thermal<br>resistance, junction<br>to ambient (natural<br>convection) | 35       | °C/W | 1     |

Table continues on the next page...

| Board type        | Symbol            | Description                                                                                                       | 100 LQFP | Unit | Notes |

|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------|----------|------|-------|

| Single-layer (1s) | R <sub>0JMA</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed)                                        | 37       | °C/W | 1     |

| Four-layer (2s2p) | R <sub>0JMA</sub> | Thermal<br>resistance, junction<br>to ambient (200 ft./<br>min. air speed)                                        | 29       | °C/W | 1     |

| —                 | R <sub>θJB</sub>  | Thermal<br>resistance, junction<br>to board                                                                       | 20       | °C/W | 2     |

| _                 | R <sub>θJC</sub>  | Thermal<br>resistance, junction<br>to case                                                                        | 9        | °C/W | 3     |

|                   | Ψ <sub>JT</sub>   | Thermal<br>characterization<br>parameter, junction<br>to package top<br>outside center<br>(natural<br>convection) | 2        | °C/W | 4     |

- 1. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air), or EIA/JEDEC Standard JESD51-6, Integrated Circuit Thermal Test Method Environmental Conditions—Forced Convection (Moving Air).

- 2. Determined according to JEDEC Standard JESD51-8, Integrated Circuit Thermal Test Method Environmental Conditions—Junction-to-Board.

- 3. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard, Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

- 4. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air).

# 6 Peripheral operating requirements and behaviors

## 6.1 Core modules

### 6.1.1 Debug trace timing specifications

Table 12.

Debug trace operating behaviors

| Symbol           | Description              | Min.                | Max. | Unit |

|------------------|--------------------------|---------------------|------|------|

| T <sub>cyc</sub> | Clock period             | Frequency dependent |      | MHz  |

| T <sub>wl</sub>  | Low pulse width          | 2                   |      | ns   |

| T <sub>wh</sub>  | High pulse width         | 2                   |      | ns   |

| T <sub>r</sub>   | Clock and data rise time |                     | 3    | ns   |

Table continues on the next page...

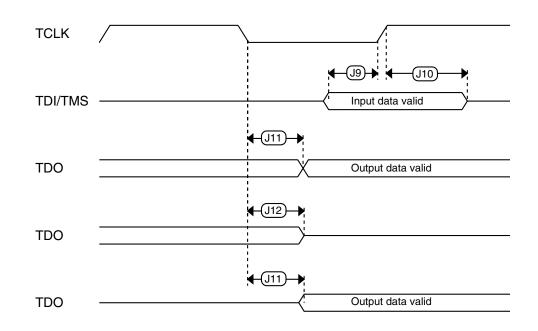

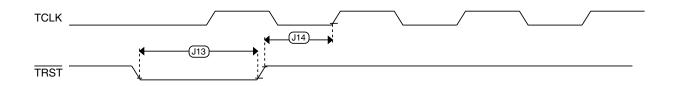

Figure 7. Test Access Port timing

# 6.2 System modules

There are no specifications necessary for the device's system modules.

# 6.3 Clock modules

| Symbol                   | Description                                                                                                                    | Min.   | Тур. | Max.                                                 | Unit | Notes |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------|------|------------------------------------------------------|------|-------|

| J <sub>cyc_fll</sub>     | FLL period jitter                                                                                                              |        | 180  | _                                                    | ps   |       |

|                          | <ul> <li>f<sub>DCO</sub> = 48 MHz</li> <li>f<sub>DCO</sub> = 98 MHz</li> </ul>                                                 | _      | 150  | _                                                    |      |       |

| t <sub>fll_acquire</sub> | FLL target frequency acquisition time                                                                                          | —      | —    | 1                                                    | ms   | 6     |

|                          | PI                                                                                                                             | LL     |      |                                                      |      |       |

| f <sub>vco</sub>         | VCO operating frequency                                                                                                        | 48.0   | —    | 100                                                  | MHz  |       |

| I <sub>pll</sub>         | PLL operating current<br>• PLL @ 96 MHz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub> =<br>2 MHz, VDIV multiplier = 48) | _      | 1060 | -                                                    | μΑ   | 7     |

| I <sub>pll</sub>         | PLL operating current<br>• PLL @ 48 MHz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub> =<br>2 MHz, VDIV multiplier = 24) | _      | 600  | -                                                    | μΑ   | 7     |

| f <sub>pll_ref</sub>     | PLL reference frequency range                                                                                                  | 2.0    | —    | 4.0                                                  | MHz  |       |

| J <sub>cyc_pll</sub>     | PLL period jitter (RMS)                                                                                                        |        |      |                                                      |      | 8     |

|                          | • f <sub>vco</sub> = 48 MHz                                                                                                    | _      | 120  |                                                      | ps   |       |

|                          | • f <sub>vco</sub> = 100 MHz                                                                                                   | _      | 50   | _                                                    | ps   |       |

| J <sub>acc_pll</sub>     | PLL accumulated jitter over 1µs (RMS)                                                                                          |        |      |                                                      |      | 8     |

|                          | • f <sub>vco</sub> = 48 MHz                                                                                                    | _      | 1350 |                                                      | ps   |       |

|                          | • f <sub>vco</sub> = 100 MHz                                                                                                   | _      | 600  |                                                      | ps   |       |

| D <sub>lock</sub>        | Lock entry frequency tolerance                                                                                                 | ± 1.49 | _    | ± 2.98                                               | %    |       |

| D <sub>unl</sub>         | Lock exit frequency tolerance                                                                                                  | ± 4.47 | _    | ± 5.97                                               | %    |       |

| t <sub>pll_lock</sub>    | Lock detector detection time                                                                                                   | _      | _    | $150 \times 10^{-6}$<br>+ 1075(1/<br>$f_{pll_ref}$ ) | S    | 9     |

Table 15.

MCG specifications (continued)

- 1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

- 2. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

- The resulting system clock frequencies should not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco t</sub>) over voltage and temperature should be considered.

- 4. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

- 5. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- 6. This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- 7. Excludes any oscillator currents that are also consuming power while PLL is in operation.

- 8. This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary.

- This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

### 6.3.2 Oscillator electrical specifications

This section provides the electrical characteristics of the module.

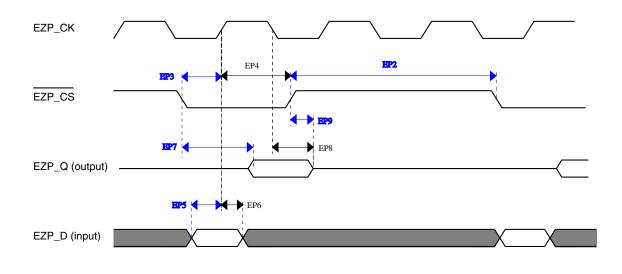

Figure 10. EzPort Timing Diagram

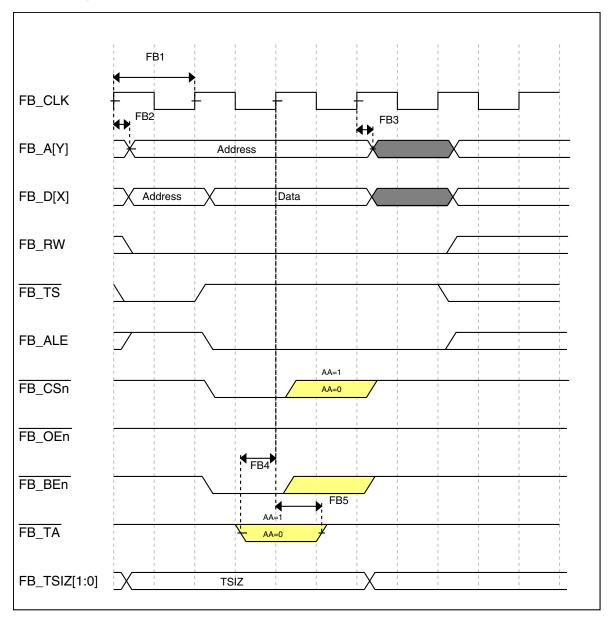

### 6.4.3 Flexbus switching specifications

All processor bus timings are synchronous; input setup/hold and output delay are given in respect to the rising edge of a reference clock, FB\_CLK. The FB\_CLK frequency may be the same as the internal system bus frequency or an integer divider of that frequency.

The following timing numbers indicate when data is latched or driven onto the external bus, relative to the Flexbus output clock (FB\_CLK). All other timing relationships can be derived from these values.

| Num | Description                             | Min. | Max.   | Unit | Notes |

|-----|-----------------------------------------|------|--------|------|-------|

|     | Operating voltage                       | 2.7  | 3.6    | V    |       |

|     | Frequency of operation                  | —    | FB_CLK | MHz  |       |

| FB1 | Clock period                            | 20   | —      | ns   |       |

| FB2 | Address, data, and control output valid | —    | 11.5   | ns   | 1     |

| FB3 | Address, data, and control output hold  | 0.5  | —      | ns   | 1     |

| FB4 | Data and FB_TA input setup              | 8.5  | —      | ns   | 2     |

| FB5 | Data and FB_TA input hold               | 0.5  | —      | ns   | 2     |

Table 25. Flexbus limited voltage range switching specifications

1. Specification is valid for all FB\_AD[31:0], FB\_BE/BWEn, FB\_CSn, FB\_OE, FB\_R/W, FB\_TBST, FB\_TSIZ[1:0], FB\_ALE, and FB\_TS.

Figure 12. FlexBus write timing diagram

## 6.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

# 6.6 Analog

| Symbol            | Description    | Conditions                     | Min.   | Typ. <sup>1</sup> | Max. | Unit | Notes |

|-------------------|----------------|--------------------------------|--------|-------------------|------|------|-------|

| C <sub>rate</sub> | ADC conversion | ≤ 13 bit modes                 | 18.484 |                   | 450  | Ksps | 7     |

|                   | rate           | No ADC hardware averaging      |        |                   |      |      |       |

|                   |                | Continuous conversions enabled |        |                   |      |      |       |

|                   |                | Peripheral clock = 50<br>MHz   |        |                   |      |      |       |

|                   |                | 16 bit modes                   | 37.037 | —                 | 250  | Ksps | 8     |

|                   |                | No ADC hardware averaging      |        |                   |      |      |       |

|                   |                | Continuous conversions enabled |        |                   |      |      |       |

|                   |                | Peripheral clock = 50<br>MHz   |        |                   |      |      |       |

#### Table 29. 16-bit ADC with PGA operating conditions (continued)

- 1. Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25°C, f<sub>ADCK</sub> = 6 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- 2. ADC must be configured to use the internal voltage reference (VREF\_OUT)

- 3. PGA reference is internally connected to the VREF\_OUT pin. If the user wishes to drive VREF\_OUT with a voltage other than the output of the VREF module, the VREF module must be disabled.

- 4. For single ended configurations the input impedance of the driven input is R<sub>PGAD</sub>/2

- 5. The analog source resistance (R<sub>AS</sub>), external to MCU, should be kept as minimum as possible. Increased R<sub>AS</sub> causes drop in PGA gain without affecting other performances. This is not dependent on ADC clock frequency.

- The minimum sampling time is dependent on input signal frequency and ADC mode of operation. A minimum of 1.25µs time should be allowed for F<sub>in</sub>=4 kHz at 16-bit differential mode. Recommended ADC setting is: ADLSMP=1, ADLSTS=2 at 8 MHz ADC clock.

- 7. ADC clock = 18 MHz, ADLSMP = 1, ADLST = 00, ADHSC = 1

- 8. ADC clock = 12 MHz, ADLSMP = 1, ADLST = 01, ADHSC = 1

### 6.6.1.4 16-bit ADC with PGA characteristics with Chop enabled (ADC\_PGA[PGACHPb] =0) Table 30. 16-bit ADC with PGA characteristics

| Symbol               | Description      | Conditions                                                    | Min.                                                 | Typ. <sup>1</sup>                  | Max. | Unit | Notes |

|----------------------|------------------|---------------------------------------------------------------|------------------------------------------------------|------------------------------------|------|------|-------|

| I <sub>DDA_PGA</sub> | Supply current   | Low power<br>(ADC_PGA[PGALPb]=0)                              | _                                                    | 420                                | 644  | μA   | 2     |

| I <sub>DC_PGA</sub>  | Input DC current |                                                               | $\frac{2}{R_{\text{PGAD}}} \left(\frac{1}{2}\right)$ | V <sub>REFPGA</sub> ×0.5<br>(Gain+ |      | A    | 3     |

|                      |                  | Gain =1, $V_{REFPGA}$ =1.2V,<br>$V_{CM}$ =0.5V                | _                                                    | 1.54                               |      | μA   |       |

|                      |                  | Gain =64, V <sub>REFPGA</sub> =1.2V,<br>V <sub>CM</sub> =0.1V | _                                                    | 0.57                               |      | μA   |       |

Table continues on the next page ...

Peripheral operating requirements and behaviors

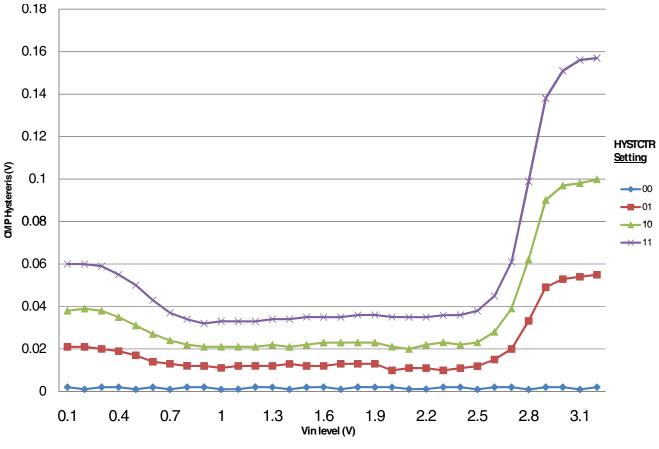

Figure 17. Typical hysteresis vs. Vin level (VDD=3.3V, PMODE=1)

### 6.6.3 12-bit DAC electrical characteristics

### 6.6.3.1 12-bit DAC operating requirements Table 32. 12-bit DAC operating requirements

| Symbol           | Desciption              | Min.                                      | Max. | Unit | Notes |

|------------------|-------------------------|-------------------------------------------|------|------|-------|

| V <sub>DDA</sub> | Supply voltage          | 1.71                                      | 3.6  | V    |       |

| VDACR            | Reference voltage       | 1.13                                      | 3.6  | V    | 1     |

| T <sub>A</sub>   | Temperature             | Operating temperature range of the device |      | °C   |       |

| CL               | Output load capacitance | _                                         | 100  | pF   | 2     |

| ١L               | Output load current     | —                                         | 1    | mA   |       |

1. The DAC reference can be selected to be V<sub>DDA</sub> or the voltage output of the VREF module (VREF\_OUT)

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC

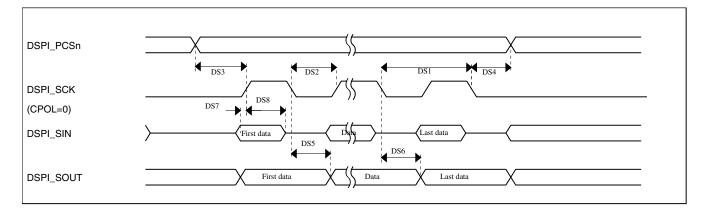

| Num | Description                         | Min.                          | Max.                     | Unit | Notes |

|-----|-------------------------------------|-------------------------------|--------------------------|------|-------|

| DS2 | DSPI_SCK output high/low time       | (t <sub>SCK</sub> /2) - 4     | (t <sub>SCK/2)</sub> + 4 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay   | (t <sub>BUS</sub> x 2) –<br>4 | _                        | ns   | 2     |

| DS4 | DSPI_SCK to DSPI_PCSn invalid delay | (t <sub>BUS</sub> x 2) –<br>4 | —                        | ns   | 3     |

| DS5 | DSPI_SCK to DSPI_SOUT valid         | _                             | 8.5                      | ns   |       |

| DS6 | DSPI_SCK to DSPI_SOUT invalid       | -1.2                          | —                        | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup    | 19.1                          | —                        | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold     | 0                             |                          | ns   |       |

Table 44. Master mode DSPI timing (full voltage range) (continued)

- 1. The DSPI module can operate across the entire operating voltage for the processor, but to run across the full voltage range the maximum frequency of operation is reduced.

- 2. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

- 3. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

### Figure 24. DSPI classic SPI timing — master mode

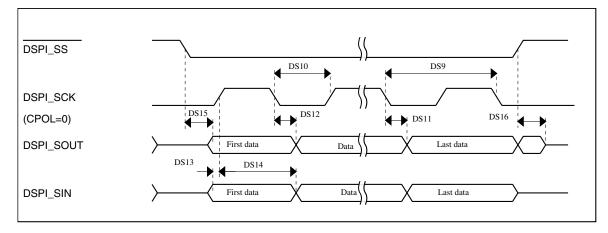

#### Table 45. Slave mode DSPI timing (full voltage range)

| Num  | Description                              | Min.                      | Max.                     | Unit |

|------|------------------------------------------|---------------------------|--------------------------|------|

|      | Operating voltage                        | 1.71                      | 3.6                      | V    |

|      | Frequency of operation                   | _                         | 6.25                     | MHz  |

| DS9  | DSPI_SCK input cycle time                | 8 x t <sub>BUS</sub>      | —                        | ns   |

| DS10 | DSPI_SCK input high/low time             | (t <sub>SCK</sub> /2) - 4 | (t <sub>SCK/2)</sub> + 4 | ns   |

| DS11 | DSPI_SCK to DSPI_SOUT valid              | _                         | 24                       | ns   |

| DS12 | DSPI_SCK to DSPI_SOUT invalid            | 0                         | —                        | ns   |

| DS13 | DSPI_SIN to DSPI_SCK input setup         | 3.2                       | —                        | ns   |

| DS14 | DSPI_SCK to DSPI_SIN input hold          | 7                         | —                        | ns   |

| DS15 | DSPI_SS active to DSPI_SOUT driven       | _                         | 19                       | ns   |

| DS16 | DSPI_SS inactive to DSPI_SOUT not driven | _                         | 19                       | ns   |

Figure 25. DSPI classic SPI timing — slave mode

### 6.8.8 Inter-Integrated Circuit Interface (I<sup>2</sup>C) timing Table 46. I<sup>2</sup>C timing

| Characteristic                                                                                     | Symbol                | Standa           | rd Mode           | Fast                               | Fast Mode        |     |

|----------------------------------------------------------------------------------------------------|-----------------------|------------------|-------------------|------------------------------------|------------------|-----|

|                                                                                                    |                       | Minimum          | Maximum           | Minimum                            | Maximum          |     |

| SCL Clock Frequency                                                                                | f <sub>SCL</sub>      | 0                | 100               | 0                                  | 400              | kHz |

| Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated. | t <sub>HD</sub> ; STA | 4                |                   | 0.6                                | —                | μs  |

| LOW period of the SCL clock                                                                        | t <sub>LOW</sub>      | 4.7              | _                 | 1.3                                | —                | μs  |

| HIGH period of the SCL clock                                                                       | t <sub>HIGH</sub>     | 4                | —                 | 0.6                                | —                | μs  |

| Set-up time for a repeated START condition                                                         | t <sub>SU</sub> ; STA | 4.7              | _                 | 0.6                                | —                | μs  |

| Data hold time for I <sub>2</sub> C bus devices                                                    | t <sub>HD</sub> ; DAT | 0 <sup>1</sup>   | 3.45 <sup>2</sup> | 0 <sup>3</sup>                     | 0.9 <sup>1</sup> | μs  |

| Data set-up time                                                                                   | t <sub>SU</sub> ; DAT | 250 <sup>4</sup> | —                 | 100 <sup>2, 5</sup>                | —                | ns  |

| Rise time of SDA and SCL signals                                                                   | t <sub>r</sub>        | —                | 1000              | 20 +0.1C <sub>b</sub> <sup>6</sup> | 300              | ns  |

| Fall time of SDA and SCL signals                                                                   | t <sub>f</sub>        | —                | 300               | 20 +0.1C <sub>b</sub> <sup>5</sup> | 300              | ns  |

| Set-up time for STOP condition                                                                     | t <sub>SU</sub> ; STO | 4                | —                 | 0.6                                | —                | μs  |

| Bus free time between STOP and<br>START condition                                                  | t <sub>BUF</sub>      | 4.7              | _                 | 1.3                                | —                | μs  |

| Pulse width of spikes that must be<br>suppressed by the input filter                               | t <sub>SP</sub>       | N/A              | N/A               | 0                                  | 50               | ns  |

1. The master mode I<sup>2</sup>C deasserts ACK of an address byte simultaneously with the falling edge of SCL. If no slaves acknowledge this address byte, then a negative hold time can result, depending on the edge rates of the SDA and SCL lines.

2. The maximum tHD; DAT must be met only if the device does not stretch the LOW period (tLOW) of the SCL signal.

- 3. Input signal Slew = 10 ns and Output Load = 50 pF

- 4. Set-up time in slave-transmitter mode is 1 IPBus clock period, if the TX FIFO is empty.

- 5. A Fast mode l<sup>2</sup>C bus device can be used in a Standard mode l2C bus system, but the requirement t<sub>SU; DAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, then it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SU; DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard mode l<sup>2</sup>C bus specification) before the SCL line is released.

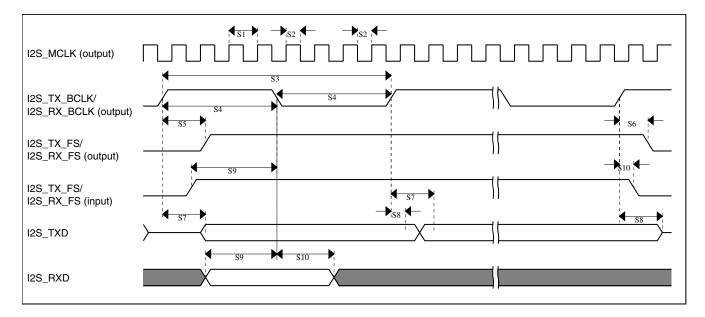

# Table 52. I2S/SAI master mode timing in VLPR, VLPW, and VLPS modes (full voltage range) (continued)

| Num. | Characteristic                                      | Min. | Max. | Unit |

|------|-----------------------------------------------------|------|------|------|

| S8   | I2S_TX_BCLK to I2S_TXD invalid                      | 0    | —    | ns   |

| S9   | I2S_RXD/I2S_RX_FS input setup before<br>I2S_RX_BCLK | 45   |      | ns   |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK      | 0    | _    | ns   |

### Figure 32. I2S/SAI timing — master modes

# Table 53. I2S/SAI slave mode timing in VLPR, VLPW, and VLPS modes (full voltage range)

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |

| S11  | I2S_TX_BCLK/I2S_RX_BCLK cycle time (input)                        | 250  | —    | ns          |

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input)              | 45%  | 55%  | MCLK period |

| S13  | I2S_TX_FS/I2S_RX_FS input setup before<br>I2S_TX_BCLK/I2S_RX_BCLK | 30   | -    | ns          |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after<br>I2S_TX_BCLK/I2S_RX_BCLK   | 3    | -    | ns          |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                     | —    | 63   | ns          |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                   | 0    | —    | ns          |

| S17  | I2S_RXD setup before I2S_RX_BCLK                                  | 30   | —    | ns          |

| S18  | I2S_RXD hold after I2S_RX_BCLK                                    | 2    | —    | ns          |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup>    | _    | 72   | ns          |

1. Applies to first bit in each frame and only if the TCR4[FSE] bit is clear

- 1. The TSI module is functional with capacitance values outside this range. However, optimal performance is not guaranteed.

- 2. Fixed external capacitance of 20 pF.

- 3. REFCHRG = 2, EXTCHRG=0.

- 4. REFCHRG = 0, EXTCHRG = 10.

- 5.  $V_{DD} = 3.0 V.$

- 6. The programmable current source value is generated by multiplying the SCANC[REFCHRG] value and the base current.

- 7. The programmable current source value is generated by multiplying the SCANC[EXTCHRG] value and the base current.

- 8. Measured with a 5 pF electrode, reference oscillator frequency of 10 MHz, PS = 128, NSCN = 8; lext = 16.

- 9. Measured with a 20 pF electrode, reference oscillator frequency of 10 MHz, PS = 128, NSCN = 2; lext = 16.

- 10. Measured with a 20 pF electrode, reference oscillator frequency of 10 MHz, PS = 16, NSCN = 3; lext = 16.

- 11. Sensitivity defines the minimum capacitance change when a single count from the TSI module changes. Sensitivity depends on the configuration used. The documented values are provided as examples calculated for a specific configuration of operating conditions using the following equation: (C<sub>ref</sub> \* I<sub>ext</sub>)/(I<sub>ref</sub> \* PS \* NSCN)

The typical value is calculated with the following configuration:

I<sub>ext</sub> = 6 μA (EXTCHRG = 2), PS = 128, NSCN = 2, I<sub>ref</sub> = 16 μA (REFCHRG = 7), C<sub>ref</sub> = 1.0 pF

The minimum value is calculated with the following configuration:

I<sub>ext</sub> = 2 μA (EXTCHRG = 0), PS = 128, NSCN = 32, I<sub>ref</sub> = 32 μA (REFCHRG = 15), C<sub>ref</sub> = 0.5 pF

The highest possible sensitivity is the minimum value because it represents the smallest possible capacitance that can be measured by a single count.

- 12. Time to do one complete measurement of the electrode. Sensitivity resolution of 0.0133 pF, PS = 0, NSCN = 0, 1 electrode, EXTCHRG = 7.

- 13. REFCHRG=0, EXTCHRG=4, PS=7, NSCN=0F, LPSCNITV=F, LPO is selected (1 kHz), and fixed external capacitance of 20 pF. Data is captured with an average of 7 periods window.

# 7 Dimensions

## 7.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

To find a package drawing, go to freescale.com and perform a keyword search for the drawing's document number:

| If you want the drawing for this package | Then use this document number |

|------------------------------------------|-------------------------------|

| 100-pin LQFP                             | 98ASS23308W                   |

| 104-pin MAPBGA                           | 98ASA00344D                   |

# 8 Pinout

| 100<br>LQFP | Pin Name                            | Default                             | ALT0                                | ALT1              | ALT2                            | ALT3                            | ALT4                           | ALT5     | ALT6         | ALT7                   | EzPort   |

|-------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------|---------------------------------|---------------------------------|--------------------------------|----------|--------------|------------------------|----------|

|             | CMP0_IN5/<br>ADC1_SE18              | CMP0_IN5/<br>ADC1_SE18              | CMP0_IN5/<br>ADC1_SE18              |                   |                                 |                                 |                                |          |              |                        |          |

| 27          | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23 | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23 | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23 |                   |                                 |                                 |                                |          |              |                        |          |

| 28          | XTAL32                              | XTAL32                              | XTAL32                              |                   |                                 |                                 |                                |          |              |                        |          |

| 29          | EXTAL32                             | EXTAL32                             | EXTAL32                             |                   |                                 |                                 |                                |          |              |                        |          |

| 30          | VBAT                                | VBAT                                | VBAT                                |                   |                                 |                                 |                                |          |              |                        |          |

| 31          | PTE24                               | ADC0_SE17                           | ADC0_SE17                           | PTE24             | CAN1_TX                         | UART4_TX                        |                                |          | EWM_OUT_b    |                        |          |

| 32          | PTE25                               | ADC0_SE18                           | ADC0_SE18                           | PTE25             | CAN1_RX                         | UART4_RX                        |                                |          | EWM_IN       |                        |          |

| 33          | PTE26                               | DISABLED                            |                                     | PTE26             | ENET_1588_<br>CLKIN             | UART4_CTS_b                     |                                |          | RTC_CLKOUT   | USB_CLKIN              |          |

| 34          | PTA0                                | JTAG_TCLK/<br>SWD_CLK/<br>EZP_CLK   | TSI0_CH1                            | PTA0              | UART0_CTS_<br>b/<br>UART0_COL_b | FTM0_CH5                        |                                |          |              | JTAG_TCLK/<br>SWD_CLK  | EZP_CLK  |

| 35          | PTA1                                | JTAG_TDI/<br>EZP_DI                 | TSI0_CH2                            | PTA1              | UARTO_RX                        | FTM0_CH6                        |                                |          |              | JTAG_TDI               | EZP_DI   |

| 36          | PTA2                                | JTAG_TDO/<br>TRACE_SWO/<br>EZP_DO   | TSI0_CH3                            | PTA2              | UARTO_TX                        | FTM0_CH7                        |                                |          |              | JTAG_TDO/<br>TRACE_SWO | EZP_DO   |

| 37          | PTA3                                | JTAG_TMS/<br>SWD_DIO                | TSI0_CH4                            | PTA3              | UARTO_RTS_b                     | FTM0_CH0                        |                                |          |              | JTAG_TMS/<br>SWD_DIO   |          |

| 38          | PTA4/<br>LLWU_P3                    | NMI_b/<br>EZP_CS_b                  | TSI0_CH5                            | PTA4/<br>LLWU_P3  |                                 | FTM0_CH1                        |                                |          |              | NMI_b                  | EZP_CS_b |

| 39          | PTA5                                | DISABLED                            |                                     | PTA5              | USB_CLKIN                       | FTM0_CH2                        | RMII0_RXER/<br>MII0_RXER       | CMP2_OUT | I2S0_TX_BCLK | JTAG_TRST_b            |          |

| 40          | VDD                                 | VDD                                 | VDD                                 |                   |                                 |                                 |                                |          |              |                        |          |

| 41          | VSS                                 | VSS                                 | VSS                                 |                   |                                 |                                 |                                |          |              |                        |          |

| 42          | PTA12                               | CMP2_IN0                            | CMP2_IN0                            | PTA12             | CAN0_TX                         | FTM1_CH0                        | rmiio_rxd1/<br>Miio_rxd1       |          | I2S0_TXD0    | FTM1_QD_<br>PHA        |          |

| 43          | PTA13/<br>LLWU_P4                   | CMP2_IN1                            | CMP2_IN1                            | PTA13/<br>LLWU_P4 | CAN0_RX                         | FTM1_CH1                        | RMII0_RXD0/<br>MII0_RXD0       |          | I2S0_TX_FS   | FTM1_QD_<br>PHB        |          |

| 44          | PTA14                               | DISABLED                            |                                     | PTA14             | SPI0_PCS0                       | UART0_TX                        | RMII0_CRS_<br>DV/<br>MII0_RXDV |          | I2S0_RX_BCLK | 12S0_TXD1              |          |

| 45          | PTA15                               | DISABLED                            |                                     | PTA15             | SPI0_SCK                        | UART0_RX                        | RMII0_TXEN/<br>MII0_TXEN       |          | I2S0_RXD0    |                        |          |

| 46          | PTA16                               | DISABLED                            |                                     | PTA16             | SPI0_SOUT                       | UART0_CTS_<br>b/<br>UART0_COL_b | RMII0_TXD0/<br>MII0_TXD0       |          | 12S0_RX_FS   | 12S0_RXD1              |          |

| 47          | PTA17                               | ADC1_SE17                           | ADC1_SE17                           | PTA17             | SPI0_SIN                        | UARTO_RTS_b                     | RMII0_TXD1/<br>MII0_TXD1       |          | I2S0_MCLK    |                        |          |

| 48          | VDD                                 | VDD                                 | VDD                                 |                   |                                 |                                 |                                |          |              |                        |          |

| 49          | VSS                                 | VSS                                 | VSS                                 |                   |                                 |                                 |                                |          |              |                        |          |

| 50          | PTA18                               | EXTAL0                              | EXTALO                              | PTA18             |                                 | FTM0_FLT2                       | FTM_CLKIN0                     |          |              |                        |          |

| 51          | PTA19                               | XTALO                               | XTALO                               | PTA19             |                                 | FTM1_FLT0                       | FTM_CLKIN1                     |          | LPTMR0_ALT1  |                        |          |

| 52          | RESET_b                             | RESET_b                             | RESET_b                             |                   |                                 |                                 |                                |          |              |                        |          |