Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 28x10b; D/A 4x5b, 4x10b                                               |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1777-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-3: PIC16(L)F1777/9 PINOUT DESCRIPTION (CONTINUED)

| Name                                                | Function              | Input<br>Type | Output<br>Type | Description                                  |  |  |  |

|-----------------------------------------------------|-----------------------|---------------|----------------|----------------------------------------------|--|--|--|

| RA5/AN4/OPA1IN0-/                                   | RA5                   | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |  |

| DAC2OUT1/PRG1F/                                     | AN4                   | AN            | _              | ADC Channel 4 input.                         |  |  |  |

| MD1MOD/SS                                           | OPA1IN0-              | AN            | _              | Operational amplifier 1 inverting input.     |  |  |  |

|                                                     | DAC2OUT1              | _             | AN             | DAC2 voltage output.                         |  |  |  |

|                                                     | PRG1F <sup>(1)</sup>  | TTL/ST        | _              | Ramp generator set_falling input.            |  |  |  |

|                                                     | MD1MOD <sup>(1)</sup> | TTL/ST        | _              | Data signal modulator modulation input.      |  |  |  |

|                                                     | SS                    | ST            |                | Slave Select input.                          |  |  |  |

| RA6/CLKOUT/C6IN1+/OSC2                              | RA6                   | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |  |

|                                                     | CLKOUT                |               | CMOS           | Fosc/4 output.                               |  |  |  |

|                                                     | C6IN1+                | AN            | _              | Comparator 6 positive input.                 |  |  |  |

|                                                     | OSC2                  | XTAL          | _              | Crystal/Resonator (LP, XT, HS modes).        |  |  |  |

| RA7/CLKIN/OSC1                                      | RA7                   | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |  |

|                                                     | CLKIN                 | TTL/ST        | _              | CLC input.                                   |  |  |  |

|                                                     | OSC1                  | XTAL          |                | Crystal/Resonator (LP, XT, HS modes).        |  |  |  |

| RB0/AN12/ZCD/HIB0/C2IN1+/                           | RB0                   | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |  |

| CCP8/COG1IN/MD4CL/                                  | AN12                  | AN            | —              | ADC Channel 12 input.                        |  |  |  |

| INT                                                 | ZCD                   | AN            | _              | Zero-cross detection input.                  |  |  |  |

|                                                     | HIB0                  | HP            | HP             | High-Power output.                           |  |  |  |

|                                                     | C2IN1+                | AN            | _              | Comparator 2 positive input.                 |  |  |  |

|                                                     | CCP8 <sup>(1)</sup>   | TTL/ST        | _              | CCP8 capture input.                          |  |  |  |

|                                                     | COG1IN <sup>(1)</sup> | TTL/ST        | _              | Complementary output generator 1 input.      |  |  |  |

|                                                     | MD4CL <sup>(1)</sup>  | TTL/ST        | _              | Data signal modulator 4 low carrier input.   |  |  |  |

|                                                     | INT                   | TTL/ST        |                | External interrupt.                          |  |  |  |

| RB1/AN10/PRG1IN1/PRG2IN0/                           | RB1                   | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |  |

| PRG4R/HIB1/C1IN3-/C2IN3-/                           | AN10                  | AN            | _              | ADC Channel 10 input.                        |  |  |  |

| C3IN3-/C4IN3-/OPA2OUT/<br>OPA1IN1+/OPA1IN1-/COG2IN/ | PRG1IN1               | AN            | _              | Ramp generator 1 reference voltage input.    |  |  |  |

| MD4CH                                               | PRG2IN0               | AN            | _              | Ramp generator 2 reference voltage input.    |  |  |  |

|                                                     | PRG4R <sup>(1)</sup>  | TTL/ST        |                | Ramp generator set_rising input.             |  |  |  |

|                                                     | HIB1                  | HP            | HP             | High-Power output.                           |  |  |  |

|                                                     | C1IN3-                | AN            | _              | Comparator 1 negative input.                 |  |  |  |

|                                                     | C2IN3-                | AN            |                | Comparator 2 negative input.                 |  |  |  |

|                                                     | C3IN3-                | AN            | _              | Comparator 3 negative input.                 |  |  |  |

|                                                     | C4IN3-                | AN            |                | Comparator 4 negative input.                 |  |  |  |

|                                                     | OPA2OUT               |               | AN             | Operational amplifier 2 output.              |  |  |  |

|                                                     | OPA1IN1+              | AN            |                | Operational amplifier 1 non-inverting input. |  |  |  |

|                                                     | OPA1IN1-              | AN            | _              | Operational amplifier 1 inverting input.     |  |  |  |

|                                                     | COG2IN <sup>(1)</sup> | TTL/ST        | —              | Complementary output generator 2 input.      |  |  |  |

|                                                     | MD4CH <sup>(1)</sup>  | TTL/ST        |                | Data signal modulator 4 high carrier input.  |  |  |  |

Legend:AN = Analog input or outputCMOS = CMOS compatible input or outputOD= Open-DrainTTL = TTL compatible inputST= Schmitt Trigger input with CMOS levelsI<sup>2</sup>C= Schmitt Trigger input with I<sup>2</sup>CHP = High PowerXTAL = Crystal levelsXTAL = Crystal levelsI

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

| Name                | Function  | Input<br>Type | Output<br>Type | Description                                |

|---------------------|-----------|---------------|----------------|--------------------------------------------|

| RE1/AN6/DAC6OUT1/   | RE1       | TTL/ST        | CMOS           | General purpose I/O.                       |

| DAC6REF1-/DAC8REF1- | AN6       | AN            |                | ADC Channel 6 input.                       |

|                     | DAC6OUT1  | —             | AN             | DAC6 voltage output.                       |

|                     | DAC6REF1- | AN            |                | DAC6 negative reference.                   |

|                     | DAC8REF1- | AN            | _              | DAC8 negative reference.                   |

| RE2/AN7/DAC8OUT1    | RE2       | TTL/ST        | CMOS           | General purpose I/O.                       |

|                     | AN7       | AN            | _              | ADC Channel 7 input.                       |

|                     | DAC8OUT1  | —             | AN             | DAC8 voltage output.                       |

| RE3/MCLR/VPP        | RE3       | TTL/ST        | CMOS           | General purpose input.                     |

|                     | MCLR      | ST            | _              | Master clear input.                        |

| Vdd                 | Vdd       | Power         |                | Positive supply.                           |

| Vss                 | Vss       | Power         |                | Ground reference.                          |

| OUT <sup>(2)</sup>  | C1OUT     |               | CMOS           | Comparator 1 output.                       |

|                     | C2OUT     |               | CMOS           | Comparator 2 output.                       |

|                     | C3OUT     |               | CMOS           | Comparator 3 output.                       |

|                     | C4OUT     |               | CMOS           | Comparator 4 output.                       |

|                     | C5OUT     |               | CMOS           | Comparator 5 output.                       |

|                     | C6OUT     |               | CMOS           | Comparator 6 output.                       |

|                     | C7OUT     |               | CMOS           | Comparator 7 output.                       |

|                     | C8OUT     |               | CMOS           | Comparator 8 output.                       |

|                     | CCP1      |               | CMOS           | Compare/PWM1 output.                       |

|                     | CCP2      |               | CMOS           | Compare/PWM2 output.                       |

|                     | CCP7      |               | CMOS           | Compare/PWM7 output.                       |

|                     | CCP8      |               | CMOS           | Compare/PWM8 output.                       |

|                     | MD1OUT    |               | CMOS           | Data signal modulator 1 output.            |

|                     | MD2OUT    |               | CMOS           | Data signal modulator 2 output.            |

|                     | MD3OUT    |               | CMOS           | Data signal modulator 3 output.            |

|                     | MD4OUT    |               | CMOS           | Data signal modulator 4 output.            |

|                     | PWM3OUT   |               | CMOS           | PWM3 output.                               |

|                     | PWM4OUT   |               | CMOS           | PWM4 output.                               |

|                     | PWM5OUT   |               | CMOS           | PWM5 output.                               |

|                     | PWM6OUT   |               | CMOS           | PWM6 output.                               |

|                     | PWM9OUT   |               | CMOS           | PWM9 output.                               |

|                     | PWM10OUT  |               | CMOS           | PWM10 output.                              |

|                     | PWM11OUT  |               | CMOS           | PWM11 output.                              |

|                     | PWM12OUT  |               | CMOS           | PWM12 output.                              |

|                     | COG1A     |               | CMOS           | Complementary output generator 1 output A. |

|                     | COG1B     |               | CMOS           | Complementary output generator 1 output B. |

|                     | COG1C     |               | CMOS           | Complementary output generator 1 output C. |

|                     | COG1D     |               | CMOS           | Complementary output generator 1 output D. |

|                     | COG2A     |               | CMOS           | Complementary output generator 2 output A. |

TABLE 1-3: PIC16(L)F1777/9 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

|                    |             | Peripheral Input |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          |                 |            |            |                    |           |                    |                    |                 |              |

|--------------------|-------------|------------------|--------------------|--------------|------------|-----------|-------------------------|---------------------------|--------------|--------------|-----|--------|--------|---------|----------|----------|-----------------|------------|------------|--------------------|-----------|--------------------|--------------------|-----------------|--------------|

| Peripheral Output  | ADC Trigger | COG Clock        | COG Rising/Falling | COG Shutdown | 10-bit DAC | 5-bit DAC | <b>PRG Analog Input</b> | <b>PRG Rising/Falling</b> | Comparator + | Comparator - | CLC | DSM CH | DSM CL | DSM Mod | Op Amp + | Op Amp - | Op Amp Override | 10-bit PWM | 16-bit PWM | <b>CCP</b> Capture | CCP Clock | Timer2/4/6/8 Clock | Timer2/4/6/8 Reset | Timer1/3/5 Gate | Timer0 Clock |

| FVR                |             |                  |                    |              | •          | •         | ٠                       |                           | ٠            | ٠            |     |        |        |         | •        | •        |                 |            |            |                    |           |                    |                    |                 |              |

| ZCD                |             |                  |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          | •               |            |            |                    |           | •                  |                    |                 |              |

| PRG                |             |                  |                    |              |            |           |                         |                           | •            |              |     |        |        |         | •        | •        |                 |            |            |                    |           |                    |                    |                 |              |

| 10-bit DAC         |             |                  |                    |              |            |           | •                       |                           | •            |              |     |        |        |         | •        | •        |                 |            |            |                    |           |                    |                    |                 |              |

| 5-bit DAC          |             |                  |                    |              |            |           | •                       |                           | •            |              |     |        |        |         | •        | •        |                 |            |            |                    |           |                    |                    |                 |              |

| CCP                | •           |                  | ٠                  |              |            |           |                         | ٠                         |              |              | ٠   | ٠      | •      | ٠       |          |          | •               |            |            |                    |           |                    | •                  |                 |              |

| Comparator (sync)  | •           |                  |                    |              |            |           |                         | •                         |              |              | •   |        |        |         |          |          | •               |            |            | •                  |           |                    | •                  | •               |              |

| Comparator (async) |             |                  | •                  | •            |            |           |                         |                           |              |              |     |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| CLC                | •           |                  | •                  | •            |            |           |                         |                           |              |              | •   | •      | •      | •       |          |          | •               |            |            | •                  |           | •                  | •                  |                 |              |

| DSM                |             |                  |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| COG                |             |                  |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          | •               |            |            |                    |           |                    |                    |                 |              |

| EUSART TX/CK       |             |                  |                    |              |            |           |                         |                           |              |              | •   |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| EUSART DT          |             |                  |                    |              |            |           |                         |                           |              |              | •   |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| MSSP SCK/SCL       |             |                  |                    |              |            |           |                         |                           |              |              | •   |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| MSSP SDO/SDA       |             |                  |                    |              |            |           |                         |                           |              |              | •   |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| Op Amp             |             |                  |                    |              |            |           | •                       |                           |              |              |     |        |        |         |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| 10-bit PWM         | •           |                  | •                  |              |            |           |                         | •                         |              |              | •   | •      | •      | •       |          |          | •               |            |            |                    |           |                    | •                  |                 |              |

| 16-bit PWM         | •           |                  | •                  |              |            |           |                         | •                         |              |              | •   | •      | •      | •       |          |          | •               |            |            |                    |           |                    | •                  |                 |              |

| Timer0 overflow    | •           |                  |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 |            |            |                    |           |                    |                    | •               |              |

| Timer2 = T2PR      |             |                  |                    | ٠            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer4 = T4PR      |             |                  |                    | ٠            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer6 = T6PR      |             |                  |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer8 = T8PR      |             |                  |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer2 Postscale   | •           |                  |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer4 Postscale   | •           |                  |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer6 Postscale   | •           |                  |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer8 Postscale   | •           |                  |                    | ٠            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer1 overflow    | ٠           |                  |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    |                    |                 |              |

| Timer3 overflow    | •           |                  |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    |                    |                 |              |

| Timer5 overflow    | •           |                  |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    |                    |                 |              |

| SOSC               |             |                  |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          |                 |            | •          |                    |           | ٠                  |                    |                 |              |

| Fosc/4             |             | ٠                |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          |                 |            |            |                    |           | •                  |                    |                 |              |

| Fosc               |             | •                |                    |              |            |           |                         |                           |              |              | •   | •      | •      |         |          |          |                 |            | •          |                    |           | ٠                  |                    |                 |              |

| HFINTOSC           |             | •                |                    |              |            |           |                         |                           |              |              | •   | •      | •      |         |          |          |                 |            | •          |                    |           | ٠                  |                    |                 |              |

| LFINTOSC           |             |                  |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 |            | •          |                    |           | •                  |                    |                 |              |

| MFINTOSC           |             |                  |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          |                 |            |            |                    |           | ٠                  |                    |                 |              |

| IOCIF              |             |                  |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 |            |            | •                  | •         |                    |                    |                 |              |

| PPS Input pin      |             |                  | •                  | ٠            |            |           |                         | •                         |              |              |     | •      | •      | •       |          |          |                 |            |            | •                  | •         | •                  | •                  | •               | •            |

TABLE 1-4: PERIPHERAL CONNECTION MATRIX

## TABLE 3-12: PIC16(L)F1777 MEMORY MAP, BANK 24-31

|              | BANK 24                       |              | BANK 25                       |              | BANK 26                       |      | BANK 27                       |      | BANK 28                       |      | BANK 29                       |              | BANK 30                       |      | BANK 31                       |

|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|--------------|-------------------------------|------|-------------------------------|

| C00h         | Core Registers<br>(Table 3-2) | C80h         | Core Registers<br>(Table 3-2) | D00h         | Core Registers<br>(Table 3-2) | D80h | Core Registers<br>(Table 3-2) | E00h | Core Registers<br>(Table 3-2) | E80h | Core Registers<br>(Table 3-2) | F00h         | Core Registers<br>(Table 3-2) | F80h | Core Registers<br>(Table 3-2) |

| C0Bh         |                               | C8Bh         |                               | D0Bh         |                               | D8Bh |                               | E0Bh |                               | E8Bh |                               | F0Bh         |                               | F8Bh |                               |

| C0Ch         | _                             | C8Ch         | —                             | D0Ch         | —                             |      |                               |      |                               |      |                               |              |                               |      |                               |

| C0Dh         | _                             | C8Dh         | —                             | D0Dh         | —                             |      |                               |      |                               |      |                               |              |                               |      |                               |

| C0Eh         | —                             | C8Eh         | —                             | D0Eh         | —                             |      |                               |      |                               |      |                               |              |                               |      |                               |

| C0Fh         | —                             | C8Fh         | —                             | D0Fh         | —                             |      |                               |      |                               |      |                               |              |                               |      |                               |

| C10h         | —                             | C90h         | —                             | D10h         | —                             |      |                               |      |                               |      |                               |              |                               |      |                               |

| C11h         | _                             | C91h         | _                             | D11h         | _                             |      |                               |      |                               |      |                               |              |                               |      |                               |

| C12h         | —                             | C92h         | —                             | D12h         | —                             |      |                               |      |                               |      |                               |              |                               |      |                               |

| C13h         | —                             | C93h         | _                             | D13h         | —                             |      |                               |      |                               |      |                               |              |                               |      |                               |

| C14h         | —                             | C94h         | _                             | D14h         | —                             |      |                               |      |                               |      |                               |              |                               |      |                               |

| C15h         | —                             | C95h         | —                             | D15h         | —                             |      |                               |      |                               |      |                               |              |                               |      |                               |

| C16h<br>C17h | —                             | C96h<br>C97h | _                             | D16h<br>D17h | —                             |      |                               |      |                               |      |                               |              |                               |      |                               |

| C17h<br>C18h |                               | C97h<br>C98h |                               | D17h<br>D18h |                               |      | See Table 3-15                |      | See Table 3-15                |      | See Table 3-15                |              | See Table 3-15                |      | See Table 3-16                |

| C18h         |                               | C99h         |                               | D19h         |                               |      | for register map-             |      | for register map-             |      | for register map-             |              | for register map-             |      | for register map-             |

| C19h<br>C1Ah |                               | C99h<br>C9Ah |                               | D19n<br>D1Ah |                               |      | ping details                  |      | ping details                  |      | ping details                  |              | ping details                  |      | ping details                  |

| C1An<br>C1Bh |                               | C9An<br>C9Bh |                               | D1An<br>D1Bh | <br>MD4CON0                   |      |                               |      |                               |      |                               |              |                               |      |                               |

| C1Ch         |                               | C9Ch         |                               | D1Ch         | MD4CON0<br>MD4CON1            |      |                               |      |                               |      |                               |              |                               |      |                               |

| C1Dh         | _                             | C9Dh         | _                             | D1Dh         | MD4SRC                        |      |                               |      |                               |      |                               |              |                               |      |                               |

| C1Eh         | _                             | C9Eh         | _                             | D1Eh         | MD4CARL                       |      |                               |      |                               |      |                               |              |                               |      |                               |

| C1Fh         | _                             | C9Fh         | _                             | D1Fh         | MD4CARH                       |      |                               |      |                               |      |                               |              |                               |      |                               |

| C20h         |                               | CA0h         |                               | D20h         | 112 10/ 4 41                  |      |                               |      |                               |      |                               |              |                               |      |                               |

|              |                               |              |                               |              |                               |      |                               |      |                               |      |                               |              |                               |      |                               |

|              | Unimplemented                 | CBFh         | Unimplemented                 |              | Unimplemented                 |      |                               |      |                               |      |                               |              |                               |      |                               |

|              | Read as '0'                   | CC0h         | Read as '0'                   |              | Read as '0'                   |      |                               |      |                               |      |                               |              |                               |      |                               |

|              |                               |              |                               |              |                               |      |                               |      |                               |      |                               |              |                               |      |                               |

| C6Fh         |                               | CEFh         |                               | D6Fh         |                               | DEFh |                               | E6Fh | -                             | EEFh |                               | F6Fh         |                               | FEFh |                               |

| C70h         |                               | CF0h         |                               | D70h         |                               | DF0h |                               | E70h |                               | EF0h |                               | F70h         |                               | FF0h | _                             |

|              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |

|              | /011 - / FII                  | CFFh         | /011 - / FI                   | D7Fh         | 1011 - 1711                   | DFFh | 1011 - 1711                   | E7Fh | /011-770                      | EFFh |                               | <b>F7F</b> b | /011-771                      | FFFb | /011-7711                     |

| CFFh         |                               | CFFN         |                               | DIFN         |                               | DEEN |                               | E/FN |                               | EFFN |                               | F7Fh         |                               | FFFh |                               |

Legend: = Unimplemented data memory locations, read as '0'.

## TABLE 3-18: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                    |          |                    |                                              |           |                      | - /       |           |         |        |                      |                              |  |

|--------------------|----------|--------------------|----------------------------------------------|-----------|----------------------|-----------|-----------|---------|--------|----------------------|------------------------------|--|

| Addr               | Name     | Bit 7              | Bit 6                                        | Bit 5     | Bit 4                | Bit 3     | Bit 2     | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on all<br>other Resets |  |

| Bank               | ¢ 9      | _                  |                                              |           |                      |           |           |         |        | _                    |                              |  |

| 48Ch<br>to<br>48Dh | _        | Unimplemented      |                                              | -         | —                    |           |           |         |        |                      |                              |  |

| 48Eh               | ADRESL   | ADC Result Regis   | ster Low                                     |           | XXXX XXXX            | uuuu uuuu |           |         |        |                      |                              |  |

| 48Fh               | ADRESH   | ADC Result Regis   | ster High                                    |           |                      |           |           |         |        | XXXX XXXX            | uuuu uuuu                    |  |

| 490h               | ADCON0   |                    |                                              | CHS       | <5:0>                |           |           | GO/DONE | ADON   | 0000 0000            | 0000 0000                    |  |

| 491h               | ADCON1   | ADFM               |                                              | ADCS<2:0> |                      | —         | ADNREF    | ADPRE   | F<1:0> | 0000 -000            | 0000 -000                    |  |

| 492h               | ADCON2   | —                  | _                                            |           |                      | TRIGSI    | EL<5:0>   |         |        | 00 0000              | 00 0000                      |  |

| 493h               | T2TMR    | Holding Register f | Holding Register for the 8-bit TMR2 Register |           |                      |           |           |         |        |                      |                              |  |

| 494h               | T2PR     | TMR2 Period Reg    | TMR2 Period Register                         |           |                      |           |           |         |        |                      |                              |  |

| 495h               | T2CON    | ON                 |                                              | CKPS<2:0> |                      |           | OUTP      | S<3:0>  |        | 0000 0000            | 0000 0000                    |  |

| 496h               | T2HLT    | PSYNC              | CKPOL                                        | CKSYNC    |                      |           | MODE<4:0> |         |        | 0000 0000            | 0000 0000                    |  |

| 497h               | T2CLKCON | _                  |                                              |           | —                    |           | CS<       | :3:0>   |        | 0000                 | 0000                         |  |

| 498h               | T2RST    | _                  |                                              |           |                      |           | RSEL<4:0> |         |        | 0 0000               | 0 0000                       |  |

| 499h               |          | Unimplemented      |                                              |           |                      |           |           |         |        | —                    | _                            |  |

| 49Ah               | T8TMR    | Holding Register f | or the 8-bit TMR8                            | Register  |                      |           |           |         |        | 0000 0000            | 0000 0000                    |  |

| 49Bh               | T8PR     | TMR8 Period Reg    | TMR8 Period Register                         |           |                      |           |           |         |        |                      |                              |  |

| 49Ch               | T8CON    | ON                 |                                              | CKPS<2:0> | CKPS<2:0> OUTPS<3:0> |           |           |         |        |                      |                              |  |

| 49Dh               | T8HLT    | PSYNC              | CKPOL                                        | CKSYNC    |                      |           | MODE<4:0> |         |        | 0000 0000            | 0000 0000                    |  |

| 49Eh               | T8CLKCON | _                  |                                              | _         | —                    |           | CS<       | :3:0>   |        | 0000                 | 0000                         |  |

| 49Fh               | T8RST    | _                  | _                                            | _         |                      |           | RSEL<4:0> |         |        | 0 0000               | 0 0000                       |  |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** Unimplemented, read as '1'.

2: Unimplemented on PIC16LF1777/8/9.

**3:** Unimplemented on PIC16(L)F1778.

### 4.6 Device ID and Revision ID

The 14-bit device ID word is located at 8006h and the 14-bit revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

## 4.7 Register Definitions: Device and Revision

### REGISTER 4-3: DEVID: DEVICE ID REGISTER

|   | R      | R   | R               | R      | R                                                   | R                          |

|---|--------|-----|-----------------|--------|-----------------------------------------------------|----------------------------|

|   |        |     | DEV<            | :13:8> |                                                     |                            |

|   | bit 13 |     |                 |        |                                                     | bit 8                      |

|   |        |     |                 |        |                                                     |                            |

| R | R      | R   | R               | R      | R                                                   | R                          |

|   |        | DEV | <7:0>           |        |                                                     |                            |

|   |        |     |                 |        |                                                     | bit 0                      |

|   | R      |     | bit 13<br>R R R | DEV<   | R         R         R         R         R         R | DEV<13:8>           bit 13 |

#### Legend:

R = Readable bit

'1' = Bit is set '0' = Bit is cleared

bit 13-0 **DEV<13:0>:** Device ID bits

| Device      | DEVID<13:0> Values                |  |  |  |  |  |  |  |

|-------------|-----------------------------------|--|--|--|--|--|--|--|

| PIC16F1777  | 11 0000 1000 1110 ( <b>308E</b> ) |  |  |  |  |  |  |  |

| PIC16F1778  | 11 0000 1000 1111 ( <b>308F</b> ) |  |  |  |  |  |  |  |

| PIC16F1779  | 11 0000 1001 0000 ( <b>3090</b> ) |  |  |  |  |  |  |  |

| PIC16LF1777 | 11 0000 1001 0001 ( <b>3091</b> ) |  |  |  |  |  |  |  |

| PIC16LF1778 | 11 0000 1001 0010 ( <b>3092</b> ) |  |  |  |  |  |  |  |

| PIC16LF1779 | 11 0000 1001 0011 ( <b>3093</b> ) |  |  |  |  |  |  |  |

| R/W-0/0      | 0 R/W-0/0                           | R/W-0/0                   | U-0              | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|--------------|-------------------------------------|---------------------------|------------------|----------------|------------------|------------------|--------------|

| OSFIF        | C2IF                                | C1IF                      | COG1IF           | BCL1IF         | C4IF             | C3IF             | CCP2IF       |

| bit 7        | •                                   |                           |                  |                |                  |                  | bit (        |

|              |                                     |                           |                  |                |                  |                  |              |

| Legend:      |                                     |                           |                  |                |                  |                  |              |

| R = Reada    |                                     | W = Writable              |                  | •              | nented bit, read |                  |              |

| u = Bit is u | -                                   | x = Bit is unk            |                  | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is | set                                 | '0' = Bit is cle          | ared             |                |                  |                  |              |

| bit 7        | <b>OSFIF:</b> Osci                  | llator Fail Interr        | upt Flag bit     |                |                  |                  |              |

|              | 1 = Interrupt                       | is pending                |                  |                |                  |                  |              |

|              | 0 = Interrupt                       | is not pending            |                  |                |                  |                  |              |

| bit 6        | C2IF: Comp                          | arator C2 Interr          | upt Flag bit     |                |                  |                  |              |

|              | 1 = Interrupt                       | is pending is not pending |                  |                |                  |                  |              |

| bit 5        | •                                   | arator C1 Interr          | unt Elag hit     |                |                  |                  |              |

| DIL J        | 1 = Interrupt                       |                           | upt i lag bit    |                |                  |                  |              |

|              |                                     | is not pending            |                  |                |                  |                  |              |

| bit 4        | COG1IF: CO                          | )<br>G1 Auto-Shuto        | lown Interrupt   | Flag bit       |                  |                  |              |

|              | 1 = Interrupt                       | is pending                |                  | -              |                  |                  |              |

|              | 0 = Interrupt                       | is not pending            |                  |                |                  |                  |              |

| bit 3        |                                     | SP Bus Collisio           | on Interrupt Fla | ag bit         |                  |                  |              |

|              | 1 = Interrupt                       |                           |                  |                |                  |                  |              |

|              | •                                   | is not pending            |                  |                |                  |                  |              |

| bit 2        |                                     | arator C4 Interr          | upt Flag bit     |                |                  |                  |              |

|              | 1 = Interrupt<br>0 = Interrupt      | is not pending            |                  |                |                  |                  |              |

| bit 1        | •                                   | arator C3 Interr          | upt Flag bit     |                |                  |                  |              |

|              | 1 = Interrupt                       |                           | apt i lag bit    |                |                  |                  |              |

|              |                                     | is not pending            |                  |                |                  |                  |              |

| bit 0        | CCP2IF: CC                          | P2 Interrupt Fla          | ag bit           |                |                  |                  |              |

|              | 1 = Interrupt                       |                           |                  |                |                  |                  |              |

|              | 0 = Interrupt                       | is not pending            |                  |                |                  |                  |              |

| Note:        | Interrupt flag bits                 |                           |                  |                |                  |                  |              |

|              | condition occurs, its corresponding |                           |                  |                |                  |                  |              |

|              | Enable bit, GIE,                    |                           |                  |                |                  |                  |              |

|              | User software                       | should ens                | ure the          |                |                  |                  |              |

|              | appropriate inter                   |                           | are clear        |                |                  |                  |              |

|              | prior to enabling a                 | an interrupt.             |                  |                |                  |                  |              |

## REGISTER 7-9: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

#### 9.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See Table 36-8: Oscillator Parameters for the LFINTOSC specification.

#### 9.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 9-1.

#### 9.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 9.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 9.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 9-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 10        | x      | Awake          | Active      |

| 10        | A      | Sleep          | Disabled    |

| 01        | 1      | х              | Active      |

| UI        | 0      | ~              | Disabled    |

| 00        | х      | х              | Disabled    |

#### TABLE 9-1: WDT OPERATING MODES

### 9.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

#### 9.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- Device wakes up from Sleep

- Oscillator fail

- · WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 9-2 for more information.

#### 9.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 5.0 "Oscillator Module (with Fail-Safe Clock Monitor)"** for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See STATUS Register (Register 3-1) for more information.

#### 16.1.6 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note 1: | The ADIF bit is set at the completion of |

|---------|------------------------------------------|

|         | every conversion, regardless of whether  |

|         | or not the ADC interrupt is enabled.     |

|         |                                          |

2: The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the ADIE bit of the PIE1 register and the PEIE bit of the INTCON register must both be set and the GIE bit of the INTCON register must be cleared. If all three of these bits are set, the execution will switch to the Interrupt Service Routine.

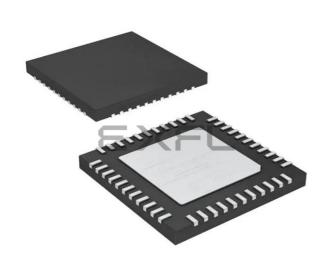

#### 16.1.7 RESULT FORMATTING

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 16-3 shows the two output formats.

#### FIGURE 16-3: 10-BIT ADC CONVERSION RESULT FORMAT

## 17.6 Register Definitions: DAC Control

Long bit name prefixes for the 5-bit DAC peripherals are shown in Table 17-2. Refer to **Section 1.1 "Register and Bit naming conventions"** for more information

TABLE 17-2:

| Peripheral          | Bit Name Prefix |

|---------------------|-----------------|

| DAC3                | DAC3            |

| DAC4                | DAC4            |

| DAC7                | DAC7            |

| DAC8 <sup>(1)</sup> | DAC8            |

Note 1: PIC16(L)F1777/9 only.

## REGISTER 17-1: DACxCON0: DACx CONTROL REGISTER 0

| R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | U-0      | R/W-0/0 |

|---------|-----|---------|---------|----------|---------|----------|---------|

| EN      | —   | OE1     | OE2     | PSS<1:0> |         | NSS<1:0> |         |

| bit 7   |     |         |         |          |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: DAC Enable bit<br>1 = DAC is enabled<br>0 = DAC is disabled                                                                                                                                  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 5   | <ul> <li>OE1: DAC Voltage Output Enable bit</li> <li>1 = DAC voltage level is also an output on the DACxOUT1 pin</li> <li>0 = DAC voltage level is disconnected from the DACxOUT1 pin</li> </ul> |

| bit 4   | <ul> <li>OE2: DAC Voltage Output Enable bit</li> <li>1 = DAC voltage level is also an output on the DACxOUT2 pin</li> <li>0 = DAC voltage level is disconnected from the DACxOUT2 pin</li> </ul> |

| bit 3-2 | <pre>PSS&lt;1:0&gt;: DAC Positive Source Select bits 11 = Reserved, do not use 10 = FVR Buffer2 output 01 = VREF+ pin 00 = VDD</pre>                                                             |

| bit 1-0 | NSS<1:0>: DAC Negative Source Select bits<br>11 = Reserved, do not use<br>10 = DACxREF1- (DAC7/8) or Reserved (DAC3/4)<br>01 = DACxREF0-<br>00 = AGND (AVSS)                                     |

## 19.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 19-1) contains Control and Status bits for the following:

- Enable

- Output

- Output polarity

- · Zero latency filter

- Speed/Power selection

- Hysteresis enable

- · Output synchronization

The CMxCON1 register (see Register 19-2) contains Control bits for the following:

- · Interrupt enable

- · Interrupt edge polarity

- Positive input channel selection

- Negative input channel selection

#### 19.2.1 COMPARATOR ENABLE

Setting the ON bit of the CMxCON0 register enables the comparator for operation. Clearing the ON bit disables the comparator resulting in minimum current consumption.

#### 19.2.2 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the OUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- · Desired pin PPS control

- Corresponding TRIS bit must be cleared

- ON bit of the CMxCON0 register must be set

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

### 19.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the POL bit of the CMxCON0 register. Clearing the POL bit results in a non-inverted output.

Table 19-2 shows the output state versus input conditions, including polarity control.

#### TABLE 19-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

#### 27.10.3 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to resume operation:

- Software controlled

- Auto-restart

The restart method is selected with the ARSEN bit of the COGxASD0 register. Waveforms of a software controlled automatic restart are shown in Figure 27-15.

#### 27.10.3.1 Software Controlled Restart

When the ARSEN bit of the COGxASD0 register is cleared, software must clear the ASE bit to restart COG operation after an auto-shutdown event.

The COG will resume operation on the first rising event after the ASE bit is cleared. Clearing the shutdown state requires all selected shutdown inputs to be false, otherwise, the ASE bit will remain set.

#### 27.10.3.2 Auto-Restart

When the ARSEN bit of the COGxASD0 register is set, the COG will restart from the auto-shutdown state automatically.

The ASE bit will clear automatically and the COG will resume operation on the first rising event after all selected shutdown inputs go false.

#### REGISTER 27-18: COGxPHR: COG RISING EVENT PHASE DELAY COUNT REGISTER

| U-0                                                                  | U-0 | R/W-0/0        | R/W-0/0  | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |

|----------------------------------------------------------------------|-----|----------------|----------|-------------------------------------------------------|---------|---------|---------|--|--|--|--|

| —                                                                    | _   |                | PHR<5:0> |                                                       |         |         |         |  |  |  |  |

| bit 7                                                                |     |                |          |                                                       |         |         | bit 0   |  |  |  |  |

|                                                                      |     |                |          |                                                       |         |         |         |  |  |  |  |

| Legend:                                                              |     |                |          |                                                       |         |         |         |  |  |  |  |

| R = Readable b                                                       | oit | W = Writable I | oit      | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |  |  |

| u = Bit is unchanged x = Bit is unknown                              |     |                | own      | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |  |  |

| '1' = Bit is set '0' = Bit is cleared q = Value depends on condition |     |                |          |                                                       |         | ion     |         |  |  |  |  |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 5-0 PHR<5:0>: Rising Event Phase Delay Count Value bits

= Number of COGx clock periods to delay rising event

#### REGISTER 27-19: COGxPHF: COG FALLING EVENT PHASE DELAY COUNT REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |  |

|-------|-----|---------|----------|---------|---------|---------|---------|--|--|--|--|--|

| —     | _   |         | PHF<5:0> |         |         |         |         |  |  |  |  |  |

| bit 7 |     |         |          |         |         |         | bit 0   |  |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

### bit 7-6 Unimplemented: Read as '0'

bit 5-0 PHF<5:0>: Falling Event Phase Delay Count Value bits

= Number of COGx clock periods to delay falling event

sensitive timing inputs that occur during, and extend beyond, the one-shot period will be suspended until the end of the one-shot time.

#### 30.1.2.2 Rising Ramp

The Rising Ramp mode is identical to the Slope Compensation mode except that the ramps have a rising slope instead of a falling slope. One side of the internal capacitor is connected to the voltage input source and the other side is connected to the internal current source. The internal current source charges this capacitor at a programmable rate. As the capacitor charges, the capacitor voltage is added to the voltage source, producing a linear voltage rise at the required rate (see Figure 30-5). The ramp terminates and the capacitor is discharged when the set\_falling timing input goes true. The next ramp starts when the set\_rising timing input goes true.

Enabling the optional one-shot by setting the OS bit of the PRGxCON0 register ensures that the capacitor is fully discharged by overriding the set\_rising timing input and holding the shorting switch closed for at least the one-shot period, typically 50 ns. Edge sensitive timing inputs that occur during the one-shot period will be ignored. Level sensitive timing inputs that occur during, and extend beyond, the one-shot period will be suspended until the end of the one-shot time.

## 30.2 Enable, Ready, Go

The EN bit of the PRGxCON0 register enables the analog circuitry including the current sources. This permits preparing the PRG module for use and allowing it to become stable before putting it into operation. When the EN bit is set then the timing inputs are enabled so that initial ramp action can be determined before the GO bit is set. The capacitor shorting switch is closed when the EN bit is set and remains closed while the GO bit is zero.

The RDY bit of the PRGxCON1 register indicates that the analog circuits and current sources are stable.

The GO bit of the PRGxCON0 register enables the switch control circuits, thereby putting the PRG into operation. The GO transition from cleared to set triggers the one-shot, thereby extending the capacitor shorting switch closure for the one-shot period.

To ensure predictable operation, set the EN bit first then wait for the RDY bit to go high before setting the GO bit.

## 30.3 Independent Set\_rising and Set\_falling Timing Inputs

The timing inputs determine when the ramp starts and stops. In the Alternating Rising/Falling mode the ramp rises when the set\_rising input goes true and falls when the set\_falling input goes true. In the Slope Compensation and Rising Ramp modes the capacitor is discharged when the set\_falling timing input goes true and the ramp starts when the set\_rising timing input goes true. The set\_falling input dominates the set\_rising input.

## 30.4 Level and Edge Timing Sensitivity

The set\_rising and set\_falling timing inputs can be independently configured as either level or edge sensitive.

Level sensitive operation is useful when it is necessary to detect a timing input true state after an overriding condition ceases. For example, level sensitivity is useful for capacitor generated timing inputs that may be suppressed by the overriding action of the one-shot. With level sensitivity a capacitor output that changes during the one-shot period will be detected at the end of the one-shot time. With edge sensitivity the change would be ignored.

Edge sensitive operation is useful for periodic timing inputs such as those generated by PWMs and clocks. The duty cycle of a level sensitive periodic signal may interfere with the other timing input. Consider an Alternating Ramp mode with a level sensitive 50% PWM as the set\_rising timing source and a level sensitive comparator as the set\_falling timing source. If the comparator output reverses the ramp while the PWM signal is still high then the ramp will improperly reverse again when the comparator signal goes low. That same scenario with the set\_rising timing input set for edge sensitivity would properly change the ramp output to rising only on the rising edge of the PWM signal.

Set\_rising and set\_falling timing input edge sensitivity is selected with the respective REDG and FEDG bits of the PRGxCON1 register.

## 30.5 One-Shot Minimum Timing

The one-shot timer ensures a minimum capacitor discharge time in the Slope Compensation and Rising Ramp modes, and a minimum rising or falling ramp duration in the Alternating Ramp mode. Setting the OS bit of the PRGxCON0 register enables the one-shot timer.

## 30.6 DAC Voltage Sources

When using any of the DACs as the voltage source expect a voltage offset equal to the current setting times the DAC equivalent resistance. This will be a constant offset in the Slope Compensation and Ramp modes and a positive/negative step offset in the Alternating mode. To avoid this limitation, feed the DAC output to the PRG input through one of the op amps set for unity gain.

## 30.7 Operation During Sleep

The RG module is unaffected by Sleep.

## 30.8 Effects of a Reset

The RG module resets to a disabled condition.