Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

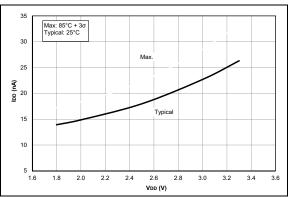

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 28x10b; D/A 4x5b, 4x10b                                              |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

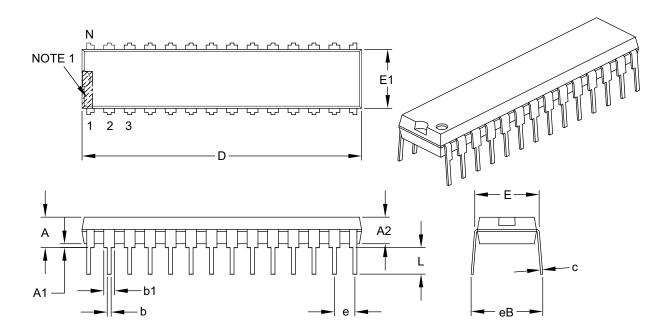

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1777-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                         | Function              | Input<br>Type    | Output<br>Type | Description                                  |  |  |

|------------------------------|-----------------------|------------------|----------------|----------------------------------------------|--|--|

| RC4/AN16/C5IN3-/C6IN3-/      | RC4                   | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

| PRG3R/T8IN/MD2CH/SDA         | AN16                  | AN               | _              | ADC Channel 16 input.                        |  |  |

|                              | C5IN3-                | AN               | _              | Comparator 5 negative input.                 |  |  |

|                              | C6IN3-                | AN               | _              | Comparator 6 negative input.                 |  |  |

|                              | PRG3R <sup>(1)</sup>  | TTL/ST           | _              | Ramp generator set_rising input.             |  |  |

|                              | T8IN <sup>(1)</sup>   | TTL/ST           | _              | Timer8 gate input.                           |  |  |

|                              | MD2CH <sup>(1)</sup>  | TTL/ST           | _              | Data signal modulator 2 high carrier input.  |  |  |

|                              | SDA                   | l <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output.          |  |  |

| RC5/AN17/OPA3IN0+/PRG3F/     | RC5                   | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

| T4IN/MD2MOD                  | AN17                  | AN               | _              | ADC Channel 17 input.                        |  |  |

|                              | OPA3IN0               | AN               | _              | Operational amplifier 3 inverting input.     |  |  |

|                              | PRG3F <sup>(1)</sup>  | TTL/ST           | _              | Ramp generator set_falling input.            |  |  |

|                              | T4IN <sup>(1)</sup>   | TTL/ST           | _              | Timer4 gate input.                           |  |  |

|                              | MD2MOD <sup>(1)</sup> | TTL/ST           | _              | Data signal modulator modulation input.      |  |  |

| RC6/AN18/PRG3IN0/PRG4IN1/    | RC6                   | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

| C5IN1-/C6IN1-/C7IN1-/C8IN1-/ | AN18                  | AN               | _              | ADC Channel 18 input.                        |  |  |

| OPA3OUT/OPA4IN1+/OPA4IN1-    | PRG3IN0               | AN               | _              | Ramp generator 3 reference voltage input.    |  |  |

|                              | PRG4IN1               | AN               | _              | Ramp generator 4 reference voltage input.    |  |  |

|                              | C5IN1-                | AN               | _              | Comparator 5 negative input.                 |  |  |

|                              | C6IN1-                | AN               | _              | Comparator 6 negative input.                 |  |  |

|                              | C7IN1-                | AN               | _              | Comparator 7 negative input.                 |  |  |

|                              | C8IN1-                | AN               | _              | Comparator 8 negative input.                 |  |  |

|                              | OPA3OUT               | _                | AN             | Operational amplifier 3 output.              |  |  |

|                              | OPA4IN1+              | AN               | _              | Operational amplifier 4 non-inverting input. |  |  |

|                              | OPA4IN1-              | AN               |                | Operational amplifier 4 inverting input.     |  |  |

| RC7/AN19/OPA3IN0-            | RC7                   | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

|                              | AN19                  | AN               | _              | ADC Channel 19 input.                        |  |  |

|                              | OPA3IN0-              | AN               | —              | Operational amplifier 3 non-inverting input. |  |  |

| RD0/AN20/OPA4IN0+            | RD0                   | TTL/ST           | CMOS           | General purpose I/O.                         |  |  |

|                              | AN20                  | AN               | —              | ADC Channel 20 input.                        |  |  |

|                              | OPA4IN0+              | AN               | —              | Operational amplifier 4 non-inverting input. |  |  |

| TABLE 1-3: | PIC16(L)F1777/9 PINOUT DESCRIPTION (CONTINUED) |

|------------|------------------------------------------------|

| IADEE 1-3. |                                                |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output = Open-Drain OD TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HP = High Power

XTAL = Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

## 3.4 Register Definitions: Status

## REGISTER 3-1: STATUS: STATUS REGISTER

| U-0                                                               | U-0                                             | U-0                                                                                       | R-1/q          | R-1/q             | R/W-0/u          | R/W-0/u           | R/W-0/u          |  |

|-------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------|----------------|-------------------|------------------|-------------------|------------------|--|

| _                                                                 | _                                               | _                                                                                         | TO             | PD                | Z                | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |

| bit 7                                                             |                                                 |                                                                                           |                | ·                 |                  |                   | bit 0            |  |

| Legend:                                                           |                                                 |                                                                                           |                |                   |                  |                   |                  |  |

| R = Readabl                                                       | e bit                                           | W = Writable I                                                                            | oit            | U = Unimpler      | mented bit, read | as '0'            |                  |  |

| u = Bit is und                                                    | changed                                         | x = Bit is unkn                                                                           | own            | -n/n = Value a    | at POR and BO    | R/Value at all o  | ther Resets      |  |

| '1' = Bit is se                                                   | et                                              | '0' = Bit is clea                                                                         | ared           | q = Value der     | pends on condit  | ion               |                  |  |

|                                                                   |                                                 |                                                                                           |                |                   |                  |                   |                  |  |

| bit 7-5                                                           | Unimplem                                        | ented: Read as 'd                                                                         | )'             |                   |                  |                   |                  |  |

| bit 4                                                             | TO: Time-C                                      | TO: Time-Out bit                                                                          |                |                   |                  |                   |                  |  |

|                                                                   | 1 = After po                                    | ower-up, CLRWDT                                                                           | instruction or | SLEEP instruc     | tion             |                   |                  |  |

|                                                                   | 0 = A WDT                                       | Time-out occurre                                                                          | d              |                   |                  |                   |                  |  |

| bit 3                                                             | PD: Power-                                      | PD: Power-Down bit                                                                        |                |                   |                  |                   |                  |  |

|                                                                   | 1 = After power-up or by the CLRWDT instruction |                                                                                           |                |                   |                  |                   |                  |  |

|                                                                   | 0 = By exec                                     | 0 = By execution of the SLEEP instruction                                                 |                |                   |                  |                   |                  |  |

| bit 2                                                             | Z: Zero bit                                     | Z: Zero bit                                                                               |                |                   |                  |                   |                  |  |

|                                                                   |                                                 | sult of an arithmet                                                                       |                |                   |                  |                   |                  |  |

|                                                                   |                                                 | sult of an arithmet                                                                       | •              |                   |                  | (4)               |                  |  |

| bit 1                                                             | •                                               | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup> |                |                   |                  |                   |                  |  |

| 1 = A carry-out from the 4th low-order bit of the result occurred |                                                 |                                                                                           |                |                   |                  |                   |                  |  |

|                                                                   |                                                 | ry-out from the 4th                                                                       |                |                   | (4)              |                   |                  |  |

| bit 0                                                             | •                                               | orrow bit (ADDWF,                                                                         |                |                   | ,                |                   |                  |  |

|                                                                   |                                                 | -out from the Mos                                                                         | U U            |                   |                  |                   |                  |  |

|                                                                   | 0 = No carr                                     | ry-out from the Mo                                                                        | ost Significan | t bit of the resu | it occurred      |                   |                  |  |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand.

## TABLE 3-18: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr               | Name                  | Bit 7         | Bit 6 | Bit 5 | Bit 4       | Bit 3 | Bit 2   | Bit 1 | Bit 0   | Value on<br>POR, BOR | Value on all other Resets |

|--------------------|-----------------------|---------------|-------|-------|-------------|-------|---------|-------|---------|----------------------|---------------------------|

| Bank               | 29 (Cont.)            |               |       |       |             |       |         |       |         |                      |                           |

| EA8h               | RD0PPS <sup>(3)</sup> | _             | _     |       | RD0PPS<5:0> |       |         |       |         | 00 0000              | uu uuuu                   |

| EA9h               | RD1PPS <sup>(3)</sup> | _             | _     |       |             | RD1PF | °S<5:0> |       |         | 00 0000              | uu uuuu                   |

| EAAh               | RD2PPS <sup>(3)</sup> | _             | _     |       | RD2PPS<5:0> |       |         |       |         | 00 0000              | uu uuuu                   |

| EABh               | RD3PPS <sup>(3)</sup> | _             | _     |       | RD3PPS<5:0> |       |         |       | 00 0000 | uu uuuu              |                           |

| EACh               | RD4PPS <sup>(3)</sup> | _             | _     |       | RD4PPS<5:0> |       |         |       | 00 0000 | uu uuuu              |                           |

| EADh               | RD5PPS <sup>(3)</sup> | _             | _     |       | RD5PPS<5:0> |       |         |       | 00 0000 | uu uuuu              |                           |

| EAEh               | RD6PPS <sup>(3)</sup> | _             | _     |       | RD6PPS<5:0> |       |         |       | 00 0000 | uu uuuu              |                           |

| EAFh               | RD7PPS <sup>(3)</sup> | _             | _     |       | RD7PPS<5:0> |       |         |       | 00 0000 | uu uuuu              |                           |

| EB0h               | RE0PPS <sup>(3)</sup> | _             | _     |       | RE0PPS<5:0> |       |         |       | 00 0000 | uu uuuu              |                           |

| EB1h               | RE1PPS <sup>(3)</sup> | _             | _     |       | RE1PPS<5:0> |       |         |       | 00 0000 | uu uuuu              |                           |

| EB2h               | RE2PPS <sup>(3)</sup> | _             | _     |       | RE2PPS<5:0> |       |         |       | 00 0000 | uu uuuu              |                           |

| EB3h<br>to<br>EEFh | —                     | Unimplemented |       |       |             |       |         |       |         | _                    | _                         |

|

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

2: Unimplemented on PIC16LF1777/8/9.

3: Unimplemented on PIC16(L)F1778.

## 7.6 Register Definitions: Interrupt Control

#### **REGISTER 7-1:** INTCON: INTERRUPT CONTROL REGISTER

| 1 = Enables a<br>0 = Disables a<br><b>PEIE:</b> Periphe                                                                      | TMR0IE<br>W = Writable I<br>x = Bit is unkn<br>'0' = Bit is clea<br>nterrupt Enable<br>Il active interru<br>all interrupts                                                                                                                                                      | own<br>ared<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TMR0IF<br>nented bit, read<br>at POR and BOI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IOCIF <sup>(1)</sup><br>bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GIE: Global Ir<br>1 = Enables a<br>0 = Disables a<br>PEIE: Periphe                                                           | x = Bit is unkn<br>'0' = Bit is clea<br>nterrupt Enable<br>Il active interru                                                                                                                                                                                                    | own<br>ared<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GIE: Global Ir<br>1 = Enables a<br>0 = Disables a<br>PEIE: Periphe                                                           | x = Bit is unkn<br>'0' = Bit is clea<br>nterrupt Enable<br>Il active interru                                                                                                                                                                                                    | own<br>ared<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GIE: Global Ir<br>1 = Enables a<br>0 = Disables a<br>PEIE: Periphe                                                           | x = Bit is unkn<br>'0' = Bit is clea<br>nterrupt Enable<br>Il active interru                                                                                                                                                                                                    | own<br>ared<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GIE: Global Ir<br>1 = Enables a<br>0 = Disables a<br>PEIE: Periphe                                                           | x = Bit is unkn<br>'0' = Bit is clea<br>nterrupt Enable<br>Il active interru                                                                                                                                                                                                    | own<br>ared<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GIE: Global Ir<br>1 = Enables a<br>0 = Disables a<br>PEIE: Periphe                                                           | '0' = Bit is clea<br>nterrupt Enable<br>Il active interru                                                                                                                                                                                                                       | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -n/n = Value a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | at POR and BOI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/Value at all o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1 = Enables a<br>0 = Disables a<br><b>PEIE:</b> Periphe                                                                      | nterrupt Enable<br>Il active interru                                                                                                                                                                                                                                            | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 = Enables a<br>0 = Disables a<br><b>PEIE:</b> Periphe                                                                      | Il active interru                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0 = Disables a                                                                                                               |                                                                                                                                                                                                                                                                                 | pts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                              |                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                              | eral Interrupt Er<br>Il active periph<br>all peripheral in                                                                                                                                                                                                                      | eral interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>TMR0IE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt |                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| INTE: INT External Interrupt Enable bit<br>1 = Enables the INT external interrupt<br>0 = Disables the INT external interrupt |                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| IOCIE: Interrupt-on-Change Enable bit<br>1 = Enables the interrupt-on-change                                                 |                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>TMR0IF:</b> Timer0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed                                        |                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |