Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 28x10b; D/A 4x5b, 4x10b                                               |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

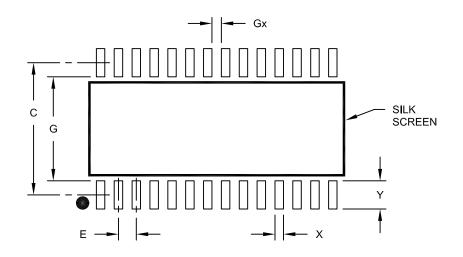

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1777-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC16(L)F1777/8/9

### 3.4 Register Definitions: Status

#### REGISTER 3-1: STATUS: STATUS REGISTER

| U-0              | U-0                                                                                          | U-0                                  | R-1/q          | R-1/q           | R/W-0/u                  | R/W-0/u           | R/W-0/u          |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------|--------------------------------------|----------------|-----------------|--------------------------|-------------------|------------------|--|--|--|--|

| _                | _                                                                                            | _                                    | TO             | PD              | Z                        | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |  |  |  |

| bit 7            | •                                                                                            |                                      |                |                 |                          |                   | bit 0            |  |  |  |  |

| Legend:          |                                                                                              |                                      |                |                 |                          |                   |                  |  |  |  |  |

| R = Readable     | bit                                                                                          | W = Writable                         | bit            | U = Unimpler    | mented bit, read         | as '0'            |                  |  |  |  |  |

| u = Bit is unch  | anged                                                                                        | x = Bit is unkr                      | nown           | -n/n = Value    | at POR and BOI           | R/Value at all o  | ther Resets      |  |  |  |  |

| '1' = Bit is set |                                                                                              | '0' = Bit is clea                    | ared           | q = Value de    | pends on conditi         | ion               |                  |  |  |  |  |

|                  |                                                                                              |                                      |                |                 |                          |                   |                  |  |  |  |  |

| bit 7-5          | Unimplemen                                                                                   | ted: Read as '                       | כ'             |                 |                          |                   |                  |  |  |  |  |

| bit 4            | TO: Time-Out                                                                                 | TO: Time-Out bit                     |                |                 |                          |                   |                  |  |  |  |  |

|                  |                                                                                              | er-up, CLRWDT                        |                | SLEEP instruc   | tion                     |                   |                  |  |  |  |  |

|                  | 0 = A WDT T                                                                                  | ime-out occurre                      | ed             |                 |                          |                   |                  |  |  |  |  |

| bit 3            | PD: Power-D                                                                                  | own bit                              |                |                 |                          |                   |                  |  |  |  |  |

|                  | 1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction |                                      |                |                 |                          |                   |                  |  |  |  |  |

|                  | •                                                                                            | tion of the SLEI                     | EP Instruction |                 |                          |                   |                  |  |  |  |  |

| bit 2            | Z: Zero bit                                                                                  |                                      |                | <i></i> .       |                          |                   |                  |  |  |  |  |

|                  |                                                                                              | t of an arithmet<br>t of an arithmet |                |                 | ero                      |                   |                  |  |  |  |  |

| bit 1            |                                                                                              |                                      | ÷ .            |                 | SUBWF instruction        | one)(1)           |                  |  |  |  |  |

| DIT I            | •                                                                                            | ut from the 4th                      |                |                 |                          | 5113)**           |                  |  |  |  |  |

|                  |                                                                                              | out from the 4th                     |                |                 | curreu                   |                   |                  |  |  |  |  |

| bit 0            | -                                                                                            | ow bit (ADDWF,                       |                |                 | ructions) <sup>(1)</sup> |                   |                  |  |  |  |  |

|                  | •                                                                                            | ut from the Mos                      |                |                 | ,                        |                   |                  |  |  |  |  |

|                  |                                                                                              | out from the Mo                      | U U            |                 |                          |                   |                  |  |  |  |  |

| Note 1: For      | Borrow the po                                                                                | larity is reverse                    | d A subtract   | ion is executed | by adding the t          | wo's compleme     | ent of the       |  |  |  |  |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand.

| TABLE 3-18: S | <b>SPECIAL FUNCTION REGISTER SUMMARY</b> |

|---------------|------------------------------------------|

|---------------|------------------------------------------|

|      |                      |                       |                      |                       |                    |                        |                     |                    |                    | Value on  | Value on all |

|------|----------------------|-----------------------|----------------------|-----------------------|--------------------|------------------------|---------------------|--------------------|--------------------|-----------|--------------|

| Addr | Name                 | Bit 7                 | Bit 6                | Bit 5                 | Bit 4              | Bit 3                  | Bit 2               | Bit 1              | Bit 0              | POR, BOR  | other Resets |

| Bank | < 0                  |                       |                      |                       |                    |                        |                     |                    |                    |           |              |

| 00Ch | PORTA                | RA7                   | RA6                  | RA5                   | RA4                | RA3                    | RA2                 | RA1                | RA0                | XXXX XXXX | uuuu uuuu    |

| 00Dh | PORTB                | RB7                   | RB6                  | RB5                   | RB4                | RB3                    | RB2                 | RB1                | RB0                | XXXX XXXX | uuuu uuuu    |

| 00Eh | PORTC                | RC7                   | RC6                  | RC5                   | RC4                | RC3                    | RC2                 | RC1                | RC0                | XXXX XXXX | uuuu uuuu    |

| 00Fh | PORTD <sup>(3)</sup> | RD7                   | RD6                  | RD5                   | RD4                | RD3                    | RD2                 | RD1                | RD0                | XXXX XXXX | uuuu uuuu    |

| 010h | PORTE                | —                     |                      |                       | _                  | RE3                    | RE2 <sup>(3)</sup>  | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup> | xxxx      | uuuu         |

| 011h | PIR1                 | TMR1GIF               | ADIF                 | RCIF                  | TXIF               | SSP1IF                 | CCP1IF              | TMR2IF             | TMR1IF             | 0000 0000 | 0000 0000    |

| 012h | PIR2                 | OSFIF                 | C2IF                 | C1IF                  | COG1IF             | BCL1IF                 | C4IF                | C3IF               | CCP2IF             | 0000 0000 | 0000 0000    |

| 013h | PIR3                 | —                     |                      | COG2IF                | ZCDIF              | CLC4IF                 | CLC3IF              | CLC2IF             | CLC1IF             | 00 0000   | 00 0000      |

| 014h | PIR4                 | —                     | TMR8IF               | TMR5GIF               | TMR5IF             | TMR3GIF                | TMR3IF              | TMR6IF             | TRM4IF             | -000 0000 | -000 0000    |

| 015h | PIR5                 | CCP8IF <sup>(3)</sup> | CCP7IF               | COG4IF <sup>(3)</sup> | COG3IF             | C8IF <sup>(3)</sup>    | C7IF <sup>(3)</sup> | C6IF               | C5IF               | 000000    | 000000       |

| 016h | PIR6                 | —                     |                      |                       | _                  | PWM12IF <sup>(3)</sup> | PWM11IF             | PWM6IF             | PWM5IF             | 0000      | 0000         |

| 017h | TMR0                 | Timer0 Module Re      | egister              |                       |                    |                        |                     |                    |                    | 0000 0000 | 0000 0000    |

| 018h | TMR1L                | Holding Register f    | or the Least Signif  | cant Byte of the 16   | 6-bit TMR1 Registe | er                     |                     |                    |                    | XXXX XXXX | uuuu uuuu    |

| 019h | TMR1H                | Holding Register f    | or the Most Signifi  | cant Byte of the 16   | -bit TMR1 Registe  | r                      |                     |                    |                    | XXXX XXXX | uuuu uuuu    |

| 01Ah | T1CON                | CS<                   | 1:0>                 | CKPS                  | 6<1:0>             | OSCEN                  | SYNC                | —                  | ON                 | 0000 00-0 | uuuu uu-u    |

| 01Bh | T1GCON               | GE                    | GPOL                 | GTM                   | GSPM               | GGO/DONE               | GVAL                | GSS                | <1:0>              | 0000 0x00 | uuuu uxuu    |

| 01Ch | TMR3L                | Holding Register f    | or the Least Signif  | cant Byte of the 16   | 5-bit TMR3 Registe | er                     |                     |                    |                    | XXXX XXXX | uuuu uuuu    |

| 01Dh | TMR3H                | Holding Register f    | or the Most Signific | cant Byte of the 16   | -bit TMR3 Registe  | r                      |                     |                    |                    | XXXX XXXX | uuuu uuuu    |

| 01Eh | T3CON                | CS<                   | 1:0>                 | CKPS                  | 6<1:0>             | OSCEN                  | SYNC                | _                  | ON                 | 0000 00-0 | uuuu uu-u    |

| 01Fh | T3GCON               | GE                    | GPOL                 | GTM                   | GSPM               | GGO/DONE               | GVAL                | GSS                | <1:0>              | 00x0 0x00 | uuuu uxuu    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

2: Unimplemented on PIC16LF1777/8/9.

**3:** Unimplemented on PIC16(L)F1778.

#### TABLE 3-18: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr              | Name           | Bit 7         | Bit 6    | Bit 5                                     | Bit 4 | Bit 3 | Bit 2 | Bit 1             | Bit 0     | Value on<br>POR, BOR | Value on all<br>other Resets |

|-------------------|----------------|---------------|----------|-------------------------------------------|-------|-------|-------|-------------------|-----------|----------------------|------------------------------|

| Bank              | 30 (Continued) |               |          |                                           |       |       |       |                   |           |                      |                              |

| F2Bh              | CLC3GLS1       | G2D4T         | G2D4N    | G2D4N G2D3T G2D3N G2D2T G2D2N G2D1T G2D1N |       |       |       |                   |           | xxxx xxxx            | uuuu uuuu                    |

| F2Ch              | CLC3GLS2       | G3D4T         | G3D4N    | G3D3T                                     | G3D3N | G3D2T | G3D2N | G3D2N G3D1T G3D1N |           |                      | uuuu uuuu                    |

| F2Dh              | CLC3GLS3       | G4D4T         | G4D4N    | G4D3T                                     | G4D3N | G4D2T | G4D2N | G4D1T             | G4D1N     | xxxx xxxx            | uuuu uuuu                    |

| F2Eh              | CLC4CON        | EN            | OE       | OUT                                       | INTP  | INTN  |       | MODE<2:0>         | 0000 0000 | 0000 0000            |                              |

| F2Fh              | CLC4POL        | POL           | —        | —                                         | —     | G4POL | G3POL | G2POL             | G1POL     | 0 xxxx               | 0 uuuu                       |

| F30h              | CLC4SEL0       |               | D1S<7:0> |                                           |       |       |       |                   |           |                      |                              |

| F31h              | CLC4SEL1       |               | D2S<7:0> |                                           |       |       |       |                   |           |                      | uuuu uuuu                    |

| F32h              | CLC4SEL2       |               |          |                                           | D3S-  | <7:0> |       |                   |           | xxxx xxxx            | uuuu uuuu                    |

| F33h              | CLC4SEL3       |               |          |                                           | D4S•  | <7:0> |       |                   |           | xxxx xxxx            | uuuu uuuu                    |

| F34h              | CLC4GLS0       | G1D4T         | G1D4N    | G1D3T                                     | G1D3N | G1D2T | G1D2N | G1D1T             | G1D1N     | xxxx xxxx            | uuuu uuuu                    |

| F35h              | CLC4GLS1       | G2D4T         | G2D4N    | G2D3T                                     | G2D3N | G2D2T | G2D2N | G2D1T             | G2D1N     | XXXX XXXX            | uuuu uuuu                    |

| F36h              | CLC4GLS2       | G3D4T         | G3D4N    | G3D3T                                     | G3D3N | G3D2T | G3D2N | G3D1T             | G3D1N     | XXXX XXXX            | uuuu uuuu                    |

| F37h              | CLC4GLS3       | G4D4T         | G4D4N    | G4D3T                                     | G4D3N | G4D2T | G4D2N | G4D1T             | G4D1N     | XXXX XXXX            | uuuu uuuu                    |

| F2Eh<br>—<br>F6Fh | _              | Unimplemented |          |                                           |       |       | -     |                   |           | _                    | _                            |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

2: Unimplemented on PIC16LF1777/8/9.

3: Unimplemented on PIC16(L)F1778.

#### REGISTER 11-17: HIDRVB: PORTB HIGH DRIVE CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|---------|---------|

| —     | —   | —   | —   | —   | —   | HIDB1   | HIDB0   |

| bit 7 |     |     |     |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-2 Unimplemented: Read as '0'

bit 1-0 HIDB<1:0>: PORTB High Drive Enable bits For RB<1:0> pins 1 = High current source and sink enabled

0 = Standard current source and sink

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELB  | —       |         | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | ANSB0   | 182                 |

| HIDRVB  | —       | _       | _       | —       | —       | —       | HIDB1   | HIDB0   | 184                 |

| INLVLB  | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 | 183                 |

| LATB    | LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   | 181                 |

| ODCONB  | ODB7    | ODB6    | ODB5    | ODB4    | ODB3    | ODB2    | ODB1    | ODB0    | 183                 |

| PORTB   | RB7     | RB6     | RB5     | RB4     | RB3     | RB2     | RB1     | RB0     | 181                 |

| SLRCONB | SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   | 183                 |

| TRISB   | TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  | 183                 |

| WPUB    | WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   | 182                 |

#### TABLE 11-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

#### REGISTER 12-3: PPSLOCK: PPS LOCK REGISTER

| U-0                                     | U-0 | U-0               | U-0  | U-0                                                   | U-0 | U-0 | R/W-0/0   |  |  |

|-----------------------------------------|-----|-------------------|------|-------------------------------------------------------|-----|-----|-----------|--|--|

| —                                       | —   | —                 | —    | —                                                     | _   | _   | PPSLOCKED |  |  |

| bit 7                                   |     |                   |      |                                                       |     |     | bit 0     |  |  |

|                                         |     |                   |      |                                                       |     |     |           |  |  |

| Legend:                                 |     |                   |      |                                                       |     |     |           |  |  |

| R = Readable                            | bit | W = Writable I    | oit  | U = Unimplemented bit, read as '0'                    |     |     |           |  |  |

| u = Bit is unchanged x = Bit is unknown |     |                   | own  | -n/n = Value at POR and BOR/Value at all other Resets |     |     |           |  |  |

| '1' = Bit is set                        |     | '0' = Bit is clea | ared |                                                       |     |     |           |  |  |

bit 7-1 Unimplemented: Read as '0'

bit 0 PPSLOCKED: PPS Locked bit

1 = PPS is locked. PPS selections can not be changed.

0 = PPS is not locked. PPS selections can be changed.

#### 14.4 **Register Definitions: FVR Control**

#### REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 | R-q/q                 | R/W-0/0             | R/W-0/0              | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----------------------|---------------------|----------------------|-------------|---------|---------|---------|

| FVREN   | FVRRDY <sup>(1)</sup> | TSEN <sup>(3)</sup> | TSRNG <sup>(3)</sup> | CDAFVR<1:0> |         | ADFVI   | R<1:0>  |

| bit 7   |                       |                     |                      |             |         |         | bit 0   |

| Legend:        |                                  |                                                                                                                                                       |                                                                                                                                                             |

|----------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R = Readal     | ole bit                          | W = Writable bit                                                                                                                                      | U = Unimplemented bit, read as '0'                                                                                                                          |

| u = Bit is ur  | nchanged                         | x = Bit is unknown                                                                                                                                    | -n/n = Value at POR and BOR/Value at all other Resets                                                                                                       |

| '1' = Bit is s | et                               | '0' = Bit is cleared                                                                                                                                  | q = Value depends on condition                                                                                                                              |

| bit 7          | 1 = Fixed                        | Fixed Voltage Reference Ena<br>I Voltage Reference is enable<br>I Voltage Reference is disable                                                        | ed                                                                                                                                                          |

| bit 6          | 1 = Fixed                        | : Fixed Voltage Reference Re<br>I Voltage Reference output is<br>I Voltage Reference output is                                                        | ready for use                                                                                                                                               |

| bit 5          | 1 = Temp                         | emperature Indicator Enable to<br>perature Indicator is enabled<br>perature Indicator is disabled                                                     | bit <sup>(3)</sup>                                                                                                                                          |

| bit 4          | 1 = VOUT                         | Temperature Indicator Range<br><sup>-</sup> = V <sub>DD</sub> - 4VT (High Range)<br><sup>-</sup> = V <sub>DD</sub> - 2VT (Low Range)                  | e Selection bit <sup>(3)</sup>                                                                                                                              |

| bit 3-2        | 11 = Com<br>10 = Com<br>01 = Com | nparator/DAC FVR Buffer Gai                                                                                                                           | in is 4x, with output VCDAFVR = 4x VFVR <sup>(2)</sup><br>in is 2x, with output VCDAFVR = 2x VFVR <sup>(2)</sup><br>in is 1x, with output VCDAFVR = 1x VFVR |

| bit 1-0        | 11 = ADC<br>10 = ADC<br>01 = ADC | 1:0>: ADC FVR Buffer Gain S<br>C FVR Buffer Gain is 4x, with<br>C FVR Buffer Gain is 2x, with<br>C FVR Buffer Gain is 1x, with<br>C FVR Buffer is off | output VADEVR = $4x VEVR^{(2)}$<br>output VADEVR = $2x VEVR^{(2)}$                                                                                          |

|                |                                  | ways '1' on PIC16F1773/6 or<br>Reference output cannot exc                                                                                            | •                                                                                                                                                           |

- **2:** Fixed Voltage Reference output cannot exceed VDD.

- 3: See Section 15.0 "Temperature Indicator Module" for additional information.

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0 | Register<br>on page |

|--------|-------|--------|-------|-------|-------------|-------|-------|-------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFVR<1:0> |       | ADFVF | <1:0> | 223                 |

Legend: Shaded cells are not used with the Fixed Voltage Reference.

# PIC16(L)F1777/8/9

#### 22.6.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 22-4. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

| <b>TABLE 22-4</b> : | TIMER1 | GATE SOURCE | S |

|---------------------|--------|-------------|---|

|---------------------|--------|-------------|---|

| T1GSS | Timer1 Gate Source                                                        |

|-------|---------------------------------------------------------------------------|

| 11    | Comparator 2 Output sync_C2OUT<br>(optionally Timer1 synchronized output) |

| 10    | Comparator 1 Output sync_C1OUT<br>(optionally Timer1 synchronized output) |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                   |

| 00    | Timer1 Gate Pin                                                           |

#### 22.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 22.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 22.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (sync\_C1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization"**.

#### 22.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 gate control. The Comparator 2 output (sync\_C2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization**".

#### 22.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 22-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | as changing the gate polarity may result in |  |  |  |  |  |

|       | indeterminate operation.                    |  |  |  |  |  |

## 22.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single-pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 22-5 for timing details.

If the Single-Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 22-6 for timing details.

#### 22.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

#### 22.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

| Mada               | MODE    | E<4:0> | Output                                         | Onenetien                                                 | Timer Control              |              |                                   |  |  |

|--------------------|---------|--------|------------------------------------------------|-----------------------------------------------------------|----------------------------|--------------|-----------------------------------|--|--|

| Mode               | <4:3>   | <2:0>  | Operation                                      | Operation                                                 | Start                      | Reset        | Stop                              |  |  |

|                    |         | 000    |                                                | Software gate (Figure 23-4)                               | <b>ON =</b> 1              | _            | ON = 0                            |  |  |

| Free<br>Running 00 |         | 001    | Period<br>Pulse                                | Hardware gate, active-high<br>(Figure 23-5)               | ON = 1 and<br>TMRx_ers = 1 | _            | ON = 0 or<br>TMRx_ers = 0         |  |  |

|                    |         | 010    | r uise                                         | Hardware gate, active-low                                 | ON = 1 and<br>TMRx_ers = 0 | _            | ON = 0 or<br>TMRx_ers = 1         |  |  |

|                    | 011     |        | Rising or falling edge Reset                   |                                                           | TMRx_ers                   |              |                                   |  |  |

| Period             | 00      | 100    | Period                                         | Rising edge Reset (Figure 23-6)                           |                            | TMRx_ers ↑   | <b>ON =</b> 0                     |  |  |

|                    |         | 101    | Pulse                                          | Falling edge Reset                                        | -                          | TMRx_ers ↓   |                                   |  |  |

|                    |         | 110    | with<br>Hardware                               | Low level Reset                                           | ON = 1                     | TMRx_ers = 0 | ON = 0 or<br>TMRx_ers = 0         |  |  |

|                    |         | 111    | Reset                                          | High level Reset (Figure 23-7)                            |                            | TMRx_ers = 1 | ON = 0 or<br>TMRx_ers = 1         |  |  |

|                    |         | 000    | One-shot                                       | Software start (Figure 23-8)                              | <b>ON =</b> 1              | _            |                                   |  |  |

|                    |         | 001    | Edge                                           | Rising edge start (Figure 23-9)                           | ON = 1 and<br>TMRx_ers ↑   | _            |                                   |  |  |

|                    |         | 010    | triggered<br>start                             | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | _            |                                   |  |  |

|                    |         | 011    | (Note 1)                                       | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _            | ON = 0<br>or                      |  |  |

| One-shot           | 01      | 100    | Edge                                           | Rising edge start and<br>Rising edge Reset (Figure 23-10) | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers ↑   | Next clock<br>after<br>TMRx = PRx |  |  |

|                    |         | 101    | triggered<br>start<br>and<br>hardware<br>Reset | Falling edge start and<br>Falling edge Reset              | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers ↓   | (Note 2)                          |  |  |

|                    |         | 110    |                                                | Rising edge start and<br>Low level Reset (Figure 23-11)   | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers = 0 |                                   |  |  |

|                    |         | 111    | (Note 1)                                       | Falling edge start and<br>High level Reset                | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers = 1 |                                   |  |  |

|                    |         | 000    |                                                | Rese                                                      | erved                      |              |                                   |  |  |

|                    |         | 001    | Edge                                           | Rising edge start<br>(Figure 23-12)                       | ON = 1 and<br>TMRx_ers ↑   | —            | ON = 0<br>or                      |  |  |

| Mono-stable        |         | 010    | triggered<br>start                             | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | —            | Next clock<br>after               |  |  |

|                    |         | 011    | (Note 1)                                       | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _            | TMRx = PRx<br>(Note 3)            |  |  |

| Reserved           | 10      | 100    |                                                | Rese                                                      | erved                      |              |                                   |  |  |

| Reserved           | /ed 101 |        |                                                | Rese                                                      | erved                      |              |                                   |  |  |

|                    |         | 110    | Level<br>triggered                             | High level start and<br>Low level Reset (Figure 23-13)    | ON = 1 and<br>TMRx_ers = 1 | TMRx_ers = 0 | ON = 0 or                         |  |  |

| One-shot           |         | 111    | start<br>and<br>hardware<br>Reset              | Low level start &<br>High level Reset                     | ON = 1 and<br>TMRx_ers = 0 | TMRx_ers = 1 | Held in Rese<br>(Note 2)          |  |  |

| Reserved           | 11      | xxx    |                                                | Rese                                                      | erved                      |              |                                   |  |  |

TABLE 23-1: TIMER2 OPERATING MODES

**Note** 1: If ON = 0 then an edge is required to restart the timer after ON = 1.

2: When TMRx = PRx then the next clock clears ON and stops TMRx at 00h.

3: When TMRx = PRx then the next clock stops TMRx at 00h but does not clear ON.

#### 23.7 PR2 Period Register

The PR2 period register (T2PR) is double-buffered. Software reads and writes the PR2 register. However, the timer uses a buffered PR2 register for operation. Software does not have direct access to the buffered PR2 register. The contents of the PR2 register are transferred to the buffer by any of the following events:

- A write to the TMR2 register

- A write to the TMR2CON register

- When TMR2 = PR2 buffer and the prescaler rolls over

- An external Reset event

#### 23.8 Timer2 Operation During Sleep

When PSYNC = 1, Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and T2PR registers will remain unchanged while processor is in Sleep mode.

When PSYNC = 0, Timer2 will operate in Sleep as long as the clock source selected is also still running. Selecting the LFINTOSC, MFINTOSC, or HFINTOSC oscillator as the timer clock source will keep the selected oscillator running during Sleep.

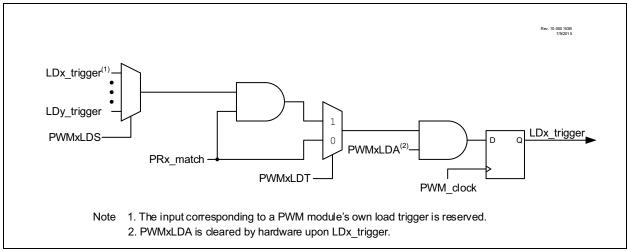

FIGURE 26-2: LOAD TRIGGER BLOCK DIAGRAM

#### 26.1 Fundamental Operation

The PWM module produces a 16-bit resolution pulse-width modulated output.

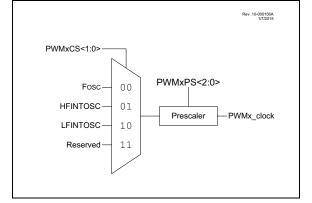

Each PWM module has an independent timer driven by a selection of clock sources determined by the PWMxCLKCON register (Register 26-4). The timer value is compared to event count registers to generate the various events of a the PWM waveform, such as the period and duty cycle. For a block diagram describing the clock sources refer to Figure 26-3.

Each PWM module can be enabled individually using the EN bit of the PWMxCON register, or several PWM modules can be enabled simultaneously using the MPWMxEN bits of the PWMEN register.

The current state of the PWM output can be read using the OUT bit of the PWMxCON register. In some modes this bit can be set and cleared by software giving additional software control over the PWM waveform. This bit is synchronized to Fosc/4 and therefore does not change in real time with respect to the PWM\_clock.

**Note:** If PWM\_clock > Fosc/4, the OUT bit may not accurately represent the output state of the PWM.

FIGURE 26-3:

PWM CLOCK SOURCE BLOCK DIAGRAM

#### 26.1.1 PWMx PIN CONFIGURATION

This device uses the PPS control circuitry to route peripherals to any device I/O pin. Select the desired pin, or pins, for PWM output with the device pin RxyPPS control registers (Register 12-2).

All PWM outputs are multiplexed with the PORT data latch, so the pins must also be configured as outputs by clearing the associated PORT TRIS bits.

The slew rate feature may be configured to optimize the rate to be used in conjunction with the PWM outputs. High-speed output switching is attained by clearing the associated PORT SLRCON bits.

The PWM outputs can be configured to be open-drain outputs by setting the associated PORT ODCON bits.

#### 26.1.2 PWMx Output Polarity

The output polarity is inverted by setting the POL bit of the PWMxCON register. The polarity control affects the PWM output even when the module is not enabled.

#### REGISTER 27-16: COGxBLKR: COG RISING EVENT BLANKING COUNT REGISTER

| U-0                                     | R/W-x/u           | R/W-x/u                                   | R/W-x/u                                               | R/W-x/u                                                                      | R/W-x/u                                                                                                                                                | R/W-x/u                                                                                                                                                                   |  |  |  |

|-----------------------------------------|-------------------|-------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                         |                   |                                           | BLKF                                                  | R<5:0>                                                                       |                                                                                                                                                        |                                                                                                                                                                           |  |  |  |

|                                         | ·                 |                                           |                                                       |                                                                              |                                                                                                                                                        | bit 0                                                                                                                                                                     |  |  |  |

|                                         |                   |                                           |                                                       |                                                                              |                                                                                                                                                        |                                                                                                                                                                           |  |  |  |

|                                         |                   |                                           |                                                       |                                                                              |                                                                                                                                                        |                                                                                                                                                                           |  |  |  |

| R = Readable bit W = Writable bit       |                   |                                           | U = Unimplemented bit, read as '0'                    |                                                                              |                                                                                                                                                        |                                                                                                                                                                           |  |  |  |

| u = Bit is unchanged x = Bit is unknown |                   |                                           | -n/n = Value at POR and BOR/Value at all other Resets |                                                                              |                                                                                                                                                        |                                                                                                                                                                           |  |  |  |

|                                         | '0' = Bit is clea | ared                                      | q = Value depends on condition                        |                                                                              |                                                                                                                                                        |                                                                                                                                                                           |  |  |  |

|                                         | bit               | bit W = Writable<br>anged x = Bit is unkr | bit W = Writable bit                                  | bit W = Writable bit U = Unimplen<br>anged x = Bit is unknown -n/n = Value a | BLKR<5:0>         bit       W = Writable bit       U = Unimplemented bit, read         anged       x = Bit is unknown       -n/n = Value at POR and BO | BLKR < 5:0 >         bit $W$ = Writable bit $U$ = Unimplemented bit, read as '0'         anged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all or |  |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 BLKR<5:0>: Rising Event Blanking Count Value bits

= Number of COGx clock periods to inhibit falling event inputs

#### REGISTER 27-17: COGxBLKF: COG FALLING EVENT BLANKING COUNT REGISTER

| U-0   | U-0 | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|-------|-----|-----------|---------|---------|---------|---------|---------|--|--|--|

|       |     | BLKF<5:0> |         |         |         |         |         |  |  |  |

| bit 7 |     |           |         |         |         |         | bit 0   |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 BLKF<5:0>: Falling Event Blanking Count Value bits

= Number of COGx clock periods to inhibit rising event inputs

#### REGISTER 27-18: COGxPHR: COG RISING EVENT PHASE DELAY COUNT REGISTER

| U-0                                                                  | U-0   | R/W-0/0         | R/W-0/0                                                       | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0     |  |  |  |  |

|----------------------------------------------------------------------|-------|-----------------|---------------------------------------------------------------|------------------------------------|---------|---------|-------------|--|--|--|--|

| —                                                                    | _     |                 | PHR<5:0>                                                      |                                    |         |         |             |  |  |  |  |

| bit 7                                                                |       |                 |                                                               |                                    |         |         | bit 0       |  |  |  |  |

|                                                                      |       |                 |                                                               |                                    |         |         |             |  |  |  |  |

| Legend:                                                              |       |                 |                                                               |                                    |         |         |             |  |  |  |  |

| R = Readable b                                                       | oit   | W = Writable I  | oit                                                           | U = Unimplemented bit, read as '0' |         |         |             |  |  |  |  |

| u = Bit is uncha                                                     | anged | x = Bit is unkn | x = Bit is unknown -n/n = Value at POR and BOR/Value at all c |                                    |         |         | ther Resets |  |  |  |  |

| '1' = Bit is set '0' = Bit is cleared q = Value depends on condition |       |                 |                                                               |                                    |         | ion     |             |  |  |  |  |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 5-0 PHR<5:0>: Rising Event Phase Delay Count Value bits

= Number of COGx clock periods to delay rising event

#### REGISTER 27-19: COGxPHF: COG FALLING EVENT PHASE DELAY COUNT REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|-------|-----|---------|----------|---------|---------|---------|---------|--|--|--|

| —     | _   |         | PHF<5:0> |         |         |         |         |  |  |  |

| bit 7 |     |         |          |         |         |         | bit 0   |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 PHF<5:0>: Falling Event Phase Delay Count Value bits

= Number of COGx clock periods to delay falling event

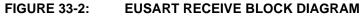

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXxSTA)

- Receive Status and Control (RCxSTA)

- Baud Rate Control (BAUDxCON)

These registers are detailed in Register 33-1, Register 33-2 and Register 33-3, respectively.

The RX and CK input pins are selected with the RXPPS and CKPPS registers, respectively. TX, CK, and DT output pins are selected with each pin's RxyPPS register. Since the RX input is coupled with the DT output in Synchronous mode, it is the user's responsibility to select the same pin for both of these functions when operating in Synchronous mode. The EUSART control logic will control the data direction drivers automatically.

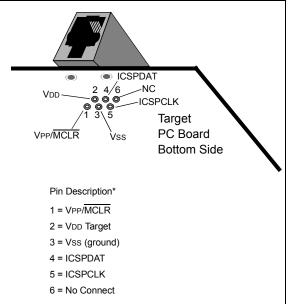

### 34.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP™ refer to the "*PIC16(L)F177X Memory Programming Specification*" (DS40001792).

#### 34.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

#### 34.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.5 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

#### 34.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 34-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 34-2.

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 34-3 for more information.

| Mnemonic,<br>Operands |      | Description                                   | Cycles |     | 14-Bit Opcode |      |      |          | Notes |

|-----------------------|------|-----------------------------------------------|--------|-----|---------------|------|------|----------|-------|

|                       |      | Description                                   | Cycles | MSb |               |      | LSb  | Affected | Notes |

|                       |      | CONTROL OPER                                  | ATIONS |     |               |      |      |          |       |

| BRA                   | k    | Relative Branch                               | 2      | 11  | 001k          | kkkk | kkkk |          |       |

| BRW                   | -    | Relative Branch with W                        | 2      | 00  | 0000          | 0000 | 1011 |          |       |

| CALL                  | k    | Call Subroutine                               | 2      | 10  | 0kkk          | kkkk | kkkk |          |       |

| CALLW                 | -    | Call Subroutine with W                        | 2      | 00  | 0000          | 0000 | 1010 |          |       |

| GOTO                  | k    | Go to address                                 | 2      | 10  | 1kkk          | kkkk | kkkk |          |       |

| RETFIE                | k    | Return from interrupt                         | 2      | 00  | 0000          | 0000 | 1001 |          |       |

| RETLW                 | k    | Return with literal in W                      | 2      | 11  | 0100          | kkkk | kkkk |          |       |

| RETURN                | -    | Return from Subroutine                        | 2      | 00  | 0000          | 0000 | 1000 |          |       |

|                       |      | INHERENT OPER                                 | ATIONS |     |               |      |      |          |       |

| CLRWDT                | _    | Clear Watchdog Timer                          | 1      | 00  | 0000          | 0110 | 0100 | TO, PD   |       |

| NOP                   | -    | No Operation                                  | 1      | 00  | 0000          | 0000 | 0000 |          |       |

| OPTION                | _    | Load OPTION_REG register with W               | 1      | 00  | 0000          | 0110 | 0010 |          |       |

| RESET                 | -    | Software device Reset                         | 1      | 00  | 0000          | 0000 | 0001 |          |       |

| SLEEP                 | -    | Go into Standby mode                          | 1      | 00  | 0000          | 0110 | 0011 | TO, PD   |       |

| TRIS                  | f    | Load TRIS register with W                     | 1      | 00  | 0000          | 0110 | Offf |          |       |

|                       |      | C-COMPILER OPT                                | IMIZED |     |               |      |      |          |       |

| ADDFSR                | n, k | Add Literal k to FSRn                         | 1      | 11  | 0001          | 0nkk | kkkk |          |       |

| MOVIW                 | n mm | Move Indirect FSRn to W with pre/post inc/dec | 1      | 00  | 0000          | 0001 | 0nmm | Z        | 2, 3  |

|                       |      | modifier, mm                                  |        |     |               |      |      |          |       |

|                       | k[n] | Move INDFn to W, Indexed Indirect.            | 1      | 11  | 1111          | 0nkk | kkkk | Z        | 2     |

| MOVWI                 | n mm | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00  | 0000          | 0001 | lnmm |          | 2, 3  |

|                       |      | modifier, mm                                  |        |     |               |      |      |          |       |

|                       | k[n] | Move W to INDFn, Indexed Indirect.            | 1      | 11  | 1111          | 1nkk | kkkk |          | 2     |

#### TABLE 35-3: INSTRUCTION SET (CONTINUED)

**Note 1:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

3: See Table in the MOVIW and MOVWI instruction descriptions.

| PIC16LF1777/8/9<br>PIC16F1777/8/9 |                        | Operating Conditions: (unless otherwise stated)<br>Low-Power Sleep Mode<br>Low-Power Sleep Mode, VREGPM = 1 |       |     |      |    |     |                                                             |  |  |

|-----------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------|-------|-----|------|----|-----|-------------------------------------------------------------|--|--|

|                                   |                        |                                                                                                             |       |     |      |    |     |                                                             |  |  |

| No.                               | Device Characteristics | e Characteristics Min. Typ† +85°C +125°C                                                                    | Units | Vdd | Note |    |     |                                                             |  |  |

| D023                              | Base IPD               |                                                                                                             | 0.05  | 1.0 | 8.0  | μA | 1.8 | DT, BOR, FVR, and SOSC                                      |  |  |

|                                   |                        | —                                                                                                           | 0.08  | 2.0 | 9.0  | μA | 3.0 | disabled, all Peripherals Inactive                          |  |  |

| D023                              | Base IPD               |                                                                                                             | 0.3   | 2.4 | 10   | μA | 2.3 | WDT, BOR, FVR, and SOSC                                     |  |  |

|                                   |                        |                                                                                                             | 0.4   | 4   | 12   | μA | 3.0 | disabled, all Peripherals Inactive,<br>Low-Power Sleep mode |  |  |

|                                   |                        | _                                                                                                           | 0.5   | 6   | 15   | μA | 5.0 | Low-Power Sleep mode                                        |  |  |

| D023A                             | Base IPD               | _                                                                                                           | 9.8   | 17  | 28   | μA | 2.3 | WDT, BOR, FVR and SOSC                                      |  |  |

|                                   |                        | _                                                                                                           | 10.3  | 20  | 40   | μA | 3.0 | disabled, all Peripherals inactive,                         |  |  |

|                                   |                        | _                                                                                                           | 11.5  | 22  | 44   | μA | 5.0 | Normal Power Sleep mode<br>VREGPM = 0                       |  |  |

| D024                              |                        | _                                                                                                           | 0.5   | 6   | 14   | μA | 1.8 | WDT Current                                                 |  |  |

|                                   |                        | —                                                                                                           | 0.8   | 7   | 17   | μA | 3.0 |                                                             |  |  |

| D024                              |                        | —                                                                                                           | 0.8   | 6   | 15   | μA | 2.3 | WDT Current                                                 |  |  |

|                                   |                        | —                                                                                                           | 0.9   | 7   | 20   | μA | 3.0 |                                                             |  |  |

|                                   |                        | _                                                                                                           | 1.0   | 8   | 22   | μA | 5.0 | ]                                                           |  |  |

| D025                              |                        | _                                                                                                           | 15    | 28  | 30   | μA | 1.8 | FVR Current (ADC)                                           |  |  |

|                                   |                        | _                                                                                                           | 24    | 35  | 38   | μA | 3.0 |                                                             |  |  |

| D025                              |                        | _                                                                                                           | 18    | 33  | 35   | μA | 2.3 | FVR Current (ADC)                                           |  |  |

|                                   |                        |                                                                                                             | 24    | 35  | 40   | μA | 3.0 | 1                                                           |  |  |

|                                   |                        |                                                                                                             | 26    | 37  | 44   | μA | 5.0 | 1                                                           |  |  |

| D025A                             |                        | _                                                                                                           | 25    | 50  | 55   | μA | 1.8 | FVR Current (DAC)                                           |  |  |

|                                   |                        |                                                                                                             | 30    | 65  | 70   | μA | 3.0 | 1                                                           |  |  |

| D025A                             |                        | _                                                                                                           | 30    | 55  | 66   | μA | 2.3 | FVR Current (DAC)                                           |  |  |

|                                   |                        |                                                                                                             | 32    | 68  | 82   | μA | 3.0 | 1                                                           |  |  |

|                                   |                        |                                                                                                             | 35    | 77  | 90   | μA | 5.0 | 1                                                           |  |  |

| D026                              |                        | _                                                                                                           | 7.5   | 25  | 28   | μA | 3.0 | BOR Current                                                 |  |  |

| D026                              |                        | _                                                                                                           | 10    | 25  | 28   | μA | 3.0 | BOR Current                                                 |  |  |

|                                   |                        |                                                                                                             | 12    | 28  | 31   | μA | 5.0 | 1                                                           |  |  |

| D027                              |                        | -                                                                                                           | 0.5   | 4   | 10   | μA | 3.0 | LPBOR Current                                               |  |  |

| D027                              |                        |                                                                                                             | 0.8   | 6   | 15   | μA | 3.0 | LPBOR Current                                               |  |  |

|                                   |                        |                                                                                                             | 1     | 8   | 17   | μA | 5.0 |                                                             |  |  |

| D028                              |                        |                                                                                                             | 0.5   | 5   | 9    | μA | 1.8 | SOSC Current                                                |  |  |

|                                   |                        |                                                                                                             | 0.8   | 8.5 | 12   | μA | 3.0 |                                                             |  |  |

| D028                              |                        | _                                                                                                           | 1.1   | 6   | 10   | μA | 2.3 | SOSC Current                                                |  |  |

|                                   |                        | _                                                                                                           | 1.3   | 8.5 | 20   | μA | 3.0 |                                                             |  |  |

|                                   |                        |                                                                                                             | 1.4   | 10  | 25   | μA | 5.0 |                                                             |  |  |

## TABLE 36-3: POWER-DOWN CURRENTS (IPD)<sup>(1,2)</sup>

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

3: ADC clock source is FRC.

| Standa       | Standard Operating Conditions (unless otherwise stated) |                                              |        |      |        |       |                                                                       |  |  |

|--------------|---------------------------------------------------------|----------------------------------------------|--------|------|--------|-------|-----------------------------------------------------------------------|--|--|

| Param<br>No. | Sym.                                                    | Sym. Characteristic                          |        | Тур† | Max.   | Units | Conditions                                                            |  |  |

|              |                                                         | Program Memory<br>Programming Specifications |        |      |        |       |                                                                       |  |  |

| D110         | Vінн                                                    | Voltage on MCLR/VPP pin                      | 8.0    | —    | 9.0    | V     | (Note 2, Note 3)                                                      |  |  |

| D111         | IDDP                                                    | Supply Current during<br>Programming         | —      | —    | 10     | mA    |                                                                       |  |  |

| D112         | VBE                                                     | VDD for Bulk Erase                           | 2.7    | _    | VDDMAX | V     |                                                                       |  |  |

| D113         | VPEW                                                    | VDD for Write or Row Erase                   | VDDMIN | _    | VDDMAX | V     |                                                                       |  |  |

| D114         | IPPPGM                                                  | Current on MCLR/VPP during<br>Erase/Write    | _      | 1.0  | _      | mA    |                                                                       |  |  |

| D115         | D115 IDDPGM Current on VDD during<br>Erase/Write        |                                              |        | 5.0  | —      | mA    |                                                                       |  |  |

|              |                                                         | Program Flash Memory                         |        |      |        |       |                                                                       |  |  |

| D121         | Ер                                                      | Cell Endurance                               | 10K    | —    | _      | E/W   | -40°C ≤ TA ≤ +85°C<br>(Note 1)                                        |  |  |

| D122         | Vprw                                                    | VDD for Read/Write                           | VDDMIN | —    | VDDMAX | V     |                                                                       |  |  |

| D123         | Tiw                                                     | Self-timed Write Cycle Time                  | —      | 2    | 2.5    | ms    |                                                                       |  |  |