Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 × 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 28x10b; D/A 4x5b, 4x10b                                               |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 40-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 40-UQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1777-i-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| DS40   |  |

|--------|--|

| 0018   |  |

| 19B-p; |  |

| age 1  |  |

| 0      |  |

TABLE 4:

#### 40-Pin (U)QFN 44-Pin QFN 44-Pin TQFP High Current 40-Pin PDIP Comparator Modulator EUSART Interrupt Pull-ups Amp Timers Basic PWM MSSP ADC VREF DAC СС ZCD PRG СCР 000 õ å RA0 AN0 C1IN0-CLCIN0<sup>(1)</sup> IOC 2 17 19 19 \_ \_ \_ \_ Υ \_ \_ \_ \_ \_ \_ \_ \_ C2IN0-C3IN0-C4IN0-C5IN0-C6IN0-C7IN0-C8IN0-C1IN1-CLCIN1(1) RA1 3 18 20 20 AN1 OPA1OUT PRG1IN0 IOC Υ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ OPA2IN1+ C2IN1-PRG2IN1 OPA2IN1-C3IN1-C4IN1-RA2 4 19 21 21 AN2 DAC1REF0-DAC10UT1 C1IN0+ IOC Υ \_ \_ \_ \_ \_ \_ \_ \_ \_ DAC2REF0-C2IN0+ DAC3REF0-C3IN0+ DAC4REF0-C4IN0+ DAC5REF0-C5IN0+ DAC6REF0-C6IN0+ DAC7REF0-C7IN0+ DAC8REF0-C8IN0+ RA3 5 20 22 22 AN3 DAC1REF0+ C1IN1+ MD1CL<sup>(1)</sup> IOC Υ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ DAC2REF0+ DAC3REF0+ DAC4REF0+ DAC5REF0+ DAC6REF0+ DAC7REF0+ DAC8REF0+ RA4 6 21 23 23 OPA1IN0+ PRG1R<sup>(1)</sup> MD1CH<sup>(1)</sup> IOC Υ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ RA5 7 22 24 24 AN4 DAC2OUT1 OPA1IN0-PRG1F<sup>(1)</sup> MD1MOD<sup>(1)</sup> SS IOC Υ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ 14 RA6 29 31 33 C6IN1+ \_ \_ IOC Υ OSC2 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ CLKOUT RA7 13 28 30 32 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ IOC Υ \_ OSC1 \_ \_ \_ \_ CLKIN CCP8<sup>(1)</sup> 33 ZCD COG1IN<sup>(1)</sup> MD4CL<sup>(1)</sup> RB0 8 8 9 AN12 C2IN1+ IOC Υ HIB0 \_ \_ \_ \_ \_ \_ \_ \_ \_ INT COG2IN<sup>(1)</sup> RB1 34 MD4CH<sup>(1)</sup> 9 9 10 AN10 OPA2OUT C1IN3-PRG2IN0 IOC Υ HIB1 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ OPA1IN1+ C2IN3-PRG1IN1 OPA1IN1-C3IN3-PRG4R<sup>(1)</sup> C4IN3-RB2 35 10 DAC3OUT1 OPA2IN0-PRG4F<sup>(1)</sup> COG3IN<sup>(1)</sup> MD4MOD<sup>(1)</sup> 10 11 AN8 \_ \_ \_ \_ \_ \_ \_ \_ IOC Υ \_ 36 RB3 11 11 12 AN9 OPA2IN0+ C1IN2-MD3CL<sup>(1)</sup> IOC \_ \_ \_ \_ \_ \_ \_ \_ \_ Υ \_ \_ C2IN2-C3IN2-RB4 37 12 14 14 AN11 \_ \_ \_ C3IN1+ \_ \_ \_ \_ MD3CH<sup>(1)</sup> \_ \_ IOC Υ \_ \_ \_ \_ Note

1: Default peripheral input. Input can be moved to any other pin with the PPS input selection register.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

40/44-PIN ALLOCATION TABLE (PIC16(L)F1777/9)

# 1.0 DEVICE OVERVIEW

The PIC16(L)F1777/8/9 are described within this data sheet. See Table 2 for available package configurations.

Figure 1-1 shows a block diagram of the PIC16(L)F1777/8/9 devices. Table 1-2 shows the pinout descriptions.

Refer to Table 1-1 for peripherals available per device.

# TABLE 1-1:DEVICE PERIPHERAL<br/>SUMMARY

| Peripheral         group         group |                                          |       |               |                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------|---------------|-----------------|

| Fixed Voltage Reference (FVR)         •         •           Zero-Cross Detection (ZCD)         •         •           Temperature Indicator         •         •           Complementary Output Generator (COG)         •         •           COG2         •         •           COG2         •         •           COG3         •         •           COG3         •         •           COG3         •         •           COG3         •         •           Programmable Ramp Generator (PRG)         •         •           PRG2         •         •           PRG3         •         •           PRG3         •         •           PRG4         •         •           10-bit Digital-to-Analog Converter (DAC)         •         •           DAC1         •         •           DAC2         •         •           DAC3         •         • <td>Peripheral</td> <td></td> <td>PIC16(L)F1778</td> <td>PIC16(L)F1777/9</td>                                                                                                                                                                 | Peripheral                               |       | PIC16(L)F1778 | PIC16(L)F1777/9 |

| Zero-Cross Detection (ZCD)         •         •           Temperature Indicator         •         •         •           Complementary Output Generator (COG)         •         •         •           COG1         •         •         •         •           COG2         •         •         •         •         •           COG3         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •                                                                                                                                                                         | Analog-to-Digital Converter (ADC)        | ٠     | ٠             |                 |

| Temperature Indicator         •         •           Complementary Output Generator (COG)         COG1         •         •           COG2         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         • <td>Fixed Voltage Reference (FVR)</td> <td></td> <td>•</td> <td>•</td>                                                                                  | Fixed Voltage Reference (FVR)            |       | •             | •               |

| Complementary Output Generator (COG)         COG1         •           COG2         •         •           COG2         •         •           COG3         •         •           COG3         •         •           COG4         •         •           Programmable Ramp Generator (PRG)         •         •           PRG1         •         •           PRG2         •         •           PRG3         •         •           PRG3         •         •           PRG4         •         •           10-bit Digital-to-Analog Converter (DAC)         •         •           DAC1         •         •           DAC2         •         •           DAC3         •         •           DAC4         •         •           DAC3         •         •           Capture/Compare/PWM (CCP/EC                                                                                                                                                                                                                                                                      | Zero-Cross Detection (ZCD)               | •     | •             |                 |

| COG1         •           COG2         •           COG3         •           COG3         •           COG3         •           COG3         •           COG4         •           Programmable Ramp Generator (PRG)         •           PRG1         •           PRG2         •           PRG3         •           PRG3         •           PRG4         •           10-bit Digital-to-Analog Converter (DAC)         •           DAC1         •           DAC2         •           DAC5         •           DAC6         •           5-bit Digital-to-Analog Converter (DAC)         •           DAC3         •           DAC4         •           DAC3         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •           CCP2         •           CCP8         •                                                                                                                                                                                                                                                                                                                  | Temperature Indicator                    |       | •             | ٠               |

| COG2         •         •           COG3         •         •           COG4         •         •           Programmable Ramp Generator (PRG)         •         •           PRG1         •         •           PRG2         •         •           PRG3         •         •           PRG3         •         •           PRG4         •         •           10-bit Digital-to-Analog Converter (DAC)         •         •           DAC1         •         •           DAC2         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           DAC3         •         •           DAC6         •         •           DAC3         •         •           DAC4         •         •           DAC3         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •         •           CCP2         •         •         •           CCP8         •                                                                                                                                                                                                                                                                | Complementary Output Generator (COG)     |       |               |                 |

| COG3         •           Programmable Ramp Generator (PRG)         •           PRG1         •           PRG2         •           PRG3         •           PRG3         •           PRG3         •           PRG4         •           10-bit Digital-to-Analog Converter (DAC)         •           DAC1         •           DAC2         •           DAC5         •           DAC6         •           5-bit Digital-to-Analog Converter (DAC)         •           DAC3         •           DAC4         •           DAC3         •           DAC4         •           DAC3         •           DAC4         •           DAC3         •           DAC4         •           DAC3         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •           CCP2         •           CCP7         •           CCP8         •                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          | COG1  | •             | ٠               |

| COG4         •           Programmable Ramp Generator (PRG)         PRG1         •           PRG2         •         •           PRG3         •         •           PRG3         •         •           PRG3         •         •           PRG4         •         •           10-bit Digital-to-Analog Converter (DAC)         •         •           DAC1         •         •           DAC2         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP2         •         •           CCP2         •         •           CCP2         •         •           CCP7         •         •           CCP8         •         •                                                                                                                                                                                                                                                                                                                     |                                          | COG2  | •             | ٠               |

| Programmable Ramp Generator (PRG)         PRG1         •           PRG2         •         •           PRG2         •         •           PRG3         •         •           PRG3         •         •           PRG4         •         •           10-bit Digital-to-Analog Converter (DAC)         •         •           DAC1         •         •           DAC2         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •           CCP2         •         •           CCP1         •         •           CCP2         •         •           CCP8         •         •                                                                                                                                                                                                                                                                                                                                              |                                          | COG3  | •             | ٠               |

| PRG1         •           PRG2         •           PRG3         •           PRG3         •           PRG4         •           10-bit Digital-to-Analog Converter (DAC)         DAC1         •           DAC2         •         •           DAC2         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           DAC6         •         •           DAC3         •         •           DAC4         •         •           DAC7         •         •           DAC3         •         •           DAC4         •         •           DAC3         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •         •           CCP2         •         • </td <td></td> <td>COG4</td> <td></td> <td>•</td>                                                                                                                                                                                                                                        |                                          | COG4  |               | •               |

| PRG1         •           PRG2         •           PRG3         •           PRG3         •           PRG4         •           10-bit Digital-to-Analog Converter (DAC)         DAC1         •           DAC2         •         •           DAC2         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           DAC6         •         •           DAC3         •         •           DAC4         •         •           DAC7         •         •           DAC3         •         •           DAC4         •         •           DAC3         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •         •           CCP2         •         • </td <td>Programmable Ramp Generator (PRG)</td> <td></td> <td></td> <td></td>                                                                                                                                                                                                            | Programmable Ramp Generator (PRG)        |       |               |                 |

| PRG3         •           PRG4         •           10-bit Digital-to-Analog Converter (DAC)         DAC1         •           DAC2         •         •           DAC2         •         •           DAC2         •         •           DAC2         •         •           DAC3         •         •           DAC4         •         •           DAC4         •         •           DAC3         •         •           DAC4         •         •           DAC4         •         •           DAC4         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP2         •         •           CCP2         •         •           CCP8         •         •           Comparators         • </td <td></td> <td>PRG1</td> <td>•</td> <td>•</td>                                                                                                                                                                                                                                               |                                          | PRG1  | •             | •               |

| PRG4         •           10-bit Digital-to-Analog Converter (DAC)         DAC1         •           DAC2         •         •           DAC2         •         •           DAC3         •         •           DAC4         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           DAC3         •         •           DAC4         •         •           DAC7         •         •           DAC7         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP2         •         •           CCP2         •         •           CCP2         •         •           CCP8         •         •           Comparators         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          | PRG2  | •             | •               |

| 10-bit Digital-to-Analog Converter (DAC)         DAC1         •           DAC2         •         •           DAC2         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           DAC3         •         •           DAC3         •         •           DAC4         •         •           DAC7         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •           CCP2         •         •           CCP7         •         •           CCP8         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                          | PRG3  | •             | •               |

| DAC1         •           DAC2         •           DAC5         •           DAC5         •           DAC6         •           5-bit Digital-to-Analog Converter (DAC)         DAC3           DAC3         •           DAC4         •           DAC7         •           DAC8         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •           CCP2         •           CCP7         •           CCP8         •           Comparators         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          |       |               | •               |

| DAC1         •           DAC2         •           DAC5         •           DAC5         •           DAC6         •           5-bit Digital-to-Analog Converter (DAC)         DAC3           DAC3         •           DAC4         •           DAC7         •           DAC8         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •           CCP2         •           CCP7         •           CCP8         •           Comparators         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10-bit Digital-to-Analog Converter (DAC) |       |               |                 |

| DAC5         •         •           DAC6         0         •         •           5-bit Digital-to-Analog Converter (DAC)         DAC3         •         •           DAC4         •         •         •           DAC4         •         •         •           DAC7         •         •         •           DAC8         •         •         •           DAC7         •         •         •           DAC8         •         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •         •           CCP1         •         •         •         •           CCP2         •         •         •         •           CCP7         •         •         •         •           CCP8         •         •         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                          | DAC1  | •             | •               |

| DAC6         •           5-bit Digital-to-Analog Converter (DAC)         DAC3         •           DAC3         •         •           DAC4         •         •           DAC7         •         •           DAC7         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •           CCP2         •         •           CCP7         •         •           CCP8         •         •           Comparators         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                          | DAC2  | •             | •               |

| DAC6         •           5-bit Digital-to-Analog Converter (DAC)         DAC3         •           DAC3         •         •           DAC4         •         •           DAC7         •         •           DAC7         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •           CCP2         •         •           CCP7         •         •           CCP8         •         •           Comparators         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                          | DAC5  | •             | •               |

| DAC3         •           DAC4         •           DAC7         •           DAC7         •           DAC8         •           DAC8         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •           CCP2         •           CCP7         •           CCP8         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          | DAC6  |               | •               |

| DAC3         •           DAC4         •           DAC7         •           DAC7         •           DAC8         •           DAC8         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •           CCP2         •           CCP7         •           CCP8         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-bit Digital-to-Analog Converter (DAC)  |       |               |                 |

| DAC7         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •           CCP2         •         •           CCP7         •         •           CCP8         •         •           Comparators         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          | DAC3  | •             | •               |

| DAC7         •         •           DAC8         •         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •         •           CCP1         •         •         •           CCP2         •         •         •           CCP7         •         •         •           CCP8         •         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                          |       | •             | •               |

| DAC8         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •         •           CCP2         •         •           CCP7         •         •           CCP8         •         •           Comparators         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          |       | •             | •               |

| Capture/Compare/PWM (CCP/ECCP) Modules         CCP1         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •                                                                                                                                                    |                                          | DAC8  |               | •               |

| CCP1         •           CCP2         •           CCP7         •           CCP8         •           Comparators         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Capture/Compare/PWM (CCP/ECCP) Mod       | dules |               |                 |

| CCP2     •       CCP7     •       CCP8     •       CCP8     •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          | 1     | •             | •               |

| CCP8 • Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          | CCP2  | •             | •               |

| Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                          | CCP7  | •             | •               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          | CCP8  |               | •               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Comparators                              |       |               | . <u> </u>      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          | C1    | •             | ٠               |

| C2 • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          | C2    | •             | ٠               |

| C3 • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          | C3    | •             | ٠               |

| C4 • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          | C4    | •             | ٠               |

| C5 • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          | C5    | •             | ٠               |

| C6 • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          |       | •             | ٠               |

| C7 •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          |       |               | ٠               |

| C8 •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          | C8    |               | ٠               |

#### TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| SUMMARY                                                               | i        |               |                 |

|-----------------------------------------------------------------------|----------|---------------|-----------------|

| Peripheral                                                            |          | PIC16(L)F1778 | PIC16(L)F1777/9 |

| Configurable Logic Cell (CLC)                                         |          |               |                 |

|                                                                       | CLC1     | •             | ٠               |

|                                                                       | CLC2     | ٠             | ٠               |

|                                                                       | CLC3     | ٠             | ٠               |

|                                                                       | CLC4     | ٠             | ٠               |

| Data Signal Modulator (DSM)                                           |          |               |                 |

|                                                                       | DSM1     | •             | ٠               |

|                                                                       | DSM2     | •             | ٠               |

|                                                                       | DSM3     | ٠             | ٠               |

|                                                                       | DSM4     |               | ٠               |

| Enhanced Universal Synchronous/Async<br>Receiver/Transmitter (EUSART) | chronous |               |                 |

|                                                                       | EUSART   | ٠             | ٠               |

| Master Synchronous Serial Ports                                       |          |               |                 |

|                                                                       | MSSP     | •             | ٠               |

| Op Amps                                                               |          |               |                 |

|                                                                       | OPA1     | ٠             | ٠               |

|                                                                       | OPA2     | •             | ٠               |

|                                                                       | OPA3     | •             | ٠               |

|                                                                       | OPA4     |               | ٠               |

| 10-bit Pulse-Width Modulator (PWM)                                    | •        |               |                 |

|                                                                       | PWM3     | •             | ٠               |

|                                                                       | PWM4     | ٠             | •               |

|                                                                       | PWM9     | ٠             | ٠               |

|                                                                       | PWM10    |               | ٠               |

| 16-bit Pulse-Width Modulator (PWM)                                    |          |               |                 |

|                                                                       | PWM5     | ٠             | ٠               |

|                                                                       | PWM6     | ٠             | ٠               |

|                                                                       | PWM11    | ٠             | ٠               |

|                                                                       | PWM12    |               | ٠               |

| 8-bit Timers                                                          |          |               |                 |

|                                                                       | Timer0   | ٠             | ٠               |

|                                                                       | Timer2   | •             | ٠               |

|                                                                       | Timer4   | ٠             | ٠               |

|                                                                       | Timer6   | •             | ٠               |

|                                                                       | Timer8   | ٠             | ٠               |

| 16-bit Timers                                                         |          |               |                 |

|                                                                       | Timer1   | ٠             | ٠               |

|                                                                       | Timer3   | ٠             | ٠               |

|                                                                       | Timer5   | ٠             | ٠               |

# TABLE 3-18: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr | Name                  | Bit 7                                | Bit 6                                | Bit 5       | Bit 4  | Bit 3     | Bit 2   | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all<br>other Resets |

|------|-----------------------|--------------------------------------|--------------------------------------|-------------|--------|-----------|---------|-----------|-----------|----------------------|------------------------------|

| Bank | <b>(</b> 5            |                                      |                                      |             |        |           |         |           |           |                      |                              |

| 28Ch | ODCONA                | ODA7                                 | ODA6                                 | ODA5        | ODA4   | ODA3      | ODA2    | ODA1      | ODA0      | 0000 0000            | 0000 0000                    |

| 28Dh | ODCONB                | ODB7                                 | ODB6                                 | ODB5        | ODB4   | ODB3      | ODB2    | ODB1      | ODB0      | 0000 0000            | 0000 0000                    |

| 28Eh | ODCONC                | ODC7                                 | ODC6                                 | ODC5        | ODC4   | ODC3      | ODC2    | ODC1      | ODC0      | 0000 0000            | 0000 0000                    |

| 28Fh | ODCOND <sup>(3)</sup> | ODD7                                 | ODD6                                 | ODD5        | ODD4   | ODD3      | ODD2    | ODD1      | ODD0      | 0000 0000            | 0000 0000                    |

| 290h | ODCONE <sup>(3)</sup> | _                                    | -                                    | —           | _      | _         | ODE2    | ODE1      | ODE0      | 000                  | 000                          |

| 291h | CCPR1L                | Capture/Compare                      | /PWM Register 1 (                    | LSB)        |        |           |         |           |           | XXXX XXXX            | uuuu uuuu                    |

| 292h | CCPR1H                | Capture/Compare                      | /PWM Register 1 (                    | MSB)        |        |           |         |           |           | XXXX XXXX            | uuuu uuuu                    |

| 293h | CCP1CON               | EN                                   | -                                    | OUT         | FMT    |           | MOD     | E<3:0>    |           | 0-00 0000            | 0-00 0000                    |

| 294h | CCP1CAP               | _                                    | _                                    | _           | _      | CTS<3:0>  |         |           | 0000      | 0000                 |                              |

| 295h | CCPR2L                | Capture/Compare                      | Capture/Compare/PWM Register 2 (LSB) |             |        |           |         |           |           | xxxx xxxx            | uuuu uuuu                    |

| 296h | CCPR2H                | Capture/Compare                      | Capture/Compare/PWM Register 2 (MSB) |             |        |           |         |           |           | xxxx xxxx            | uuuu uuuu                    |

| 297h | CCP2CON               | EN                                   | _                                    | OUT         | FMT    |           | MOD     | E<3:0>    |           | 0-00 0000            | 0-00 0000                    |

| 298h | CCP2CAP               | _                                    | _                                    | _           | _      |           | CTS     | <3:0>     |           | 0000                 | 0000                         |

| 299h | CCPR7L                | Capture/Compare                      | Capture/Compare/PWM Register 7 (LSB) |             |        |           |         |           | xxxx xxxx | uuuu uuuu            |                              |

| 29Ah | CCPR7H                | Capture/Compare/PWM Register 7 (MSB) |                                      |             |        |           |         | xxxx xxxx | uuuu uuuu |                      |                              |

| 29Bh | CCP7CON               | EN                                   | _                                    | OUT         | FMT    | MODE<3:0> |         |           | 0-00 0000 | 0-00 0000            |                              |

| 29Ch | CCP7CAP               | _                                    | _                                    | _           | _      | CTS<3:0>  |         |           | 0000      | 0000                 |                              |

| 29Dh | —                     | Unimplemented                        | Unimplemented                        |             |        |           |         | —         | _         |                      |                              |

| 29Eh | CCPTMRS1              | C8TSEL                               | .<1:0> <sup>(3)</sup>                | C7TSEL<1:0> |        | C2TSE     | :L<1:0> | C1TSI     | EL<1:0>   | 00 0000              | 00 0000                      |

| 29Fh | CCPTMRS2              | P10TSE                               | _<1:0> <sup>(3)</sup>                | P9TSE       | L<1:0> | P4TSE     | L<1:0>  | P3TSI     | EL<1:0>   | 00 0000              | 00 0000                      |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Unimplemented, read as '1'.

Note 1: 2:

Unimplemented on PIC16LF1777/8/9.

3: Unimplemented on PIC16(L)F1778.

# 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

#### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register select the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by the value of the FOSC<2:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the secondary oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bits of the OSCCON register. The user can monitor the OSTS bit of the OSCSTAT register to determine the current system clock source.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-1.

#### 5.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the secondary oscillator.

#### 5.3.3 SECONDARY OSCILLATOR

The secondary oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the SOSCO and SOSCI device pins.

The secondary oscillator is enabled using the OSCEN control bit in the T1CON register. See **Section 22.0 "Timer1/3/5 Module with Gate Control"** for more information about the Timer1 peripheral.

#### 5.3.4 SECONDARY OSCILLATOR READY (SOSCR) BIT

The user must ensure that the secondary oscillator is ready to be used before it is selected as a system clock source. The Secondary Oscillator Ready (SOSCR) bit of the OSCSTAT register indicates whether the secondary oscillator is ready to be used. After the SOSCR bit is set, the SCS bits can be configured to select the secondary oscillator.

#### 5.3.5 CLOCK SWITCH BEFORE SLEEP

When a clock switch from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the sleep instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PLLR is cleared the switch from 32 MHz operation to the selected internal clock is complete.

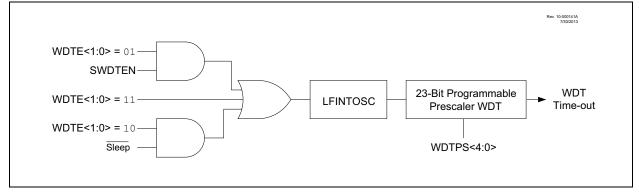

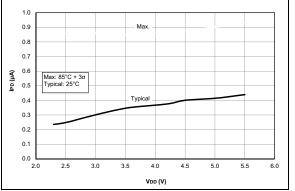

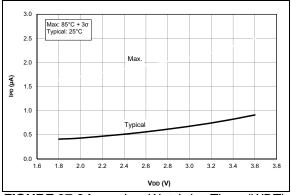

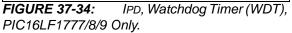

# 9.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- · Independent clock source

- Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Multiple Reset conditions

- Operation during Sleep

#### FIGURE 9-1: WATCHDOG TIMER BLOCK DIAGRAM

| U-0   | U-0 | U-0 | U-0 | R/W/HS-0/0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|------------|-----|-----|-------|

| —     | —   | —   | _   | IOCEF3     | —   | —   | —     |

| bit 7 |     |     |     |            |     |     | bit 0 |

|       |     |     |     |            |     |     |       |

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-4 Unimplemented: Read as '0'

Lanandi

bit 3 IOCEF3: Interrupt-on-Change PORTE Flag bits

1 = An enabled change was detected on the associated pin.

Set when IOCEPx = 1 and a rising edge was detected on REx, or when IOCENx = 1 and a falling edge was detected on REx.

0 = No change was detected, or the user cleared the detected change.

bit 2-0 Unimplemented: Read as '0'

#### TABLE 13-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|-----------------------|-----------------------|-----------------------|---------------------|

| ANSELA | —      | —      | ANSA5  | ANSA4  | ANSA3  | ANSA2                 | ANSA1                 | ANSA0                 | 177                 |

| ANSELB | —      | —      | ANSB5  | ANSB4  | ANSB3  | ANSB2                 | ANSB1                 | ANSB0                 | 182                 |

| ANSELC | ANSC7  | ANSC6  | ANSC5  | ANSC4  | ANSC3  | ANSC2                 | —                     | —                     | 187                 |

| INTCON | GIE    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF                | INTF                  | IOCIF                 | 132                 |

| IOCAF  | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3 | IOCAF2                | IOCAF1                | IOCAF0                | 216                 |

| IOCAN  | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3 | IOCAN2                | IOCAN1                | IOCAN0                | 215                 |

| IOCAP  | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3 | IOCAP2                | IOCAP1                | IOCAP0                | 215                 |

| IOCBF  | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3 | IOCBF2                | IOCBF1                | IOCBF0                | 217                 |

| IOCBN  | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3 | IOCBN2                | IOCBN1                | IOCBN0                | 216                 |

| IOCBP  | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3 | IOCBP2                | IOCBP1                | IOCBP0                | 216                 |

| IOCCF  | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3 | IOCCF2                | IOCCF1                | IOCCF0                | 218                 |

| IOCCN  | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3 | IOCCN2                | IOCCN1                | IOCCN0                | 218                 |

| IOCCP  | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3 | IOCCP2                | IOCCP1                | IOCCP0                | 218                 |

| IOCEP  | _      | _      | _      | _      | IOCEP3 | —                     | _                     | _                     | 219                 |

| IOCEN  | _      | _      | _      | _      | IOCEN3 | _                     | _                     | _                     | 219                 |

| IOCEF  | _      | —      | _      | _      | IOCEF3 | _                     | —                     | _                     | 220                 |

| TRISA  | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2                | TRISA1                | TRISA0                | 176                 |

| TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2                | TRISB1                | TRISB0                | 181                 |

| TRISC  | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2                | TRISC1                | TRISC0                | 186                 |

| TRISE  |        | —      | _      | —      | _(1)   | TRISE2 <sup>(2)</sup> | TRISE1 <sup>(2)</sup> | TRISE0 <sup>(2)</sup> | 199                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

Note 1: Unimplemented, read as '1'.

2: Unimplemented on PIC16(L)F1778.

# **16.1 ADC Configuration**

When configuring and using the ADC the following functions must be considered:

- Port configuration

- · Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- · Interrupt control

- Result formatting

#### 16.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 11.0 "I/O Ports"** for more information.

| Note: | Analog voltages on any pin that is defined |

|-------|--------------------------------------------|

|       | as a digital input may cause the input     |

|       | buffer to conduct excess current.          |

#### 16.1.2 CHANNEL SELECTION

There are up to 27 channel selections available:

- AN<4:0> pins (PIC16(L)F1778 only)

- AN<11:8> pins (PIC16(L)F1778 only)

- AN<27:0> pins (PIC16(L)F1777/9 only)

- Temperature Indicator

- DAC1\_output and DAC3\_output

- DAC2\_output and DAC4\_output (PIC16(L)F1777/9 only)

- FVR\_buffer1

The CHS bits of the ADCON0 register (Register 16-1) determine which channel is connected to the sample and hold circuit.