#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 28x10b; D/A 4x5b, 4x10b                                                |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

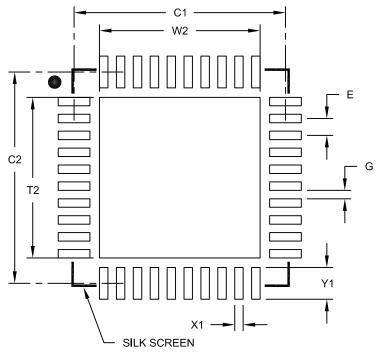

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1777t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-3: PIC16(L)F1777/9 PINOUT DESCRIPTION

| Name                                                 | Function              | Input<br>Type | Output<br>Type | Description                                  |

|------------------------------------------------------|-----------------------|---------------|----------------|----------------------------------------------|

| RA0/AN0/C1IN0-/C2IN0-/                               | RA0                   | TTL/ST        | CMOS           | General purpose I/O.                         |

| C3IN0-/C4IN0-/C5IN0-/<br>C6IN0-/C7IN0-/C8IN0-/CLCIN0 | AN0                   | AN            |                | ADC Channel 0 input.                         |

|                                                      | C1IN0-                | AN            | _              | Comparator 1 negative input.                 |

|                                                      | C2IN0-                | AN            | _              | Comparator 2 negative input.                 |

|                                                      | C3IN0-                | AN            | _              | Comparator 3 negative input.                 |

|                                                      | C4IN0-                | AN            |                | Comparator 4 negative input.                 |

|                                                      | C5IN0-                | AN            |                | Comparator 5 negative input.                 |

|                                                      | C6IN0-                | AN            |                | Comparator 6 negative input.                 |

|                                                      | C7IN0-                | AN            |                | Comparator 7 negative input.                 |

|                                                      | C8IN0-                | AN            | _              | Comparator 8 negative input.                 |

|                                                      | CLCIN0 <sup>(1)</sup> | TTL/ST        |                | CLC input 0.                                 |

| RA1/AN1/C1IN1-/C2IN1-/                               | RA1                   | TTL/ST        | CMOS           | General purpose I/O.                         |

| C3IN1-/C4IN1-/PRG1IN0/<br>PRG2IN1/OPA1OUT/OPA2IN1+/  | AN1                   | AN            |                | Channel 1 input.                             |

| OPA2IN1/OPA1001/OPA2IN1+/                            | C1IN1-                | AN            |                | Comparator 1 negative input.                 |

|                                                      | C2IN1-                | AN            | _              | Comparator 2 negative input.                 |

|                                                      | C3IN1-                | AN            |                | Comparator 3 negative input.                 |

|                                                      | C4IN1-                | AN            |                | Comparator 4 negative input.                 |

|                                                      | PRG1IN0               | AN            | _              | Ramp generator 1 reference voltage input.    |

|                                                      | PRG2IN1               | AN            | _              | Ramp generator 2 reference voltage input.    |

|                                                      | OPA10UT               | —             | AN             | Operational amplifier 1 output.              |

|                                                      | OPA2IN1+              | AN            |                | Operational amplifier 2 non-inverting input. |

|                                                      | OPA2IN1-              | AN            |                | Operational amplifier 2 inverting input.     |

|                                                      | CLCIN1 <sup>(1)</sup> | TTL/ST        |                | CLC input 0.                                 |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HP = High Power XTAL = Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

**3:** These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

| Name                     | Function              | Input<br>Type | Output<br>Type | Description                                  |

|--------------------------|-----------------------|---------------|----------------|----------------------------------------------|

| RB2/AN8/OPA2IN0-/        | RB2                   | TTL/ST        | CMOS           | General purpose I/O.                         |

| DAC3OUT1/PRG4F/COG3IN/   | AN8                   | AN            |                | ADC Channel 8 input.                         |

| MD4MOD                   | OPA2IN0-              | AN            | _              | Operational amplifier 2 inverting input.     |

|                          | DAC3OUT1              | —             | AN             | DAC3 voltage output.                         |

|                          | PRG4F <sup>(1)</sup>  | TTL/ST        |                | Ramp generator set_falling input.            |

|                          | COG3IN <sup>(1)</sup> | TTL/ST        | _              | Complementary output generator 3 input.      |

|                          | MD4MOD <sup>(1)</sup> | TTL/ST        | _              | Data signal modulator modulation input.      |

| RB3/AN9/C1IN2-/C2IN2-/   | RB3                   | TTL/ST        | CMOS           | General purpose I/O.                         |

| C3IN2-/OPA2IN0+/MD3CL    | AN9                   | AN            | _              | ADC Channel 9 input.                         |

|                          | C1IN2-                | AN            | _              | Comparator 1 negative input.                 |

|                          | C2IN2-                | AN            | _              | Comparator 2 negative input.                 |

|                          | C3IN2-                | AN            | _              | Comparator 3 negative input.                 |

|                          | OPA2IN0+              | AN            |                | Operational amplifier 2 non-inverting input. |

|                          | MD3CL <sup>(1)</sup>  | TTL/ST        | _              | Data signal modulator 3 low carrier input.   |

| RB4/AN11/C3IN1+/MD3CH    | RB4                   | TTL/ST        | CMOS           | General purpose I/O.                         |

|                          | AN11                  | AN            | _              | ADC Channel 11 input.                        |

|                          | C3IN1+                | AN            | _              | Comparator 3 positive input.                 |

|                          | MD3CH <sup>(1)</sup>  | TTL/ST        | _              | Data signal modulator 3 high carrier input.  |

| RB5/AN13/DAC5REF1-/      | RB5                   | TTL/ST        | CMOS           | General purpose I/O.                         |

| DAC7REF1-/C4IN2-/CCP7/   | AN13                  | AN            | _              | ADC Channel 11 input.                        |

| MD3MOD                   | DAC5REF1-             | AN            | _              | DAC5 negative reference.                     |

|                          | DAC7REF1-             | AN            | _              | DAC7 negative reference.                     |

|                          | C4IN2-                | AN            | _              | Comparator 4 negative input.                 |

|                          | CCP7 <sup>(1)</sup>   | TTL/ST        | _              | CCP7 capture input.                          |

|                          | MD3MOD <sup>(1)</sup> | TTL/ST        | _              | Data signal modulator modulation input.      |

| RB6/DAC5REF1+/DAC7REF1+/ | RB6                   | TTL/ST        | CMOS           | General purpose I/O.                         |

| C4IN1+/CLCIN2/ICSPCLK    | DAC5REF1+             | AN            | _              | DAC5 positive reference.                     |

|                          | DAC7REF1+             | AN            | —              | DAC7 positive reference.                     |

|                          | C4IN1+                | AN            | _              | Comparator 2 positive input.                 |

|                          | CLCIN2 <sup>(1)</sup> | TTL/ST        |                | CLC input 2.                                 |

|                          | ICSPCLK               | ST            | _              | Serial Programming Clock.                    |

TABLE 1-3: PIC16(L)F1777/9 PINOUT DESCRIPTION (CONTINUED)

Legend:AN = Analog input or outputCMOS = CMOS compatible input or outputOD= Open-DrainTTL = TTL compatible inputST= Schmitt Trigger input with CMOS levelsI<sup>2</sup>C= Schmitt Trigger input with I<sup>2</sup>CHP = High PowerXTAL= Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

# 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

Note 1: The method to access Flash memory through the PMCON registers is described in Section 10.0 "Flash Program Memory Control".

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

## TABLE 3-1: DEVICE SIZES AND ADDRESSES

## 3.1 **Program Memory Organization**

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1777/8/9 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figures 3-1 and 3-2).

## 3.2 High-Endurance Flash

This device has a 128-byte section of high-endurance program Flash memory (PFM) in lieu of data EEPROM. This area is especially well suited for nonvolatile data storage that is expected to be updated frequently over the life of the end product. See Section 10.2 "Flash **Program Memory Overview**" for more information on writing data to PFM. See Section 3.2.1.2 "Indirect **Read with FSR**" for more information about using the FSR registers to read byte data stored in PFM.

| Device          | Program Memory Space<br>(Words) | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address Range <sup>(1)</sup> |  |

|-----------------|---------------------------------|--------------------------------|-------------------------------------------------------------|--|

| PIC16(L)F1777   | 8,192                           | 1FFFh                          | 1F80h-1FFFh                                                 |  |

| PIC16(L)F1778/9 | 16,384                          | 3FFFh                          | 3F80h-3FFFh                                                 |  |

**Note 1:** High-endurance Flash applies to the low byte of each address in the range.

# 7.6 Register Definitions: Interrupt Control

#### **REGISTER 7-1:** INTCON: INTERRUPT CONTROL REGISTER

| 1 = Enables a<br>0 = Disables a<br><b>PEIE:</b> Periphe                                                                                                      | TMR0IE<br>W = Writable I<br>x = Bit is unkn<br>'0' = Bit is clea<br>nterrupt Enable<br>Il active interru<br>all interrupts                                                                                                                                                      | own<br>ared<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TMR0IF<br>nented bit, read<br>at POR and BOI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IOCIF <sup>(1)</sup><br>bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GIE: Global Ir<br>1 = Enables a<br>0 = Disables a<br>PEIE: Periphe                                                                                           | x = Bit is unkn<br>'0' = Bit is clea<br>nterrupt Enable<br>Il active interru                                                                                                                                                                                                    | own<br>ared<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GIE: Global Ir<br>1 = Enables a<br>0 = Disables a<br>PEIE: Periphe                                                                                           | x = Bit is unkn<br>'0' = Bit is clea<br>nterrupt Enable<br>Il active interru                                                                                                                                                                                                    | own<br>ared<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GIE: Global Ir<br>1 = Enables a<br>0 = Disables a<br>PEIE: Periphe                                                                                           | x = Bit is unkn<br>'0' = Bit is clea<br>nterrupt Enable<br>Il active interru                                                                                                                                                                                                    | own<br>ared<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GIE: Global Ir<br>1 = Enables a<br>0 = Disables a<br>PEIE: Periphe                                                                                           | x = Bit is unkn<br>'0' = Bit is clea<br>nterrupt Enable<br>Il active interru                                                                                                                                                                                                    | own<br>ared<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GIE: Global Ir<br>1 = Enables a<br>0 = Disables a<br>PEIE: Periphe                                                                                           | '0' = Bit is clea<br>nterrupt Enable<br>Il active interru                                                                                                                                                                                                                       | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -n/n = Value a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | at POR and BOI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/Value at all o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1 = Enables a<br>0 = Disables a<br><b>PEIE:</b> Periphe                                                                                                      | nterrupt Enable<br>Il active interru                                                                                                                                                                                                                                            | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 = Enables a<br>0 = Disables a<br><b>PEIE:</b> Periphe                                                                                                      | Il active interru                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0 = Disables a                                                                                                                                               |                                                                                                                                                                                                                                                                                 | pts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                              | eral Interrupt Er<br>Il active periph<br>all peripheral in                                                                                                                                                                                                                      | eral interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 = Enables th                                                                                                                                               | er0 Overflow In<br>ne Timer0 inter<br>he Timer0 inter                                                                                                                                                                                                                           | rupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>INTE: INT External Interrupt Enable bit</li> <li>1 = Enables the INT external interrupt</li> <li>0 = Disables the INT external interrupt</li> </ul> |                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 3 <b>IOCIE:</b> Interrupt-on-Change Enable bit<br>1 = Enables the interrupt-on-change<br>0 = Disables the interrupt-on-change                            |                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <pre>it 2 TMR0IF: Timer0 Overflow Interrupt Flag bit 1 = TMR0 register has overflowed 0 = TMR0 register did not overflow</pre>                               |                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |