Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 28x10b; D/A 4x5b, 4x10b                                               |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1779-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| DS40   |  |

|--------|--|

| 0018   |  |

| 19B-p; |  |

| age 1  |  |

| 0      |  |

TABLE 4:

#### 40-Pin (U)QFN 44-Pin QFN 44-Pin TQFP High Current 40-Pin PDIP Comparator Modulator EUSART Interrupt Pull-ups Amp Timers Basic PWM MSSP ADC VREF DAC СС ZCD PRG СCР 000 õ å RA0 AN0 C1IN0-CLCIN0<sup>(1)</sup> IOC 2 17 19 19 \_ \_ \_ \_ Υ \_ \_ \_ \_ \_ \_ \_ \_ C2IN0-C3IN0-C4IN0-C5IN0-C6IN0-C7IN0-C8IN0-C1IN1-CLCIN1(1) RA1 3 18 20 20 AN1 OPA1OUT PRG1IN0 IOC Υ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ OPA2IN1+ C2IN1-PRG2IN1 OPA2IN1-C3IN1-C4IN1-RA2 4 19 21 21 AN2 DAC1REF0-DAC10UT1 C1IN0+ IOC Υ \_ \_ \_ \_ \_ \_ \_ \_ \_ DAC2REF0-C2IN0+ DAC3REF0-C3IN0+ DAC4REF0-C4IN0+ DAC5REF0-C5IN0+ DAC6REF0-C6IN0+ DAC7REF0-C7IN0+ DAC8REF0-C8IN0+ RA3 5 20 22 22 AN3 DAC1REF0+ C1IN1+ MD1CL<sup>(1)</sup> IOC Υ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ DAC2REF0+ DAC3REF0+ DAC4REF0+ DAC5REF0+ DAC6REF0+ DAC7REF0+ DAC8REF0+ RA4 6 21 23 23 OPA1IN0+ PRG1R<sup>(1)</sup> MD1CH<sup>(1)</sup> IOC Υ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ RA5 7 22 24 24 AN4 DAC2OUT1 OPA1IN0-PRG1F<sup>(1)</sup> MD1MOD<sup>(1)</sup> SS IOC Υ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ 14 RA6 29 31 33 C6IN1+ \_ \_ IOC Υ OSC2 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ CLKOUT RA7 13 28 30 32 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ IOC Υ \_ OSC1 \_ \_ \_ \_ CLKIN CCP8<sup>(1)</sup> 33 ZCD COG1IN<sup>(1)</sup> MD4CL<sup>(1)</sup> RB0 8 8 9 AN12 C2IN1+ IOC Υ HIB0 \_ \_ \_ \_ \_ \_ \_ \_ \_ INT COG2IN<sup>(1)</sup> RB1 34 MD4CH<sup>(1)</sup> 9 9 10 AN10 OPA2OUT C1IN3-PRG2IN0 IOC Υ HIB1 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ OPA1IN1+ C2IN3-PRG1IN1 OPA1IN1-C3IN3-PRG4R<sup>(1)</sup> C4IN3-RB2 35 10 DAC3OUT1 OPA2IN0-PRG4F<sup>(1)</sup> COG3IN<sup>(1)</sup> MD4MOD<sup>(1)</sup> 10 11 AN8 \_ \_ \_ \_ \_ \_ \_ \_ IOC Υ \_ 36 RB3 11 11 12 AN9 OPA2IN0+ C1IN2-MD3CL<sup>(1)</sup> IOC \_ \_ \_ \_ \_ \_ \_ \_ \_ Υ \_ \_ C2IN2-C3IN2-RB4 37 12 14 14 AN11 \_ \_ \_ C3IN1+ \_ \_ \_ \_ MD3CH<sup>(1)</sup> \_ \_ IOC Υ \_ \_ \_ \_ Note

1: Default peripheral input. Input can be moved to any other pin with the PPS input selection register.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

40/44-PIN ALLOCATION TABLE (PIC16(L)F1777/9)

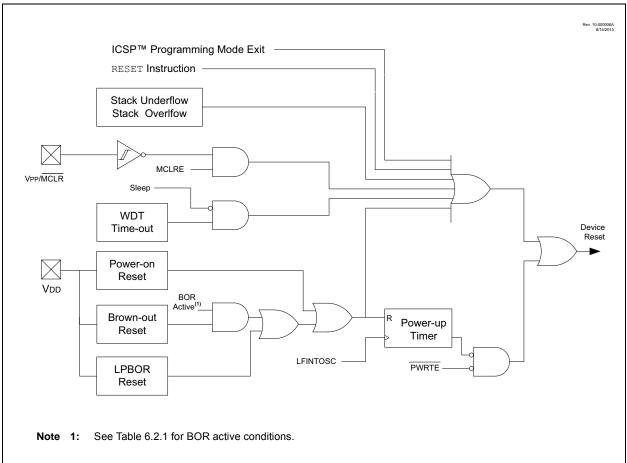

A simplified block diagram of the On-Chip Reset Circuit

is shown in Figure 6-1.

# 6.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Low-Power Brown-out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- · Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

# FIGURE 6-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| R/W-0/0                              | R/W-0/0                                                        | R/W-0/0                           | R/W-0/0                     | R/W-0/0             | R/W-0/0                           | R/W-0/0          | R/W-0/0     |

|--------------------------------------|----------------------------------------------------------------|-----------------------------------|-----------------------------|---------------------|-----------------------------------|------------------|-------------|

| CCP8IE <sup>(1)</sup>                | CCP7IE                                                         | COG4IE                            | COG3IE                      | C8IE <sup>(1)</sup> | C7IE <sup>(1)</sup>               | C6IE             | C5IE        |

| bit 7                                |                                                                |                                   |                             |                     |                                   |                  | bit 0       |

|                                      |                                                                |                                   |                             |                     |                                   |                  |             |

| Legend:<br>R = Readable t            | .:+                                                            | W = Writable                      | hit.                        |                     | nantad hit raad                   |                  |             |

|                                      |                                                                | x = Bit is unkr                   |                             |                     | nented bit, read<br>at POR and BO |                  | ther Beeste |

| u = Bit is uncha<br>'1' = Bit is set | ingeu                                                          | x = Bit is unki'0' = Bit is clear |                             |                     | at FOR and BO                     | R/Value at all 0 | Inel Resels |

| I = BILIS SEL                        |                                                                |                                   | areu                        |                     |                                   |                  |             |

| bit 7                                | CCP8IF: CC                                                     | P8 Interrupt En                   | able bit(1)                 |                     |                                   |                  |             |

|                                      |                                                                | the CCP8 inter                    |                             |                     |                                   |                  |             |

|                                      |                                                                | the CCP8 inter                    |                             |                     |                                   |                  |             |

| bit 6                                | CCP7IE: CC                                                     | P7 Interrupt En                   | able bit                    |                     |                                   |                  |             |

|                                      |                                                                | the CCP7 inter                    |                             |                     |                                   |                  |             |

|                                      |                                                                | the CCP7 inter                    | •                           |                     |                                   |                  |             |

| bit 5                                |                                                                | G4 Auto-Shutd                     | •                           | Enable bit          |                                   |                  |             |

|                                      |                                                                | nterrupt enabled                  |                             |                     |                                   |                  |             |

| hit 1                                |                                                                | •                                 |                             | Enchla bit          |                                   |                  |             |

| bit 4                                |                                                                | G3 Auto-Shutd<br>nterrupt enabled | •                           |                     |                                   |                  |             |

|                                      |                                                                | nterrupt disabled                 |                             |                     |                                   |                  |             |

| bit 3                                | <b>C8IE:</b> Comparator C8 Interrupt Enable bit <sup>(1)</sup> |                                   |                             |                     |                                   |                  |             |

|                                      |                                                                | the Comparato                     |                             |                     |                                   |                  |             |

|                                      |                                                                | the Comparate                     |                             |                     |                                   |                  |             |

| bit 2                                | C7IE: Compa                                                    | arator C7 Interru                 | upt Enable bit <sup>(</sup> | 1)                  |                                   |                  |             |

|                                      |                                                                | the Comparato                     |                             |                     |                                   |                  |             |

|                                      |                                                                | the Comparato                     |                             |                     |                                   |                  |             |

| bit 1                                | •                                                              | arator C6 Interru                 | •                           |                     |                                   |                  |             |

|                                      |                                                                | the Comparato<br>the Comparato    |                             |                     |                                   |                  |             |

| bit 0                                |                                                                | arator C5 Interru                 |                             |                     |                                   |                  |             |

| *                                    | •                                                              | the Comparato                     |                             |                     |                                   |                  |             |

|                                      |                                                                | the Comparato                     |                             |                     |                                   |                  |             |

|                                      |                                                                |                                   |                             |                     |                                   |                  |             |

# REGISTER 7-6: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

# 11.5 PORTC Registers

## 11.5.1 DATA REGISTER

PORTC is an 8-bit wide bidirectional port in the PIC16(L)F1777/8/9 devices. The corresponding data direction register is TRISC (Register 11-19). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 11-18) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

# 11.5.2 DIRECTION CONTROL

The TRISC register (Register 11-19) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

# 11.5.3 INPUT THRESHOLD CONTROL

The INLVLC register (Register 11-25) controls the input voltage threshold for each of the available PORTC input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTC register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 36-4: I/O Ports for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

# 11.5.4 OPEN-DRAIN CONTROL

The ODCONC register (Register 11-23) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONC bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONC bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

# 11.5.5 SLEW RATE CONTROL

The SLRCONC register (Register 11-24) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONC bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONC bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

# 11.5.6 ANALOG CONTROL

The ANSELC register (Register 11-21) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELC bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

# 11.5.7 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELC register. Digital output functions may continue to control the pin when it is in Analog mode.

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELC  | ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | —       | _       | 187                 |

| INLVLC  | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 189                 |

| LATC    | LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 187                 |

| ODCONC  | ODC7    | ODC6    | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    | 188                 |

| PORTC   | RC7     | RC6     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 186                 |

| SLRCONC | SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 189                 |

| TRISC   | TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 186                 |

| WPUC    | WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 188                 |

# TABLE 11-5: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

#### REGISTER 11-38: WPUE: WEAK PULL-UP PORTE REGISTER

|   | U-0 | U-0 | R/W-1/1 | R/W-1/1              | R/W-1/1                          | R/W-1/1                                               |

|---|-----|-----|---------|----------------------|----------------------------------|-------------------------------------------------------|

| — |     | _   | WPUE3   | WPUE2 <sup>(3)</sup> | WPUE1 <sup>(3)</sup>             | WPUE0 <sup>(3)</sup>                                  |

|   |     |     |         |                      |                                  | bit 0                                                 |

|   |     |     |         |                      |                                  |                                                       |

|   | _   |     |         | — — — WPUE3          | — — — WPUE3 WPUE2 <sup>(3)</sup> | — — — WPUE3 WPUE2 <sup>(3)</sup> WPUE1 <sup>(3)</sup> |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'                          |

|---------|-----------------------------------------------------|

| bit 3-0 | WPUE<3:0>: Weak Pull-up Register bit <sup>(3)</sup> |

|         | 1 = Pull-up enabled                                 |

|         | 0 = Pull-up disabled                                |

|         |                                                     |

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- **2:** The weak pull-up device is automatically disabled if the pin is in configured as an output.

- **3:** WPUE<2:0> is not implemented on the PIC16(L)F1778.

# REGISTER 11-39: ODCONE: PORTE OPEN-DRAIN CONTROL REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| _     | —   | —   | _   | _   | ODE2    | ODE1    | ODE0    |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 2-0 **ODE<2:0>:** PORTE Open-Drain Enable bits For RE<2:0> pins 1 = Port pin operates as open-drain drive (sink current only) 0 = Port pin operates as standard push-pull drive (source and sink current)

**Note 1:** The ODCONE register is not implemented on the PIC16(L)F1778.

# 18.7 Register Definitions: DAC Control

Long bit name prefixes for the 10-bit DAC peripherals are shown in Table 18-2. Refer to **Section 1.1** "**Register and Bit naming conventions**" for more information

#### TABLE 18-2:

| Peripheral          | Bit Name Prefix |

|---------------------|-----------------|

| DAC1                | DAC1            |

| DAC2                | DAC2            |

| DAC5                | DAC5            |

| DAC6 <sup>(1)</sup> | DAC6            |

**Note 1:** PIC16(L)F1777/9 only.

#### REGISTER 18-1: DACxCON0: DAC CONTROL REGISTER 0

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| EN      | FM      | OE1     | OE2     | PSS     | <1:0>   | NSS     | <1:0>   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: DAC Enable bit                                           |

|---------|--------------------------------------------------------------|

|         | 1 = DACx is enabled                                          |

|         | 0 = DACx is disabled                                         |

| bit 6   | FM: DAC Reference Format bit                                 |

|         | 1 = DACx reference selection is left justified               |

|         | 0 = DACx reference selection is right justified              |

| bit 5   | OE1: DAC Voltage Output Enable bit                           |

|         | 1 = DACx voltage level is also an output on the DACxOUT1 pin |

|         | 0 = DACx voltage level is disconnected from the DACxOUT1 pin |

| bit 4   | OE2: DAC Voltage Output Enable bit                           |

|         | 1 = DACx voltage level is also an output on the DACxOUT2 pin |

|         | 0 = DACx voltage level is disconnected from the DACxOUT2 pin |

| bit 3-2 | PSS<1:0>: DAC Positive Source Select bits                    |

|         | 11 = DACxREF1+ (DAC5/6) or Reserved (DAC1/2)                 |

|         | 10 = FVR_buffer2                                             |

|         | 01 = DACxREF0+                                               |

|         | 00 = VDD                                                     |

| bit 1-0 | NSS<1:0>: DAC Negative Source Select bit                     |

|         | 11 = Reserved. Do not use.                                   |

|         | 10 = DACxREF1- (DAC5/6) or Reserved (DAC1/2)                 |

|         | 01 = DACxREF0-                                               |

|         | 00 = Agnd(AVss)                                              |

|         |                                                              |

# **19.11 Register Definitions: Comparator Control**

Long bit name prefixes for the Comparator peripherals are shown in Table 19-3. Refer to **Section 1.1.2.2** "Long Bit Names" for more information

#### TABLE 19-3:

| Peripheral                  | Bit Name Prefix |

|-----------------------------|-----------------|

| Comparator 1                | C1              |

| Comparator 2                | C2              |

| Comparator 3                | C3              |

| Comparator 4                | C4              |

| Comparator 5                | C5              |

| Comparator 6                | C6              |

| Comparator 7 <sup>(1)</sup> | C7              |

| Comparator 8 <sup>(1)</sup> | C8              |

Note 1: PIC16(L)F1777/9 only.

#### REGISTER 19-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| R/W-0/0 | R-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-1/1 | R/W-0/0 | R/W-0/0 |

|---------|-------|-----|---------|---------|---------|---------|---------|

| ON      | OUT   | —   | POL     | ZLF     | —       | HYS     | SYNC    |

| bit 7   |       |     |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | <b>ON:</b> Comparator Enable bit<br>1 = Comparator is enabled<br>0 = Comparator is disabled and consumes no active power                                                                                                                                                                                |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | OUT: Comparator Output bit $If POL = 1$ (inverted polarity): $1 = CxVP < CxVN$ $0 = CxVP > CxVN$ $If POL = 0$ (non-inverted polarity): $1 = CxVP > CxVN$ $0 = CxVP < CxVN$ $0 = CxVP < CxVN$                                                                                                            |

| bit 5 | Reserved: Read as '1'. Maintain this bit set.                                                                                                                                                                                                                                                           |

| bit 4 | <ul> <li>POL: Comparator Output Polarity Select bit</li> <li>1 = Comparator output is inverted</li> <li>0 = Comparator output is not inverted</li> </ul>                                                                                                                                                |

| bit 3 | <b>ZLF:</b> Comparator Zero Latency Filter Enable bit<br>1 = Comparator output is filtered<br>0 = Comparator output is unfiltered                                                                                                                                                                       |

| bit 2 | Reserved: Read as '1'. Maintain this bit set.                                                                                                                                                                                                                                                           |

| bit 1 | <ul> <li>HYS: Comparator Hysteresis Enable bit</li> <li>1 = Comparator hysteresis enabled</li> <li>0 = Comparator hysteresis disabled</li> </ul>                                                                                                                                                        |

| bit 0 | <ul> <li>SYNC: Comparator Output Synchronous Mode bit</li> <li>1 = Comparator output to Timer1 and I/O pin is synchronous to changes on Timer1 clock source. Output updated on the falling edge of Timer1 clock source.</li> <li>0 = Comparator output to Timer1 and I/O pin is asynchronous</li> </ul> |

## 23.6.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode except the TMRx\_ers external signal can also gate the timer. When used with the CCP the gating extends the PWM period. If the timer is stopped when the PWM output is high then the duty cycle is also extended.

When MODE<4:0> = 00001 then the timer is stopped when the external signal is high. When MODE<4:0> = 00010 then the timer is stopped when the external signal is low.

Figure 23-5 illustrates the Hardware Gating mode for MODE<4:0> = 00001 in which a high input level starts the counter.

|                   | Rey, 10-00/968<br>590/2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE              | 0b00001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| TMRx_clk          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| TMRx_ers_         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| PRx               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| TMRx              | $0 \qquad \begin{pmatrix} 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 1$ |  |

| TMRx_postscaled_  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| PWM Duty<br>Cycle | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| PWM Output        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

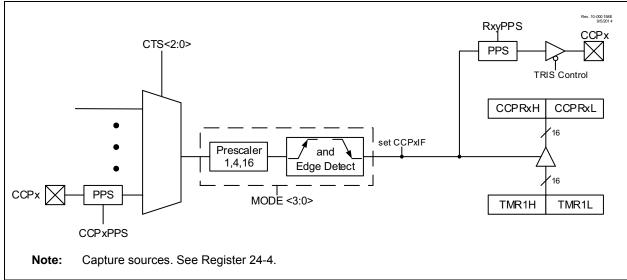

# FIGURE 24-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

# 24.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 22.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

#### 24.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in operating mode.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

# 24.1.4 CCP PRESCALER

There are four prescaler settings specified by the MODE<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the EN bit of the CCPxCON register before changing the prescaler.

# 24.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

#### 24.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the PPS controls. See **Section 12.0 "Peripheral Pin Select (PPS) Module"** for more details.

# 24.1.7 CAPTURE OUTPUT

Whenever a capture occurs, the output of the CCP will go high for a period equal to one system clock period (1/Fosc). This output is available as an input signal to the following peripherals:

- ADC Trigger

- COG

- PRG

- DSM

- CLC

- · Op Amp override

- Timer2/4/6/8 Reset

- Any device pins

In addition, the CCP output can be output to any pin with that pin's PPS control.

DS40001819B-page 336

© 2015-2016 Microchip Technology Inc.

PIC16(L)F1777/8/9

# 27.11 Buffer Updates

Changes to the phase, dead-band, and blanking count registers need to occur simultaneously during COG operation to avoid unintended operation that may occur as a result of delays between each register write. This is accomplished with the LD bit of the COGxCON0 register and double buffering of the phase, blanking and dead-band count registers.

Before the COG module is enabled, writing the count registers loads the count buffers without need of the LD bit. However, when the COG is enabled, the count buffer updates are suspended after writing the count registers until after the LD bit is set. When the LD bit is set, the phase, dead-band and blanking register values are transferred to the corresponding buffers synchronous with COG operation. The LD bit is cleared by hardware when the transfer is complete.

# 27.12 Input and Output Pin Selection

The COG has one selection for an input from a device pin. That one input can be used as rising and falling event source or a fault source. The COGxINPPS register is used to select the pin. Refer to registers xxxPPS (Register 12-1) and RxyPPS (Register 12-2).

The pin PPS control registers are used to enable the COG outputs. Any combination of outputs to pins is possible including multiple pins for the same output. See the RxyPPS control register and **Section 12.2** "**PPS Outputs**" for more details.

# 27.13 Operation During Sleep

The COG continues to operate in Sleep provided that the COG\_clock, rising event, and falling event sources remain active.

The HFINTSOC remains active during Sleep when the COG is enabled and the HFINTOSC is selected as the COG\_clock source.

# 27.14 Configuring the COG

The following steps illustrate how to properly configure the COG to ensure a synchronous start with the rising event input:

- 1. If a pin is to be used for the COG fault or event input, use the COGxINPPS register to configure the desired pin.

- 2. Clear all ANSEL register bits associated with pins that are used for COG functions.

- Ensure that the TRIS control bits corresponding to the COG outputs to be used are set so that all are configured as inputs. The COG module will enable the output drivers as needed later.

- 4. Clear the EN bit, if not already cleared.

- 5. Set desired dead-band times with the COGxDBR and COGxDBF registers and select the source with the RDBS and FDBS bits of the COGxCON1 register.

- 6. Set desired blanking times with the COGxBLKR and COGxBLKF registers.

- 7. Set desired phase delay with the COGxPHR and COGxPHF registers.

- 8. Select the desired shutdown sources with the COGxASD1 register.

- 9. Setup the following controls in COGxASD0 auto-shutdown register:

- Select both output override controls to the desired levels (this is necessary, even if not using auto-shutdown because start-up will be from a shutdown state).

- Set the ASE bit and clear the ARSEN bit.

- 10. Select the desired rising and falling event sources with the COGxRIS0, COGxRIS1, COGxFIS0, and COGxFIS1 registers.

- 11. Select the desired rising and falling event modes with the COGxRSIM0, COGxRSIMI1, COGxFSIM0, and COGxFSIM1 registers.

- 12. Configure the following controls in the COGxCON1 register:

- Set the polarity for each output

- Select the desired dead-band timing sources

- 13. Configure the following controls in the COGxCON0 register:

- Set the desired operating mode

- Select the desired clock source

- 14. If one of the steering modes is selected then configure the following controls in the COGxSTR register:

- Set the steering bits of the outputs to be used.

- Set the desired static levels.

- 15. Set the EN bit.

- 16. Set the pin PPS controls to direct the COG outputs to the desired pins.

- 17. If auto-restart is to be used, set the ARSEN bit and the ASE will be cleared automatically. Otherwise, clear the ASE bit to start the COG.

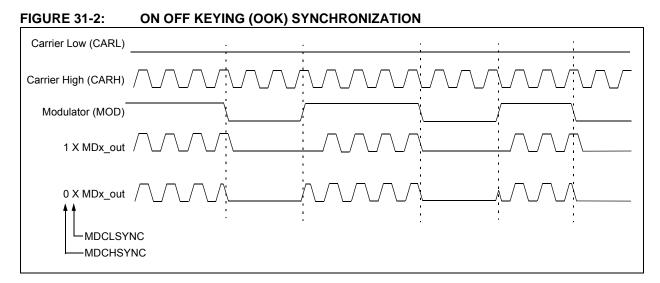

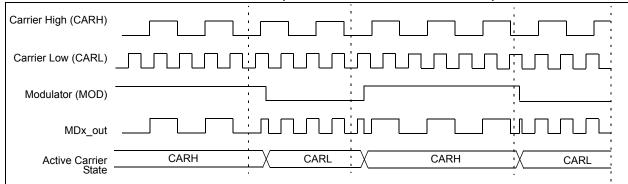

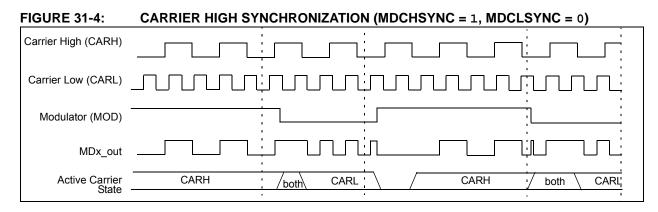

FIGURE 31-3: NO SYNCHRONIZATION (MDCHSYNC = 0, MDCLSYNC = 0)

# 31.11 Register Definitions: Data Signal Modulator

Long bit name prefixes for the 10-bit DAC peripherals are shown in Table 31-3. Refer to **Section 1.1 "Register and Bit naming conventions**" for more information

#### **TABLE 31-3:**

| Peripheral          | Bit Name Prefix |

|---------------------|-----------------|

| DSM1                | DSM1            |

| DSM2                | DSM2            |

| DSM3                | DSM3            |

| DSM4 <sup>(1)</sup> | DSM4            |

**Note 1:** PIC16(L)F1777/9 only.

#### REGISTER 31-1: MDxCON0: MODULATION CONTROL REGISTER 0

| R/W-0/0     | U-0 | R-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 |

|-------------|-----|-------|---------|-----|-----|-----|---------|

| EN          | —   | OUT   | OPOL    | —   | —   | —   | BIT     |

| bit 7 bit 0 |     |       |         |     |     |     |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: Modulator Module Enable bit                                                                                                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Modulator module is enabled and mixing input signals</li> <li>0 = Modulator module is disabled and has no output</li> </ul> |

| bit 6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5   | OUT: Modulator Output bit                                                                                                                |

|         | Displays the current output value of the modulator module. <sup>(1)</sup>                                                                |

| bit 4   | OPOL: Modulator Output Polarity Select bit                                                                                               |

|         | <ol> <li>1 = Modulator output signal is inverted. Idle high output.</li> </ol>                                                           |

|         | 0 = Modulator output signal is not inverted. Idle low output.                                                                            |

| bit 3-1 | Unimplemented: Read as '0'                                                                                                               |

| bit 0   | BIT: Allows direct software control of the modulation source input to module <sup>(2)</sup>                                              |

|         | 1 = Modulator uses High Carrier source                                                                                                   |

|         | 0 = Modulator uses Low Carrier source                                                                                                    |

| Note di | The medulated events if from up not one has even the events on the start the start the start of the start of the                         |

- **Note 1:** The modulated output frequency can be greater and asynchronous from the clock that updates this register bit, the bit value may not be valid for higher speed modulator or carrier signals.

- 2: BIT must be selected as the modulation source in the MDSRC register for this operation.

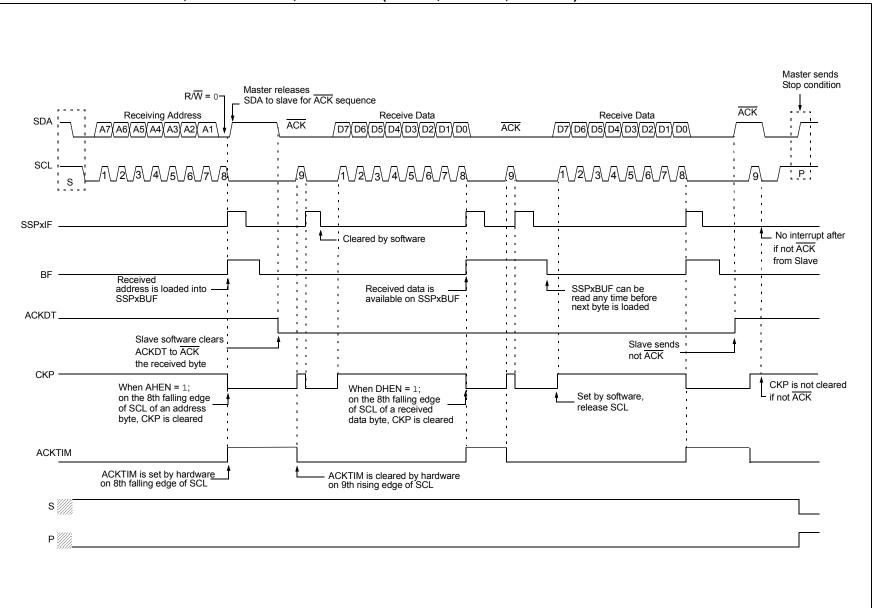

# FIGURE 32-17: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 1, AHEN = 1, DHEN = 1)

PIC16(L)F1777/8/9

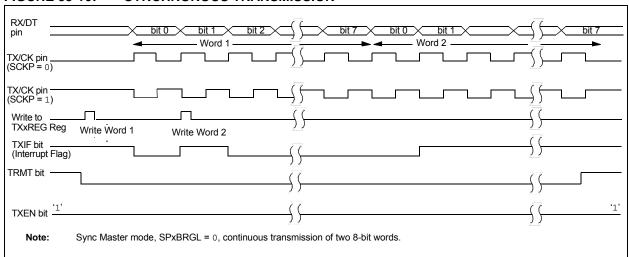

# 33.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VoL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(baud rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 33-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 33.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 33-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXxREG register.

#### 33.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXxSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

Note: The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 33.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXxREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXxREG until the Stop bit of the previous character has been transmitted. The pending character in the TXxREG is then transferred to the TSR in one TcY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXxREG.

#### 33.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0', which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 33.5.1.2 "Clock Polarity"**.

#### 33.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXxREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXxREG. The TXIF flag bit is not cleared immediately upon writing TXxREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXxREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXxREG is empty, regardless of the state of the TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXxREG.

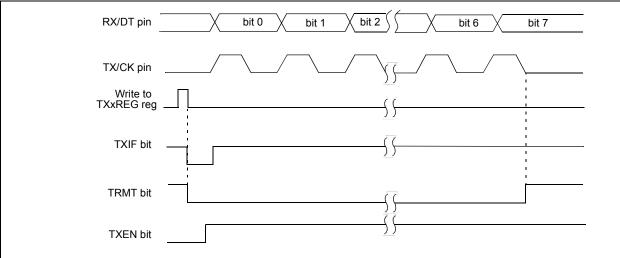

# FIGURE 33-10: SYNCHRONOUS TRANSMISSION

# FIGURE 33-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

| ΜΟΥΨΙ      | Move W to INDFn                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:    | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                                                                                                                   |

| Operands:  | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ -32 \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                                                                        |

| Operation: | $\label{eq:states} \begin{array}{l} W \rightarrow INDFn \\ Effective \ address \ is \ determined \ by \\ \bullet \ FSR + 1 \ (preincrement) \\ \bullet \ FSR + 1 \ (predecrement) \\ \bullet \ FSR + k \ (relative \ offset) \\ After \ the \ Move, \ the \ FSR \ value \ will \ be \\ either: \\ \bullet \ FSR + 1 \ (all \ increments) \\ \bullet \ FSR + 1 \ (all \ increments) \\ Unchanged \\ \end{array}$ |

Status Affected:

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

None

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h-FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation         |

|------------------|----------------------|

| Syntax:          | [ <i>label</i> ] NOP |

| Operands:        | None                 |

| Operation:       | No operation         |

| Status Affected: | None                 |

| Description:     | No operation.        |

| Words:           | 1                    |

| Cycles:          | 1                    |

| Example:         | NOP                  |

| OPTION           | Load OPTION_REG Register with W                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] OPTION                                                                                            |

| Operands:        | None                                                                                                      |

| Operation:       | $(W) \rightarrow OPTION\_REG$                                                                             |

| Status Affected: | None                                                                                                      |

| Description:     | Move data from W register to<br>OPTION_REG register.                                                      |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | OPTION                                                                                                    |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F |

| RESET            | Software Reset                                                                 |

|------------------|--------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                  |

| Operands:        | None                                                                           |

| Operation:       | Execute a device Reset. Resets the $\overline{RI}$ flag of the PCON register.  |

| Status Affected: | None                                                                           |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by<br>software. |

# TABLE 36-17: OPERATIONAL AMPLIFIER (OPA)

| <b>Operating Conditions (unless otherwise stated)</b><br>VDD = 3.0V, TA = 25°C, OPAxSP = 1 (High GBWP mode) |        |                              |      |      |      |         |            |

|-------------------------------------------------------------------------------------------------------------|--------|------------------------------|------|------|------|---------|------------|

| Param<br>No.                                                                                                | Symbol | Parameters                   | Min. | Тур. | Max. | Units   | Conditions |

| OPA01*                                                                                                      | GBWP   | Gain Bandwidth Product       | _    | 3.5  | —    | MHz     |            |

| OPA02*                                                                                                      | Ton    | Turn-on Time                 | —    | 10   |      | μS      |            |

| OPA03*                                                                                                      | Рм     | Phase Margin                 | _    | 40   |      | degrees |            |

| OPA04*                                                                                                      | SR     | Slew Rate                    | _    | 3    | _    | V/μs    |            |

| OPA05                                                                                                       | Off    | Offset                       | _    | ±3   | ±9   | mV      |            |

| OPA06                                                                                                       | CMRR   | Common-Mode Rejection Ratio  | 52   | 70   | _    | dB      |            |

| OPA07*                                                                                                      | AOL    | Open Loop Gain               | —    | 90   |      | dB      |            |

| OPA08                                                                                                       | VICM   | Input Common-Mode Voltage    | 0    | —    | Vdd  | V       | VDD > 2.5V |

| OPA09*                                                                                                      | PSRR   | Power Supply Rejection Ratio | _    | 80   |      | dB      |            |

| OPA10*                                                                                                      | HZ     | High-Impedance On/Off Time   | —    | 50   | —    | ns      |            |

\* These parameters are characterized but not tested.

# TABLE 36-18: PROGRAMMABLE RAMP GENERATOR (PRG) SPECIFICATIONS

| Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C (unless otherwise stated) |      |                                  |      |      |      |       |                |

|---------------------------------------------------------------------------------------------------|------|----------------------------------|------|------|------|-------|----------------|

| Param<br>No.                                                                                      | Sym. | Characteristics                  | Min. | Тур. | Max. | Units | Comments       |

| PRG01                                                                                             | RRR  | Rising Ramp Rate <sup>(1)</sup>  | —    | 1    | _    | V/µs  | PRGxCON2 = 10h |

| PRG02                                                                                             | FRR  | Falling Ramp Rate <sup>(1)</sup> | —    | 1    | _    | V/μs  | PRGxCON2 = 10h |

\* These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to VDD.

# TABLE 36-19: COMPARATOR SPECIFICATIONS

| <b>Operating Conditions (unless otherwise stated)</b><br>VDD = 3.0V, TA = 25°C<br>See <b>Section 31.0 "DC and AC Characteristics Graphs and Charts"</b> for operating characterization. |                      |                                            |      |      |      |       |              |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------|------|------|------|-------|--------------|--|

| Param<br>No.                                                                                                                                                                            | Sym.                 | Characteristics                            | Min. | Тур. | Max. | Units | Comments     |  |

| CM01                                                                                                                                                                                    | VIOFF                | Input Offset Voltage                       | —    | ±2.5 | ±5   | mV    | VICM = VDD/2 |  |

| CM02                                                                                                                                                                                    | VICM                 | Input Common-Mode Voltage                  | 0    |      | Vdd  | V     |              |  |

| CM03                                                                                                                                                                                    | CMRR                 | Common-Mode Rejection Ratio                | 40   | 50   |      | dB    |              |  |

| CM04A                                                                                                                                                                                   |                      | Response Time Rising Edge                  | —    | 60   | 125  | ns    | CxSP = 1     |  |

| CM04B                                                                                                                                                                                   | Tresp <sup>(1)</sup> | Response Time Falling Edge                 | _    | 60   | 110  | ns    | CxSP = 1     |  |

| CM04C                                                                                                                                                                                   | Tresp.               | Response Time Rising Edge                  | —    | 85   | —    | ns    | CxSP = 0     |  |

| CM04D                                                                                                                                                                                   |                      | Response Time Falling Edge                 | _    | 85   |      | ns    | CxSP = 0     |  |

| CM05                                                                                                                                                                                    | Тмс2о∨               | Comparator Mode Change to<br>Output Valid* | _    | —    | 10   | μS    |              |  |

| CM06                                                                                                                                                                                    | CHYSTER              | Comparator Hysteresis                      | 20   | 45   | 75   | mV    | CxHYS = 1    |  |

\* These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to VDD.