Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 28KB (16K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 2K x 8                                                                   |

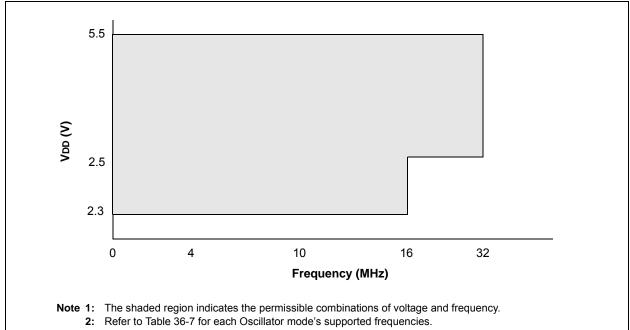

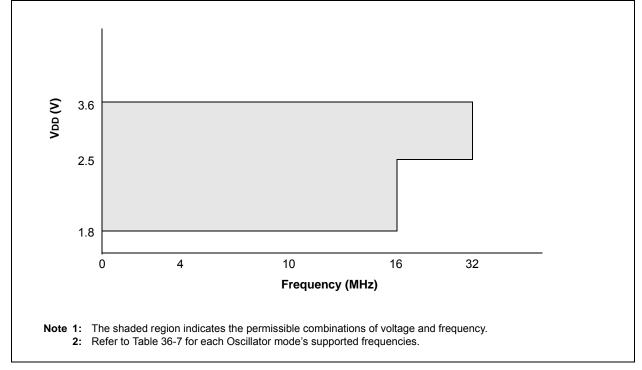

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 28x10b; D/A 4x5b, 4x10b                                              |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1779-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                    |             |           |                    |              |            |           |                         |                           |              |              | Ре  | riph   | nera   | Inp     | ut       |          |                 |            |            |                    |           |                    |                    |                 |              |

|--------------------|-------------|-----------|--------------------|--------------|------------|-----------|-------------------------|---------------------------|--------------|--------------|-----|--------|--------|---------|----------|----------|-----------------|------------|------------|--------------------|-----------|--------------------|--------------------|-----------------|--------------|

| Peripheral Output  | ADC Trigger | COG Clock | COG Rising/Falling | COG Shutdown | 10-bit DAC | 5-bit DAC | <b>PRG Analog Input</b> | <b>PRG Rising/Falling</b> | Comparator + | Comparator - | CLC | DSM CH | DSM CL | DSM Mod | Op Amp + | Op Amp - | Op Amp Override | 10-bit PWM | 16-bit PWM | <b>CCP</b> Capture | CCP Clock | Timer2/4/6/8 Clock | Timer2/4/6/8 Reset | Timer1/3/5 Gate | Timer0 Clock |

| FVR                |             |           |                    |              | •          | •         | ٠                       |                           | ٠            | ٠            |     |        |        |         | •        | •        |                 |            |            |                    |           |                    |                    |                 |              |

| ZCD                |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          | •               |            |            |                    |           | •                  |                    |                 |              |

| PRG                |             |           |                    |              |            |           |                         |                           | •            |              |     |        |        |         | •        | •        |                 |            |            |                    |           |                    |                    |                 |              |

| 10-bit DAC         |             |           |                    |              |            |           | •                       |                           | •            |              |     |        |        |         | •        | •        |                 |            |            |                    |           |                    |                    |                 |              |

| 5-bit DAC          |             |           |                    |              |            |           | •                       |                           | •            |              |     |        |        |         | •        | •        |                 |            |            |                    |           |                    |                    |                 |              |

| CCP                | •           |           | ٠                  |              |            |           |                         | ٠                         |              |              | ٠   | ٠      | •      | ٠       |          |          | •               |            |            |                    |           |                    | •                  |                 |              |

| Comparator (sync)  | •           |           |                    |              |            |           |                         | •                         |              |              | •   |        |        |         |          |          | •               |            |            | •                  |           |                    | •                  | •               |              |

| Comparator (async) |             |           | •                  | •            |            |           |                         |                           |              |              |     |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| CLC                | •           |           | •                  | •            |            |           |                         |                           |              |              | •   | •      | •      | •       |          |          | •               |            |            | •                  |           | •                  | •                  |                 |              |

| DSM                |             |           |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| COG                |             |           |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          | •               |            |            |                    |           |                    |                    |                 |              |

| EUSART TX/CK       |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| EUSART DT          |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| MSSP SCK/SCL       |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| MSSP SDO/SDA       |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| Op Amp             |             |           |                    |              |            |           | •                       |                           |              |              |     |        |        |         |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| 10-bit PWM         | •           |           | •                  |              |            |           |                         | •                         |              |              | •   | •      | •      | •       |          |          | •               |            |            |                    |           |                    | •                  |                 |              |

| 16-bit PWM         | •           |           | •                  |              |            |           |                         | •                         |              |              | •   | •      | •      | •       |          |          | •               |            |            |                    |           |                    | •                  |                 |              |

| Timer0 overflow    | •           |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 |            |            |                    |           |                    |                    | •               |              |

| Timer2 = T2PR      |             |           |                    | ٠            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer4 = T4PR      |             |           |                    | ٠            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer6 = T6PR      |             |           |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer8 = T8PR      |             |           |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer2 Postscale   | •           |           |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer4 Postscale   | •           |           |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer6 Postscale   | •           |           |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer8 Postscale   | •           |           |                    | ٠            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer1 overflow    | ٠           |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    |                    |                 |              |

| Timer3 overflow    | •           |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | ٠          |            |                    | •         |                    |                    |                 |              |

| Timer5 overflow    | •           |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    |                    |                 |              |

| SOSC               |             |           |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          |                 |            | •          |                    |           | ٠                  |                    |                 |              |

| Fosc/4             |             | ٠         |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          |                 |            |            |                    |           | •                  |                    |                 |              |

| Fosc               |             | •         |                    |              |            |           |                         |                           |              |              | •   | •      | •      |         |          |          |                 |            | •          |                    |           | ٠                  |                    |                 |              |

| HFINTOSC           |             | •         |                    |              |            |           |                         |                           |              |              | •   | •      | •      |         |          |          |                 |            | •          |                    |           | ٠                  |                    |                 |              |

| LFINTOSC           |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 |            | •          |                    |           | •                  |                    |                 |              |

| MFINTOSC           |             |           |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          |                 |            |            |                    |           | ٠                  |                    |                 |              |

| IOCIF              |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 |            |            | •                  | •         |                    |                    |                 |              |

| PPS Input pin      |             |           | •                  | ٠            |            |           |                         | •                         |              |              |     | •      | •      | •       |          |          |                 |            |            | •                  | •         | •                  | •                  | •               | •            |

TABLE 1-4: PERIPHERAL CONNECTION MATRIX

#### TABLE 3-18: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr | Name                  | Bit 7         | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all other Resets |

|------|-----------------------|---------------|---------|---------|---------|---------|---------|---------|---------|----------------------|---------------------------|

| Banl | k7                    |               |         |         |         |         |         |         |         |                      |                           |

| 38Ch | INLVLA                | INLVLA7       | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 1111 1111            | 1111 1111                 |

| 38Dh | INLVLB                | INLVLB7       | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 | 1111 1111            | 1111 1111                 |

| 38Eh | INLVLC                | INLVLC7       | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 1111 1111            | 1111 1111                 |

|      | INLVLD <sup>(3)</sup> | INLVLD7       | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2 | INLVLD1 | INLVLD0 | 1111 1111            | 1111 1111                 |

| 390h | INLVLE <sup>(3)</sup> | _             | —       | —       | _       | INLVLE3 | INLVLE2 | INLVLE1 | INLVLE0 | 1111                 | 1111                      |

| 391h | IOCAP                 | IOCAP7        | IOCAP6  | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  | 0000 0000            | 0000 0000                 |

| 392h | IOCAN                 | IOCAN7        | IOCAN6  | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  | 0000 0000            | 0000 0000                 |

| 393h | IOCAF                 | IOCAF7        | IOCAF6  | IOCAF5  | IOCAF4  | IOCAF3  | IOCAF2  | IOCAF1  | IOCAF0  | 0000 0000            | 0000 0000                 |

| 394h | IOCBP                 | IOCBP7        | IOCBP6  | IOCBP5  | IOCBP4  | IOCBP3  | IOCBP2  | IOCBP1  | IOCBP0  | 0000 0000            | 0000 0000                 |

| 395h | IOCBN                 | IOCBN7        | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  | 0000 0000            | 0000 0000                 |

| 396h | IOCBF                 | IOCBF7        | IOCBF6  | IOCBF5  | IOCBF4  | IOCBF3  | IOCBF2  | IOCBF1  | IOCBF0  | 0000 0000            | 0000 0000                 |

| 397h | IOCCP                 | IOCCP7        | IOCCP6  | IOCCP5  | IOCCP4  | IOCCP3  | IOCCP2  | IOCCP1  | IOCCP0  | 0000 0000            | 0000 0000                 |

| 398h | IOCCN                 | IOCCN7        | IOCCN6  | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  | 0000 0000            | 0000 0000                 |

| 399h | IOCCF                 | IOCCF7        | IOCCF6  | IOCCF5  | IOCCF4  | IOCCF3  | IOCCF2  | IOCCF1  | IOCCF0  | 0000 0000            | 0000 0000                 |

| 39Ah | —                     | Unimplemented |         |         |         |         |         |         |         | —                    | —                         |

| 39Bh | —                     | Unimplemented |         |         |         |         |         |         |         | —                    | —                         |

| 39Ch | —                     | Unimplemented |         |         |         |         |         |         |         | _                    | _                         |

| 39Dh | IOCEP                 |               | _       | —       |         | IOCEP3  | _       | _       | _       | 0                    | 0                         |

| 39Eh | IOCEN                 |               | _       | _       |         | IOCEN3  | _       | _       | _       | 0                    | 0                         |

| 39Fh | IOCEF                 | _             | _       | —       | _       | IOCEF3  | —       | —       | —       | 0                    | 0                         |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Unimplemented, read as '1'.

Note 1:

Unimplemented on PIC16LF1777/8/9. 2:

3: Unimplemented on PIC16(L)F1778.

#### TABLE 3-18: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr              | Name     | Bit 7         | Bit 6 | Bit 5    | Bit 4 | Bit 3   | Bit 2   | Bit 1     | Bit 0   | Value on<br>POR, BOR | Value on all other Resets |  |  |

|-------------------|----------|---------------|-------|----------|-------|---------|---------|-----------|---------|----------------------|---------------------------|--|--|

| Ban               | k 30     |               |       |          |       | 1       | 1       |           |         |                      |                           |  |  |

| F0Ch<br>—<br>F0Eh | _        | Unimplemented |       |          |       |         |         |           |         |                      |                           |  |  |

| F0Fh              | CLCDATA  | —             | —     | _        | _     | MLC4OUT | MLC3OUT | MLC2OUT   | MLC1OUT | x000                 | u000                      |  |  |

| F10h              | CLC1CON  | EN            | —     | OUT      | INTP  | INTN    |         | MODE<2:0> |         | 0-00 0000            | 0-00 0000                 |  |  |

| F11h              | CLC1POL  | POL           | —     | _        |       | G4POL   | G3POL   | G2POL     | G1POL   | 0 xxxx               | 0 uuuu                    |  |  |

| F12h              | CLC1SEL0 | —             | —     |          |       | D1S·    | <5:0>   |           |         | xx xxxx              | uu uuuu                   |  |  |

| F13h              | CLC1SEL1 | —             | _     |          |       | D2S·    | <5:0>   |           |         | xx xxxx              | uu uuuu                   |  |  |

| F14h              | CLC1SEL2 | —             | _     |          |       | D3S-    | <5:0>   |           |         | xx xxxx              | uu uuuu                   |  |  |

| F15h              | CLC1SEL3 | —             | _     |          |       | D4S·    | <5:0>   |           |         | xx xxxx              | uu uuuu                   |  |  |

| F16h              | CLC1GLS0 | G1D4T         | G1D4N | G1D3T    | G1D3N | G1D2T   | G1D2N   | G1D1T     | G1D1N   | XXXX XXXX            | uuuu uuuu                 |  |  |

| F17h              | CLC1GLS1 | G2D4T         | G2D4N | G2D3T    | G2D3N | G2D2T   | G2D2N   | G2D1T     | G2D1N   | XXXX XXXX            | uuuu uuuu                 |  |  |

| F18h              | CLC1GLS2 | G3D4T         | G3D4N | G3D3T    | G3D3N | G3D2T   | G3D2N   | G3D1T     | G3D1N   | XXXX XXXX            | uuuu uuuu                 |  |  |

| F19h              | CLC1GLS3 | G4D4T         | G4D4N | G4D3T    | G4D3N | G4D2T   | G4D2N   | G4D1T     | G4D1N   | XXXX XXXX            | uuuu uuuu                 |  |  |

| F1Ah              | CLC2CON  | EN            | _     | OUT      | INTP  | INTN    |         | MODE<2:0> |         | 0-00 0000            | 0-00 0000                 |  |  |

| F1Bh              | CLC2POL  | POL           | _     |          |       | G4POL   | G3POL   | G2POL     | G1POL   | 0 xxxx               | 0 uuuu                    |  |  |

| F1Ch              | CLC2SEL0 | —             | _     |          |       | D1S·    | <5:0>   |           |         | xx xxxx              | uu uuuu                   |  |  |

| F1Dh              | CLC2SEL1 | —             | —     |          |       | D2S-    | <5:0>   |           |         | xx xxxx              | uu uuuu                   |  |  |

| F1Eh              | CLC2SEL2 | —             | —     |          |       | D3S-    | <5:0>   |           |         | xx xxxx              | uu uuuu                   |  |  |

| F1Fh              | CLC2SEL3 | —             | —     |          |       | D4S·    | <5:0>   |           |         | xx xxxx              | uu uuuu                   |  |  |

| F20h              | CLC2GLS0 | G1D4T         | G1D4N | G1D3T    | G1D3N | G1D2T   | G1D2N   | G1D1T     | G1D1N   | XXXX XXXX            | uuuu uuuu                 |  |  |

| F21h              | CLC2GLS1 | G2D4T         | G2D4N | G2D3T    | G2D3N | G2D2T   | G2D2N   | G2D1T     | G2D1N   | XXXX XXXX            | uuuu uuuu                 |  |  |

| F22h              | CLC2GLS2 | G3D4T         | G3D4N | G3D3T    | G3D3N | G3D2T   | G3D2N   | G3D1T     | G3D1N   | XXXX XXXX            | uuuu uuuu                 |  |  |

| F23h              | CLC2GLS3 | G4D4T         | G4D4N | G4D3T    | G4D3N | G4D2T   | G4D2N   | G4D1T     | G4D1N   | XXXX XXXX            | uuuu uuuu                 |  |  |

| F24h              | CLC3CON  | EN            | —     | OUT      | INTP  | INTN    |         | MODE<2:0> |         | 0-00 0000            | 0-00 0000                 |  |  |

| F25h              | CLC3POL  | POL           | —     | _        | _     | G4POL   | G3POL   | G2POL     | G1POL   | 0 xxxx               | 0 uuuu                    |  |  |

| F26h              | CLC3SEL0 | —             | —     | D1S<5:0> |       |         |         |           |         |                      | uu uuuu                   |  |  |

| F27h              | CLC3SEL1 | —             | _     | D2S<5:0> |       |         |         |           |         |                      | uu uuuu                   |  |  |

| F28h              | CLC3SEL2 | —             | _     | D3S<5:0> |       |         |         |           |         |                      | uu uuuu                   |  |  |

| F29h              | CLC3SEL3 | —             | _     | D4S<5:0> |       |         |         |           |         |                      | uu uuuu                   |  |  |

| F2Ah              | CLC3GLS0 | G1D4T         | G1D4N | G1D3T    | G1D3N | G1D2T   | G1D2N   | G1D1T     | G1D1N   | xxxx xxxx            | uuuu uuuu                 |  |  |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** Unimplemented, read as '1'.

2: Unimplemented on PIC16LF1777/8/9.

3: Unimplemented on PIC16(L)F1778.

#### 3.5 PCL and PCLATH

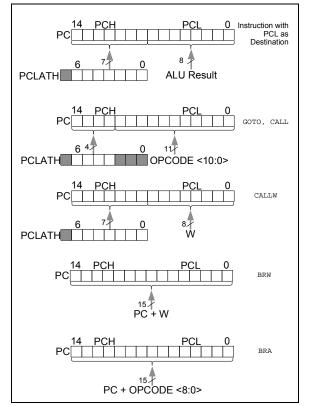

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-4 shows the five situations for the loading of the PC.

FIGURE 3-4: LOADING OF PC IN DIFFERENT SITUATIONS

#### 3.5.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

#### 3.5.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

#### 3.5.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.5.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

| FIGURE 5-7:               | INTERNAL OSCILLATOR SWITCH TIMING                      |

|---------------------------|--------------------------------------------------------|

|                           |                                                        |

| MENEROSC/                 | LFINYOSC (FSCM and WOY disabled)                       |

| HFINTOSC/<br>MEINTOSC     | Citati vas Time Skovite Sync Risming                   |

| LFINTOSC                  |                                                        |

| IRCF <3:0>                | $\neq 0$ $X = 0$                                       |

| System Clock              |                                                        |

|                           |                                                        |

| 99998763867<br>8859876386 | LEWYCOCC (EMMOR FACIAL OF WOY specified)               |

| HFINTOSC/<br>MEENTOSC     |                                                        |

| LFINTOSC                  |                                                        |

| IRCF <3:0>                | $\neq 0$ $\chi = 0$                                    |

| System Clock              |                                                        |

|                           |                                                        |

|                           |                                                        |

| LEBELOSO                  | UPPER STATE OF UPPER STATE OF UPPER STATE STATE STATES |

| xx 224 (xxxxX)            | Barnand Bina (Broycle Synce) Recognize                 |

| HEINTOSO<br>MEINTOSO      |                                                        |

| \$\$\C\$\K\$\C\$\         | × 0 X V 0                                              |

| System Crook              |                                                        |

|                           |                                                        |

|                           |                                                        |

| R/W-0/0        | ) R/W-0/0                            | R/W-0/0                               | R/W-0/0    | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|----------------|--------------------------------------|---------------------------------------|------------|----------------|------------------|------------------|-------------|

| _              | _                                    | COG2IE                                | ZCDIE      | CLC4IE         | CLC3IE           | CLC2IE           | CLC1IE      |

| bit 7          | ·                                    |                                       |            |                |                  |                  | bit 0       |

|                |                                      |                                       |            |                |                  |                  |             |

| Legend:        |                                      |                                       |            |                |                  |                  |             |

| R = Reada      | ble bit                              | W = Writable                          | bit        |                | nented bit, read |                  |             |

| u = Bit is u   | nchanged                             | x = Bit is unkr                       | nown       | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is s | set                                  | '0' = Bit is cle                      | ared       |                |                  |                  |             |

|                |                                      |                                       |            |                |                  |                  |             |

| bit 7-6        | -                                    | nted: Read as '                       |            |                |                  |                  |             |

| bit 5          |                                      | DG2 Auto-Shutd                        | •          | Enable bit     |                  |                  |             |

|                |                                      | nterrupt enabled<br>nterrupt disabled |            |                |                  |                  |             |

| bit 4          |                                      | -Cross Detectio                       |            | able bit       |                  |                  |             |

|                | 1 = ZCD inte                         | errupt enabled                        |            |                |                  |                  |             |

|                | 0 = ZCD inte                         | errupt disabled                       |            |                |                  |                  |             |

| bit 3          |                                      | C4 Interrupt Ena                      | able bit   |                |                  |                  |             |

|                |                                      | terrupt enabled                       |            |                |                  |                  |             |

| bit 2          |                                      | iterrupt disabled<br>C3 Interrupt Ena |            |                |                  |                  |             |

|                |                                      | terrupt enabled                       |            |                |                  |                  |             |

|                |                                      | terrupt disabled                      |            |                |                  |                  |             |

| bit 1          | CLC2IE: CL                           | C2 Interrupt Ena                      | able bit   |                |                  |                  |             |

|                |                                      | nterrupt enabled                      |            |                |                  |                  |             |

|                |                                      | terrupt disabled                      |            |                |                  |                  |             |

| bit 0          |                                      | C1 Interrupt Ena                      | able bit   |                |                  |                  |             |

|                |                                      | terrupt enabled                       |            |                |                  |                  |             |

|                | v = CLC1 ln                          | terrupt disabled                      |            |                |                  |                  |             |

| Nata           |                                      |                                       | market has |                |                  |                  |             |

|                | Bit PEIE of the IN set to enable any |                                       |            |                |                  |                  |             |

#### REGISTER 7-4: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

#### **REGISTER 16-4:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | ADRE    | S<9:2>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper eight bits of 10-bit conversion result

#### **REGISTER 16-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADRES   | S<1:0>  | —       | —       | —       | —       | —       | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 ADRES<1:0>: ADC Result Register bits Lower two bits of 10-bit conversion result

bit 5-0 **Reserved**: Do not use.

#### 23.6.7 EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE

In Edge-Triggered Hardware Limit One-Shot modes the timer starts on the first external signal edge after the ON bit is set and resets on all subsequent edges. Only the first edge after the ON bit is set is needed to start the timer. The counter will resume counting automatically two clocks after all subsequent external Reset edges. Edge triggers are as follows:

- Rising edge start and Reset (MODE<4:0> = 01100)

- Falling edge start and Reset (MODE<4:0> = 01101)

The timer resets and clears the ON bit when the timer value matches the PRx period value. External signal edges will have no effect until after software sets the ON bit. Figure 23-10 illustrates the rising edge hardware limit one-shot operation.

When this mode is used in conjunction with the CCP then the first starting edge trigger, and all subsequent Reset edges, will activate the PWM drive. The PWM drive will deactivate when the timer matches the CCPRx pulse-width value and stay deactivated until the timer halts at the PRx period match unless an external signal edge resets the timer before the match occurs.

| REGISTER 26-7: | PWMxPHH: PWMx PHASE COUNT HIGH REGISTER |  |

|----------------|-----------------------------------------|--|

|----------------|-----------------------------------------|--|

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | PH<     | :15:8>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 **PH<15:8>**: PWM Phase High bits Upper eight bits of PWM phase count

#### REGISTER 26-8: PWMxPHL: PWMx PHASE COUNT LOW REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | PH<     | 7:0>    |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| -       |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| _ogona.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-0 **PH<7:0>**: PWM Phase Low bits Lower eight bits of PWM phase count

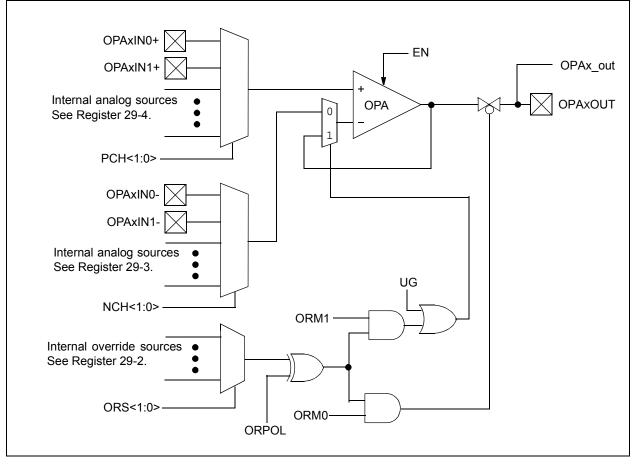

#### 29.0 OPERATIONAL AMPLIFIER (OPA) MODULES

The Operational Amplifier (OPA) is a standard threeterminal device requiring external feedback to operate. The OPA module has the following features:

- External connections to I/O ports

- · Low leakage inputs

- Factory Calibrated Input Offset Voltage

- Unity gain control

- Programmable positive and negative source selections

- Override controls

- Forced tri-state output

- Forced unity gain

#### FIGURE 29-1: OPAx MODULE BLOCK DIAGRAM

#### TABLE 29-1: AVAILABLE OP AMP MODULES

| Device          | OPA1 | OP2 | OPA3 | OPA4 |

|-----------------|------|-----|------|------|

| PIC16(L)F1778   | •    | •   | •    |      |

| PIC16(L)F1777/9 | •    | •   | •    | •    |

#### REGISTER 30-2: PRGxCON1: PROGRAMMABLE RAMP GENERATOR CONTROL 1 REGISTER

| U-0                                                                                                                                            | U-0                                                                                    | U-0                | U-0     | U-0                                     | R-0                | R/W-0/0 | R/W-0/0 |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------|---------|-----------------------------------------|--------------------|---------|---------|--|

| _                                                                                                                                              | —                                                                                      | —                  | _       | —                                       | RDY                | FPOL    | RPOL    |  |

| bit 7                                                                                                                                          |                                                                                        |                    |         |                                         |                    |         | bit (   |  |

| Legend:                                                                                                                                        |                                                                                        |                    |         |                                         |                    |         |         |  |

| R = Readable                                                                                                                                   | bit                                                                                    | W = Writable b     | it      | U = Unimplem                            | ented bit, read as | s 'O'   |         |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Rese                                                    |                                                                                        |                    |         | Resets                                  |                    |         |         |  |

| '1' = Bit is set                                                                                                                               |                                                                                        | '0' = Bit is clear | red     | q = value depends on configuration bits |                    |         |         |  |

|                                                                                                                                                |                                                                                        |                    |         |                                         |                    |         |         |  |

| bit 7-3                                                                                                                                        | Unimplemente                                                                           | ed: Read as '0'    |         |                                         |                    |         |         |  |

| bit 2                                                                                                                                          | it 2 RDY: Slope Generator Ready Status bit<br>1 = PRG is ready<br>0 = PRG is not ready |                    |         |                                         |                    |         |         |  |

| bit 1 <b>FPOL:</b> Fall Event Polarity Select bit<br>1 = Set_falling timing input is active-low<br>0 = Set_falling timing input is active-high |                                                                                        |                    |         |                                         |                    |         |         |  |

| bit 0                                                                                                                                          | RPOL: Rise Ev                                                                          | ent Polarity Sele  | ect bit |                                         |                    |         |         |  |

#### REGISTER 30-3: PRGxINS: VOLTAGE INPUT SELECT REGISTER

1 = Set\_rising timing input is active-low0 = Set\_rising timing input is active-high

| U-0   | U-0 | U-0 | U-0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|----------|---------|---------|---------|

| —     | —   | _   | _   | INS<3:0> |         |         |         |

| bit 7 |     |     |     |          |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = value depends on configuration bits               |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 **INS<3:0>:** Voltage Input Select bits Selects source of voltage level at which the ramp starts. See Table 30-3.

#### TABLE 30-3: VOLTAGE INPUT SOURCES

| INS<2:0>        | PRG1 Voltage Source                    | PRG2 Voltage Source      | PRG3 Voltage Source                        | PRG4 Voltage Source <sup>(2)</sup> |

|-----------------|----------------------------------------|--------------------------|--------------------------------------------|------------------------------------|

| 1010-1111       | Reserved                               | Reserved                 | Reserved                                   | Reserved                           |

| 1001(1)         | Switched PRG1IN1/OPA2OUT               | Switched PRG1IN1/OPA2OUT | Switched<br>PRG3IN1/OPA4OUT <sup>(2)</sup> | Switched PRG4IN1/OPA3OUT           |

| 1000 <b>(1)</b> | Switched PRG1IN0/OPA1OUT               | Switched PRG1IN0/OPA1OUT | Switched PRG3IN0/OPA3OUT                   | Switched PRG4IN0/OPA4OUT           |

| 0111            | Reserved                               | Reserved                 | Reserved                                   | Reserved                           |

| 0110            | DAC4_output                            | DAC4_output              | DAC8_output <sup>(2)</sup>                 | DAC8_output                        |

| 0101            | DAC3_output                            | DAC3_output              | DAC7_output                                | DAC7_output                        |

| 0100            | DAC2_output                            | DAC2_output              | DAC6_output <sup>(2)</sup>                 | DAC6_output                        |

| 0011            | DAC1_output                            | DAC1_output              | DAC5_output                                | DAC5_output                        |

| 0010            | FVR_buffer1                            | FVR_buffer1              | FVR_buffer2                                | FVR_buffer2                        |

| 0001            | PRG1IN1/OPA2OUT                        | PRG2IN1/OPA1OUT          | PRG3IN1/OPA4OUT <sup>(2)</sup>             | PRG4IN1/OPA3OUT                    |

| 0000            | PRG1IN0/OPA1OUT                        | PRG2IN0/OPA2OUT          | PRG3IN0/OPA3OUT PRG4IN0/OPA40              |                                    |

| Nata di         | l<br>Innut course is suitched off when |                          |                                            | ļ                                  |

Note 1: Input source is switched off when op amp override is forcing tri-state. See Section 29.3 "Override

**Control**". 2: PIC16(L)F1777/9 only.

#### 32.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 32-4.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 32.5.6.2 "10-bit Addressing Mode"** for more detail.

#### 32.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 7-bit Addressing mode. Figure 32-14 and Figure 32-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $I^2C$  communication.

- 1. Start bit detected.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDA low sending an ACK to the master, and sets SSPxIF bit.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCL line.

- 8. The master clocks out a data byte.

- Slave drives SDA low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- 11. Software reads the received byte from SSPxBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes idle.

### 32.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the eighth falling edge of SCL. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 32-16 displays a module using both address and data holding. Figure 32-17 includes the operation with the SEN bit of the SSPxCON2 register set.

- 1. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the eighth falling edge of SCL.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPxCON3 register to <u>determine</u> if the SSPxIF was after or before the ACK.

- 5. Slave reads the address value from SSPxBUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an  $\overline{ACK}$ , not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPxIF.

Note: SSPxIF is still set after the ninth falling edge of SCL even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSPxIF not set

- 11. SSPxIF set and CKP cleared after eighth falling edge of SCL for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and interrupt on Stop detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

#### 32.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 32.5.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPSR register. Then the SCL pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

#### 32.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLIF bit of the PIR register is set. Once a bus collision is detected, the slave goes idle and waits to be addressed again. User software can use the BCLIF bit to handle a slave bus collision.

#### 32.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 32-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

**Note 1:** If the master ACKs the clock will be stretched.

2: ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

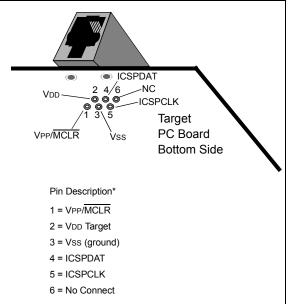

#### 34.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP™ refer to the "*PIC16(L)F177X Memory Programming Specification*" (DS40001792).

#### 34.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

#### 34.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.5 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

#### 34.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 34-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 34-2.

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 34-3 for more information.

| MOVIW            | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVIW ++FSRn<br>[ <i>label</i> ] MOVIWFSRn<br>[ <i>label</i> ] MOVIW FSRn++<br>[ <i>label</i> ] MOVIW FSRn<br>[ <i>label</i> ] MOVIW k[FSRn]                                                                                                                                                                                                                                                                                           |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01, 10, 11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                                                                                                                                                       |

| Operation:       | $\begin{split} &\text{INDFn} \rightarrow W \\ &\text{Effective address is determined by} \\ &\text{•} \ &\text{FSR + 1 (preincrement)} \\ &\text{•} \ &\text{FSR - 1 (predecrement)} \\ &\text{•} \ &\text{FSR + k (relative offset)} \\ &\text{After the Move, the FSR value will be} \\ &\text{either:} \\ &\text{•} \ &\text{FSR + 1 (all increments)} \\ &\text{•} \ &\text{FSR - 1 (all decrements)} \\ &\text{•} \ &\text{Unchanged} \end{split}$ |

| Status Affected: | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

| Syntax:          | [ <i>label</i> ] MOVLB k                                             |

|------------------|----------------------------------------------------------------------|

| Operands:        | $0 \leq k \leq 31$                                                   |

| Operation:       | $k \rightarrow BSR$                                                  |

| Status Affected: | None                                                                 |

| Description:     | The 5-bit literal 'k' is loaded into the Bank Select Register (BSR). |

| MOVLP            | Move literal to PCLATH                                                                            |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLP k                                                                          |  |  |  |  |

| Operands:        | $0 \le k \le 127$                                                                                 |  |  |  |  |

| Operation:       | $k \rightarrow PCLATH$                                                                            |  |  |  |  |

| Status Affected: | None                                                                                              |  |  |  |  |

| Description:     | The 7-bit literal 'k' is loaded into the PCLATH register.                                         |  |  |  |  |

| MOVLW            | Move literal to W                                                                                 |  |  |  |  |

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                          |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                 |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                               |  |  |  |  |

| Status Affected: | None                                                                                              |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W reg-<br>ister. The "don't cares" will assemble as<br>'0's. |  |  |  |  |

| Words:           | 1                                                                                                 |  |  |  |  |

| Cycles:          | 1                                                                                                 |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                        |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                                     |  |  |  |  |

| MOVWF            | Move W to f                                                                                       |  |  |  |  |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                          |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                                               |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                                                                             |  |  |  |  |

| Status Affected: | None                                                                                              |  |  |  |  |

| Description:     | Move data from W register to register<br>'f'.                                                     |  |  |  |  |

| Words:           | 1                                                                                                 |  |  |  |  |

| Cycles:          | 1                                                                                                 |  |  |  |  |

| Example:         | MOVWF OPTION_REG                                                                                  |  |  |  |  |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F                                               |  |  |  |  |

|                  | After Instruction                                                                                 |  |  |  |  |

After Instruction OPTION\_REG = 0x4F W = 0x4F

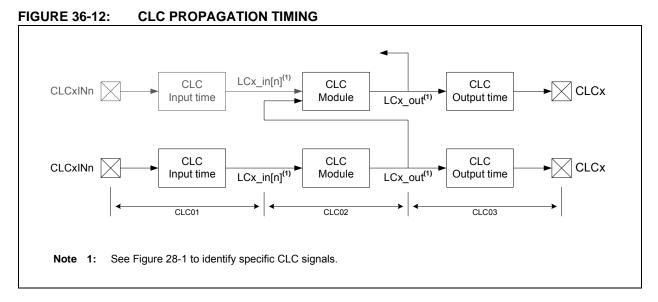

#### TABLE 36-14: CONFIGURATION LOGIC CELL (CLC) CHARACTERISTICS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |         |                                             |      |          |      |          |                          |

|----------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------|------|----------|------|----------|--------------------------|

| Param.<br>No.                                                                                                        | Sym.    | Characteristic                              | Min. | Тур†     | Max. | Units    | Conditions               |

| CLC01*                                                                                                               | TCLCIN  | CLC input time                              |      | 7        | OS17 | ns       | (Note 1)                 |

| CLC02*                                                                                                               | TCLC    | CLC module input to output progagation time |      | 24<br>12 | _    | ns<br>ns | VDD = 1.8V<br>VDD > 3.6V |

| CLC03*                                                                                                               | TCLCOUT | CLC output time Rise Time                   |      | OS18     |      | ns       | (Note 1)                 |

|                                                                                                                      |         | Fall Time                                   | _    | OS19     | _    | ns       | (Note 1)                 |

| CLC04*                                                                                                               | FCLCMAX | CLC maximum switching frequency             | _    | 45       | _    | MHz      |                          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: See Table 36-10 for OS17, OS18 and OS19 rise and fall times.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1 µF, TA = 25°C.

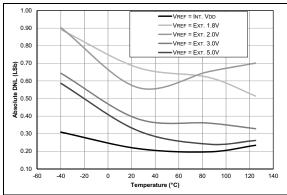

**FIGURE 37-127:** Absolute Value of DAC DNL Error, VDD = 5.0V, VREF = VDD, PIC16F1777/8/9 Only.

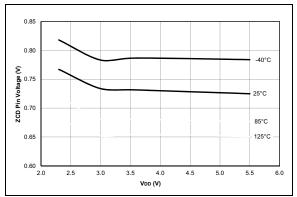

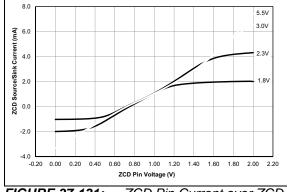

FIGURE 37-129: ZCD Pin Voltage, Typical Measured Values.

FIGURE 37-128: Absolute Value of DAC INL Error, VDD = 5.0V, VREF = VDD, PIC16F1777/8/9 Only.

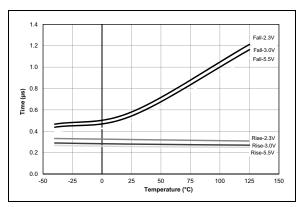

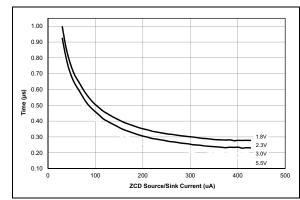

FIGURE 37-130: ZCD Response Time over Voltage, Typical Measured Values.

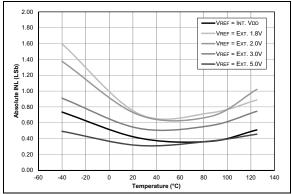

**FIGURE 37-132:** ZCD Pin Response Time over Current, Typical Measured Values from -40°C to 125°C.

**FIGURE 37-131:** ZCD Pin Current over ZCD Pin Voltage, Typical Measured Values from -40°C to 125°C.

#### 38.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 38.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.