Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 28x10b; D/A 4x5b, 4x10b                                                |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1777-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 3-18: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr | Name      | Bit 7         | Bit 6  | Bit 5             | Bit 4                                    | Bit 3        | Bit 2  | Bit 1 | Bit 0   | Value on<br>POR, BOR | Value on all other Resets |

|------|-----------|---------------|--------|-------------------|------------------------------------------|--------------|--------|-------|---------|----------------------|---------------------------|

| Bank | k 13      |               |        |                   |                                          |              |        |       |         |                      |                           |

| 68Ch | —         | Unimplemented |        |                   |                                          |              |        |       |         | —                    | —                         |

| 68Dh | COG1PHR   | —             | _      | COG Rising Edge   | Phase Delay Cou                          | nt Register  |        |       |         | 00 0000              | 00 0000                   |

| 68Eh | COG1PHF   | —             |        | COG Falling Edge  | Phase Delay Cou                          | unt Register |        |       |         | 00 0000              | 00 0000                   |

| 68Fh | COG1BLKR  | —             |        | COG Rising Edge   | DG Rising Edge Blanking Count Register   |              |        |       |         |                      | 00 0000                   |

| 690h | COG1BLKF  | —             | _      | COG Falling Edge  | DG Falling Edge Blanking Count Register  |              |        |       |         |                      | 00 0000                   |

| 691h | COG1DBR   | —             | _      | COG Rising Edge   | G Rising Edge Dead-band Count Register   |              |        |       |         |                      | 00 0000                   |

| 692h | COG1DBF   | —             |        | COG Falling Edge  | OG Falling Edge Dead-band Count Register |              |        |       |         | 00 0000              | 00 0000                   |

| 693h | COG1CON0  | EN            | LD     | — CS<1:0> MD<2:0> |                                          |              |        |       |         | 00-0 0000            | 00-0 0000                 |

| 694h | COG1CON1  | RDBS          | FDBS   | —                 | —                                        | POLD         | POLC   | POLB  | POLA    | 00 0000              | 00 0000                   |

| 695h | COG1RIS0  | RIS7          | RIS6   | RIS5              | RIS4                                     | RIS3         | RIS2   | RIS1  | RIS0    | 0000 0000            | 0000 0000                 |

| 696h | COG1RIS1  | RIS15         | RIS14  | RIS13             | RIS12                                    | RIS11        | RIS10  | RIS9  | RIS8    | 0000 0000            | 0000 0000                 |

| 697h | COG1RSIM0 | RSIM7         | RSIM6  | RSIM5             | RSIM4                                    | RSIM3        | RSIM2  | RSIM1 | RSIM0   | 0000 0000            | 0000 0000                 |

| 698h | COG1RSIM1 | RSIM15        | RSIM14 | RSIM13            | RSIM12                                   | RSIM11       | RSIM10 | RSIM9 | RSIM8   | 0000 0000            | 0000 0000                 |

| 699h | COG1FIS0  | FIS7          | FIS6   | FIS5              | FIS4                                     | FIS3         | FIS2   | FIS1  | FIS0    | 0000 0000            | 0000 0000                 |

| 69Ah | COG1FIS1  | FIS15         | FIS14  | FIS13             | FIS12                                    | FIS11        | FIS10  | FIS9  | FIS8    | 0000 0000            | 0000 0000                 |

| 69Bh | COG1FSIM0 | FSIM7         | FSIM6  | FSIM5             | FSIM4                                    | FSIM3        | FSIM2  | FSIM1 | FSIM0   | 0000 0000            | 0000 0000                 |

| 69Ch | COG1FSIM1 | FSIM15        | FSIM14 | FSIM13            | FSIM12                                   | FSIM11       | FSIM10 | FSIM9 | FSIM8   | 0000 0000            | 0000 0000                 |

| 69Dh | COG1ASD0  | ASE           | ARSEN  | ASDBI             | ASDBD<1:0> ASDAC<1:0>                    |              |        |       | 0001 01 | 0001 01              |                           |

| 69Eh | COG1ASD1  | AS7E          | AS6E   | AS5E              | AS4E                                     | AS3E         | AS2E   | AS1E  | AS0E    | 0000 0000            | 0000 0000                 |

| 69Fh | COG1STR   | SDATD         | SDATC  | SDATB             | SDATA                                    | STRD         | STRC   | STRB  | STRA    | 0000 0000            | 0000 0000                 |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: Unimplemented, read as '1'.

2:

Unimplemented on PIC16LF1777/8/9. 3: Unimplemented on PIC16(L)F1778.

# PIC16(L)F1777/8/9

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------|------------|-------|-------|-------|--------|---------------------|

| BORCON | SBOREN | BORFS  | _     | _          | _     |       |       | BORRDY | 121                 |

| PCON   | STKOVF | STKUNF |       | RWDT       | RMCLR | RI    | POR   | BOR    | 125                 |

| STATUS |        |        | _     | TO         | DC    | С     | 40    |        |                     |

| WDTCON | —      | —      |       | WDTPS<4:0> |       |       |       |        | 154                 |

#### TABLE 6-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

| R/W-0/0                                        | R/W-0/0                                                                                           | R/W-0/0                                         | U-0              | R/W-0/0      | R/W-0/0          | R/W-0/0  | R/W-0/0     |  |  |  |

|------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------|--------------|------------------|----------|-------------|--|--|--|

| OSFIE                                          | C2IE                                                                                              | C1IE                                            | COG1IE           | BCL1IE       | C4IE             | C3IE     | CCP2IE      |  |  |  |

| bit 7                                          |                                                                                                   |                                                 |                  |              |                  |          | bit         |  |  |  |

| Logondi                                        |                                                                                                   |                                                 |                  |              |                  |          |             |  |  |  |

| Legend:<br>R = Readable                        | e bit                                                                                             | W = Writable                                    | bit              | U = Unimpler | nented bit, read | l as '0' |             |  |  |  |

| u = Bit is uncl                                |                                                                                                   | x = Bit is unk                                  |                  | •            | at POR and BO    |          | ther Resets |  |  |  |

| '1' = Bit is set                               | 0                                                                                                 | '0' = Bit is cle                                |                  |              |                  |          |             |  |  |  |

|                                                |                                                                                                   |                                                 |                  |              |                  |          |             |  |  |  |

| bit 7                                          | OSFIE: Osci                                                                                       | llator Fail Interr                              | upt Enable bit   |              |                  |          |             |  |  |  |

|                                                |                                                                                                   | the Oscillator F<br>the Oscillator              |                  |              |                  |          |             |  |  |  |

| bit 6                                          | C2IE: Comp                                                                                        | arator C2 Interr                                | upt Enable bit   |              |                  |          |             |  |  |  |

|                                                |                                                                                                   | the Comparate                                   |                  |              |                  |          |             |  |  |  |

|                                                |                                                                                                   | 0 = Disables the Comparator C2 interrupt        |                  |              |                  |          |             |  |  |  |

| bit 5 C1IE: Comparator C1 Interrupt Enable bit |                                                                                                   |                                                 |                  |              |                  |          |             |  |  |  |

|                                                |                                                                                                   | the Comparato<br>the Comparato                  |                  |              |                  |          |             |  |  |  |

| bit 4                                          |                                                                                                   | DG1 Auto-Shuto                                  | •                |              |                  |          |             |  |  |  |

|                                                | 1 = COG1 ir                                                                                       | nterrupt enableo<br>nterrupt disable            | t                |              |                  |          |             |  |  |  |

| bit 3                                          |                                                                                                   | BCL1IE: MSSP Bus Collision Interrupt Enable bit |                  |              |                  |          |             |  |  |  |

|                                                |                                                                                                   | the MSSP Bus                                    |                  |              |                  |          |             |  |  |  |

|                                                | 0 = Disables                                                                                      | s the MSSP Bus                                  | s Collision inte | errupt       |                  |          |             |  |  |  |

| bit 2                                          | C4IE: TMR6                                                                                        | to T6PR Match                                   | Interrupt Ena    | ıble bit     |                  |          |             |  |  |  |

|                                                |                                                                                                   | the Comparate                                   |                  |              |                  |          |             |  |  |  |

| bit 1                                          |                                                                                                   | the Comparate                                   | •                |              |                  |          |             |  |  |  |

| DILI                                           | 1 <b>C3IE:</b> TMR4 to T4PR Match Interrupt Enable bit<br>1 = Enables the Comparator C3 interrupt |                                                 |                  |              |                  |          |             |  |  |  |

|                                                |                                                                                                   | the Comparate                                   |                  |              |                  |          |             |  |  |  |

| bit 0                                          | CCP2IE: CC                                                                                        | P2 Interrupt En                                 | able bit         |              |                  |          |             |  |  |  |

|                                                | 1 = Enables                                                                                       | the CCP2 inter                                  | rupt             |              |                  |          |             |  |  |  |

|                                                | 0 = Disables                                                                                      | s the CCP2 inte                                 | rrupt            |              |                  |          |             |  |  |  |

| Note: Bit                                      |                                                                                                   | ITCON register                                  | must be          |              |                  |          |             |  |  |  |

|                                                |                                                                                                   | peripheral inter                                |                  |              |                  |          |             |  |  |  |

## REGISTER 7-3: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0/0                                                                                         | R/W-0/0                            | R/W-0/0           | R/W-0/0                 | R/W-0/0                            | R/W-0/0       | R/W-0/0          | R/W-0/0      |  |  |  |

|-------------------------------------------------------------------------------------------------|------------------------------------|-------------------|-------------------------|------------------------------------|---------------|------------------|--------------|--|--|--|

| _                                                                                               | —                                  | —                 | _                       | PWM12IF <sup>(1)</sup>             | PWM11IF       | PWM6IF           | PWM5IF       |  |  |  |

| bit 7                                                                                           |                                    |                   |                         |                                    |               |                  | bit 0        |  |  |  |

| Legend:                                                                                         |                                    |                   |                         |                                    |               |                  |              |  |  |  |

| R = Readable                                                                                    | e bit                              | W = Writable      | bit                     | U = Unimplemented bit, read as '0' |               |                  |              |  |  |  |

| u = Bit is unc                                                                                  | hanged                             | x = Bit is unkr   | iown                    | -n/n = Value a                     | t POR and BOI | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set                                                                                |                                    | '0' = Bit is clea | ared                    |                                    |               |                  |              |  |  |  |

|                                                                                                 |                                    |                   |                         |                                    |               |                  |              |  |  |  |

| bit 7-4                                                                                         | bit 7-4 Unimplemented: Read as '0' |                   |                         |                                    |               |                  |              |  |  |  |

| bit 3                                                                                           | PWM12IF: P                         | WM12 Interrupt    | Flag bit <sup>(1)</sup> |                                    |               |                  |              |  |  |  |

|                                                                                                 | 1 = Interrupt i                    | is pending        | -                       |                                    |               |                  |              |  |  |  |

|                                                                                                 | 0 = Interrupt i                    | is not pending    |                         |                                    |               |                  |              |  |  |  |

| bit 2                                                                                           | PWM11IF: P\                        | WM11 Interrupt    | Flag bit                |                                    |               |                  |              |  |  |  |

|                                                                                                 | 1 = Interrupt i                    |                   |                         |                                    |               |                  |              |  |  |  |

|                                                                                                 |                                    | is not pending    |                         |                                    |               |                  |              |  |  |  |

| bit 1                                                                                           |                                    | /M6 Interrupt F   | ag bit                  |                                    |               |                  |              |  |  |  |

|                                                                                                 | 1 = Interrupt i                    |                   |                         |                                    |               |                  |              |  |  |  |

| <ul> <li>0 = Interrupt is not pending</li> <li>bit 0 PWM5IF: PWM5 Interrupt Flag bit</li> </ul> |                                    |                   |                         |                                    |               |                  |              |  |  |  |

| DIEU                                                                                            | 1 = Interrupt i                    | •                 | ag bit                  |                                    |               |                  |              |  |  |  |

|                                                                                                 |                                    | is not pending    |                         |                                    |               |                  |              |  |  |  |

| Note 1. Di                                                                                      | •                                  |                   |                         |                                    |               |                  |              |  |  |  |

| Note 1: Pl                                                                                      | C16(L)F1777/9                      | orny.             |                         |                                    |               |                  |              |  |  |  |

## REGISTER 7-13: PIR6: PERIPHERAL INTERRUPT REQUEST REGISTER 6

## PIC16(L)F1777/8/9

## 9.6 Register Definitions: Watchdog Control

#### REGISTER 9-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0             | U-0                                                  | R/W-0/0                                                          | R/W-1/1                        | R/W-0/0         | R/W-1/1          | R/W-1/1        | R/W-0/0      |  |  |

|-----------------|------------------------------------------------------|------------------------------------------------------------------|--------------------------------|-----------------|------------------|----------------|--------------|--|--|

| _               | —                                                    |                                                                  |                                | WDTPS<4:0>      | (1)              |                | SWDTEN       |  |  |

| bit 7           |                                                      | ·                                                                |                                |                 |                  |                | bit 0        |  |  |

|                 |                                                      |                                                                  |                                |                 |                  |                |              |  |  |

| Legend:         |                                                      |                                                                  |                                |                 |                  |                |              |  |  |

| R = Readable    | e bit                                                | W = Writable                                                     | bit                            | U = Unimpler    | mented bit, read | l as '0'       |              |  |  |

| u = Bit is unc  | hanged                                               | x = Bit is unki                                                  | nown                           | -m/n = Value    | at POR and BC    | R/Value at all | other Resets |  |  |

| '1' = Bit is se | t                                                    | '0' = Bit is cle                                                 | ared                           |                 |                  |                |              |  |  |

| bit 7-6         | Unimplom                                             | ented: Read as '                                                 | 0'                             |                 |                  |                |              |  |  |

| bit 5-1         | -                                                    | WDTPS<4:0>: Watchdog Timer Period Select bits <sup>(1)</sup>     |                                |                 |                  |                |              |  |  |

|                 |                                                      | Prescale Rate                                                    |                                |                 |                  |                |              |  |  |

|                 |                                                      |                                                                  | e in minimum                   | intonyal (1.32) |                  |                |              |  |  |

|                 | •                                                    | Reserved. Result                                                 | S III IIIIIIIIIIIIIIIIIIIIIIII |                 |                  |                |              |  |  |

|                 | •                                                    |                                                                  |                                |                 |                  |                |              |  |  |

|                 | •                                                    |                                                                  |                                |                 |                  |                |              |  |  |

|                 | 10011 <b>=</b> R                                     | Reserved. Result                                                 | s in minimum                   | interval (1:32) |                  |                |              |  |  |

|                 | 10010 = <b>1</b>                                     | :8388608 (2 <sup>23</sup> ) (                                    | Interval 256s                  | nominal)        |                  |                |              |  |  |

|                 | $10001 = 1:4194304 (2^{22})$ (Interval 128s nominal) |                                                                  |                                |                 |                  |                |              |  |  |

|                 | 10000 <b>= 1</b>                                     | :2097152 (2 <sup>21</sup> ) (                                    | Interval 64s n                 | ominal)         |                  |                |              |  |  |

|                 | 01111 = <b>1</b>                                     | :1048576 (2 <sup>20</sup> ) (                                    | Interval 32s n                 | ominal)         |                  |                |              |  |  |

|                 | 01110 = 1                                            | :524288 (2 <sup>19</sup> ) (Ir                                   | nterval 16s no                 | minal)          |                  |                |              |  |  |

|                 | 01101 = 1                                            | :262144 (2 <sup>18</sup> ) (Ir<br>:131072 (2 <sup>17</sup> ) (Ir | nterval 8s non                 | ninal)          |                  |                |              |  |  |

|                 |                                                      | :65536 (Interval                                                 |                                |                 |                  |                |              |  |  |

|                 |                                                      | :32768 (Interval                                                 |                                |                 |                  |                |              |  |  |

|                 |                                                      | :16384 (Interval                                                 |                                | nal)            |                  |                |              |  |  |

|                 |                                                      | :8192 (Interval 2                                                |                                | ,               |                  |                |              |  |  |

|                 |                                                      | :4096 (Interval 1                                                |                                |                 |                  |                |              |  |  |

|                 | 00110 <b>= 1</b>                                     | :2048 (Interval 6                                                | 4 ms nominal                   | )               |                  |                |              |  |  |

|                 |                                                      | :1024 (Interval 3                                                |                                | )               |                  |                |              |  |  |

|                 |                                                      | :512 (Interval 16                                                | ,                              |                 |                  |                |              |  |  |

|                 |                                                      | :256 (Interval 8 )                                               |                                |                 |                  |                |              |  |  |

|                 |                                                      | :128 (Interval 4 i<br>:64 (Interval 2 m                          |                                |                 |                  |                |              |  |  |

|                 |                                                      | :32 (Interval 1 m                                                | ,                              |                 |                  |                |              |  |  |

| bit 0           |                                                      | Software Enable                                                  | -                              | /atchdog Timer  | bit              |                |              |  |  |

|                 | If WDTE<1:                                           |                                                                  |                                | atonaog milei   | Sit              |                |              |  |  |

|                 | This bit is ig                                       |                                                                  |                                |                 |                  |                |              |  |  |

|                 | If WDTE<1:                                           |                                                                  |                                |                 |                  |                |              |  |  |

|                 | 1 = WDT is                                           |                                                                  |                                |                 |                  |                |              |  |  |

|                 | 0 = WDT is                                           |                                                                  |                                |                 |                  |                |              |  |  |

|                 | <u>If WDTE&lt;1:</u>                                 |                                                                  |                                |                 |                  |                |              |  |  |

|                 | This bit is ig                                       | nored.                                                           |                                |                 |                  |                |              |  |  |

|            |         |         |         |         | -       |         | -       | -       | -                   |

|------------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| Name       | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

| ANSELA     | —       | —       | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 177                 |

| INLVLA     | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 178                 |

| LATA       | LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   | 176                 |

| ODCONA     | ODA7    | ODA6    | ODA5    | ODA4    | ODA3    | ODA2    | ODA1    | ODA0    | 178                 |

| OPTION_REG | WPUEN   | INTEDG  | TMR0CS  | TMR0SE  | PSA     |         | PS<2:0> |         | 274                 |

| PORTA      | RA7     | RA6     | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 176                 |

| SLRCONA    | SLRA7   | SLRA6   | SLRA5   | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   | 178                 |

| TRISA      | TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 176                 |

| WPUA       | WPUA7   | WPUA6   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 177                 |

TABLE 11-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|------------|---------|---------|---------------------|

| CONFIG1 | 13:8 |         |         | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0> |         |         | 95                  |

| CONFIGI | 7:0  | CP      | MCLRE   | PWRTE    | WD       | TE<1:0>  | FOSC<2:0>  |         | >       | 95                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

## 11.6 Register Definitions: PORTC

## REGISTER 11-18: PORTC: PORTC REGISTER

| R/W-x/u                                 | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|-----------------------------------------|---------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| RC7                                     | RC6     | RC5               | RC4     | RC3                                                   | RC2     | RC1     | RC0     |  |  |

| bit 7                                   |         |                   |         |                                                       |         |         | bit 0   |  |  |

|                                         |         |                   |         |                                                       |         |         |         |  |  |

| Legend:                                 |         |                   |         |                                                       |         |         |         |  |  |

| R = Readable                            | bit     | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |         |                   |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared    |                                                       |         |         |         |  |  |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

### REGISTER 11-19: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **TRISC<7:0>:** PORTC Tri-State Control bits 1 = PORTC pin configured as an input (tri-stated) 0 = PORTC pin configured as an output

#### 16.2.6 ADC CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (refer to the TRIS register)

- Configure pin as analog (refer to the ANSEL register)

- Disable weak pull-ups either globally (refer to the OPTION\_REG register) or individually (refer to the appropriate WPUx register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- · Configure voltage reference

- · Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

**Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 16.4 "ADC Acquisition Requirements".

#### EXAMPLE 16-1: ADC CONVERSION

;This code block configures the ADC ; for polling, Vdd and Vss references, FRC ;oscillator and ANO input. ;Conversion start & polling for completion ; are included. ADCON1 BANKSEL : B'11110000' ;Right justify, FRC MOVLW ;oscillator MOVWF ADCON1 ;Vdd and Vss Vref BANKSEL TRISA ; BSF TRISA,0 ;Set RA0 to input BANKSEL ANSEL ; BSF ANSEL,0 ;Set RA0 to analog BANKSEL WPUA BCF WPUA,0 ;Disable weak ;pull-up on RA0 BANKSEL ADCON0 B'00000001' ;Select channel AN0 MOVLW MOVWF ADCON0 ;Turn ADC On CALL SampleTime ;Acquisiton delay BSF ADCON0, ADGO ;Start conversion ADCON0, ADGO ; Is conversion done? BTFSC GOTO \$-1 ;No, test again BANKSEL ADRESH ; ;Read upper 2 bits ADRESH,W MOVF RESULTHI MOVWE ;store in GPR space BANKSEL ADRESL ; MOVF ADRESL,W ;Read lower 8 bits MOVWF RESULTLO ;Store in GPR space

#### 23.6.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

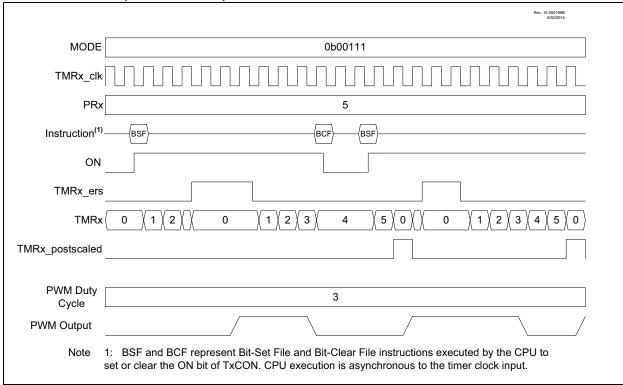

In the Level-Triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMRx\_ers, as shown in Figure 23-7. Selecting MODE<4:0> = 00110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 00111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMRx\_ers = 1. ON is controlled by BSF and BCF instructions. When ON = 0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the PRx value or two clock periods after the external Reset signal goes true and stays true. The timer starts counting, and the PWM output is set high, on either the clock following the PRx match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

FIGURE 23-7: LEVEL-TRIGGERED HARDWARE LIMIT MODE TIMING DIAGRAM (MODE = 00111)

#### 26.2 PWM Modes

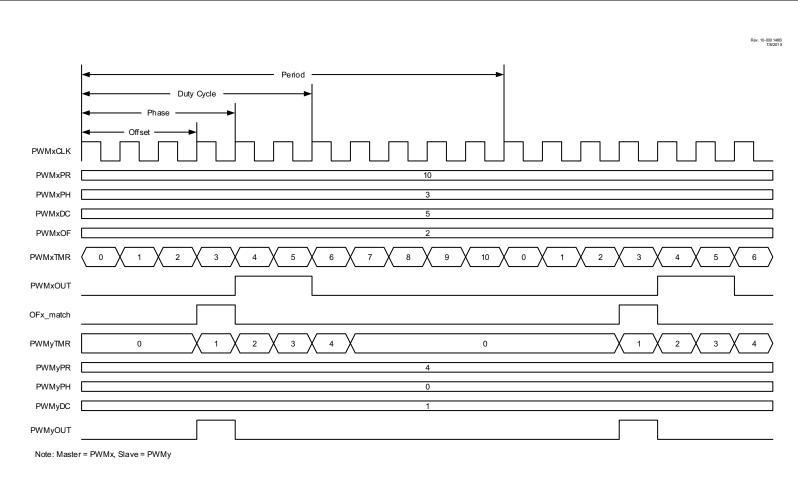

PWM modes are selected with MODE<1:0> bits of the PWMxCON register (Register 26-1).

In all PWM modes an offset match event can also be used to synchronize the PWMxTMR in three offset modes. See **Section 26.3 "Offset Modes"** for more information.

#### 26.2.1 STANDARD MODE

The Standard mode (MODE = 00) selects a single phase PWM output. The PWM output in this mode is determined by when the period, duty cycle, and phase counts match the PWMxTMR value. The start of the duty cycle occurs on the phase match and the end of the duty cycle occurs on the duty cycle match. The period match resets the timer. The offset match can also be used to synchronize the PWMxTMR in the offset modes. See **Section 26.3 "Offset Modes"** for more information.

Equation 26-1 is used to calculate the PWM period in Standard mode.

Equation 26-2 is used to calculate the PWM duty cycle ratio in Standard mode.

#### EQUATION 26-1: PWM PERIOD IN STANDARD MODE

$$Period = \frac{(PWMxPR + 1) \cdot Prescale}{PWM\_clock}$$

## EQUATION 26-2: PWM DUTY CYCLE IN STANDARD MODE

$$Duty Cycle = \frac{(PWMxDC - PWMxPH)}{PWMxPR + 1}$$

A detailed timing diagram for Standard mode is shown in Figure 26-4.

#### 26.2.2 SET ON MATCH MODE

The Set On Match mode (MODE = 01) generates an active output when the phase count matches the PWMxTMR value. The output stays active until the OUT bit of the PWMxCON register is cleared or the PWM module is disabled. The duty cycle count has no effect in this mode. The period count only determines the maximum PWMxTMR value above which no phase matches can occur.

The PWMxOUT bit can be used to set or clear the output of the PWM in this mode. Writes to this bit will take place on the next rising edge of the PWM\_clock after the bit is written.

A detailed timing diagram for Set On Match is shown in Figure 26-5.

#### 26.2.3 TOGGLE ON MATCH MODE

The Toggle On Match mode (MODE = 10) generates a 50% duty cycle PWM with a period twice as long as that computed for the standard PWM mode. Duty cycle count has no effect in this mode. The phase count determines how many PWMxTMR periods after a period event the output will toggle.

Writes to the OUT bit of the PWMxCON register will have no effect in this mode.

A detailed timing diagram for Toggle On Match is shown in Figure 26-6.

#### 26.2.4 CENTER ALIGNED MODE

The Center Aligned mode (MODE = 11) generates a PWM waveform that is centered in the period. In this mode the period is two times the PWMxPR count. The PWMxTMR counts up to the period value then counts back down to 0. The duty cycle count determines both the start and end of the active PWM output. The start of the duty cycle occurs at the match event when PWMxTMR is incrementing and the duty cycle ends at the match event when PWMxTMR is decrementing. The incrementing match value is the period count minus the duty cycle count. The decrementing match value is the incrementing match value plus 1.

Equation 26-3 is used to calculate the PWM period in Center Aligned mode.

#### EQUATION 26-3: PWM PERIOD IN CENTER ALIGNED MODE

$$Period = \frac{(PWMxPR + 1) \cdot 2 \cdot Prescale}{PWM\_clock}$$

Equation 26-4 is used to calculate the PWM duty cycle ratio in Center Aligned mode

#### EQUATION 26-4: PWM DUTY CYCLE IN CENTER ALIGNED MODE

$$Duty Cycle = \frac{PWMxDC \cdot 2}{(PWMxPR + 1) \cdot 2}$$

Writes to PWMxOUT will have no effect in this mode.

A detailed timing diagram for Center Aligned mode is shown in Figure 26-7.

## FIGURE 26-10: ONE-SHOT SLAVE RUN MODE WITH SYNC START TIMING DIAGRAM

PIC16(L)F1777/8/9

| U-0                  | R/W-0/0                                                                                                                                                                                                                                                                                                              | R/W-0/0                    | R/W-0/0 | U-0                                                   | U-0     | R/W-0/0 | R/W-0/0 |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| — PS<2:0>            |                                                                                                                                                                                                                                                                                                                      |                            | _       | _                                                     | CS<1:0> |         |         |  |  |

| bit 7                |                                                                                                                                                                                                                                                                                                                      |                            |         |                                                       | •       |         | bit 0   |  |  |

|                      |                                                                                                                                                                                                                                                                                                                      |                            |         |                                                       |         |         |         |  |  |

| Legend:              |                                                                                                                                                                                                                                                                                                                      |                            |         |                                                       |         |         |         |  |  |

| R = Readable bit     |                                                                                                                                                                                                                                                                                                                      | W = Writable bit           |         | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is unchanged |                                                                                                                                                                                                                                                                                                                      | x = Bit is unkno           | wn      | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set     |                                                                                                                                                                                                                                                                                                                      | '0' = Bit is clear         | ed      |                                                       |         |         |         |  |  |

|                      |                                                                                                                                                                                                                                                                                                                      |                            |         |                                                       |         |         |         |  |  |

| bit 7                | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                           |                            |         |                                                       |         |         |         |  |  |

| bit 6-4              | PS<2:0>: Clock Source Prescaler Select bits<br>111 = Divide clock source by 128<br>110 = Divide clock source by 64<br>101 = Divide clock source by 32<br>100 = Divide clock source by 16<br>011 = Divide clock source by 8<br>010 = Divide clock source by 4<br>001 = Divide clock source by 2<br>000 = No Prescaler |                            |         |                                                       |         |         |         |  |  |

| bit 3-2              | Unimplemen                                                                                                                                                                                                                                                                                                           | Unimplemented: Read as '0' |         |                                                       |         |         |         |  |  |

| bit 1-0              | CS<1:0>: Clock Source Select bits<br>11 = Reserved<br>10 = LFINTOSC (continues to operate during Sleep)<br>01 = HFINTOSC (continues to operate during Sleep)<br>00 = FOSC                                                                                                                                            |                            |         |                                                       |         |         |         |  |  |

## REGISTER 26-4: PWMxCLKCON: PWM CLOCK CONTROL REGISTER

## 27.3 Modes of Operation

#### 27.3.1 STEERED PWM MODES

In Steered PWM mode, the PWM signal derived from the input event sources is output as a single phase PWM which can be steered to any combination of the four COG outputs. Output steering takes effect on the instruction cycle following the write to the COGxSTR register.

Synchronous Steered PWM mode is identical to the Steered PWM mode except that changes to the output steering take effect on the first rising event after the COGxSTR register write. Static output data is not synchronized.

Steering mode configurations are shown in Figure 27-2 and Figure 27-3.

Steered PWM and Synchronous Steered PWM modes are selected by setting the MD<2:0> bits of the COGxCON0 register (Register 27-1) to '000' and '001', respectively.

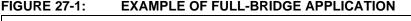

### 27.3.2 FULL-BRIDGE MODES

In both Forward and Reverse Full-Bridge modes, two of the four COG outputs are active and the other two are inactive. Of the two active outputs, one is modulated by the PWM input signal and the other is on at 100% duty cycle. When the direction is changed, the dead-band time is inserted to delay the modulated output. This gives the unmodulated driver time to shut down, thereby, preventing shoot-through current in the series connected power devices.

In Forward Full-Bridge mode, the PWM input modulates the COGxD output and drives the COGA output at 100%.

In Reverse Full-Bridge mode, the PWM input modulates the COGxB output and drives the COGxC output at 100%.

The full-bridge configuration is shown in Figure 27-4. Typical full-bridge waveforms are shown in Figure 27-12 and Figure 27-13.

Full-Bridge Forward and Full-Bridge Reverse modes are selected by setting the MD<2:0> bits of the COGxCON0 register to '010' and '011', respectively.

#### 27.10.3 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to resume operation:

- Software controlled

- Auto-restart

The restart method is selected with the ARSEN bit of the COGxASD0 register. Waveforms of a software controlled automatic restart are shown in Figure 27-15.

#### 27.10.3.1 Software Controlled Restart

When the ARSEN bit of the COGxASD0 register is cleared, software must clear the ASE bit to restart COG operation after an auto-shutdown event.

The COG will resume operation on the first rising event after the ASE bit is cleared. Clearing the shutdown state requires all selected shutdown inputs to be false, otherwise, the ASE bit will remain set.

#### 27.10.3.2 Auto-Restart

When the ARSEN bit of the COGxASD0 register is set, the COG will restart from the auto-shutdown state automatically.

The ASE bit will clear automatically and the COG will resume operation on the first rising event after all selected shutdown inputs go false.

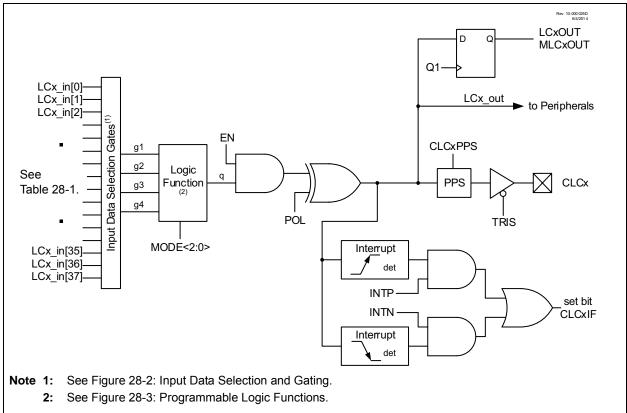

## 28.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLCx) provides programmable logic that operates outside the speed limitations of software execution. The logic cell takes up to 32 input signals and, through the use of configurable gates, reduces the 32 inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- · I/O pins

- Internal clocks

- · Peripherals

- · Register bits

The output can be directed internally to peripherals and to an output pin.

Refer to Figure 28-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

- Clocked J-K with Reset

#### FIGURE 28-1: CLCx SIMPLIFIED BLOCK DIAGRAM

sensitive timing inputs that occur during, and extend beyond, the one-shot period will be suspended until the end of the one-shot time.

#### 30.1.2.2 Rising Ramp

The Rising Ramp mode is identical to the Slope Compensation mode except that the ramps have a rising slope instead of a falling slope. One side of the internal capacitor is connected to the voltage input source and the other side is connected to the internal current source. The internal current source charges this capacitor at a programmable rate. As the capacitor charges, the capacitor voltage is added to the voltage source, producing a linear voltage rise at the required rate (see Figure 30-5). The ramp terminates and the capacitor is discharged when the set\_falling timing input goes true. The next ramp starts when the set\_rising timing input goes true.

Enabling the optional one-shot by setting the OS bit of the PRGxCON0 register ensures that the capacitor is fully discharged by overriding the set\_rising timing input and holding the shorting switch closed for at least the one-shot period, typically 50 ns. Edge sensitive timing inputs that occur during the one-shot period will be ignored. Level sensitive timing inputs that occur during, and extend beyond, the one-shot period will be suspended until the end of the one-shot time.

## 30.2 Enable, Ready, Go

The EN bit of the PRGxCON0 register enables the analog circuitry including the current sources. This permits preparing the PRG module for use and allowing it to become stable before putting it into operation. When the EN bit is set then the timing inputs are enabled so that initial ramp action can be determined before the GO bit is set. The capacitor shorting switch is closed when the EN bit is set and remains closed while the GO bit is zero.

The RDY bit of the PRGxCON1 register indicates that the analog circuits and current sources are stable.

The GO bit of the PRGxCON0 register enables the switch control circuits, thereby putting the PRG into operation. The GO transition from cleared to set triggers the one-shot, thereby extending the capacitor shorting switch closure for the one-shot period.

To ensure predictable operation, set the EN bit first then wait for the RDY bit to go high before setting the GO bit.

## 30.3 Independent Set\_rising and Set\_falling Timing Inputs

The timing inputs determine when the ramp starts and stops. In the Alternating Rising/Falling mode the ramp rises when the set\_rising input goes true and falls when the set\_falling input goes true. In the Slope Compensation and Rising Ramp modes the capacitor is discharged when the set\_falling timing input goes true and the ramp starts when the set\_rising timing input goes true. The set\_falling input dominates the set\_rising input.

## 30.4 Level and Edge Timing Sensitivity

The set\_rising and set\_falling timing inputs can be independently configured as either level or edge sensitive.

Level sensitive operation is useful when it is necessary to detect a timing input true state after an overriding condition ceases. For example, level sensitivity is useful for capacitor generated timing inputs that may be suppressed by the overriding action of the one-shot. With level sensitivity a capacitor output that changes during the one-shot period will be detected at the end of the one-shot time. With edge sensitivity the change would be ignored.

Edge sensitive operation is useful for periodic timing inputs such as those generated by PWMs and clocks. The duty cycle of a level sensitive periodic signal may interfere with the other timing input. Consider an Alternating Ramp mode with a level sensitive 50% PWM as the set\_rising timing source and a level sensitive comparator as the set\_falling timing source. If the comparator output reverses the ramp while the PWM signal is still high then the ramp will improperly reverse again when the comparator signal goes low. That same scenario with the set\_rising timing input set for edge sensitivity would properly change the ramp output to rising only on the rising edge of the PWM signal.

Set\_rising and set\_falling timing input edge sensitivity is selected with the respective REDG and FEDG bits of the PRGxCON1 register.

## 30.5 One-Shot Minimum Timing

The one-shot timer ensures a minimum capacitor discharge time in the Slope Compensation and Rising Ramp modes, and a minimum rising or falling ramp duration in the Alternating Ramp mode. Setting the OS bit of the PRGxCON0 register enables the one-shot timer.

## 30.6 DAC Voltage Sources

When using any of the DACs as the voltage source expect a voltage offset equal to the current setting times the DAC equivalent resistance. This will be a constant offset in the Slope Compensation and Ramp modes and a positive/negative step offset in the Alternating mode. To avoid this limitation, feed the DAC output to the PRG input through one of the op amps set for unity gain.

## 30.7 Operation During Sleep

The RG module is unaffected by Sleep.

## 30.8 Effects of a Reset

The RG module resets to a disabled condition.

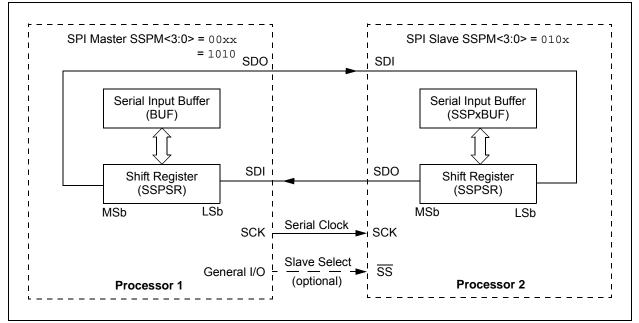

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPxBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full Detect bit, BF of the SSPxSTAT register, and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit WCOL of the SSPxCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPxBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various Status conditions.

FIGURE 32-5: SPI MASTER/SLAVE CONNECTION

#### 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |           |      |      |  |

|------------------------|-------------|-----------|------|------|--|

| Dimensio               | on Limits   | MIN       | NOM  | MAX  |  |

| Number of Pins         | N           | 40        |      |      |  |

| Pitch                  | е           | 0.40 BSC  |      |      |  |

| Overall Height         | A           | 0.45      | 0.50 | 0.55 |  |

| Standoff               | A1          | 0.00      | 0.02 | 0.05 |  |

| Contact Thickness      | A3          | 0.127 REF |      |      |  |

| Overall Width          | E           | 5.00 BSC  |      |      |  |

| Exposed Pad Width      | E2          | 3.60      | 3.70 | 3.80 |  |

| Overall Length         | D           | 5.00 BSC  |      |      |  |

| Exposed Pad Length     | D2          | 3.60      | 3.70 | 3.80 |  |

| Contact Width          | b           | 0.15      | 0.20 | 0.25 |  |

| Contact Length         | L           | 0.30      | 0.40 | 0.50 |  |

| Contact-to-Exposed Pad | K           | 0.20      | -    | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-156A Sheet 2 of 2

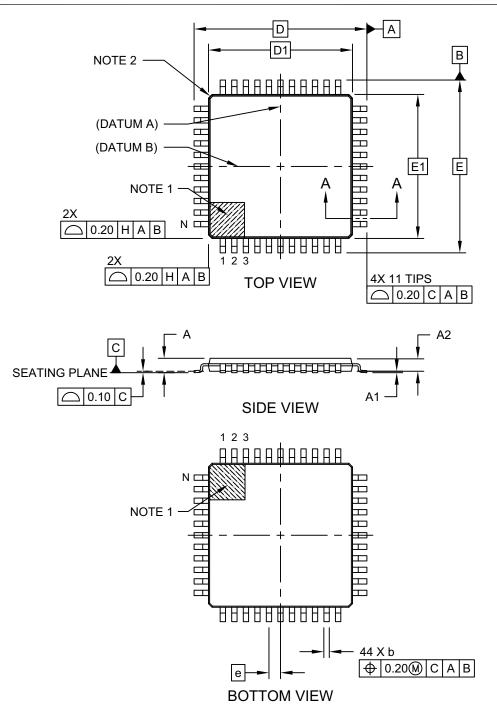

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-076C Sheet 1 of 2

## APPENDIX A: DATA SHEET REVISION HISTORY

## **Revision A (11/2015)**

Initial release of this document.

## **Revision B (10/2016)**

Updated Figures 14-1, 23-3, 23-8, 23-9, and 23-10; Registers 7-5, 7-11, 18-1, 19-1, 24-6, 27-11, 31-3, 31-4, 31-5, 31-6, 31-7, and 32-4; Section 32.6; Tables 3, 4, 3-4, 3-6, 3-7, 3-14, 3-15, 3-18, 12-1, 12-2, 12-3, 24-4, 25-5, 27-5, 27-6, 28-1, 32-4, 36-1, 36-2, 36-7 and 36-8.

Updated the Cover page.

Section 20.5 rewritten. Added Characterization Data.