Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

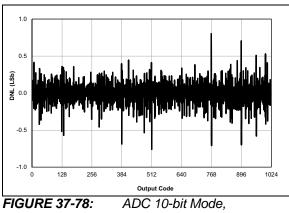

| Data Converters            | A/D 28x10b; D/A 4x5b, 4x10b                                                |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1777-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.6 Device ID and Revision ID

The 14-bit device ID word is located at 8006h and the 14-bit revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

#### 4.7 Register Definitions: Device and Revision

#### REGISTER 4-3: DEVID: DEVICE ID REGISTER

|          | R      | R | R               | R             | R                                                   | R                          |  |  |  |  |  |

|----------|--------|---|-----------------|---------------|-----------------------------------------------------|----------------------------|--|--|--|--|--|

|          |        |   | DEV<            | :13:8>        |                                                     |                            |  |  |  |  |  |

|          | bit 13 |   |                 |               |                                                     | bit 8                      |  |  |  |  |  |

|          |        |   |                 |               |                                                     |                            |  |  |  |  |  |

| R        | R      | R | R               | R             | R                                                   | R                          |  |  |  |  |  |

| DEV<7:0> |        |   |                 |               |                                                     |                            |  |  |  |  |  |

|          |        |   |                 |               |                                                     | bit 0                      |  |  |  |  |  |

|          | R      |   | bit 13<br>R R R | DEV<br>bit 13 | R         R         R         R         R         R | DEV<13:8>           bit 13 |  |  |  |  |  |

#### Legend:

R = Readable bit

'1' = Bit is set '0' = Bit is cleared

bit 13-0 **DEV<13:0>:** Device ID bits

| Device      | DEVID<13:0> Values                |  |  |  |  |  |  |  |  |

|-------------|-----------------------------------|--|--|--|--|--|--|--|--|

| PIC16F1777  | 11 0000 1000 1110 ( <b>308E</b> ) |  |  |  |  |  |  |  |  |

| PIC16F1778  | 11 0000 1000 1111 ( <b>308F</b> ) |  |  |  |  |  |  |  |  |

| PIC16F1779  | 11 0000 1001 0000 ( <b>3090</b> ) |  |  |  |  |  |  |  |  |

| PIC16LF1777 | 11 0000 1001 0001 ( <b>3091</b> ) |  |  |  |  |  |  |  |  |

| PIC16LF1778 | 11 0000 1001 0010 ( <b>3092</b> ) |  |  |  |  |  |  |  |  |

| PIC16LF1779 | 11 0000 1001 0011 ( <b>3093</b> ) |  |  |  |  |  |  |  |  |

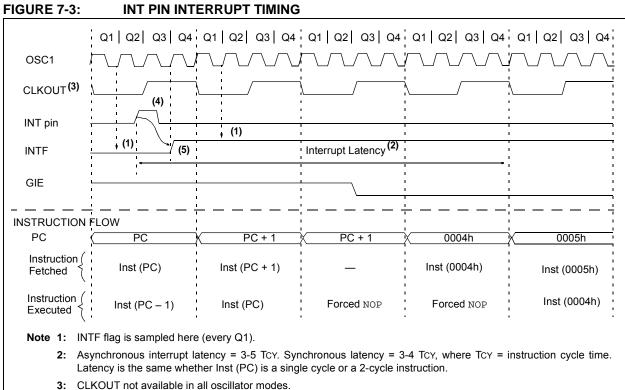

3: CLKOUT not available in all oscillator modes.

4: For minimum width of INT pulse, refer to AC specifications in Section 36.0 "Electrical Specifications"".

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### EXAMPLE 10-3: WRITING TO FLASH PROGRAM MEMORY

; This write routine assumes the following: ; 1. 64 bytes of data are loaded, starting at the address in DATA\_ADDR ; 2. Each word of data to be written is made up of two adjacent bytes in DATA\_ADDR, ; stored in little endian format ; 3. A valid starting address (the least significant bits = 00000) is loaded in ADDRH: ADDRL ; 4. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM) ; BCF INTCON,GIE ; Disable ints so required sequences will execute properly ; Bank 3 BANKSEL PMADRH MOVF ADDRH,W ; Load initial address MOVWF PMADRH MOVF ADDRL,W MOVWF PMADRL LOW DATA\_ADDR ; Load initial data address MOVLW MOVWF FSROL ; MOVLW HIGH DATA\_ADDR ; Load initial data address MOVWF FSR0H ; PMCON1,CFGS ; Not configuration space BCF BSF PMCON1,WREN ; Enable writes PMCON1,LWLO ; Only Load Write Latches BSF LOOP MOVIW FSR0++ ; Load first data byte into lower MOVWF PMDATT. ; ; Load second data byte into upper MOVIW FSR0++ MOVWF PMDATH MOVF ; Check if lower bits of address are '00000' PMADRL,W ; Check if we're on the last of 32 addresses XORLW 0x1F ANDLW 0x1F BTFSC STATUS,Z ; Exit if last of 32 words, GOTO START\_WRITE ; MOVLW 55h ; Start of required write sequence: MOVWF PMCON2 ; Write 55h Required Sequence MOVLW 0AAh MOVWF PMCON2 ; Write AAh BSF ; Set WR bit to begin write PMCON1,WR NOP ; NOP instructions are forced as processor ; loads program memory write latches NOP INCF PMADRL, F ; Still loading latches Increment address GOTO LOOP ; Write next latches START\_WRITE BCF PMCON1,LWLO ; No more loading latches - Actually start Flash program ; memory write MOVLW 55h ; Start of required write sequence: MOVWF PMCON2 ; Write 55h Required Sequence MOVLW 0AAh ; MOVWF PMCON2 ; Write AAh BSF PMCON1,WR ; Set WR bit to begin write NOP ; NOP instructions are forced as processor writes ; all the program memory write latches simultaneously NOP ; to program memory. ; After NOPs, the processor ; stalls until the self-write process in complete ; after write processor continues with 3rd instruction PMCON1,WREN BCF ; Disable writes BSF INTCON,GIE ; Enable interrupts

#### REGISTER 11-22: WPUC: WEAK PULL-UP PORTC REGISTER

| Legend: |         |         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

| bit 7   |         |         |         |         |         |         | bit 0   |

| WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| R/W-1/1 |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits<sup>(1, 2)</sup> 1 = Pull-up enabled 0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

#### REGISTER 11-23: ODCONC: PORTC OPEN-DRAIN CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODC7    | ODC6    | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    |

| bit 7   |         | •       |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| Legenu.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ODC<7:0>:** PORTC Open-Drain Enable bits

For RC<7:0> pins

- 1 = Port pin operates as open-drain drive (sink current only)

- 0 = Port pin operates as standard push-pull drive (source and sink current)

| U-0              | U-0                    | U-0                   | R/W-0/0      | U-0             | U-0              | R/W-0/0           | R/W-0/0       |

|------------------|------------------------|-----------------------|--------------|-----------------|------------------|-------------------|---------------|

|                  | —                      | DAC6LD <sup>(1)</sup> | DAC5LD       | —               | —                | DAC2LD            | DAC1LD        |

| bit 7            |                        |                       |              |                 |                  |                   | bit 0         |

|                  |                        |                       |              |                 |                  |                   |               |

| Legend:          |                        |                       |              |                 |                  |                   |               |

| R = Readable     |                        | W = Writable          |              |                 | mented bit, read |                   |               |

| u = Bit is uncha | anged                  | x = Bit is unkn       |              |                 | at POR and BO    |                   | ther Resets   |

| '1' = Bit is set |                        | '0' = Bit is clea     | ared         | q = value dep   | pends on config  | uration bits      |               |

|                  |                        |                       |              |                 |                  |                   |               |

| bit 7-6          | •                      | ted: Read as '        |              |                 |                  |                   |               |

| bit 5            |                        | C6 Double Buf         |              |                 |                  |                   |               |

|                  | 1 = DAC6RE<br>by hardw |                       | L values are | transfered to t | he double buffe  | r. Bit is cleared | automatically |

|                  | ,                      | FHL:DAC6REF           | L double buf | fers remain un  | changed.         |                   |               |

| bit 4            |                        | C5 Double Buf         |              |                 | U U              |                   |               |

|                  | 1 = DAC5RE<br>by hardw |                       | L values are | transfered to t | he double buffe  | r. Bit is cleared | automatically |

|                  | ,                      | FHL:DAC5REF           | L double buf | fers remain un  | changed.         |                   |               |

| bit 3-2          | Unimplemen             | ted: Read as '        | )'           |                 |                  |                   |               |

| bit 1            | DAC2LD: DA             | C2 Double Buf         | fer Load bit |                 |                  |                   |               |

|                  | 1 = DAC2RE<br>by hardw |                       | L values are | transfered to t | he double buffe  | r. Bit is cleared | automatically |

|                  | 0 = DAC2RE             | FHL:DAC2REF           | L double buf | fers remain un  | changed.         |                   |               |

| bit 0            | DAC1LD: DA             | C1 Double Buf         | fer Load bit |                 |                  |                   |               |

|                  | 1 = DAC1RE<br>by hardw |                       | L values are | transfered to t | he double buffe  | r. Bit is cleared | automatically |

|                  |                        | FHL:DAC1REF           | L double buf | fers remain un  | changed.         |                   |               |

| Note 1: PIC      | 16LF1777/9 on          | nly.                  |              |                 |                  |                   |               |

#### REGISTER 18-4: DACLD: DAC BUFFER LOAD REGISTER

| TABLE 18-3: SUMMARY OF | REGISTERS ASSOCIATED WITH THE DACX MODULE |

|------------------------|-------------------------------------------|

|------------------------|-------------------------------------------|

| Name                    | Bit 7 | Bit 6 | Bit 5 | Bit 4                  | Bit 3        | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |

|-------------------------|-------|-------|-------|------------------------|--------------|---------|--------|--------|---------------------|

| DAC1CON0                | EN    | FM    | OE1   | OE2                    | PSS          | <1:0>   | NSS    | <1:0>  | 249                 |

| DAC2CON0                | EN    | FM    | OE1   | OE2                    | PSS          | <1:0>   | NSS    | <1:0>  | 249                 |

| DAC5CON0                | EN    | FM    | OE1   | OE2                    | PSS          | <1:0>   | NSS    | <1:0>  | 249                 |

| DAC6CON0 <sup>(1)</sup> | EN    | FM    | OE1   | OE2                    | PSS          | <1:0>   | NSS    | <1:0>  | 249                 |

| DAC1REFH                |       |       | RE    | F<9:x> (x D            | epends on F  | M bit)  |        |        | 250                 |

| DAC2REFH                |       |       | RE    | EF<9:x> (x D           | epends on F  | M bit)  |        |        | 250                 |

| DAC5REFH                |       |       | RE    | EF<9:x> (x D           | epends on F  | M bit)  |        |        | 250                 |

| DAC6REFH <sup>(1)</sup> |       |       | RE    | EF<9:x> (x D           | epends on F  | M bit)  |        |        | 250                 |

| DAC1REFL                |       |       | REF   | = <x-1:0> (x [</x-1:0> | Depends on I | FM bit) |        |        | 250                 |

| DAC2REFL                |       |       | REF   | = <x-1:0> (x [</x-1:0> | Depends on I | =M bit) |        |        | 250                 |

| DAC5REFL                |       |       | REF   | = <x-1:0> (x [</x-1:0> | Depends on I | -M bit) |        |        | 250                 |

| DAC6REFL <sup>(1)</sup> |       |       | REF   | = <x-1:0> (x [</x-1:0> | Depends on I | =M bit) |        |        | 250                 |

| DACLD                   |       | _     | _     | DAC5LD                 | _            |         | DAC2LD | DAC1LD | 251                 |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used with the DACx module.

**Note 1:** PIC16LF1777/9 only.

| Name                    | Bit 7                 | Bit 6                 | Bit 5  | Bit 4               | Bit 3    | Bit 2    | Bit 1  | Bit 0  | Register<br>on Page |

|-------------------------|-----------------------|-----------------------|--------|---------------------|----------|----------|--------|--------|---------------------|

| ANSELA                  | _                     | _                     | ANSA5  | ANSA4               | ANSA3    | ANSA2    | ANSA1  | ANSA0  | 177                 |

| ANSELB                  | _                     | _                     | ANSB5  | ANSB4               | ANSB3    | ANSB2    | ANSB1  | ANSB0  | 182                 |

| ANSELC                  | ANSC7                 | ANSC6                 | ANSC5  | ANSC4               | ANSC3    | ANSC2    | _      | _      | 187                 |

| CM1CON0                 | ON                    | OUT                   | _      | POL                 | ZLF      | Reserved | HYS    | SYNC   | 258                 |

| CM2CON0                 | ON                    | OUT                   | _      | POL                 | ZLF      | Reserved | HYS    | SYNC   | 258                 |

| CM3CON0                 | ON                    | OUT                   | _      | POL                 | ZLF      | Reserved | HYS    | SYNC   | 258                 |

| CM4CON0                 | ON                    | OUT                   | _      | POL                 | ZLF      | Reserved | HYS    | SYNC   | 258                 |

| CM5CON0                 | ON                    | OUT                   | _      | POL                 | ZLF      | Reserved | HYS    | SYNC   | 258                 |

| CM6CON0                 | ON                    | OUT                   | _      | POL                 | ZLF      | Reserved | HYS    | SYNC   | 258                 |

| CM1CON1                 | _                     | _                     | _      | _                   | _        | _        | INTP   | INTN   | 259                 |

| CM2CON1                 | _                     | _                     | _      | _                   | _        | _        | INTP   | INTN   | 259                 |

| CM3CON1                 |                       |                       | _      | _                   | _        | _        | INTP   | INTN   | 259                 |

| CM4CON1                 | _                     | _                     |        | _                   | _        | _        | INTP   | INTN   | 259                 |

| CM5CON1                 |                       |                       | _      | _                   | _        | _        | INTP   | INTN   | 259                 |

| CM6CON1                 | _                     | _                     |        | _                   | _        | _        | INTP   | INTN   | 259                 |

| CM7CON1 <sup>(1)</sup>  | _                     | _                     |        | _                   | _        | _        | INTP   | INTN   | 259                 |

| CM8CON1 <sup>(1)</sup>  | _                     | _                     |        | _                   | _        | _        | INTP   | INTN   | 259                 |

| CM1NSEL                 | _                     | _                     | _      | _                   |          | NCH      | <3:0>  |        | 260                 |

| CM2NSEL                 | _                     | _                     | _      | _                   |          | NCH      | <3:0>  |        | 260                 |

| CM3NSEL                 | _                     | _                     | _      | _                   |          | NCH      | <3:0>  |        | 260                 |

| CM4NSEL                 | _                     | _                     | _      | _                   |          |          | <3:0>  |        | 260                 |

| CM5NSEL                 | _                     | _                     | _      | _                   | NCH<3:0> |          |        |        | 260                 |

| CM6NSEL                 | _                     | _                     | _      | _                   | NCH<3:0> |          |        |        | 260                 |

| CM7NSEL <sup>(1)</sup>  | _                     | _                     | _      | _                   | NCH<3:0> |          |        |        | 260                 |

| CM8NSEL <sup>(1)</sup>  | _                     | _                     | _      | _                   |          |          | <3:0>  |        | 260                 |

| CM1PSEL                 | _                     | _                     |        | _                   |          |          | <3:0>  |        | 261                 |

| CM2PSEL                 | _                     | _                     |        | _                   |          |          | <3:0>  |        | 261                 |

| CM3PSEL                 | _                     | _                     | _      | _                   |          | PCH      | <3:0>  |        | 261                 |

| CM4PSEL                 | _                     | _                     | _      | _                   |          | PCH      | <3:0>  |        | 261                 |

| CM5PSEL                 | _                     | _                     | _      | _                   |          | PCH      | <3:0>  |        | 261                 |

| CM6PSEL                 | _                     | _                     | _      | _                   |          | PCH      | <3:0>  |        | 261                 |

| CM7PSEL <sup>(1)</sup>  | _                     | _                     | _      | _                   |          | PCH      | <3:0>  |        | 261                 |

| CM8PSEL <sup>(1)</sup>  | _                     | _                     |        | _                   |          | PCH      | <3:0>  |        | 261                 |

| CMOUT                   | MC8OUT <sup>(1)</sup> | MC7OUT <sup>(1)</sup> | MC6OUT | MC5OUT              | MC4OUT   | MC3OUT   | MC2OUT | MC1OUT | 262                 |

| FVRCON                  | FVREN                 | FVRRDY                | TSEN   | TSRNG               |          | /R<1:0>  |        | R<1:0> | 223                 |

| DAC1CON0                | EN                    | FM                    | OE1    | OE2                 | PSS      | <1:0>    | NSS    | <1:0>  | 249                 |

| DAC2CON0                | EN                    | FM                    | OE1    | OE2                 | PSS      | <1:0>    | NSS    | <1:0>  | 249                 |

| DAC5CON0                | EN                    | FM                    | OE1    | OE2                 | PSS      | <1:0>    | NSS    | <1:0>  | 249                 |

| DAC6CON0 <sup>(1)</sup> | EN                    | FM                    | OE1    | OE2                 | PSS      | <1:0>    | NSS    | <1:0>  | 249                 |

| DAC3CON0                | EN                    | _                     | OE1    | OE2                 | PSS      | <1:0>    | NSS    | <1:0>  | 244                 |

| DAC4CON0                | EN                    | _                     | OE1    | OE2                 | PSS      | <1:0>    | NSS    | <1:0>  | 244                 |

| DAC7CON0                | EN                    |                       | OE1    | OE2                 | PSS      | <1:0>    | NSS    | <1:0>  | 244                 |

| DAC8CON0 <sup>(1)</sup> | EN                    |                       | OE1    | OE2                 |          | <1:0>    | NSS    | <1:0>  | 244                 |

| DAC3REF                 |                       |                       |        |                     | L        | REF<4:0> | L      |        | 245                 |

| DAC4REF                 |                       |                       |        |                     |          | REF<4:0> |        |        | 245                 |

| DAC7REF                 |                       |                       |        |                     |          | REF<4:0> |        |        | 245                 |

| DAC8REF <sup>(1)</sup>  |                       |                       |        |                     |          | REF<4:0> |        |        | 245                 |

|                         |                       |                       |        | I<br>REF<9:x> (x De |          |          |        |        | -                   |

#### **TABLE 19-6:** SUMMARY OF REGISTERS ASSOCIATED WITH COMPARATOR MODULE

Legend:

- = unimplemented location, read as '0'. Shaded cells are unused by the comparator module.

Note

1:

PIC16LF1777/9 only.

| U-0             | U-0             | U-0                                | U-0             | R/W-0/0         | R/W-0/0           | R/W-0/0           | R/W-0/0   |

|-----------------|-----------------|------------------------------------|-----------------|-----------------|-------------------|-------------------|-----------|

| _               | _               | _                                  | _               | OFIE            | PHIE              | DCIE              | PRIE      |

| bit 7           | ·               | •                                  | •               | ·               |                   |                   | bit 0     |

|                 |                 |                                    |                 |                 |                   |                   |           |

| Legend:         |                 |                                    |                 |                 |                   |                   |           |

| R = Readabl     | le bit          | W = Writable b                     | bit             | U = Unimplem    | ented bit, read a | as '0'            |           |

| u = Bit is und  | changed         | x = Bit is unkno                   | own             | -n/n = Value at | POR and BOR       | /Value at all oth | er Resets |

| '1' = Bit is se | et              | '0' = Bit is clea                  | red             |                 |                   |                   |           |

|                 |                 |                                    |                 |                 |                   |                   |           |

| bit 7-4         | Unimplement     | ed: Read as '0'                    |                 |                 |                   |                   |           |

| bit 3           | OFIE: Offset I  | nterrupt Enable                    | bit             |                 |                   |                   |           |

|                 |                 | CPU on Offset Match                |                 |                 |                   |                   |           |

|                 |                 | errupt CPU on (                    |                 |                 |                   |                   |           |

| bit 2           |                 | Interrupt Enable<br>CPU on Phase N |                 |                 |                   |                   |           |

|                 |                 | terrupt CPU on I                   |                 |                 |                   |                   |           |

| bit 1           | DCIE: Duty C    | vcle Interrupt Er                  | nable bit       |                 |                   |                   |           |

|                 | 1 = Interrupt ( | CPU on Duty Cycle Match            |                 |                 |                   |                   |           |

|                 | 0 = Do not int  | errupt CPU on I                    | Duty Cycle Mate | h               |                   |                   |           |

| bit 0           |                 | Interrupt Enable                   |                 |                 |                   |                   |           |

|                 |                 | CPU on Period I<br>errupt CPU on I |                 |                 |                   |                   |           |

|                 |                 |                                    |                 |                 |                   |                   |           |

#### REGISTER 26-2: PWMxINTE: PWM INTERRUPT ENABLE REGISTER

#### REGISTER 26-3: PWMxINTF: PWM INTERRUPT REQUEST REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|------------|------------|------------|------------|

| _     | _   | —   | —   | OFIF       | PHIF       | DCIF       | PRIF       |

| bit 7 |     |     |     |            |            |            | bit 0      |

| Legend:                    |                      |                                                       |

|----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by har | dware                | HS = Bit is set by hardware                           |

| R = Readable bit           | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged       | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set           | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'                             |

|---------|--------------------------------------------------------|

| bit 3   | <b>OFIF</b> : Offset Interrupt Flag bit <sup>(1)</sup> |

|         | 1 = Offset Match Event occurred                        |

|         | 0 = Offset Match Event did not occur                   |

| bit 2   | PHIF: Phase Interrupt Flag bit <sup>(1)</sup>          |

|         | 1 = Phase Match Event occurred                         |

|         | 0 = Phase Match Event did not occur                    |

| bit 1   | DCIF: Duty Cycle Interrupt Flag bit <sup>(1)</sup>     |

|         | 1 = Duty Cycle Match Event occurred                    |

|         | 0 = Duty Cycle Match Event did not occur               |

| bit 0   | PRIF: Period Interrupt Flag bit <sup>(1)</sup>         |

|         | 1 = Period Match Event occurred                        |

|         | 0 = Period Match Event did not occur                   |

|         |                                                        |

**Note 1:** Bit is forced clear by hardware while module is disabled (EN = 0).

#### REGISTER 29-4: OPAxPCHS: OP AMP POSITIVE CHANNEL SOURCE SELECT REGISTER

| bit 7 |     |     |     |         |         |         |         |

|-------|-----|-----|-----|---------|---------|---------|---------|

| bit 7 |     |     |     |         |         |         |         |

| bit 7 |     |     |     |         |         |         |         |

|       |     |     |     |         |         |         | bit 0   |

| —     | _   | —   | —   |         | PCH     | <3:0>   |         |

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 PCH<3:0>: Op Amp Non-Inverting Input Channel Selection bits See Table 29-5: Non-Inverting Input Sources

#### TABLE 29-5: NON-INVERTING INPUT SOURCES

| NCH<3:0> | OPA1                 | OPA2                 | OPA3                    | OPA4 <sup>(1)</sup>  |

|----------|----------------------|----------------------|-------------------------|----------------------|

| 1111     | Reserved. Do not use | Reserved. Do not use | Reserved. Do not use    | Reserved. Do not use |

| 1110     | Reserved. Do not use | Reserved. Do not use | Reserved. Do not use    | Reserved. Do not use |

| 1101     | Reserved. Do not use | Reserved. Do not use | Reserved. Do not use    | Reserved. Do not use |

| 1100     | Reserved. Do not use | Reserved. Do not use | Reserved. Do not use    | Reserved. Do not use |

| 1011     | Reserved. Do not use | Reserved. Do not use | Reserved. Do not use    | Reserved. Do not use |

| 1010     | Reserved. Do not use | Reserved. Do not use | Reserved. Do not use    | Reserved. Do not use |

| 1001     | Reserved. Do not use | Reserved. Do not use | Reserved. Do not use    | Reserved. Do not use |

| 1000     | PRG2_out             | PRG2_out             | PRG4_out <sup>(1)</sup> | PRG4_out             |

| 0111     | PRG1_out             | PRG1_out             | PRG3_out                | PRG3_out             |

| 0110     | FVR_Buffer1          | FVR_Buffer1          | FVR_Buffer2             | FVR_Buffer2          |

| 0101     | DAC4_out             | DAC4_out             | DAC8_out <sup>(1)</sup> | DAC8_out             |

| 0100     | DAC3_out             | DAC3_out             | DAC7_out                | DAC7_out             |

| 0011     | DAC2_out             | DAC2_out             | DAC6_out <sup>(1)</sup> | DAC6_out             |

| 0010     | DAC1_out             | DAC1_out             | DAC5_out                | DAC5_out             |

| 0001     | OPA1IN1+             | OPA2IN1+             | OPA3IN1+ <sup>(1)</sup> | OPA4IN1+             |

| 0000     | OPA1IN0+             | OPA2IN0+             | OPA3IN0+                | OPA4IN0+             |

Note 1: PIC16(L)F1777/9 only.

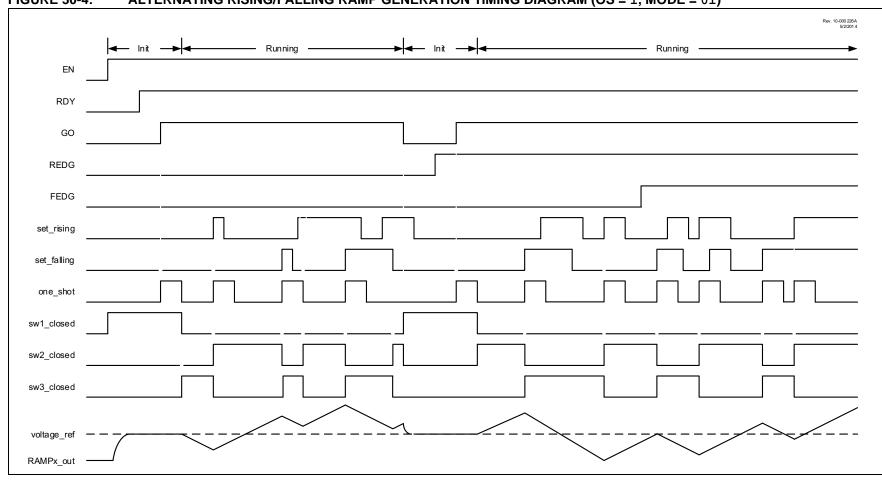

#### FIGURE 30-4: ALTERNATING RISING/FALLING RAMP GENERATION TIMING DIAGRAM (OS = 1, MODE = 01)

PIC16(L)F1777/8/9

| U-0            | U-0                                         | R/W-0/0          | R/W-0/0          | U-0             | U-0                | R/W-0/0          | R/W-0/0     |

|----------------|---------------------------------------------|------------------|------------------|-----------------|--------------------|------------------|-------------|

| _              | _                                           | CHPOL            | CHSYNC           | _               | —                  | CLPOL            | CLSYNC      |

| bit 7          |                                             |                  |                  |                 |                    |                  | bit 0       |

|                |                                             |                  |                  |                 |                    |                  |             |

| Legend:        |                                             |                  |                  |                 |                    |                  |             |

| R = Readab     | ole bit                                     | W = Writable     | bit              | U = Unimpler    | mented bit, read   | as '0'           |             |

| u = Bit is un  | ichanged                                    | x = Bit is unki  | nown             | -n/n = Value a  | at POR and BO      | R/Value at all c | ther Resets |

| '1' = Bit is s | et                                          | '0' = Bit is cle | ared             |                 |                    |                  |             |

|                |                                             |                  |                  |                 |                    |                  |             |

| bit 7-6        | Unimplemen                                  | ted: Read as '   | 0'               |                 |                    |                  |             |

| bit 5          | CHPOL: Mod                                  | lulation High C  | arrier Polarity  | Select bit      |                    |                  |             |

|                | 1 = Selected                                | high carrier so  | ource is inverte | ed              |                    |                  |             |

|                | 0 = Selected                                | high carrier so  | ource is not inv | verted          |                    |                  |             |

| bit 4          | CHSYNC: Mo                                  | odulation High   | Carrier Synch    | ronization Ena  | ble bit            |                  |             |

|                |                                             |                  |                  |                 | efore allowing a   | switch to the le | ow carrier  |

|                |                                             | -                | -                | to the high car | rier               |                  |             |

| bit 3-2        | Unimplemen                                  | ted: Read as '   | 0'               |                 |                    |                  |             |

| bit 1          | CLPOL: Mod                                  | ulation Low Ca   | rrier Polarity   | Select bit      |                    |                  |             |

|                | 1 = Selected low carrier source is inverted |                  |                  |                 |                    |                  |             |

|                | 0 = Selected                                | low carrier sou  | urce is not inv  | erted           |                    |                  |             |

| bit 0          | CLSYNC: Mo                                  | odulation Low 0  | Carrier Synchr   | onization Enab  | ole bit            |                  |             |

|                |                                             |                  |                  |                 | fore allowing a    | switch to the hi | gh carrier  |

|                | 0 = Modulato                                | or output is not | synchronized     | to the low carr | ier <sup>(1)</sup> |                  |             |

|                |                                             |                  |                  |                 |                    |                  |             |

#### REGISTER 31-2: MDxCON1: MODULATION CONTROL REGISTER 1

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

#### REGISTER 31-3: MDxSRC: MODULATION SOURCE CONTROL REGISTER

| U-0   | U-0 | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   |     |         |         | MS<4:0> |         |         |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **MS<4:0>** Modulation Source Selection bits See Table 31-4 or Table 31-5.

#### 33.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VoL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(baud rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 33-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 33.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 33-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXxREG register.

#### 33.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXxSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

Note: The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 33.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXxREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXxREG until the Stop bit of the previous character has been transmitted. The pending character in the TXxREG is then transferred to the TSR in one TcY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXxREG.

#### 33.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0', which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 33.5.1.2 "Clock Polarity"**.

#### 33.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXxREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXxREG. The TXIF flag bit is not cleared immediately upon writing TXxREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXxREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXxREG is empty, regardless of the state of the TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXxREG.

### 33.6 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 33.6.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCxSTA and TXxSTA Control registers must be configured for Synchronous Slave Reception (see Section 33.5.2.4 "Synchronous Slave Reception Set-up:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCxREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

#### 33.6.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- The RCxSTA and TXxSTA Control registers must be configured for synchronous slave transmission (see Section 33.5.2.2 "Synchronous Slave Transmission Set-up:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXxREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXxREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXxREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                  |

| Operation:       | See description below                                                                                                                                                                                              |

| Status Affected: | С                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

| SUBLW            | Subtract V                                                                                                               | V from literal    |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|

| Syntax:          | [label] S                                                                                                                | UBLW k            |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                        | $0 \le k \le 255$ |  |  |  |

| Operation:       | $k - (W) \to (V$                                                                                                         | V)                |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                 | C, DC, Z          |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the 8-bit literal 'k'. The result is placed in the W register. |                   |  |  |  |

|                  | <b>C</b> = 0                                                                                                             | W > k             |  |  |  |

|                  | <b>C =</b> 1                                                                                                             | $W \le k$         |  |  |  |

|                  | DC = 0                                                                                                                   | W<3:0> > k<3:0>   |  |  |  |

**DC =** 1

$W<3:0> \le k<3:0>$

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                                    |

| Operands:        | None                                                                                                                                                                                                                                             |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{WDT} \text{ prescaler}, \\ 1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                          |

| Status Affected: | TO, PD                                                                                                                                                                                                                                           |

| Description:     | The power-down Status bit, $\overline{\text{PD}}$ is<br>cleared. Time-out Status bit, $\overline{\text{TO}}$ is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into Sleep mode<br>with the oscillator stopped. |

| SUBWF                  | Subtract W from f                                                                                                                                                                                                  |                 |  |  |  |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Syntax:                | [label] SL                                                                                                                                                                                                         | IBWF f,d        |  |  |  |  |  |

| Operands:              | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                 |                 |  |  |  |  |  |

| Operation:             | (f) - (W) $\rightarrow$ (d                                                                                                                                                                                         | estination)     |  |  |  |  |  |

| Status Affected:       | C, DC, Z                                                                                                                                                                                                           |                 |  |  |  |  |  |

| Description:           | Subtract (2's complement method) W<br>register from register 'f'. If 'd' is '0', the<br>result is stored in the W register. If 'd' is<br>'1', the result is stored back in register<br>'f.<br>$C = 0 \qquad W > f$ |                 |  |  |  |  |  |

|                        |                                                                                                                                                                                                                    |                 |  |  |  |  |  |

|                        | $W \leq f$                                                                                                                                                                                                         |                 |  |  |  |  |  |

|                        | DC = 0                                                                                                                                                                                                             | W<3:0> > f<3:0> |  |  |  |  |  |

| DC = 1 W<3:0> ≤ f<3:0> |                                                                                                                                                                                                                    |                 |  |  |  |  |  |

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                     |

| Status Affected: | C, DC, Z                                                                                                                                                                                          |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's<br>complement method). If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'. |

| PIC16LI | F1777/8/9       | Standa | rd Operat | ing Conc | litions (un | less oth | erwise stated)                                               |

|---------|-----------------|--------|-----------|----------|-------------|----------|--------------------------------------------------------------|

| PIC16F  | 1777/8/9        |        |           |          |             |          |                                                              |

| Param   | Device          | Min.   | Typt      | Max.     | Units       |          | Conditions                                                   |

| No.     | Characteristics | wiiri. | турт      |          |             | Vdd      | Note                                                         |

| D009    | LDO Regulator   | —      | 75        | _        | μA          | _        | High-Power mode, normal operation                            |

|         |                 | —      | 15        | _        | μA          | _        | Sleep, VREGCON<1> = 0                                        |

|         |                 | _      | 0.3       |          | μA          |          | Sleep, VREGCON<1> = 1                                        |

| D010    |                 | _      | 8         | 25       | μA          | 1.8      | Fosc = 32 kHz,                                               |

|         |                 | _      | 12        | 30       | μA          | 3.0      | LP Oscillator mode (Note 4),<br>-40°C $\leq$ TA $\leq$ +85°C |

| D010    |                 | —      | 21        | 30       | μA          | 2.3      | Fosc = 32 kHz,                                               |

|         |                 | —      | 25        | 34       | μA          | 3.0      | LP Oscillator mode (Note 4,5)                                |

|         |                 | —      | 26        | 35       | μA          | 5.0      | $-40^{\circ}C \le TA \le +85^{\circ}C$                       |

| D012    |                 | _      | 210       | 440      | μA          | 1.8      | Fosc = 4 MHz,                                                |

|         |                 | —      | 390       | 620      | μA          | 3.0      | XT Oscillator mode                                           |

| D012    |                 | —      | 320       | 530      | μA          | 2.3      | Fosc = 4 MHz,                                                |

|         |                 |        | 430       | 680      | μA          | 3.0      | XT Oscillator mode (Note 5)                                  |

|         |                 | —      | 530       | 790      | μA          | 5.0      |                                                              |

| D014    |                 | _      | 170       | 380      | μA          | 1.8      | Fosc = 4 MHz,                                                |

|         |                 | —      | 320       | 550      | μA          | 3.0      | External Clock (ECM),<br>Medium Power mode                   |

| D014    |                 | —      | 250       | 513      | μA          | 2.3      | Fosc = 4 MHz,                                                |

|         |                 | —      | 360       | 645      | μA          | 3.0      | External Clock (ECM),<br>Medium Power mode                   |

|         |                 | —      | 430       | 735      | μA          | 5.0      |                                                              |

| D015    |                 | _      | 2.5       | 3.8      | mA          | 3.0      | Fosc = 32 MHz,                                               |

|         |                 | —      | 3.1       | 4.0      | mA          | 3.6      | External Clock (ECH),<br>High-Power mode (Note 5)            |

| D015    |                 | —      | 2.5       | 4.3      | mA          | 3.0      | Fosc = 32 MHz,                                               |

|         |                 | —      | 2.7       | 4.6      | mA          | 5.0      | External Clock (ECH),<br>High-Power mode <b>(Note 5)</b>     |

#### TABLE 36-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup>

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For EXTRC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: FVR and BOR are disabled.

5: 8 MHz crystal/oscillator with 4x PLL enabled.

### TABLE 36-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup> (CONTINUED)

| PIC16LF | 1777/8/9        | Standard Operating Conditions (unless otherwise stated) |        |      |       |     |                             |  |

|---------|-----------------|---------------------------------------------------------|--------|------|-------|-----|-----------------------------|--|

| PIC16F1 | 777/8/9         |                                                         |        |      |       |     |                             |  |

| Param   | Device          | Min.                                                    | Turnet | Max. | Units |     | Conditions                  |  |

| No.     | Characteristics | win.                                                    | Тур†   | wax. | Units | VDD | Note                        |  |

| D017    |                 | —                                                       | 115    | 190  | μA    | 1.8 | Fosc = 500 kHz,             |  |

|         |                 | _                                                       | 145    | 320  | μA    | 3.0 | MFINTOSC mode               |  |

| D017    |                 | _                                                       | 160    | 215  | μA    | 2.3 | Fosc = 500 kHz,             |  |

|         |                 |                                                         | 180    | 340  | μA    | 3.0 | MFINTOSC mode               |  |

|         |                 |                                                         | 230    | 420  | μA    | 5.0 |                             |  |

| D019    |                 | _                                                       | 0.9    | 1.5  | mA    | 1.8 | Fosc = 16 MHz,              |  |

|         |                 | _                                                       | 1.5    | 2.3  | mA    | 3.0 | HFINTOSC mode               |  |

| D019    |                 |                                                         | 1.2    | 2.0  | mA    | 2.3 | Fosc = 16 MHz,              |  |

|         |                 |                                                         | 1.5    | 2.5  | mA    | 3.0 | HFINTOSC mode               |  |

|         |                 |                                                         | 1.7    | 2.6  | mA    | 5.0 |                             |  |

| D020    |                 | _                                                       | 2.9    | 4.2  | mA    | 3.0 | Fosc = 32 MHz,              |  |

|         |                 |                                                         | 3.5    | 4.3  | mA    | 3.6 | HFINTOSC mode (Note 5)      |  |

| D020    |                 |                                                         | 2.9    | 4.2  | mA    | 3.0 | Fosc = 32 MHz,              |  |

|         |                 | —                                                       | 3.0    | 5.0  | mA    | 5.0 | HFINTOSC mode (Note 5)      |  |

| D022    |                 |                                                         | 2.8    | 4    | mA    | 3.0 | Fosc = 32 MHz,              |  |

|         |                 | —                                                       | 3.4    | 4.7  | mA    | 3.6 | HS Oscillator mode (Note 5) |  |

| D022    |                 |                                                         | 2.9    | 4    | mA    | 3.0 | Fosc = 32 MHz               |  |

|         |                 | —                                                       | 3.1    | 4.5  | mA    | 5.0 | HS Oscillator mode (Note 5) |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For EXTRC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: FVR and BOR are disabled.

5: 8 MHz crystal/oscillator with 4x PLL enabled.

#### TABLE 36-4: I/O PORTS (CONTINUED) (CONTINUED)

| Standard | l Operati | ng Conditions (unless otherwi | se stated) |  |

|----------|-----------|-------------------------------|------------|--|

|          |           |                               |            |  |

| Param<br>No. | Sym.  | Characteristic                          | Min. | Тур† | Max. | Units | Conditions                                                             |  |

|--------------|-------|-----------------------------------------|------|------|------|-------|------------------------------------------------------------------------|--|

|              |       | Capacitive Loading Specs on Output Pins |      |      |      |       |                                                                        |  |

| D101*        | COSC2 | OSC2 pin                                | _    | —    | 15   | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1 |  |

| D101A*       | Сю    | All I/O pins                            |      |      | 50   | pF    |                                                                        |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in EXTRC mode.

2: Negative current is defined <u>as current sourced by the pin.</u>

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**4:** Including OSC2 in CLKOUT mode.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

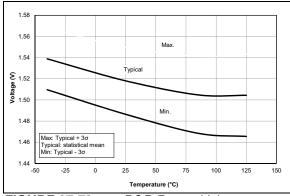

FIGURE 37-73: POR Rearm Voltage, NP Mode (VREGPM1 = 0), PIC16F1773/6 Only.

FIGURE 37-74: POR Rearm Voltage, NP Mode, PIC16LF1777/8/9 Only.

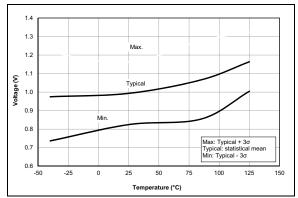

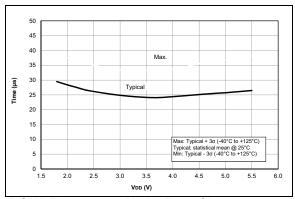

FIGURE 37-75: Wake From Sleep, VREGPM = 0.

FIGURE 37-76: Wake From Sleep, VREGPM = 1.

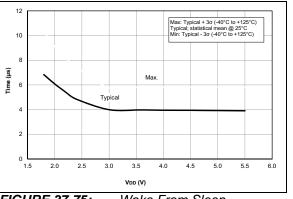

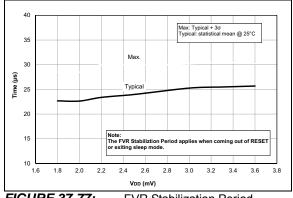

FIGURE 37-77: FVR Stabilization Period, PIC16LF1777/8/9 Only.