Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 28x10b; D/A 4x5b, 4x10b                                                 |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

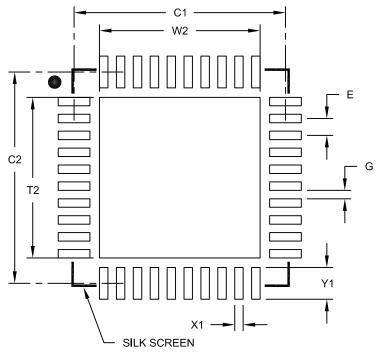

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1777t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.1 Register and Bit naming conventions

### 1.1.1 REGISTER NAMES

When there are multiple instances of the same peripheral in a device, the peripheral control registers will be depicted as the concatenation of a peripheral identifier, peripheral instance, and control identifier. The control registers section will show just one instance of all the register names with an 'x' in the place of the peripheral instance number. This naming convention may also be applied to peripherals when there is only one instance of that peripheral in the device to maintain compatibility with other devices in the family that contain more than one.

### 1.1.2 BIT NAMES

There are two variants for bit names:

- · Short name: Bit function abbreviation

- Long name: Peripheral abbreviation + short name

### 1.1.2.1 Short Bit Names

Short bit names are an abbreviation for the bit function. For example, some peripherals are enabled with the EN bit. The bit names shown in the registers are the short name variant.

Short bit names are useful when accessing bits in C programs. The general format for accessing bits by the short name is *RegisterName*bits. *ShortName*. For example, the enable bit, EN, in the COG1CON0 register can be set in C programs with the instruction COG1CON0bits.EN = 1.

Short names are generally not useful in assembly programs because the same name may be used by different peripherals in different bit positions. When this occurs, during the include file generation, all instances of that short bit name are appended with an underscore plus the name of the register in which the bit resides to avoid naming contentions.

### 1.1.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral, thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C the COG1CON0 enable bit can be set with the GIEN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, GIEN instruction.

### 1.1.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

COG1CON0bits.MD = 0x5;

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name MD2 and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to the Push-Pull mode:

### **EXAMPLE 1-1:**

```

MOVLW ~(1<<G1MD1)

ANDWF COG1CON0,F

MOVLW 1<<G1MD2 | 1<<G1MD0

IORWF COG1CON0,F

```

### EXAMPLE 1-2:

BSF COG1CON0,G1MD2 BCF COG1CON0,G1MD1 BSF COG1CON0,G1MD0

## 1.1.3 REGISTER AND BIT NAMING EXCEPTIONS

### 1.1.3.1 Status, Interrupt, and Mirror Bits

Status, interrupt enables, interrupt flags, and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

### 1.1.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

|                    |             |           |                    |              |            |           |                         |                           |              |              | Ре  | riph   | nera   | Inp     | ut       |          |                 |            |            |                    |           |                    |                    |                 |              |

|--------------------|-------------|-----------|--------------------|--------------|------------|-----------|-------------------------|---------------------------|--------------|--------------|-----|--------|--------|---------|----------|----------|-----------------|------------|------------|--------------------|-----------|--------------------|--------------------|-----------------|--------------|

| Peripheral Output  | ADC Trigger | COG Clock | COG Rising/Falling | COG Shutdown | 10-bit DAC | 5-bit DAC | <b>PRG Analog Input</b> | <b>PRG Rising/Falling</b> | Comparator + | Comparator - | CLC | DSM CH | DSM CL | DSM Mod | Op Amp + | Op Amp - | Op Amp Override | 10-bit PWM | 16-bit PWM | <b>CCP</b> Capture | CCP Clock | Timer2/4/6/8 Clock | Timer2/4/6/8 Reset | Timer1/3/5 Gate | Timer0 Clock |

| FVR                |             |           |                    |              | •          | •         | ٠                       |                           | ٠            | ٠            |     |        |        |         | •        | •        |                 |            |            |                    |           |                    |                    |                 |              |

| ZCD                |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          | •               |            |            |                    |           | •                  |                    |                 |              |

| PRG                |             |           |                    |              |            |           |                         |                           | •            |              |     |        |        |         | •        | •        |                 |            |            |                    |           |                    |                    |                 |              |

| 10-bit DAC         |             |           |                    |              |            |           | •                       |                           | •            |              |     |        |        |         | •        | •        |                 |            |            |                    |           |                    |                    |                 |              |

| 5-bit DAC          |             |           |                    |              |            |           | •                       |                           | •            |              |     |        |        |         | •        | •        |                 |            |            |                    |           |                    |                    |                 |              |

| CCP                | •           |           | ٠                  |              |            |           |                         | ٠                         |              |              | ٠   | ٠      | •      | ٠       |          |          | •               |            |            |                    |           |                    | •                  |                 |              |

| Comparator (sync)  | •           |           |                    |              |            |           |                         | •                         |              |              | •   |        |        |         |          |          | •               |            |            | •                  |           |                    | •                  | •               |              |

| Comparator (async) |             |           | •                  | •            |            |           |                         |                           |              |              |     |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| CLC                | •           |           | •                  | •            |            |           |                         |                           |              |              | •   | •      | •      | •       |          |          | •               |            |            | •                  |           | •                  | •                  |                 |              |

| DSM                |             |           |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| COG                |             |           |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          | •               |            |            |                    |           |                    |                    |                 |              |

| EUSART TX/CK       |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| EUSART DT          |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| MSSP SCK/SCL       |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| MSSP SDO/SDA       |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        | •       |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| Op Amp             |             |           |                    |              |            |           | •                       |                           |              |              |     |        |        |         |          |          |                 |            |            |                    |           |                    |                    |                 |              |

| 10-bit PWM         | •           |           | •                  |              |            |           |                         | •                         |              |              | •   | •      | •      | •       |          |          | •               |            |            |                    |           |                    | •                  |                 |              |

| 16-bit PWM         | •           |           | •                  |              |            |           |                         | •                         |              |              | •   | •      | •      | •       |          |          | •               |            |            |                    |           |                    | •                  |                 |              |

| Timer0 overflow    | •           |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 |            |            |                    |           |                    |                    | •               |              |

| Timer2 = T2PR      |             |           |                    | ٠            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer4 = T4PR      |             |           |                    | ٠            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer6 = T6PR      |             |           |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer8 = T8PR      |             |           |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer2 Postscale   | •           |           |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer4 Postscale   | •           |           |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer6 Postscale   | •           |           |                    | •            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer8 Postscale   | •           |           |                    | ٠            |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    | •                  |                 |              |

| Timer1 overflow    | ٠           |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    |                    |                 |              |

| Timer3 overflow    | •           |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    |                    |                 |              |

| Timer5 overflow    | •           |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 | •          |            |                    | •         |                    |                    |                 |              |

| SOSC               |             |           |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          |                 |            | •          |                    |           | ٠                  |                    |                 |              |

| Fosc/4             |             | ٠         |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          |                 |            |            |                    |           | •                  |                    |                 |              |

| Fosc               |             | •         |                    |              |            |           |                         |                           |              |              | •   | •      | •      |         |          |          |                 |            | •          |                    |           | ٠                  |                    |                 |              |

| HFINTOSC           |             | •         |                    |              |            |           |                         |                           |              |              | •   | •      | •      |         |          |          |                 |            | •          |                    |           | ٠                  |                    |                 |              |

| LFINTOSC           |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 |            | •          |                    |           | •                  |                    |                 |              |

| MFINTOSC           |             |           |                    |              |            |           |                         |                           |              |              |     |        |        |         |          |          |                 |            |            |                    |           | ٠                  |                    |                 |              |

| IOCIF              |             |           |                    |              |            |           |                         |                           |              |              | •   |        |        |         |          |          |                 |            |            | •                  | •         |                    |                    |                 |              |

| PPS Input pin      |             |           | •                  | ٠            |            |           |                         | •                         |              |              |     | •      | •      | •       |          |          |                 |            |            | •                  | •         | •                  | •                  | •               | •            |

TABLE 1-4: PERIPHERAL CONNECTION MATRIX

# 3.3 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-3):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- · 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.7** "Indirect Addressing" for more information.

Data memory uses a 12-bit address. The upper five bits of the address define the Bank address and the lower seven bits select the registers/RAM in that bank.

## 3.3.1 CORE REGISTERS

**TABLE 3-2:**

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-17.

**CORE REGISTERS**

#### Addresses BANKx x00h or x80h INDF0 x01h or x81h INDF1 x02h or x82h PCL x03h or x83h STATUS x04h or x84h FSR0L x05h or x85h FSR0H FSR1L x06h or x86h FSR1H x07h or x87h x08h or x88h BSR x09h or x89h WREG PCLATH x0Ah or x8Ah x0Bh or x8Bh INTCON

## 3.3.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 35.0 "Instruction Set Summary").

Note: The C and DC bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

# TABLE 3-9: PIC16(L)F1777 MEMORY MAP, BANK 16-23

|              | BANK 16                       |      | BANK 17                       |      | BANK 18                       |      | BANK 19                       |      | BANK 20                       |       | BANK 21                       |      | BANK 22                       |      | BANK 23                       |

|--------------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|-------|-------------------------------|------|-------------------------------|------|-------------------------------|

| 800h         |                               | 880h |                               | 900h |                               | 980h |                               | A00h |                               | A80h  |                               | B00h |                               | B80h |                               |

|              | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |       | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |

| 80Bh         | (10016-0-2)                   | 88Bh | (10010-0-2)                   | 90Bh | (18016-0-2)                   | 98Bh | (10016-0-2)                   | A0Bh | (10016-0-2)                   | A8Bh  | (10016-0-2)                   | B0Bh | (18616-5-2)                   | B8Bh | (18016-0-2)                   |

| 80Ch         | _                             | 88Ch | _                             | 90Ch | CM4CON0                       | 98Ch |                               | A0Ch |                               | A8Ch  |                               | B0Ch |                               | B8Ch |                               |

| 80Dh         | COG3PHR                       |      | COG4PHR                       | 90Dh | CM4CON1                       |      |                               | ,    |                               | 1.001 |                               | 200  |                               | 200  |                               |

| 80Eh         | COG3PHF                       |      | COG4PHF                       | 90Eh | CM4NSEL                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 80Fh         | COG3BLKR                      | ·    | COG4BLKR                      | 90Fh | CM4PSEL                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 810h         | COG3BLKF                      | Ī    | COG4BLKF                      | 910h | CM5CON0                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 811h         | COG3DBR                       | ĺ    | COG4DBR                       | 911h | CM5CON1                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 812h         | COG3DBF                       |      | COG4DBF                       | 912h | CM5NSEL                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 813h         | COG3CON0                      |      | COG4CON0                      | 913h | CM5PSEL                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 814h         | COG3CON1                      |      | COG4CON1                      | 914h | CM6CON0                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 815h         | COG3RIS0                      |      | COG4RIS0                      | 915h | CM6CON1                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 816h         | COG3RIS1                      | _    | COG4RIS1                      | 916h | CM6NSEL                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 817h         | COG3RSIM0                     | _    | COG4RSIM0                     | 917h | CM6PSEL                       |      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |       | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |

| 818h         | COG3RSIM1                     |      | COG4RSIM1                     | 918h | CM7CON0                       |      | Redu as 0                     |      | Redu ds 0                     |       | Redu ds 0                     |      | Redu ds 0                     |      | Redu as 0                     |

| 819h         | COG3FIS0                      |      | COG4FIS0                      |      | CM7CON1                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 81Ah         | COG3FIS1                      | -    | COG4FIS1                      |      | CM7NSEL                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 81Bh         | COG3FSIM0                     |      | COG4FSIM0<br>COG4FSIM1        |      | CM7PSEL                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 81Ch<br>81Dh | COG3FSIM1<br>COG3ASD0         | -    | COG4FSIM1<br>COG4ASD0         |      | CM8CON0<br>CM8CON1            |      |                               |      |                               |       |                               |      |                               |      |                               |

| 81Dh<br>81Eh | COG3ASD0<br>COG3ASD1          | ·    | COG4ASD0<br>COG4ASD1          |      | CM8CON1                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 81Fh         | COG3STR                       | 89Fh | COG4STR                       | 91Fh | CM8PSEL                       |      |                               |      |                               |       |                               |      |                               |      |                               |

| 820h         | 00000111                      | 8A0h | 0004011                       | 920h | CINICI SEL                    |      |                               |      |                               |       |                               |      |                               |      |                               |

|              | Unimplemented                 |      | Unimplemented                 |      | Unimplemented                 |      |                               |      |                               |       |                               |      |                               |      |                               |

|              | Read as '0'                   |      | Read as '0'                   |      | Read as '0'                   |      |                               |      |                               |       |                               |      |                               |      |                               |

| 86Fh         |                               | 8EFh |                               | 96Fh |                               | 9EFh |                               | A6Fh |                               | AEFh  |                               | B6Fh |                               | BEFh |                               |

| 870h         |                               | 8F0h |                               | 970h |                               | 9F0h |                               | A70h |                               | AF0h  |                               | B70h |                               | BF0h |                               |

|              | Accesses                      |      | Accesses                      |      | Accesses                      |      | Accesses                      |      | Accesses                      |       | Accesses                      |      | Accesses                      |      | Accesses                      |

|              | 70h – 7Fh                     |      | 70h – 7Fh                     |      | 70h – 7Fh                     |      | 70h – 7Fh                     |      | 70h – 7Fh                     |       | 70h – 7Fh                     |      | 70h – 7Fh                     |      | 70h – 7Fh                     |

| 87Fh         |                               | 8FFh |                               | 97Fh |                               | 9FFh |                               | A7Fh |                               | AFFh  |                               | B7Fh |                               | BFFh |                               |

Legend: = Unimplemented data memory locations, read as '0'.

1

# TABLE 3-18: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr | Name      | Bit 7         | Bit 6  | Bit 5            | Bit 4            | Bit 3        | Bit 2  | Bit 1   | Bit 0 | Value on<br>POR, BOR | Value on all other Resets |

|------|-----------|---------------|--------|------------------|------------------|--------------|--------|---------|-------|----------------------|---------------------------|

| Bank | k 13      |               |        |                  |                  |              |        |         |       |                      |                           |

| 68Ch | —         | Unimplemented |        |                  |                  |              |        |         |       | —                    | —                         |

| 68Dh | COG1PHR   | —             | _      | COG Rising Edge  | Phase Delay Cou  | nt Register  |        |         |       | 00 0000              | 00 0000                   |

| 68Eh | COG1PHF   | —             |        | COG Falling Edge | Phase Delay Cou  | unt Register |        |         |       | 00 0000              | 00 0000                   |

| 68Fh | COG1BLKR  | —             |        | COG Rising Edge  | Blanking Count R | egister      |        |         |       | 00 0000              | 00 0000                   |

| 690h | COG1BLKF  | —             | _      | COG Falling Edge | Blanking Count F | Register     |        |         |       | 00 0000              | 00 0000                   |

| 691h | COG1DBR   | —             | _      | COG Rising Edge  | Dead-band Coun   | t Register   |        |         |       | 00 0000              | 00 0000                   |

| 692h | COG1DBF   | —             |        | COG Falling Edge | e Dead-band Coun | t Register   |        |         |       | 00 0000              | 00 0000                   |

| 693h | COG1CON0  | EN            | LD     | —                | CS<              | 1:0>         |        | MD<2:0> |       | 00-0 0000            | 00-0 0000                 |

| 694h | COG1CON1  | RDBS          | FDBS   | —                | —                | POLD         | POLC   | POLB    | POLA  | 00 0000              | 00 0000                   |

| 695h | COG1RIS0  | RIS7          | RIS6   | RIS5             | RIS4             | RIS3         | RIS2   | RIS1    | RIS0  | 0000 0000            | 0000 0000                 |

| 696h | COG1RIS1  | RIS15         | RIS14  | RIS13            | RIS12            | RIS11        | RIS10  | RIS9    | RIS8  | 0000 0000            | 0000 0000                 |

| 697h | COG1RSIM0 | RSIM7         | RSIM6  | RSIM5            | RSIM4            | RSIM3        | RSIM2  | RSIM1   | RSIM0 | 0000 0000            | 0000 0000                 |

| 698h | COG1RSIM1 | RSIM15        | RSIM14 | RSIM13           | RSIM12           | RSIM11       | RSIM10 | RSIM9   | RSIM8 | 0000 0000            | 0000 0000                 |

| 699h | COG1FIS0  | FIS7          | FIS6   | FIS5             | FIS4             | FIS3         | FIS2   | FIS1    | FIS0  | 0000 0000            | 0000 0000                 |

| 69Ah | COG1FIS1  | FIS15         | FIS14  | FIS13            | FIS12            | FIS11        | FIS10  | FIS9    | FIS8  | 0000 0000            | 0000 0000                 |

| 69Bh | COG1FSIM0 | FSIM7         | FSIM6  | FSIM5            | FSIM4            | FSIM3        | FSIM2  | FSIM1   | FSIM0 | 0000 0000            | 0000 0000                 |

| 69Ch | COG1FSIM1 | FSIM15        | FSIM14 | FSIM13           | FSIM12           | FSIM11       | FSIM10 | FSIM9   | FSIM8 | 0000 0000            | 0000 0000                 |

| 69Dh | COG1ASD0  | ASE           | ARSEN  | ASDBI            | 0<1:0>           | ASDA         | C<1:0> | _       | _     | 0001 01              | 0001 01                   |

| 69Eh | COG1ASD1  | AS7E          | AS6E   | AS5E             | AS4E             | AS3E         | AS2E   | AS1E    | AS0E  | 0000 0000            | 0000 0000                 |

| 69Fh | COG1STR   | SDATD         | SDATC  | SDATB            | SDATA            | STRD         | STRC   | STRB    | STRA  | 0000 0000            | 0000 0000                 |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: Unimplemented, read as '1'.

2:

Unimplemented on PIC16LF1777/8/9. 3: Unimplemented on PIC16(L)F1778.

# TABLE 3-18: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr     | Name                   | Bit 7         | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2   | Bit 1 | Bit 0  | Value on POR, BOR | Value on all<br>other Resets |

|----------|------------------------|---------------|-------|-------|--------|-------|---------|-------|--------|-------------------|------------------------------|

| Bank     | c 26                   |               |       |       |        |       |         |       |        |                   |                              |

| D0Ch     |                        | Unimplemented |       |       |        |       |         |       |        |                   |                              |

| <br>D1Ah |                        | Onimplemented |       |       |        |       |         |       |        | _                 | _                            |

| D1Bh     | MD4CON0 <sup>(3)</sup> | EN            | -     | OUT   | OPOL   | _     | _       | _     | BIT    | 0-000             | 0-000                        |

| D1Ch     | MD4CON1 <sup>(3)</sup> | —             | -     | CHPOL | CHSYNC | _     | _       | CLPOL | CLSYNC | 0000              | 0000                         |

| D1Dh     | MD4SRC <sup>(3)</sup>  | —             | -     | —     |        |       | MS<4:0> |       |        | 0 0000            | 0 0000                       |

| D1Eh     | MD4CARL <sup>(3)</sup> | —             | _     | _     |        |       | CL<4:0> |       |        | 0 0000            | 0 0000                       |

| D1Fh     | MD4CARH <sup>(3)</sup> | —             | _     | _     |        |       | CH<4:0> |       |        | 0 0000            | 0 0000                       |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

2: Unimplemented on PIC16LF1777/8/9.

**3:** Unimplemented on PIC16(L)F1778.

# 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

## TABLE 5-1:OSCILLATOR SWITCHING DELAYS

#### Switch From Switch To Frequency **Oscillator Delav** LFINTOSC<sup>(1)</sup> 31 kHz MFINTOSC<sup>(1)</sup> Oscillator Warm-up Delay (TWARM)(2) 31.25 kHz-500 kHz Sleep HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz EC, RC<sup>(1)</sup> Sleep/POR DC - 32 MHz 2 cycles EC. RC<sup>(1)</sup> **LFINTOSC** DC - 32 MHz 1 cycle of each Secondary Oscillator Sleep/POR 32 kHz-20 MHz 1024 Clock Cycles (OST) LP, XT, HS<sup>(1)</sup> MFINTOSC<sup>(1)</sup> 31.25 kHz-500 kHz Any clock source 2 µs (approx.) HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz LFINTOSC<sup>(1)</sup> Any clock source 31 kHz 1 cycle of each Any clock source Secondary Oscillator 32 kHz 1024 Clock Cycles (OST) PLL inactive 16-32 MHz PLL active 2 ms (approx.)

Note 1: PLL inactive.

2: See Section 36.0 "Electrical Specifications".

# 5.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

# 8.2 Low-Power Sleep Mode

The PIC16F1773/6 devices contain an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode. The PIC16F1773/6 allow the user to optimize the operating current in Sleep, depending on the application requirements.

A Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register. With this bit set, the LDO and reference circuitry are placed in a low-power state when the device is in Sleep.

8.2.1 SLEEP CURRENT VS. WAKE-UP TIME

In the Default Operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

## 8.2.2 PERIPHERAL USAGE IN SLEEP

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use with the following peripherals only:

- Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- · External interrupt pin/interrupt-on-change pins

- Timer1 (with external clock source < 100 kHz)

- Note: The PIC16LF1777/8/9 do not have a configurable Low-Power Sleep mode. PIC16LF1777/8/9 are unregulated devices and are always in the lowest power state when in Sleep, with no wake-up time penalty. These devices have a lower maximum VDD and I/O voltage than the PIC16F1777/8/9. See Section 36.0 "Electrical Specifications" for more information.

### EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY

- ; This row erase routine assumes the following:

- ; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory  $0\,\mathrm{x}70$  -  $0\,\mathrm{x}7F$  (common RAM)

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVF<br>MOVF<br>BCF<br>BCF<br>BSF<br>BSF | INTCON, GIE<br>PMADRL<br>ADDRL,W<br>PMADRL<br>ADDRH,W<br>PMADRH<br>PMCON1,CFGS<br>PMCON1,FREE<br>PMCON1,WREN | <pre>; Disable ints so required sequences will execute properly<br/>; Load lower 8 bits of erase address boundary<br/>; Load upper 6 bits of erase address boundary<br/>; Not configuration space<br/>; Specify an erase operation<br/>; Enable writes</pre>                                                                                             |

|----------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Required<br>Sequence | MOVLW<br>MOVUF<br>MOVLW<br>MOVWF<br>BSF<br>NOP<br>NOP              | 55h<br>PMCON2<br>0AAh<br>PMCON2<br>PMCON1,WR                                                                 | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; NOP instructions are forced as processor starts<br/>; row erase of program memory.<br/>;<br/>; The processor stalls until the erase process is complete<br/>; after erase processor continues with 3rd instruction</pre> |

|                      | BCF<br>BSF                                                         | PMCON1,WREN<br>INTCON,GIE                                                                                    | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                                  |

# 18.7 Register Definitions: DAC Control

Long bit name prefixes for the 10-bit DAC peripherals are shown in Table 18-2. Refer to **Section 1.1** "**Register and Bit naming conventions**" for more information

### TABLE 18-2:

| Peripheral          | Bit Name Prefix |

|---------------------|-----------------|

| DAC1                | DAC1            |

| DAC2                | DAC2            |

| DAC5                | DAC5            |

| DAC6 <sup>(1)</sup> | DAC6            |

**Note 1:** PIC16(L)F1777/9 only.

### REGISTER 18-1: DACxCON0: DAC CONTROL REGISTER 0

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| EN      | FM      | OE1     | OE2     | PSS     | <1:0>   | NSS     | <1:0>   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: DAC Enable bit                                           |

|---------|--------------------------------------------------------------|

|         | 1 = DACx is enabled                                          |

|         | 0 = DACx is disabled                                         |

| bit 6   | FM: DAC Reference Format bit                                 |

|         | 1 = DACx reference selection is left justified               |

|         | 0 = DACx reference selection is right justified              |

| bit 5   | OE1: DAC Voltage Output Enable bit                           |

|         | 1 = DACx voltage level is also an output on the DACxOUT1 pin |

|         | 0 = DACx voltage level is disconnected from the DACxOUT1 pin |

| bit 4   | OE2: DAC Voltage Output Enable bit                           |

|         | 1 = DACx voltage level is also an output on the DACxOUT2 pin |

|         | 0 = DACx voltage level is disconnected from the DACxOUT2 pin |

| bit 3-2 | PSS<1:0>: DAC Positive Source Select bits                    |

|         | 11 = DACxREF1+ (DAC5/6) or Reserved (DAC1/2)                 |

|         | 10 = FVR_buffer2                                             |

|         | 01 = DACxREF0+                                               |

|         | 00 = VDD                                                     |

| bit 1-0 | NSS<1:0>: DAC Negative Source Select bit                     |

|         | 11 = Reserved. Do not use.                                   |

|         | 10 = DACxREF1- (DAC5/6) or Reserved (DAC1/2)                 |

|         | 01 = DACxREF0-                                               |

|         | 00 = Agnd(AVss)                                              |

|         |                                                              |

FIGURE 26-9:

PIC16(L)F1777/8/9

# 27.3 Modes of Operation

### 27.3.1 STEERED PWM MODES

In Steered PWM mode, the PWM signal derived from the input event sources is output as a single phase PWM which can be steered to any combination of the four COG outputs. Output steering takes effect on the instruction cycle following the write to the COGxSTR register.

Synchronous Steered PWM mode is identical to the Steered PWM mode except that changes to the output steering take effect on the first rising event after the COGxSTR register write. Static output data is not synchronized.

Steering mode configurations are shown in Figure 27-2 and Figure 27-3.

Steered PWM and Synchronous Steered PWM modes are selected by setting the MD<2:0> bits of the COGxCON0 register (Register 27-1) to '000' and '001', respectively.

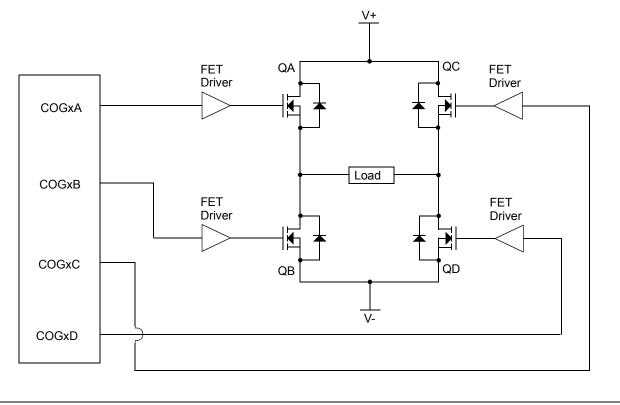

# 27.3.2 FULL-BRIDGE MODES

In both Forward and Reverse Full-Bridge modes, two of the four COG outputs are active and the other two are inactive. Of the two active outputs, one is modulated by the PWM input signal and the other is on at 100% duty cycle. When the direction is changed, the dead-band time is inserted to delay the modulated output. This gives the unmodulated driver time to shut down, thereby, preventing shoot-through current in the series connected power devices.

In Forward Full-Bridge mode, the PWM input modulates the COGxD output and drives the COGA output at 100%.

In Reverse Full-Bridge mode, the PWM input modulates the COGxB output and drives the COGxC output at 100%.

The full-bridge configuration is shown in Figure 27-4. Typical full-bridge waveforms are shown in Figure 27-12 and Figure 27-13.

Full-Bridge Forward and Full-Bridge Reverse modes are selected by setting the MD<2:0> bits of the COGxCON0 register to '010' and '011', respectively.

| Name     | Bit 7  | Bit 6  | Bit 5  | Bit 4        | Bit 3        | Bit 2    | Bit 1  | Bit 0  | Register<br>on Page |  |  |

|----------|--------|--------|--------|--------------|--------------|----------|--------|--------|---------------------|--|--|

| ANSELB   |        |        | ANSB5  | ANSB4        | ANSB3        | ANSB2    | ANSB1  | ANSB0  | 182                 |  |  |

| ANSELC   | ANSC7  | ANSC6  | ANSC5  | ANSC4        | ANSC3        | ANSC2    |        | —      | 187                 |  |  |

| DAC1CON0 | EN     | FM     | OE1    | OE2          | PSS          | <1:0>    | NSS    | <1:0>  | 249                 |  |  |

| DAC2CON0 | EN     | FM     | OE1    | OE2          | PSS          | <1:0>    | NSS    | <1:0>  | 249                 |  |  |

| DAC5CON0 | EN     | FM     | OE1    | OE2          | PSS          | <1:0>    | NSS    | <1:0>  | 249                 |  |  |

| DAC3CON0 | EN     | _      | OE1    | OE2          | PSS          | <1:0>    | NSS    | <1:0>  | 244                 |  |  |

| DAC4CON0 | EN     | —      | OE1    | OE2          | PSS•         | <1:0>    | NSS    | <1:0>  | 244                 |  |  |

| DAC7CON0 | EN     | _      | OE1    | OE2          | PSS          | <1:0>    | NSS    | <1:0>  | 244                 |  |  |

| DAC3REF  |        |        |        |              |              | REF<4:0> |        | 245    |                     |  |  |

| DAC4REF  |        |        |        |              |              | REF<4:0> |        | 245    |                     |  |  |

| DAC7REF  |        |        |        |              |              | REF<4:0> |        |        |                     |  |  |

| DAC1REFH |        |        | R      | EF<9:x> (x D | epends on FM | bit)     |        |        | 250                 |  |  |

| DAC2REFH |        |        | R      | EF<9:x> (x D | epends on FM | bit)     |        |        | 250                 |  |  |

| DAC5REFH |        |        | R      | EF<9:x> (x D | epends on FM | bit)     |        |        | 250                 |  |  |

| FVRCON   | FVREN  | FVRRDY | TSEN   | TSRNG        | CDAFV        | ′R<1:0>  | ADFVI  | R<1:0> | 223                 |  |  |

| OPAxCON  | EN     |        | _      | UG           | —            | ORPOL    | ORM    | <1:0>  | 408                 |  |  |

| OPAxNCHS | —      | _      | —      | _            |              | NCH<     | 3:0>   |        | 410                 |  |  |

| OPAxPCHS | —      | _      | —      | _            |              | PCH<     | 3:0>   | 411    |                     |  |  |

| OPAxORS  | _      | _      | _      |              |              | ORS<4:0> |        |        |                     |  |  |

| TRISB    | TRISB7 | TRISB6 | TRISB5 | TRISB4       | TRISB3       | TRISB2   | TRISB1 | TRISB0 | 181                 |  |  |

| TRISC    | TRISC7 | TRISC6 | TRISC5 | TRISC4       | TRISC3       | TRISC2   | TRISC1 | TRISC0 | 186                 |  |  |

## TABLE 29-6: SUMMARY OF REGISTERS ASSOCIATED WITH OP AMPS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by op amps.

-n/n = Value at POR and BOR/Value at all other Resets

q = value depends on configuration bits

| U-0                               | U-0 | U-0 | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0 | R/W-0/0 |

|-----------------------------------|-----|-----|---------|--------------|------------------|---------|---------|

| —                                 | —   | —   |         |              | ISET<4:0>        |         |         |

| bit 7                             |     |     |         |              |                  |         | bit 0   |

|                                   |     |     |         |              |                  |         |         |

| Legend:                           |     |     |         |              |                  |         |         |

| R = Readable bit W = Writable bit |     |     |         | U = Unimpler | nented bit, read | as '0'  |         |

# REGISTER 30-4: PRGxCON2: PROGRAMMABLE RAMP GENERATOR CONTROL 2 REGISTER

bit 7-5 **Unimplemented:** Read as '0'

u = Bit is unchanged

'1' = Bit is set

bit 4-0 **ISET<4:0>:** PRG Current Source/Sink Set bits Current source/sink setting and slope rate. See Table 30-4.

x = Bit is unknown

'0' = Bit is cleared

## TABLE 30-4: PROGRAMMABLE RAMP GENERATOR CURRENT SETTINGS

| ISET<4:0> | Current Setting<br>(uA) | Slope Rate<br>(V/us) | ISET<4:0> | Current Setting<br>(uA) | Slope Rate<br>(V/us) |

|-----------|-------------------------|----------------------|-----------|-------------------------|----------------------|

| 0h        | 2                       | 0.2                  | 10h       | 10                      | 1.0                  |

| 1h        | 2.5                     | 0.25                 | 11h       | 11                      | 1.1                  |

| 2h        | 3                       | 0.3                  | 12h       | 12                      | 1.2                  |

| 3h        | 3.5                     | 0.35                 | 13h       | 13                      | 1.3                  |

| 4h        | 4                       | 0.4                  | 14h       | 14                      | 1.4                  |

| 5h        | 4.5                     | 0.45                 | 15h       | 15                      | 1.5                  |

| 6h        | 5                       | 0.5                  | 16h       | 16                      | 1.6                  |

| 7h        | 5.5                     | 0.55                 | 17h       | 17                      | 1.7                  |

| 8h        | 6                       | 0.6                  | 18h       | 18                      | 1.8                  |

| 9h        | 6.5                     | 0.65                 | 19h       | 19                      | 1.9                  |

| Ah        | 7                       | 0.7                  | 1Ah       | 20                      | 2.0                  |

| Bh        | 7.5                     | 0.75                 | 1Bh       | 21                      | 2.1                  |

| Ch        | 8                       | 0.8                  | 1Ch       | 22                      | 2.2                  |

| Dh        | 8.5                     | 0.85                 | 1Dh       | 23                      | 2.3                  |

| Eh        | 9                       | 0.9                  | 1Eh       | 24                      | 2.4                  |

| Fh        | 9.5                     | 0.95                 | 1Fh       | 25                      | 2.5                  |

| RTSS<3:0>/<br>FTSS<3:0> | PRG1 Timing Source             | PRG1 Timing Source PRG2 Timing Source |                                | PRG4 Timing Source <sup>(2)</sup> |

|-------------------------|--------------------------------|---------------------------------------|--------------------------------|-----------------------------------|

| 1111                    | Reserved                       | Reserved                              | PWM12_output <sup>(2)</sup>    | PWM12_output                      |

| 1110                    | Reserved                       | Reserved                              | PWM11_output                   | PWM11_output                      |

| 1101                    | LC2_out                        | LC2_out                               | PWM6_output                    | PWM6_output                       |

| 1100                    | LC1_out                        | LC1_out                               | PWM5_output                    | PWM5_output                       |

| 1011                    | PWM10_output <sup>(2)</sup>    | PWM10_output <sup>(2)</sup>           | Reserved                       | Reserved                          |

| 1010                    | PWM9_output                    | PWM9_output                           | Reserved                       | Reserved                          |

| 1001                    | PWM4_output                    | PWM4_output                           | LC4_out <sup>(2)</sup>         | LC4_out                           |

| 1000                    | PWM3_output                    | PWM3_output                           | LC3_out                        | LC3_out                           |

| 0111                    | PRGxR/PRGxF Pin <sup>(1)</sup> | PRGxR/PRGxF Pin <sup>(1)</sup>        | PRGxR/PRGxF Pin <sup>(1)</sup> | PRGxR/PRGxF Pin <sup>(1)</sup>    |

| 0110                    | Reserved                       | Reserved                              | sync_C7OUT <sup>(2)</sup>      | sync_C7OUT                        |

| 0101                    | Reserved                       | Reserved                              | sync_C6OUT                     | sync_C6OUT                        |

| 0100                    | Reserved                       | Reserved                              | sync_C5OUT                     | sync_C5OUT                        |

| 0011                    | sync_C4OUT                     | sync_C4OUT                            | Reserved                       | Reserved                          |

| 0010                    | sync_C3OUT                     | sync_C3OUT                            | Reserved                       | Reserved                          |

| 0001                    | sync_C2OUT                     | sync_C2OUT                            | Reserved                       | Reserved                          |

| 0000                    | sync_C1OUT                     | sync_C1OUT                            | Reserved                       | Reserved                          |

| <b>TABLE 30-5</b> : | PROGRAMMABLE RAMP GENERATOR TIMING SOURCES |

|---------------------|--------------------------------------------|

|---------------------|--------------------------------------------|

**Note 1:** Input pin is selected with the PRGxRPPS or PRGxFPPS register.

2: PIC16(L)F1777/9 only.

| U-0            | U-0                                                                                                | R/W-0/0                                           | R/W-0/0          | U-0            | U-0              | R/W-0/0          | R/W-0/0      |  |  |

|----------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------|----------------|------------------|------------------|--------------|--|--|

|                | _                                                                                                  | CHPOL                                             | CHSYNC           | _              | —                | CLPOL            | CLSYNC       |  |  |

| bit 7          |                                                                                                    |                                                   |                  |                |                  |                  | bit 0        |  |  |

|                |                                                                                                    |                                                   |                  |                |                  |                  |              |  |  |

| Legend:        |                                                                                                    |                                                   |                  |                |                  |                  |              |  |  |

| R = Readab     | ole bit                                                                                            | W = Writable                                      | bit              | U = Unimpler   | mented bit, read | as '0'           |              |  |  |

| u = Bit is un  | changed                                                                                            | x = Bit is unkr                                   | nown             | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |

| '1' = Bit is s | et                                                                                                 | '0' = Bit is cle                                  | ared             |                |                  |                  |              |  |  |

|                |                                                                                                    |                                                   |                  |                |                  |                  |              |  |  |

| bit 7-6        | -6 Unimplemented: Read as '0'                                                                      |                                                   |                  |                |                  |                  |              |  |  |

| bit 5          | CHPOL: Mod                                                                                         | lulation High C                                   | arrier Polarity  | Select bit     |                  |                  |              |  |  |

|                | 1 = Selected                                                                                       | high carrier so                                   | ource is inverte | ed             |                  |                  |              |  |  |

|                | 0 = Selected                                                                                       | high carrier so                                   | ource is not inv | verted         |                  |                  |              |  |  |

| bit 4          | CHSYNC: Mo                                                                                         | odulation High                                    | Carrier Synch    | ronization Ena | ble bit          |                  |              |  |  |

|                |                                                                                                    |                                                   |                  |                | efore allowing a | switch to the le | ow carrier   |  |  |

|                | 0 = Modulator output is not synchronized to the high carrier <sup>(1)</sup>                        |                                                   |                  |                |                  |                  |              |  |  |

| bit 3-2        | Unimplemen                                                                                         | Unimplemented: Read as '0'                        |                  |                |                  |                  |              |  |  |

| bit 1          | CLPOL: Mod                                                                                         | CLPOL: Modulation Low Carrier Polarity Select bit |                  |                |                  |                  |              |  |  |

|                | 1 = Selected low carrier source is inverted                                                        |                                                   |                  |                |                  |                  |              |  |  |

|                | 0 = Selected                                                                                       | 0 = Selected low carrier source is not inverted   |                  |                |                  |                  |              |  |  |

| bit 0          | CLSYNC: Mo                                                                                         | dulation Low C                                    | Carrier Synchr   | onization Enab | ole bit          |                  |              |  |  |

|                | 1 = Modulator waits for a low edge on the low carrier before allowing a switch to the high carrier |                                                   |                  |                |                  |                  |              |  |  |

|                | 0 = Modulator output is not synchronized to the low carrier <sup>(1)</sup>                         |                                                   |                  |                |                  |                  |              |  |  |

|                |                                                                                                    |                                                   |                  |                |                  |                  |              |  |  |

# REGISTER 31-2: MDxCON1: MODULATION CONTROL REGISTER 1

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

# REGISTER 31-3: MDxSRC: MODULATION SOURCE CONTROL REGISTER

| U-0   | U-0 | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   |     |         |         | MS<4:0> |         |         |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **MS<4:0>** Modulation Source Selection bits See Table 31-4 or Table 31-5.

| <b>TABLE 36-27:</b> | I <sup>2</sup> C BUS DATA REQUIREMENTS |

|---------------------|----------------------------------------|

|---------------------|----------------------------------------|

| Standard Operating Conditions (unless otherwise stated) |         |                       |              |            |      |       |                                             |  |

|---------------------------------------------------------|---------|-----------------------|--------------|------------|------|-------|---------------------------------------------|--|

| Param.<br>No.                                           | Symbol  | Characteristic        |              | Min.       | Max. | Units | Conditions                                  |  |

| SP100*                                                  | Тнідн   | Clock high time       | 100 kHz mode | 4.0        |      | μS    | Device must operate at a minimum of 1.5 MHz |  |

|                                                         |         |                       | 400 kHz mode | 0.6        |      | μS    | Device must operate at a minimum of 10 MHz  |  |

|                                                         |         |                       | SSP module   | 1.5Tcy     | _    |       |                                             |  |

| SP101*                                                  | TLOW    | Clock low time        | 100 kHz mode | 4.7        |      | μS    | Device must operate at a minimum of 1.5 MHz |  |

|                                                         |         |                       | 400 kHz mode | 1.3        |      | μS    | Device must operate at a minimum of 10 MHz  |  |

|                                                         |         |                       | SSP module   | 1.5Tcy     | _    |       |                                             |  |

| SP102*                                                  | TR      | SDA and SCL rise      | 100 kHz mode | —          | 1000 | ns    |                                             |  |

|                                                         |         | time                  | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10-400 pF        |  |

| SP103*                                                  | TF      | SDA and SCL fall      | 100 kHz mode | —          | 250  | ns    |                                             |  |

|                                                         |         | time                  | 400 kHz mode | 20 + 0.1Св | 250  | ns    | CB is specified to be from 10-400 pF        |  |

| SP106*                                                  | THD:DAT | Data input hold time  | 100 kHz mode | 0          | _    | ns    |                                             |  |

|                                                         |         |                       | 400 kHz mode | 0          | 0.9  | μS    |                                             |  |

| SP107*                                                  | TSU:DAT | Data input setup      | 100 kHz mode | 250        |      | ns    | (Note 2)                                    |  |

|                                                         |         | time                  | 400 kHz mode | 100        | _    | ns    |                                             |  |

| SP109*                                                  | ΤΑΑ     | Output valid from     | 100 kHz mode | —          | 3500 | ns    | (Note 1)                                    |  |

|                                                         |         | clock                 | 400 kHz mode | —          | _    | ns    |                                             |  |

| SP110*                                                  | TBUF    | Bus free time         | 100 kHz mode | 4.7        | _    | μS    | Time the bus must be free                   |  |

|                                                         |         |                       | 400 kHz mode | 1.3        | —    | μS    | before a new transmission<br>can start      |  |