Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betalls                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 3x5b, 3x10b                                                |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1778-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.2.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

#### 3.2.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

EXAMPLE 3-1: RETLW INSTRUCTION

| constants         |                     |

|-------------------|---------------------|

| BRW               | ;Add Index in W to  |

|                   | ;program counter to |

|                   | ;select data        |

| RETLW DATA0       | ;Index0 data        |

| RETLW DATA1       | ;Index1 data        |

| RETLW DATA2       |                     |

| RETLW DATA3       |                     |

|                   |                     |

|                   |                     |

| my_function       |                     |

| ; LOTS OF CODE    |                     |

| MOVLW DATA_IN     | DEX                 |

| call constants    |                     |

| ; THE CONSTANT IS | IN W                |

| L                 |                     |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

#### 3.2.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The high directive will set bit<7> if a label points to a location in program memory.

#### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants       |           |         |             |

|-----------------|-----------|---------|-------------|

| DW DATAO        |           | ;First  | constant    |

| DW DATA1        |           | ;Second | l constant  |

| DW DATA2        |           |         |             |

| DW DATA3        |           |         |             |

| my_function     |           |         |             |

| ; LOTS OF C     | ODE       |         |             |

| MOVLW DATA_     | _INDEX    |         |             |

| ADDLW LOW C     | constants |         |             |

| MOVWF FSR11     | _         |         |             |

| MOVLW HIGH      | constants | s;MSb s | ets         |

|                 |           | automa  | atically    |

| MOVWF FSR1H     | ł         |         |             |

| BTFSC STATU     | JS, C     | ;carry  | from ADDLW? |

| INCF FSR1H      | I, f      | ;yes    |             |

| MOVIW 0[FSF     | R1]       |         |             |

| ; THE PROGRAM M | EMORY IS  | IN W    |             |

#### TABLE 3-18: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr | Name            | Bit 7  | Bit 6  | Bit 5            | Bit 4            | Bit 3        | Bit 2  | Bit 1   | Bit 0 | Value on<br>POR, BOR | Value on all other Resets |

|------|-----------------|--------|--------|------------------|------------------|--------------|--------|---------|-------|----------------------|---------------------------|

| Bank | Bank 13         |        |        |                  |                  |              |        |         |       |                      |                           |

| 68Ch | — Unimplemented |        |        |                  |                  |              |        |         |       |                      | —                         |

| 68Dh | COG1PHR         | —      | _      | COG Rising Edge  | Phase Delay Cou  | nt Register  |        |         |       | 00 0000              | 00 0000                   |

| 68Eh | COG1PHF         | —      |        | COG Falling Edge | Phase Delay Cou  | unt Register |        |         |       | 00 0000              | 00 0000                   |

| 68Fh | COG1BLKR        | —      |        | COG Rising Edge  | Blanking Count R | egister      |        |         |       | 00 0000              | 00 0000                   |

| 690h | COG1BLKF        | —      | _      | COG Falling Edge | Blanking Count F | Register     |        |         |       | 00 0000              | 00 0000                   |

| 691h | COG1DBR         | —      | _      | COG Rising Edge  | Dead-band Coun   | t Register   |        |         |       | 00 0000              | 00 0000                   |

| 692h | COG1DBF         | —      |        | COG Falling Edge | e Dead-band Coun | t Register   |        |         |       | 00 0000              | 00 0000                   |

| 693h | COG1CON0        | EN     | LD     | —                | CS<              | 1:0>         |        | MD<2:0> |       | 00-0 0000            | 00-0 0000                 |

| 694h | COG1CON1        | RDBS   | FDBS   | —                | —                | POLD         | POLC   | POLB    | POLA  | 00 0000              | 00 0000                   |

| 695h | COG1RIS0        | RIS7   | RIS6   | RIS5             | RIS4             | RIS3         | RIS2   | RIS1    | RIS0  | 0000 0000            | 0000 0000                 |

| 696h | COG1RIS1        | RIS15  | RIS14  | RIS13            | RIS12            | RIS11        | RIS10  | RIS9    | RIS8  | 0000 0000            | 0000 0000                 |

| 697h | COG1RSIM0       | RSIM7  | RSIM6  | RSIM5            | RSIM4            | RSIM3        | RSIM2  | RSIM1   | RSIM0 | 0000 0000            | 0000 0000                 |

| 698h | COG1RSIM1       | RSIM15 | RSIM14 | RSIM13           | RSIM12           | RSIM11       | RSIM10 | RSIM9   | RSIM8 | 0000 0000            | 0000 0000                 |

| 699h | COG1FIS0        | FIS7   | FIS6   | FIS5             | FIS4             | FIS3         | FIS2   | FIS1    | FIS0  | 0000 0000            | 0000 0000                 |

| 69Ah | COG1FIS1        | FIS15  | FIS14  | FIS13            | FIS12            | FIS11        | FIS10  | FIS9    | FIS8  | 0000 0000            | 0000 0000                 |

| 69Bh | COG1FSIM0       | FSIM7  | FSIM6  | FSIM5            | FSIM4            | FSIM3        | FSIM2  | FSIM1   | FSIM0 | 0000 0000            | 0000 0000                 |

| 69Ch | COG1FSIM1       | FSIM15 | FSIM14 | FSIM13           | FSIM12           | FSIM11       | FSIM10 | FSIM9   | FSIM8 | 0000 0000            | 0000 0000                 |

| 69Dh | COG1ASD0        | ASE    | ARSEN  | ASDBI            | 0<1:0>           | ASDA         | C<1:0> | _       | _     | 0001 01              | 0001 01                   |

| 69Eh | COG1ASD1        | AS7E   | AS6E   | AS5E             | AS4E             | AS3E         | AS2E   | AS1E    | AS0E  | 0000 0000            | 0000 0000                 |

| 69Fh | COG1STR         | SDATD  | SDATC  | SDATB            | SDATA            | STRD         | STRC   | STRB    | STRA  | 0000 0000            | 0000 0000                 |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: Unimplemented, read as '1'.

2:

Unimplemented on PIC16LF1777/8/9. 3: Unimplemented on PIC16(L)F1778.

|         |                     |       |       |                                             | •                                        | ,            |       |       |       |                      |  |

|---------|---------------------|-------|-------|---------------------------------------------|------------------------------------------|--------------|-------|-------|-------|----------------------|--|

| Addr    | Name                | Bit 7 | Bit 6 | Bit 5                                       | Bit 4                                    | Bit 3        | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR |  |

| Bank 14 |                     |       |       |                                             |                                          |              |       |       |       |                      |  |

| 70Ch    | OCh — Unimplemented |       |       |                                             |                                          |              |       |       |       |                      |  |

| 70Dh    | COG2PHR             | —     | _     | COG Rising Edge                             | Phase Delay Cou                          | int Register |       |       |       | 00 0000              |  |

| 70Eh    | COG2PHF             | —     |       | COG Falling Edge                            | e Phase Delay Cou                        | unt Register |       |       |       | 00 0000              |  |

| 70Fh    | COG2BLKR            | —     |       | COG Rising Edge                             | Blanking Count R                         | legister     |       |       |       | 00 0000              |  |

| 710h    | COG2BLKF            | —     |       | COG Falling Edge                            | COG Falling Edge Blanking Count Register |              |       |       |       |                      |  |

| 711h    | COG2DBR             | —     |       | COG Rising Edge                             | COG Rising Edge Dead-band Count Register |              |       |       |       |                      |  |

| 712h    | COG2DBF             | —     |       | COG Falling Edge Dead-band Count Register - |                                          |              |       |       |       |                      |  |

| 713h    | COG2CON0            | EN    | LD    | _                                           | — CS<1:0> MD<2:0>                        |              |       |       |       |                      |  |

\_

RIS4

RIS12

RSIM4

RSIM12

FIS4

FIS12

FSIM4

FSIM12

AS4E

SDATA

POLD

RIS3

RIS11

RSIM3

RSIM11

FIS3

FIS11

FSIM3

FSIM11

AS3E

STRD

ASDAC<1:0>

POLC

RIS2

RIS10

RSIM2

RSIM10

FIS2

FIS10

FSIM2

FSIM10

AS2E

STRC

POLB

RIS1

RIS9

RSIM1

RSIM9

FIS1

FIS9

FSIM1

FSIM9

\_

AS1E

STRB

POLA

RIS0

RIS8

RSIM0

RSIM8

FIS0

FIS8

FSIM0

FSIM8

\_

AS0E

STRA

00-- 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0001 01--

0000 0000

0000 0000

#### TABLE 3-18: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

FDBS

RIS6

RIS14

RSIM6

RSIM14

FIS6

FIS14

FSIM6

FSIM14

ARSEN

AS6E

SDATC

\_

RIS5

RIS13

RSIM5

RSIM13

FIS5

FIS13

FSIM5

FSIM13

AS5E

SDATB

ASDBD<1:0>

**Legend:** x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, read as '0', r = reserved.Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

2: Unimplemented on PIC16LF1777/8/9.

RDBS

RIS7

RIS15

RSIM7

RSIM15

FIS7

FIS15

FSIM7

FSIM15

ASE

AS7E

SDATD

3: Unimplemented on PIC16(L)F1778.

714h

715h

716h

717h

718h

719h

71Ah

71Bh

71Ch

71Dh

71Eh

COG2CON1

COG2RIS0

COG2RIS1

COG2RSIM0

COG2RSIM1

COG2FIS0

COG2FIS1

COG2FSIM0

COG2FSIM1

COG2ASD0

COG2ASD1

71Fh COG2STR

Value on all other Resets

--00 0000 --00 0000 --00 0000 --00 0000 --00 0000 00-0 0000

00-- 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0001 01--

0000 0000

0000 0000

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

###

#### FIGURE 5-8: TWO-SPEED START-UP

#### 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or the internal oscillator.

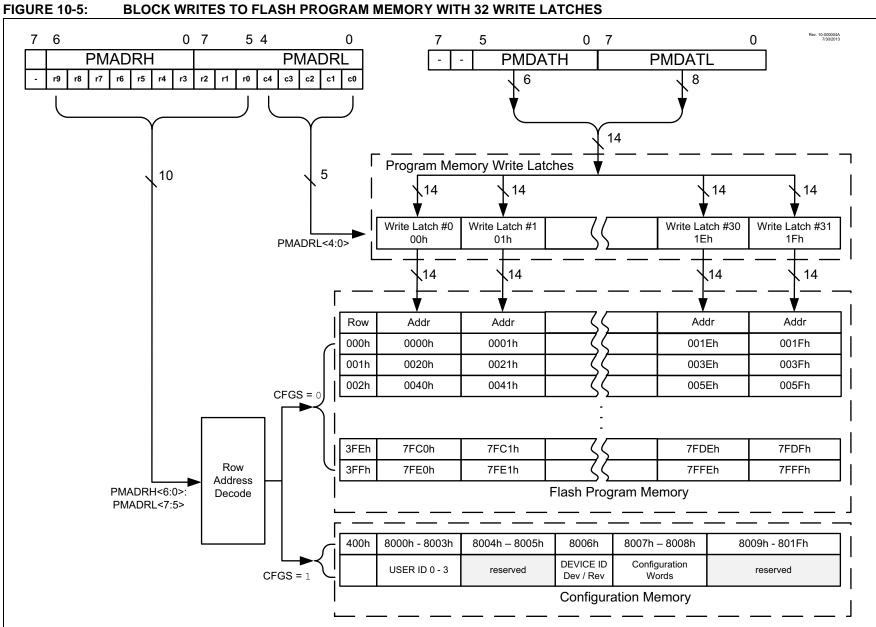

#### 10.2.4 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the address in PMADRH:PMADRL of the row to be programmed.

- 2. Load each write latch with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 10-5 (row writes to program memory with 32 write latches) for more details.

The write latches are aligned to the Flash row address boundary defined by the upper ten bits of PMADRH:PMADRL, (PMADRH<6:0>:PMADRL<7:5>) with the lower five bits of PMADRL, (PMADRL<7:5>) determining the write latch being loaded. Write operations do not cross these boundaries. At the completion of a program memory write operation, the data in the write latches is reset to contain 0x3FFF. The following steps should be completed to load the write latches and program a row of program memory. These steps are divided into two parts. First, each write latch is loaded with data from the PMDATH:PMDATL using the unlock sequence with LWLO = 1. When the last word to be loaded into the write latch is ready, the LWLO bit is cleared and the unlock sequence executed. This initiates the programming operation, writing all the latches into Flash program memory.

- Note: The special unlock sequence is required to load a write latch with data or initiate a Flash programming operation. If the unlock sequence is interrupted, writing to the latches or program memory will not be initiated.

- 1. Set the WREN bit of the PMCON1 register.

- 2. Clear the CFGS bit of the PMCON1 register.

- Set the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the PMADRH:PMADRL register pair with the address of the location to be written.

- 5. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The write latch is now loaded.

- 7. Increment the PMADRH:PMADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- 11. Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The entire program memory latch content is now written to Flash program memory.

- **Note:** The program memory write latches are reset to the blank state (0x3FFF) at the completion of every write or erase operation. As a result, it is not necessary to load all the program memory write latches. Unloaded latches will remain in the blank state.

An example of the complete write sequence is shown in Example 10-3. The initial address is loaded into the PMADRH:PMADRL register pair; the data is loaded using indirect addressing.

| D DD0 5 0   |                           | PIC | C16(L)F1 | 778 | PIC16(L)F1777/9 |   |   |   |   |

|-------------|---------------------------|-----|----------|-----|-----------------|---|---|---|---|

| RxyPPS<5:0> | Output Signal             | Α   | В        | С   | Α               | В | С | D | Е |

| 110001      | MD4_out <sup>(3)</sup>    |     |          |     |                 | • | _ | • |   |

| 110000      | MD3_out                   |     | •        | ٠   | _               | • | _ | • | _ |

| 101111      | MD2_out                   | •   |          | •   | •               |   | _ | • | _ |

| 101110      | MD1_out                   | •   |          | •   | •               |   | _ | • | _ |

| 101101      | sync_C8OUT <sup>(3)</sup> |     |          |     | _               | • | _ | • | _ |

| 101100      | sync_C7OUT <sup>(3)</sup> |     |          |     | _               | • | _ | • |   |

| 101011      | sync_C6OUT                | •   |          | •   | •               |   | _ | _ | • |

| 101010      | sync_C5OUT                | •   |          | •   | •               |   | _ | • | _ |

| 101001      | sync_C4OUT                |     | •        | •   | _               | • | _ | • | _ |

| 101000      | sync_C3OUT                |     | •        | •   | _               | • | _ | • |   |

| 100111      | sync_C2OUT                | •   |          | •   | •               |   | _ |   | • |

| 100110      | sync_C1OUT                | •   |          | •   | •               |   | _ | • | _ |

| 100101      | DT                        |     | •        | •   | _               | • | • | _ |   |

| 100100      | TX/CK                     |     | •        | •   | _               | • | • | _ | _ |

| 100011      | SDO                       |     | •        | •   | _               | • | • | _ | _ |

| 100010      | SDA                       |     | •        | •   | _               | • | • | _ |   |

| 100001      | SCK/SCL <sup>(1)</sup>    |     | •        | •   | _               | • | • | _ | _ |

| 100000      | PWM12_out <sup>(3)</sup>  |     |          |     | _               | • | _ | • | _ |

| 011111      | PWM11_out                 |     | •        | •   | _               | • | _ | • |   |

| 011110      | PWM6_out                  | •   |          | •   | •               |   | _ | • | _ |

| 011101      | PWM5_out                  | •   |          | •   | •               |   |   | • | _ |

| 011100      | PWM10_out <sup>(3)</sup>  |     |          |     | •               |   | • | _ | _ |

| 011011      | PWM9_out                  | •   |          | •   | •               | _ | • |   | _ |

| 011010      | PWM4_out                  | •   |          | •   | •               |   |   | • |   |

| 011001      | PWM3_out                  | •   |          | •   | •               |   |   | _ | • |

| 011000      | CCP8_out <sup>(3)</sup>   |     |          |     | _               | • | _ | • | _ |

| 010111      | CCP7_out                  |     | •        | •   | _               | • | _ | • | _ |

| 010110      | CCP2_out                  |     | •        | •   | _               | • | • | _ |   |

| 010101      | CCP1_out                  |     | •        | •   | _               | • | • | _ | _ |

| 010100      | COG4D <sup>(1,3)</sup>    |     |          |     | •               |   |   | • | _ |

| 010011      | COG4C <sup>(1,3)</sup>    |     |          |     | •               |   |   | • |   |

| 010010      | COG4B <sup>(1,3)</sup>    |     |          |     | •               |   |   | _ | • |

| 010001      | COG4A <sup>(1,3)</sup>    |     |          |     |                 | • | • | _ |   |

| 010000      | COG3D <sup>(1)</sup>      | •   |          | •   | •               |   | _ | • |   |

| 001111      | COG3C <sup>(1)</sup>      | •   |          | •   | •               |   | _ | • |   |

| 001110      | COG3B <sup>(1)</sup>      | •   |          | •   | •               |   | _ | _ | • |

| 001101      | COG3A <sup>(1)</sup>      | •   | <u> </u> | •   |                 | • | • |   |   |

| 001100      | COG2D <sup>(1)</sup>      | -   | •        | •   | _               | • | _ | • |   |

| 001011      | COG2C <sup>(1)</sup>      |     | •        | •   |                 | • | _ | • | _ |

| 001010      | COG2B <sup>(1)</sup>      |     | •        | •   |                 | • |   | • |   |

#### TABLE 12-2: AVAILABLE PORTS FOR OUTPUT BY PERIPHERAL<sup>(2)</sup>

**Note 1:** TRIS control is overridden by the peripheral as required.

**2:** Unsupported peripherals will output a '0'.

3: PIC16(L)F1777/9 only.

| Name                     | Bit 7 | Bit 6 | Bit 5 | Bit 4        | Bit 3 | Bit 2     | Bit 1                                 | Bit 0     | Register<br>on page |  |

|--------------------------|-------|-------|-------|--------------|-------|-----------|---------------------------------------|-----------|---------------------|--|

| PPSLOCK                  | _     | _     | _     |              | _     | —         | —                                     | PPSLOCKED | 206                 |  |

| INTPPS                   | _     | _     |       | INTPPS<5:0>  |       |           |                                       |           |                     |  |

| TOCKIPPS                 | _     | _     |       |              | TOCK  | PPS<5:0>  |                                       |           | 205                 |  |

| T1CKIPPS                 | _     | _     |       |              | T1CK  | PPS<5:0>  |                                       |           | 205                 |  |

| T1GPPS                   | _     | —     |       |              | T1GF  | PPS<5:0>  |                                       |           | 205                 |  |

| T3CKIPPS                 | —     | _     |       |              | T3CK  | PPS<5:0>  |                                       |           | 205                 |  |

| T3GPPS                   |       | _     |       |              | T3GF  | PS<5:0>   |                                       |           | 205                 |  |

| T5CKIPPS                 | _     | _     |       |              | T5CK  | PPS<5:0>  |                                       |           | 205                 |  |

| T5GPPS                   | _     | _     |       |              | T5GF  | PPS<5:0>  |                                       |           | 205                 |  |

| T2INPPS                  | _     | _     |       |              | T2IN  | PPS<5:0>  |                                       |           | 205                 |  |

| T4INPPS                  | _     | _     |       |              | T4IN  | PPS<5:0>  |                                       |           | 205                 |  |

| T6INPPS                  | _     | _     |       |              | T6INI | PPS<5:0>  |                                       |           | 205                 |  |

| T8INPPS                  | _     | _     |       |              | T8INI | PPS<5:0>  |                                       |           | 205                 |  |

| CCP1PPS                  | _     | —     |       |              | CCP1  | PPS<5:0>  |                                       |           | 205                 |  |

| CCP2PPS                  | —     | —     |       |              | CCP2  | PPS<5:0>  |                                       |           | 205                 |  |

| CCP7PPS                  | _     | —     |       |              | CCP7  | PPS<5:0>  |                                       |           | 205                 |  |

| CCP8PPS <sup>(1)</sup>   | _     | _     |       |              | CCP8  | PPS<5:0>  |                                       |           | 205                 |  |

| COGIN1PPS                | _     | _     |       |              | COG1  | PPS<5:0>  |                                       |           | 205                 |  |

| COG2INPPS                | _     | _     |       |              | COG2  | PPS<5:0>  |                                       |           | 205                 |  |

| COG3INPPS                | _     | _     |       |              | COG3  | PPS<5:0>  |                                       |           | 205                 |  |

| COG4INPPS <sup>(1)</sup> | _     | _     |       | COG4PPS<5:0> |       |           |                                       |           |                     |  |

| MD1CLPPS                 | _     | _     |       |              | MD1CI | LPPS<5:0> |                                       |           | 205                 |  |

| MD1CHPPS                 | _     | _     |       |              | MD1CI | HPPS<5:0> |                                       |           | 205                 |  |

| MD1MODPPS                | _     | —     |       |              | MD1MC | DPPS<5:0  | >                                     |           | 205                 |  |

| MD2CLPPS                 | —     | —     |       |              | MD2CI | LPPS<5:0> |                                       |           | 205                 |  |

| MD2CHPPS                 |       | —     |       |              | MD2CI | HPPS<5:0> |                                       |           | 205                 |  |

| MD2MODPPS                | —     | —     |       |              | MD2MC | DPPS<5:0  | >                                     |           | 205                 |  |

| MD3CLPPS                 | —     | —     |       |              | MD3CI | _PPS<5:0> |                                       |           | 205                 |  |

| MD3CHPPS                 | —     | —     |       |              | MD3CI | HPPS<5:0> | •                                     |           | 205                 |  |

| MD3MODPPS                | —     | —     |       |              | MD3MC | DPPS<5:0  | >                                     |           | 205                 |  |

| MD4CLPPS <sup>(1)</sup>  | —     | —     |       |              | MD4CI | LPPS<5:0> |                                       |           | 205                 |  |

| MD4CHPPS <sup>(1)</sup>  | _     | —     |       |              | MD4CI | HPPS<5:0> |                                       |           | 205                 |  |

| MD4MODPPS <sup>(1)</sup> | _     | _     |       |              | MD4MC | DPPS<5:0  | >                                     |           | 205                 |  |

| PRG1RPPS                 | _     | _     |       |              | PRG1F | RPPS<5:0> |                                       |           | 205                 |  |

| PRG1FPPS                 | _     | _     |       |              | PRG1  | -PPS<5:0> |                                       |           | 205                 |  |

| PRG2RPPS                 |       | _     |       |              | PRG2F | RPPS<5:0> |                                       |           | 205                 |  |

| PRG2FPPS                 |       |       |       |              | PRG2  |           |                                       |           | 205                 |  |

| PRG3RPPS                 |       | _     |       |              | PRG3F | RPPS<5:0> | · · · · · · · · · · · · · · · · · · · |           | 205                 |  |

| PRG3FPPS                 |       | _     |       |              | PRG3  |           |                                       |           | 205                 |  |

| PRG4RPPS                 |       | —     |       |              | PRG4F | RPPS<5:0> |                                       |           | 205                 |  |

| PRG4FPPS                 |       |       |       |              | PRG4  |           |                                       |           | 205                 |  |

| CLC1IN0PPS               |       | _     |       |              | CLCIN | 0PPS<5:0> | ,                                     |           | 205                 |  |

TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE

© 2015-2016 Microchip Technology Inc.

|                 |                                                                                                                                           | ON1: ADC CO                                                 |                |                  |                  |                     |              |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------|------------------|------------------|---------------------|--------------|

| R/W-0/0         | R/W-0/0                                                                                                                                   | R/W-0/0                                                     | R/W-0/0        | U-0              | R/W-0/0          | R/W-0/0             | R/W-0/0      |

| ADFM            |                                                                                                                                           | ADCS<2:0>                                                   |                | —                | ADNREF           | ADPRE               | EF<1:0>      |

| bit 7           |                                                                                                                                           | _                                                           |                |                  |                  |                     | bit (        |

|                 |                                                                                                                                           |                                                             |                |                  |                  |                     |              |

| Legend:         |                                                                                                                                           |                                                             |                |                  |                  |                     |              |

| R = Readabl     |                                                                                                                                           | W = Writable                                                | bit            | -                | mented bit, read |                     |              |

| u = Bit is und  | changed                                                                                                                                   | x = Bit is unkr                                             | nown           | -n/n = Value a   | at POR and BO    | R/Value at all      | other Resets |

| '1' = Bit is se | t                                                                                                                                         | '0' = Bit is clea                                           | ared           |                  |                  |                     |              |

| bit 7           | 1 = Right jus<br>loaded.<br>0 = Left just<br>loaded.                                                                                      | Result Format stified. Six Most ified. Six Least            | Significant bi | ts of ADRESL a   |                  |                     |              |

| bit 6-4         | 111 = FRC (<br>110 = Fosc/<br>101 = Fosc/<br>100 = Fosc/                                                                                  | /16<br>/4<br>(clock supplied<br>/32<br>/8                   | from an intern | al RC oscillator |                  |                     |              |

| bit 3           | Unimplemer                                                                                                                                | nted: Read as '                                             | 0'             |                  |                  |                     |              |

| bit 2           | ADNREF: ADC Negative Voltage Reference Configuration bit<br>1 = VREF- is connected to external VREF- pin<br>0 = VREF- is connected to VSS |                                                             |                |                  |                  |                     |              |

| bit 1-0         | 11 = VREF+                                                                                                                                | <b>0&gt;:</b> ADC Positivities connected to is connected to | internal Fixed | Voltage Refere   |                  | dule <sup>(1)</sup> |              |

**Note 1:** When selecting the VREF+ pin as the source of the positive reference, be aware that a minimum volta specification exists. See Table 36-16: ADC Conversion Requirements for details.

| Mada              | MODE  | E<4:0> | Output                            | Onenetien                                                 |                            | Timer Control |                                   |

|-------------------|-------|--------|-----------------------------------|-----------------------------------------------------------|----------------------------|---------------|-----------------------------------|

| Mode              | <4:3> | <2:0>  | Operation                         | Operation                                                 | Start                      | Reset         | Stop                              |

|                   |       | 000    |                                   | Software gate (Figure 23-4)                               | <b>ON =</b> 1              | _             | ON = 0                            |

|                   |       | 001    | Period<br>Pulse                   | Hardware gate, active-high<br>(Figure 23-5)               | ON = 1 and<br>TMRx_ers = 1 | _             | ON = 0 or<br>TMRx_ers = 0         |

|                   |       | 010    | r uise                            | Hardware gate, active-low                                 | ON = 1 and<br>TMRx_ers = 0 | _             | ON = 0 or<br>TMRx_ers = 1         |

| Free              | 0.0   | 011    |                                   | Rising or falling edge Reset                              |                            | TMRx_ers      |                                   |

| Running<br>Period | 00    | 100    | Period                            | Rising edge Reset (Figure 23-6)                           |                            | TMRx_ers ↑    | <b>ON =</b> 0                     |

|                   |       | 101    | Pulse                             | Falling edge Reset                                        | -                          | TMRx_ers ↓    |                                   |

|                   |       | 110    | with<br>Hardware                  | Low level Reset                                           | ON = 1                     | TMRx_ers = 0  | ON = 0 or<br>TMRx_ers = 0         |

|                   |       | 111    | Reset                             | High level Reset (Figure 23-7)                            |                            | TMRx_ers = 1  | ON = 0 or<br>TMRx_ers = 1         |

|                   |       | 000    | One-shot                          | Software start (Figure 23-8)                              | <b>ON =</b> 1              | _             |                                   |

|                   |       | 001    | Edge                              | Rising edge start (Figure 23-9)                           | ON = 1 and<br>TMRx_ers ↑   | _             |                                   |

|                   |       | 010    | triggered<br>start                | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | _             |                                   |

|                   |       | 011    | (Note 1)                          | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _             | ON = 0<br>or                      |

| One-shot          | 01    | 100    | Edge                              | Rising edge start and<br>Rising edge Reset (Figure 23-10) | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers ↑    | Next clock<br>after<br>TMRx = PRx |

|                   |       | 101    | triggered<br>start<br>and         | Falling edge start and<br>Falling edge Reset              | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers ↓    | (Note 2)                          |

|                   |       | 110    | hardware<br>Reset                 | Rising edge start and<br>Low level Reset (Figure 23-11)   | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers = 0  |                                   |

|                   |       | 111    | (Note 1)                          | Falling edge start and<br>High level Reset                | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers = 1  |                                   |

|                   |       | 000    |                                   | Rese                                                      | erved                      |               |                                   |

|                   |       | 001    | Edge                              | Rising edge start<br>(Figure 23-12)                       | ON = 1 and<br>TMRx_ers ↑   | —             | ON = 0<br>or                      |

| Mono-stable       |       | 010    | triggered<br>start                | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | -             | Next clock<br>after               |

|                   |       | 011    | (Note 1)                          | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _             | TMRx = PRx<br>(Note 3)            |

| Reserved          | 10    | 100    |                                   | Rese                                                      | erved                      |               |                                   |

| Reserved          |       | 101    |                                   | Rese                                                      | erved                      |               |                                   |

|                   |       | 110    | Level<br>triggered                | High level start and<br>Low level Reset (Figure 23-13)    | ON = 1 and<br>TMRx_ers = 1 | TMRx_ers = 0  | ON = 0 or                         |

| One-shot          |       | 111    | start<br>and<br>hardware<br>Reset | Low level start &<br>High level Reset                     | ON = 1 and<br>TMRx_ers = 0 | TMRx_ers = 1  | Held in Rese<br>(Note 2)          |

| Reserved          | 11    | xxx    |                                   | Rese                                                      | erved                      |               |                                   |

TABLE 23-1: TIMER2 OPERATING MODES

**Note** 1: If ON = 0 then an edge is required to restart the timer after ON = 1.

2: When TMRx = PRx then the next clock clears ON and stops TMRx at 00h.

3: When TMRx = PRx then the next clock stops TMRx at 00h but does not clear ON.

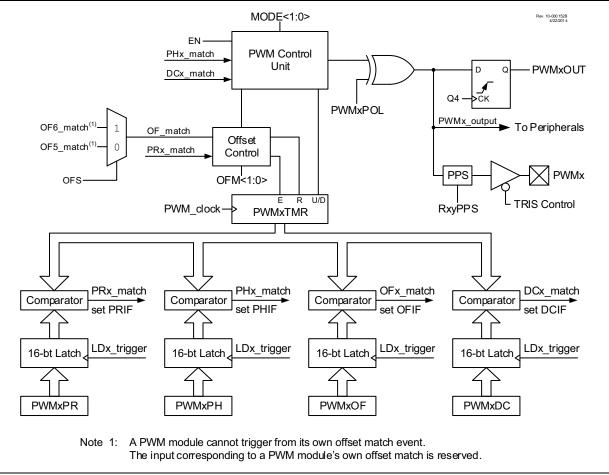

#### 26.0 16-BIT PULSE-WIDTH MODULATION (PWM) MODULE

The Pulse-Width Modulation (PWM) module generates a pulse-width modulated signal determined by the phase, duty cycle, period, and offset event counts that are contained in the following registers:

- PWMxPH register

- PWMxDC register

- PWMxPR register

- PWMxOF register

Figure 26-1 shows a simplified block diagram of the PWM operation. Each PWM module has four modes of operation:

- Standard

- Set On Match

- Toggle On Match

- · Center Aligned

### TABLE 26-1:AVAILABLE 16-BIT PWM<br/>MODULES

| Device          | PWM5 | PWM6 | PWM11 | PWM12 |

|-----------------|------|------|-------|-------|

| PIC16(L)F1778   | •    | •    | •     |       |

| PIC16(L)F1777/9 | •    | •    | ٠     | •     |

#### FIGURE 26-1: 16-BIT PWM BLOCK DIAGRAM

For a more detailed description of each PWM mode, refer to **Section 26.2** "**PWM Modes**".

Each PWM module has four offset modes:

- · Independent Run

- Slave Run with Synchronous Start

- One-Shot Slave with Synchronous Start

- Continuous Run Slave with Synchronous Start and Timer Reset

Using the offset modes, each PWM module can offset its waveform relative to any other PWM module in the same device. For a more detailed description of the offset modes refer to **Section 26.3 "Offset Modes"**.

Every PWM module has a configurable reload operation to ensure all event count buffers change at the end of a period, thereby avoiding signal glitches. Figure 26-2 shows a simplified block diagram of the reload operation. For a more detailed description of the reload operation, refer to Section **Section 26.4 "Reload Operation**".

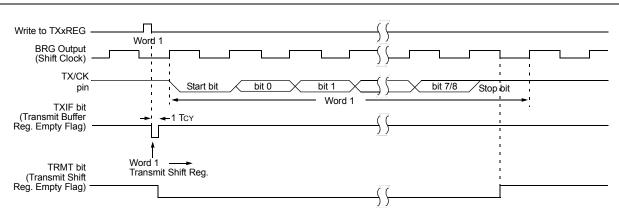

#### 33.1.1.5 TSR Status

The TRMT bit of the TXxSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXxREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

#### 33.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXxSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXxSTA register is the ninth, and Most Significant data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXxREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXxREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 33.1.2.7** "Address **Detection**" for more information on the Address mode.

- 33.1.1.7 Asynchronous Transmission Set-up:

- Initialize the SPxBRGH:SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set the SCKP bit if inverted transmit is desired.

- 5. Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TXxREG register. This will start the transmission.

#### FIGURE 33-3: ASYNCHRONOUS TRANSMISSION

| (    | Configuration Bi | ts   |                     | David Data Farmula |  |

|------|------------------|------|---------------------|--------------------|--|

| SYNC | BRG16            | BRGH | BRG/EUSART Mode     | Baud Rate Formula  |  |

| 0    | 0                | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]    |  |

| 0    | 0                | 1    | 8-bit/Asynchronous  |                    |  |

| 0    | 1                | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]    |  |

| 0    | 1                | 1    | 16-bit/Asynchronous |                    |  |

| 1    | 0                | x    | 8-bit/Synchronous   | Fosc/[4 (n+1)]     |  |

| 1    | 1                | x    | 16-bit/Synchronous  |                    |  |

#### TABLE 33-3: BAUD RATE FORMULAS

**Legend:** x = Don't care, n = value of SPxBRGH:SPxBRGL register pair.

#### TABLE 33-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name     | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|----------|--------------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| BAUD1CON | ABDOVF       | RCIDL | _     | SCKP  | BRG16 | _     | WUE   | ABDEN | 505                 |

| RC1STA   | SPEN         | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 504                 |

| SP1BRGL  | SP1BRG<7:0>  |       |       |       |       |       |       |       | 506                 |

| SP1BRGH  | SP1BRG<15:8> |       |       |       |       |       |       |       | 506                 |

| TX1STA   | CSRC         | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 503                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

\* Page provides register information.

| PIC16LF1777/8/9 |                        | Operating Conditions: (unless otherwise stated)<br>Low-Power Sleep Mode |      |       |        |       |            |                                                             |  |  |

|-----------------|------------------------|-------------------------------------------------------------------------|------|-------|--------|-------|------------|-------------------------------------------------------------|--|--|

| PIC16F17        | 77/8/9                 | Low-Power Sleep Mode, VREGPM = 1                                        |      |       |        |       |            |                                                             |  |  |

| Param           | Device Characteristics | Min.                                                                    | Тур† | Max.  | Max.   | Units | Conditions |                                                             |  |  |

| No.             | Device Characteristics | WIIII.                                                                  | וקעי | +85°C | +125°C | Units | Vdd        | Note                                                        |  |  |

| D023            | Base IPD               |                                                                         | 0.05 | 1.0   | 8.0    | μA    | 1.8        | WDT, BOR, FVR, and SOSC                                     |  |  |

|                 |                        | —                                                                       | 0.08 | 2.0   | 9.0    | μA    | 3.0        | disabled, all Peripherals Inactive                          |  |  |

| D023            | Base IPD               |                                                                         | 0.3  | 2.4   | 10     | μA    | 2.3        | WDT, BOR, FVR, and SOSC                                     |  |  |

|                 |                        |                                                                         | 0.4  | 4     | 12     | μA    | 3.0        | disabled, all Peripherals Inactive,<br>Low-Power Sleep mode |  |  |

|                 |                        | _                                                                       | 0.5  | 6     | 15     | μA    | 5.0        | Low-Power Sleep mode                                        |  |  |

| D023A           | Base IPD               | _                                                                       | 9.8  | 17    | 28     | μA    | 2.3        | WDT, BOR, FVR and SOSC                                      |  |  |

|                 |                        | _                                                                       | 10.3 | 20    | 40     | μA    | 3.0        | disabled, all Peripherals inactive,                         |  |  |

|                 |                        | _                                                                       | 11.5 | 22    | 44     | μA    | 5.0        | Normal Power Sleep mode<br>VREGPM = 0                       |  |  |

| D024            |                        | _                                                                       | 0.5  | 6     | 14     | μA    | 1.8        | WDT Current                                                 |  |  |

|                 |                        | —                                                                       | 0.8  | 7     | 17     | μA    | 3.0        |                                                             |  |  |

| D024            |                        | —                                                                       | 0.8  | 6     | 15     | μA    | 2.3        | WDT Current                                                 |  |  |

|                 |                        | —                                                                       | 0.9  | 7     | 20     | μA    | 3.0        |                                                             |  |  |

|                 |                        | _                                                                       | 1.0  | 8     | 22     | μA    | 5.0        | ]                                                           |  |  |

| D025            |                        | _                                                                       | 15   | 28    | 30     | μA    | 1.8        | FVR Current (ADC)                                           |  |  |

|                 |                        | _                                                                       | 24   | 35    | 38     | μA    | 3.0        |                                                             |  |  |

| D025            |                        | _                                                                       | 18   | 33    | 35     | μA    | 2.3        | FVR Current (ADC)                                           |  |  |

|                 |                        |                                                                         | 24   | 35    | 40     | μA    | 3.0        | 1                                                           |  |  |

|                 |                        |                                                                         | 26   | 37    | 44     | μA    | 5.0        | 1                                                           |  |  |

| D025A           |                        | _                                                                       | 25   | 50    | 55     | μA    | 1.8        | FVR Current (DAC)                                           |  |  |

|                 |                        |                                                                         | 30   | 65    | 70     | μA    | 3.0        | 1                                                           |  |  |

| D025A           |                        | _                                                                       | 30   | 55    | 66     | μA    | 2.3        | FVR Current (DAC)                                           |  |  |

|                 |                        |                                                                         | 32   | 68    | 82     | μA    | 3.0        | 1                                                           |  |  |

|                 |                        |                                                                         | 35   | 77    | 90     | μA    | 5.0        | 1                                                           |  |  |

| D026            |                        | _                                                                       | 7.5  | 25    | 28     | μA    | 3.0        | BOR Current                                                 |  |  |

| D026            |                        | _                                                                       | 10   | 25    | 28     | μA    | 3.0        | BOR Current                                                 |  |  |

|                 |                        |                                                                         | 12   | 28    | 31     | μA    | 5.0        | 1                                                           |  |  |

| D027            |                        | -                                                                       | 0.5  | 4     | 10     | μA    | 3.0        | LPBOR Current                                               |  |  |

| D027            |                        |                                                                         | 0.8  | 6     | 15     | μA    | 3.0        | LPBOR Current                                               |  |  |

|                 |                        |                                                                         | 1    | 8     | 17     | μA    | 5.0        |                                                             |  |  |

| D028            |                        |                                                                         | 0.5  | 5     | 9      | μA    | 1.8        | SOSC Current                                                |  |  |

|                 |                        |                                                                         | 0.8  | 8.5   | 12     | μA    | 3.0        |                                                             |  |  |

| D028            |                        | _                                                                       | 1.1  | 6     | 10     | μA    | 2.3        | SOSC Current                                                |  |  |

|                 |                        | _                                                                       | 1.3  | 8.5   | 20     | μA    | 3.0        |                                                             |  |  |

|                 |                        |                                                                         | 1.4  | 10    | 25     | μA    | 5.0        |                                                             |  |  |

### TABLE 36-3: POWER-DOWN CURRENTS (IPD)<sup>(1,2)</sup>

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

3: ADC clock source is FRC.

#### TABLE 36-4: I/O PORTS (CONTINUED) (CONTINUED)

| Standard | l Operati | ng Conditions (unless otherwi | se stated) |  |

|----------|-----------|-------------------------------|------------|--|

|          |           |                               |            |  |

| Param<br>No. | Sym.  | Characteristic              | Min.               | Тур† | Max. | Units | Conditions                                                             |

|--------------|-------|-----------------------------|--------------------|------|------|-------|------------------------------------------------------------------------|

|              |       | Capacitive Loading Specs on | <b>Output Pins</b> |      |      |       |                                                                        |

| D101*        | COSC2 | OSC2 pin                    | _                  | —    | 15   | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1 |

| D101A*       | Сю    | All I/O pins                |                    |      | 50   | pF    |                                                                        |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in EXTRC mode.

2: Negative current is defined <u>as current sourced by the pin.</u>

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**4:** Including OSC2 in CLKOUT mode.

#### TABLE 36-11: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET PARAMETERS

| Standa       | Standard Operating Conditions (unless otherwise stated) |                                                          |              |              |              |        |                                                         |  |  |  |

|--------------|---------------------------------------------------------|----------------------------------------------------------|--------------|--------------|--------------|--------|---------------------------------------------------------|--|--|--|

| Param<br>No. | Sym.                                                    | Characteristic                                           | Min.         | Тур†         | Max.         | Units  | Conditions                                              |  |  |  |

| 30           | TMCL                                                    | MCLR Pulse Width (low)                                   | 2            | —            | _            | μS     |                                                         |  |  |  |

| 31           | TWDTLP                                                  | Low-Power Watchdog Timer<br>Time-out Period              | 10           | 16           | 27           | ms     | VDD = 3.3V-5V<br>1:512 Prescaler used                   |  |  |  |

| 32           | Tost                                                    | Oscillator Start-up Timer Period <sup>(1)</sup>          |              | 1024         | _            | Tosc   |                                                         |  |  |  |

| 33*          | TPWRT                                                   | Power-up Timer Period, $\overline{PWRTE} = 0$            | 40           | 65           | 140          | ms     |                                                         |  |  |  |

| 34*          | Tioz                                                    | I/O high-impedance from MCLR Low or Watchdog Timer Reset |              | —            | 2.0          | μS     |                                                         |  |  |  |

| 35           | VBOR                                                    | Brown-out Reset Voltage <sup>(2)</sup>                   | 2.55         | 2.70         | 2.85         | V      | BORV = 0                                                |  |  |  |

|              |                                                         |                                                          | 2.30<br>1.80 | 2.45<br>1.90 | 2.60<br>2.10 | V<br>V | BORV = 1 (PIC16F1777/8/9)<br>BORV = 1 (PIC16LF1777/8/9) |  |  |  |

| 35A          | Vlpbor                                                  | Low-Power Brown-out                                      | 1.8          | 2.1          | 2.5          | V      | LPBOR = 1                                               |  |  |  |

| 36*          | VHYST                                                   | Brown-out Reset Hysteresis                               | 0            | 25           | 75           | mV     | $-40^\circ C \le T A \le +85^\circ C$                   |  |  |  |

| 37*          | TBORDC                                                  | Brown-out Reset DC Response<br>Time                      | 1            | 3            | 35           | μS     | $VDD \leq VBOR$                                         |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: By design, the Oscillator Start-up Timer (OST) counts the first 1024 cycles, independent of frequency.

2: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

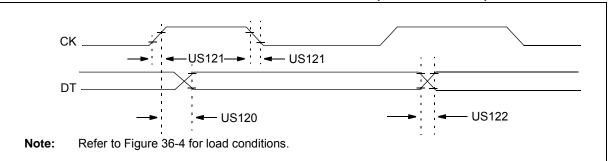

#### FIGURE 36-15: EUSART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 36-23: EUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standaro       | d Operating C                     |                                  |      |      |                                |                                  |

|----------------|-----------------------------------|----------------------------------|------|------|--------------------------------|----------------------------------|

| Param.<br>No.  | Symbol                            | Characteristic                   | Min. | Max. | Units                          | Conditions                       |

| US120 TCKH2DTV | / SYNC XMIT (Master and Slave)    | _                                | 80   | ns   | $3.0V \le V\text{DD} \le 5.5V$ |                                  |

|                |                                   | Clock high to data-out valid     |      | 100  | ns                             | $1.8V \le V\text{DD} \le 5.5V$   |

| US121 TCKRF    | Clock out rise time and fall time | _                                | 45   | ns   | $3.0V \le V\text{DD} \le 5.5V$ |                                  |

|                |                                   | (Master mode)                    |      | 50   | ns                             | $1.8V \le V\text{DD} \le 5.5V$   |

| US122          | TDTRF                             | Data-out rise time and fall time |      | 45   | ns                             | $3.0V \le V\text{DD} \le 5.5V$   |

|                |                                   |                                  | _    | 50   | ns                             | $1.8V \leq V\text{DD} \leq 5.5V$ |

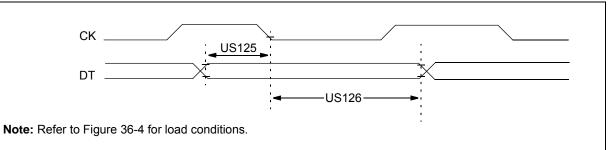

#### FIGURE 36-16: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 36-24: EUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                                                                 |      |      |       |            |  |  |  |

|---------------|---------------------------------------------------------|---------------------------------------------------------------------------------|------|------|-------|------------|--|--|--|

| Param.<br>No. | Symbol                                                  | Characteristic                                                                  | Min. | Max. | Units | Conditions |  |  |  |

| US125         | TDTV2CKL                                                | SYNC RCV (Master and Slave)<br>Data-setup before CK $\downarrow$ (DT hold time) | 10   |      | ns    |            |  |  |  |

| US126         | TCKL2DTL                                                | Data-hold after CK $\downarrow$ (DT hold time)                                  | 15   | _    | ns    |            |  |  |  |

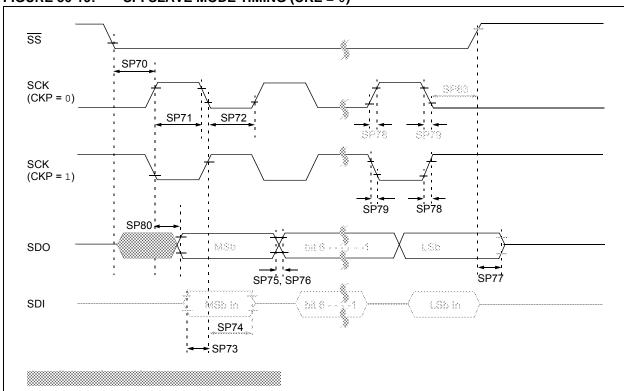

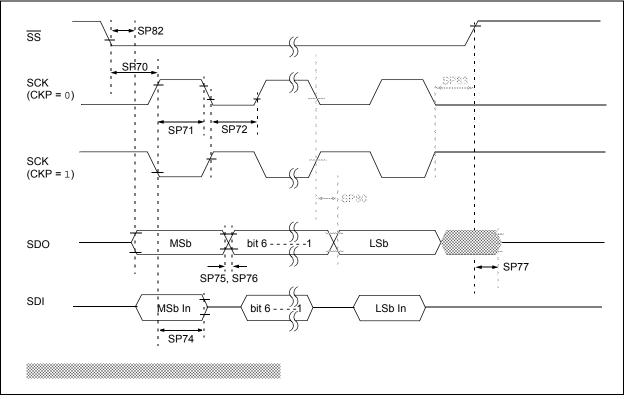

#### FIGURE 36-19: SPI SLAVE MODE TIMING (CKE = 0)

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

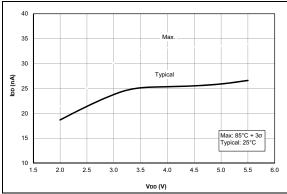

FIGURE 37-37: IPD, Fixed Voltage Reference (FVR), ADC, PIC16F1777/8/9 Only.

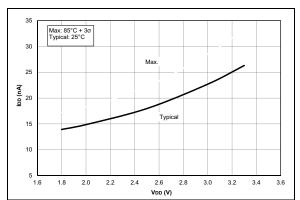

FIGURE 37-38: IPD, Fixed Voltage Reference (FVR), DAC/Comparator, PIC16LF1777/8/9 Only.

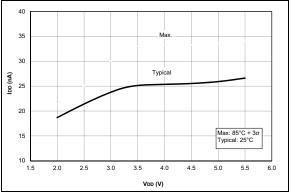

FIGURE 37-39: IPD, Fixed Voltage Reference (FVR), DAC/Comparator, PIC16F1777/8/9 Only.

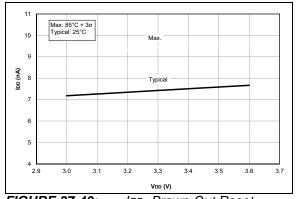

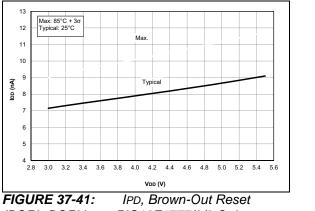

FIGURE 37-40: IPD, Brown-Out Reset (BOR), BORV = 1, PIC16LF1777/8/9 Only.

(BOR), BORV = 1, PIC16F1777/8/9 Only.

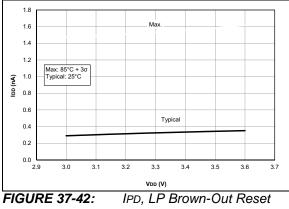

(LPBOR = 0), PIC16LF1777/8/9 Only.