#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 3x5b, 3x10b                                                |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1778-e-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Digital Peripherals**

- Four Configurable Logic Cells (CLC):

Integrated combinational and state logic

- Four Complementary Output Generators (COG):

Push-pull, Full-Bridge and Steering modes

- Four Capture/Compare/PWM (CCP) Modules

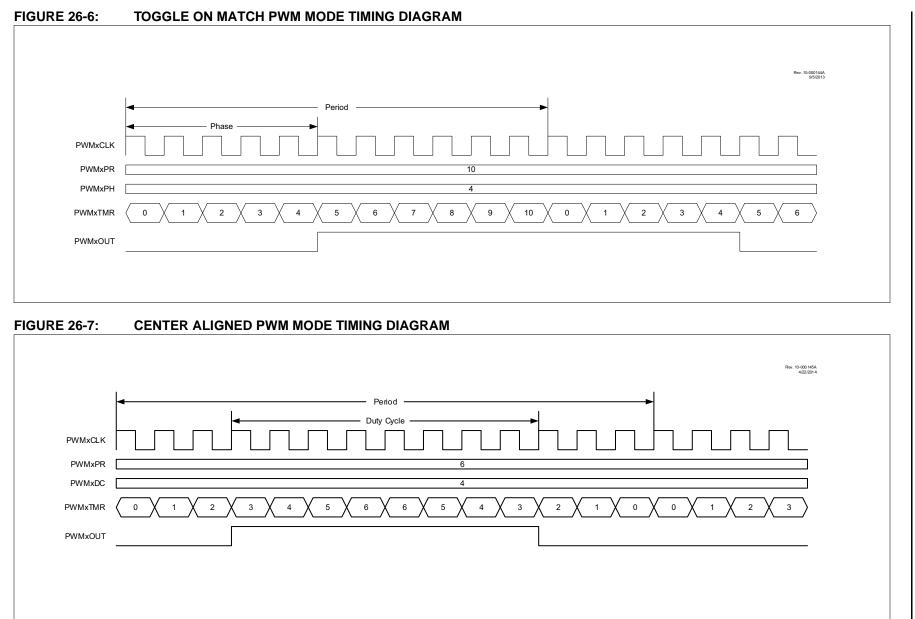

- Pulse-Width Modulator (PWM):

- Four 16-bit PWMs

- Independent timers

- Multiple output modes (Edge-, Center-Aligned, set and toggle on register match)

- User settings for phase, duty cycle, period, offset and polarity

- 16-bit timer capability

- Three 10-bit PWMs

- Digital Signal Modulator (DSM):

- Modulates a carrier signal with a digital data to create custom carrier synchronized output waveforms

- Part of LED dimming engine

- Peripheral Pin Select (PPS):

- I/O remapping of digital peripherals

- Serial Communications:

- Enhanced USART (EUSART)

- SPI, I<sup>2</sup>C, RS-232, RS-485, LIN compatible

- Auto-Baud Detect, auto-wake-up on start

- Up to 25 I/O Pins:

- Individually programmable pull-ups

- Slew rate control

- Interrupt-on-change with edge-select

### **Clocking Structure**

- Precision Internal Oscillator:

- ±1% at calibration

- Selectable frequency range 32 MHz to 31 kHz

- 31 kHz Low-Power Internal Oscillator

- 4x Phase-Locked Loop (PLL) for up to 32 MHz Internal Operation

- External Oscillator Block with Three External Clock modes up to 32 MHz

| TABLE 1:      | PIC              | 16(L)                           | F1//3                          | 5/6/7/                   | 8/9 F             |                         | ILY                 | IYP                   | ES              |              |     |                   |     |     |        |                   |                       |                   |                       |        |                      |                      |

|---------------|------------------|---------------------------------|--------------------------------|--------------------------|-------------------|-------------------------|---------------------|-----------------------|-----------------|--------------|-----|-------------------|-----|-----|--------|-------------------|-----------------------|-------------------|-----------------------|--------|----------------------|----------------------|

| Device        | Data Sheet Index | Program Flash Memory<br>(bytes) | Program Flash Memory<br>(word) | High Endurance Flash (B) | Data SRAM (Bytes) | I/O Pins <sup>(1)</sup> | 8-Bit/16-Bit Timers | High-Speed Comparator | 10-bit ADC (ch) | 5/10-bit DAC | ССР | 10-bit/16-bit PWM | 900 | CLC | Op Amp | Zero Cross Detect | Programmable Ramp Gen | High-Current I/Os | Peripheral Pin Select | EUSART | I <sup>2</sup> C/SPI | Debug <sup>(2)</sup> |

| PIC16(L)F1773 | (A)              | 7K                              | 4K                             | 128                      | 512               | 25                      | 5/3                 | 6                     | 17              | 3/3          | 3   | 3/3               | 3   | 4   | 3      | 1                 | 3                     | 2                 | Υ                     | 1      | 1                    | I                    |

| PIC16(L)F1776 | (A)              | 14K                             | 8K                             | 128                      | 1K                | 25                      | 5/3                 | 6                     | 17              | 3/3          | 3   | 3/3               | 3   | 4   | 3      | 1                 | 3                     | 2                 | Υ                     | 1      | 1                    | 1                    |

| PIC16(L)F1777 | (B)              | 14K                             | 8K                             | 128                      | 1K                | 36                      | 5/3                 | 8                     | 28              | 4/4          | 4   | 4/4               | 4   | 4   | 4      | 1                 | 4                     | 2                 | Υ                     | 1      | 1                    | I                    |

| PIC16(L)F1778 | (B)              | 28K                             | 16K                            | 128                      | 2K                | 25                      | 5/3                 | 6                     | 17              | 3/3          | 3   | 3/3               | 3   | 4   | 3      | 1                 | 3                     | 2                 | Υ                     | 1      | 1                    | I                    |

| PIC16(L)F1779 | (B)              | 28K                             | 16K                            | 128                      | 2K                | 36                      | 5/3                 | 8                     | 28              | 4/4          | 4   | 4/4               | 4   | 4   | 4      | 1                 | 4                     | 2                 | Υ                     | 1      | 1                    | I                    |

Note 1: One pin is input-only.

2: I – Debugging integrated on chip.

Data Sheet Index:

- A: DS40001810

- 1810 PIC16(L)F1773/6 Data Sheet, 28-Pin, 8-bit Flash Microcontrollers

B: DS40001819 PIC16(

PIC16(L)F1777/8/9 Data Sheet, 28/40/44-Pin, 8-bit Flash Microcontrollers

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

TABLE 1: PIC16(L)F1773/6/7/8/9 FAMILY TYPES

# PIC16(L)F1777/8/9

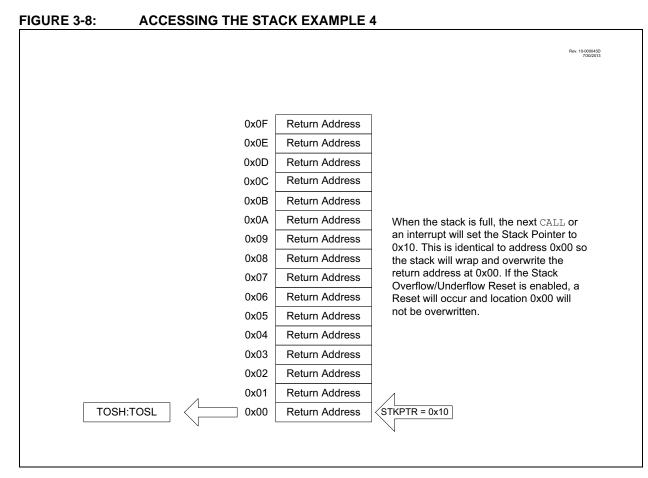

### 3.6.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

### 3.7 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- · Traditional Data Memory

- · Linear Data Memory

- Program Flash Memory

#### 4.6 Device ID and Revision ID

The 14-bit device ID word is located at 8006h and the 14-bit revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

### 4.7 Register Definitions: Device and Revision

#### REGISTER 4-3: DEVID: DEVICE ID REGISTER

|          | R      | R | R               | R             | R                                                   | R                          |  |  |

|----------|--------|---|-----------------|---------------|-----------------------------------------------------|----------------------------|--|--|

|          |        |   | DEV<            | :13:8>        |                                                     |                            |  |  |

|          | bit 13 |   |                 |               |                                                     | bit 8                      |  |  |

|          |        |   |                 |               |                                                     |                            |  |  |

| R        | R      | R | R               | R             | R                                                   | R                          |  |  |

| DEV<7:0> |        |   |                 |               |                                                     |                            |  |  |

|          |        |   |                 |               |                                                     | bit 0                      |  |  |

|          | R      |   | bit 13<br>R R R | DEV<br>bit 13 | R         R         R         R         R         R | DEV<13:8>           bit 13 |  |  |

#### Legend:

R = Readable bit

'1' = Bit is set '0' = Bit is cleared

bit 13-0 **DEV<13:0>:** Device ID bits

| Device      | DEVID<13:0> Values                |

|-------------|-----------------------------------|

| PIC16F1777  | 11 0000 1000 1110 ( <b>308E</b> ) |

| PIC16F1778  | 11 0000 1000 1111 ( <b>308F</b> ) |

| PIC16F1779  | 11 0000 1001 0000 ( <b>3090</b> ) |

| PIC16LF1777 | 11 0000 1001 0001 ( <b>3091</b> ) |

| PIC16LF1778 | 11 0000 1001 0010 ( <b>3092</b> ) |

| PIC16LF1779 | 11 0000 1001 0011 ( <b>3093</b> ) |

# PIC16(L)F1777/8/9

| FIGURE 6-3:               | RESET START-UP SEQUENCE |

|---------------------------|-------------------------|

|                           |                         |

| Internal POR              |                         |

| Power-up Timer            |                         |

| MCLR                      |                         |

| Internal RESET            |                         |

|                           | Oscillator Modes        |

| External Crystal          |                         |

| Oscillator Start-up Timer |                         |

| Oscillator<br>Fosc        |                         |

| Internal Oscillator       |                         |

| Oscillator                |                         |

| Fosc                      |                         |

| External Clock (EC)       |                         |

| CLKIN                     |                         |

| Fosc                      |                         |

|                           |                         |

# PIC16(L)F1777/8/9

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------|------------|-------|-------|-------|--------|---------------------|

| BORCON | SBOREN | BORFS  | _     | _          | _     |       |       | BORRDY | 121                 |

| PCON   | STKOVF | STKUNF |       | RWDT       | RMCLR | RI    | POR   | BOR    | 125                 |

| STATUS |        |        | _     | TO         | PD    | Z     | DC    | С      | 40                  |

| WDTCON | —      | —      |       | WDTPS<4:0> |       |       |       |        | 154                 |

#### TABLE 6-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

| R/W-0/0          | R/W-0/0      | R/W-0/0                            | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|--------------|------------------------------------|-----------------|----------------|------------------|------------------|-------------|

| _                | TMR8IE       | TMR5GIE                            | TMR5IE          | TMR3GIE        | TMR3IE           | TMR6IE           | TRM4IE      |

| bit 7            |              |                                    |                 |                |                  |                  | bit (       |

|                  |              |                                    |                 |                |                  |                  |             |

| Legend:          |              |                                    |                 |                |                  |                  |             |

| R = Readable     | bit          | W = Writable                       | bit             | U = Unimplem   | nented bit, read | as '0'           |             |

| u = Bit is uncł  | nanged       | x = Bit is unkr                    | iown            | -n/n = Value a | t POR and BO     | R/Value at all c | ther Resets |

| '1' = Bit is set |              | '0' = Bit is clea                  | ared            |                |                  |                  |             |

| bit 7            | Unimplemer   | nted: Read as '                    | )'              |                |                  |                  |             |

| bit 6            | -            | R8 to T8PR Ma                      |                 | Enable bit     |                  |                  |             |

|                  |              | the Timer8 to Ta                   | •               |                |                  |                  |             |

|                  |              | the Timer8 to T                    |                 |                |                  |                  |             |

| bit 5            | TMR5GIE: T   | imer5 Gate Inte                    | rrupt Enable b  | bit            |                  |                  |             |

|                  | 1 = Enables  | the Timer5 gate                    | acquisition in  | nterrupt       |                  |                  |             |

|                  | 0 = Disables | the Timer5 gate                    | e acquisition i | nterrupt       |                  |                  |             |

| bit 4            | TMR5IE: TM   | R5 to Overflow                     | Interrupt Ena   | ble bit        |                  |                  |             |

|                  |              | the Timer5 to T                    |                 |                |                  |                  |             |

|                  |              | the Timer5 to T                    |                 | •              |                  |                  |             |

| bit 3            |              | imer3 Gate Inte                    |                 |                |                  |                  |             |

|                  |              | the Timer3 gate<br>the Timer3 gate |                 |                |                  |                  |             |

| bit 2            |              | R3 to Overflow                     | •               |                |                  |                  |             |

|                  |              | the Timer3 to T                    | •               |                |                  |                  |             |

|                  |              | the Timer3 to T                    |                 |                |                  |                  |             |

| bit 1            |              | R6 to T6PR Ma                      |                 | •              |                  |                  |             |

|                  |              | the Timer6 to T                    | •               |                |                  |                  |             |

|                  |              | the Timer6 to T                    |                 |                |                  |                  |             |

| bit 0            | TMR4IE: TM   | R4 to T4PR Ma                      | tch Interrupt I | Enable bit     |                  |                  |             |

|                  |              | the Timer4 to T4                   |                 |                |                  |                  |             |

|                  | 0 = Disables | the Timer4 to T                    | 4PR match in    | torrunt        |                  |                  |             |

#### REGISTER 7-5: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

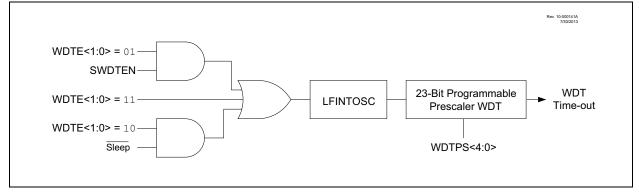

### 9.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- · Independent clock source

- Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Multiple Reset conditions

- Operation during Sleep

#### FIGURE 9-1: WATCHDOG TIMER BLOCK DIAGRAM

# TABLE 10-1:FLASH MEMORY<br/>ORGANIZATION BY DEVICE

| Device          | Row Erase<br>(words) | Write<br>Latches<br>(words) |

|-----------------|----------------------|-----------------------------|

| PIC16(L)F1778   | 32                   | 32                          |

| PIC16(L)F1777/9 | 52                   | 52                          |

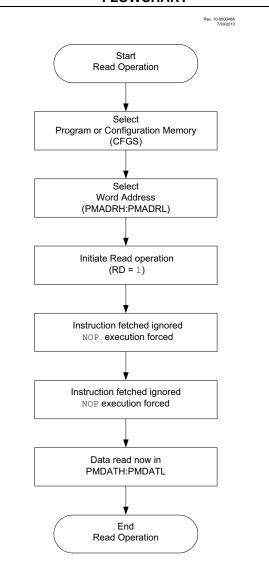

## 10.2.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the desired address to the PMADRH:PMADRL register pair.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Then, set control bit RD of the PMCON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle, in the PMDATH:PMDATL register pair; therefore, it can be read as two bytes in the following instructions.

The PMDATH:PMDATL register pair will hold this value until another read or until it is written to by the user.

| Note: | The two instructions following a program    |

|-------|---------------------------------------------|

|       | memory read are required to be NOPS.        |

|       | This prevents the user from executing a     |

|       | 2-cycle instruction on the next instruction |

|       | after the RD bit is set.                    |

#### FIGURE 10-1:

#### FLASH PROGRAM MEMORY READ FLOWCHART

### 18.7 Register Definitions: DAC Control

Long bit name prefixes for the 10-bit DAC peripherals are shown in Table 18-2. Refer to **Section 1.1** "**Register and Bit naming conventions**" for more information

#### TABLE 18-2:

| Peripheral          | Bit Name Prefix |

|---------------------|-----------------|

| DAC1                | DAC1            |

| DAC2                | DAC2            |

| DAC5                | DAC5            |

| DAC6 <sup>(1)</sup> | DAC6            |

**Note 1:** PIC16(L)F1777/9 only.

#### REGISTER 18-1: DACxCON0: DAC CONTROL REGISTER 0

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| EN      | FM      | OE1     | OE2     | PSS     | <1:0>   | NSS     | <1:0>   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: DAC Enable bit                                           |

|---------|--------------------------------------------------------------|

|         | 1 = DACx is enabled                                          |

|         | 0 = DACx is disabled                                         |

| bit 6   | FM: DAC Reference Format bit                                 |

|         | 1 = DACx reference selection is left justified               |

|         | 0 = DACx reference selection is right justified              |

| bit 5   | OE1: DAC Voltage Output Enable bit                           |

|         | 1 = DACx voltage level is also an output on the DACxOUT1 pin |

|         | 0 = DACx voltage level is disconnected from the DACxOUT1 pin |

| bit 4   | OE2: DAC Voltage Output Enable bit                           |

|         | 1 = DACx voltage level is also an output on the DACxOUT2 pin |

|         | 0 = DACx voltage level is disconnected from the DACxOUT2 pin |

| bit 3-2 | PSS<1:0>: DAC Positive Source Select bits                    |

|         | 11 = DACxREF1+ (DAC5/6) or Reserved (DAC1/2)                 |

|         | 10 = FVR_buffer2                                             |

|         | 01 = DACxREF0+                                               |

|         | 00 = VDD                                                     |

| bit 1-0 | NSS<1:0>: DAC Negative Source Select bit                     |

|         | 11 = Reserved. Do not use.                                   |

|         | 10 = DACxREF1- (DAC5/6) or Reserved (DAC1/2)                 |

|         | 01 = DACxREF0-                                               |

|         | 00 = Agnd(AVss)                                              |

|         |                                                              |

| U-0                                                                 | U-0 | U-0  |                                                       |     |     |         |         |  |

|---------------------------------------------------------------------|-----|------|-------------------------------------------------------|-----|-----|---------|---------|--|

|                                                                     |     | 0-0  | U-0                                                   | U-0 | U-0 | R/W-0/0 | R/W-0/0 |  |

|                                                                     | _   | —    | _                                                     | _   | —   | INTP    | INTN    |  |

| bit 7                                                               |     |      |                                                       |     |     |         | bit 0   |  |

|                                                                     |     |      |                                                       |     |     |         |         |  |

| Legend:                                                             |     |      |                                                       |     |     |         |         |  |

| R = Readable bit W = Writable bit                                   |     | bit  | U = Unimplemented bit, read as '0'                    |     |     |         |         |  |

| u = Bit is unchanged x = Bit is unknown                             |     | iown | -n/n = Value at POR and BOR/Value at all other Resets |     |     |         |         |  |

| '1' = Bit is set '0' = Bit is cleared                               |     |      | ared                                                  |     |     |         |         |  |

|                                                                     |     |      |                                                       |     |     |         |         |  |

| bit 7-2 Unimplemented: Read as '0'                                  |     |      |                                                       |     |     |         |         |  |

| bit 1 INTP: Comparator Interrupt on Positive Going Edge Enable bits |     |      |                                                       |     |     |         |         |  |

#### REGISTER 19-2: CMxCON1: COMPARATOR Cx CONTROL REGISTER 1

1 = The CxIF interrupt flag will be set upon a positive going edge of the CxOUT bit

0 = No interrupt flag will be set on a positive going edge of the CxOUT bit

#### bit 0 INTN: Comparator Interrupt on Negative Going Edge Enable bits

1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit

0 = No interrupt flag will be set on a negative going edge of the CxOUT bit

# PIC16(L)F1777/8/9

Note: There are no long and short bit name variants for the following mirror register

#### REGISTER 19-5: CMOUT: COMPARATOR OUTPUT REGISTER

| R-0/0                 | R-0/0                 | R-0/0  | R-0/0  | R-0/0  | R-0/0  | R-0/0  | R-0/0  |

|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|

| MC8OUT <sup>(1)</sup> | MC7OUT <sup>(1)</sup> | MC6OUT | MC5OUT | MC4OUT | MC3OUT | MC2OUT | MC1OUT |

| bit 7                 |                       |        |        |        |        |        | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | MC8OUT: Mirror | Copy of C8OUT bit <sup>(1)</sup> |

|-------|----------------|----------------------------------|

|       |                |                                  |

- bit 6 **MC7OUT:** Mirror Copy of C7OUT bit<sup>(1)</sup>

- bit 5 MC6OUT: Mirror Copy of C6OUT bit

- bit 4 MC5OUT: Mirror Copy of C5OUT bit

- bit 3 MC4OUT: Mirror Copy of C4OUT bit

- bit 2 MC3OUT: Mirror Copy of C3OUT bit

- bit 1 MC2OUT: Mirror Copy of C2OUT bit

- bit 0 MC10UT: Mirror Copy of C10UT bit

Note 1: PIC16LF1777/9 only.

#### 22.6.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 22-4. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

| <b>TABLE 22-4</b> : | TIMER1 | GATE SOURCE | S |

|---------------------|--------|-------------|---|

|---------------------|--------|-------------|---|

| T1GSS | Timer1 Gate Source                                                        |  |  |  |  |

|-------|---------------------------------------------------------------------------|--|--|--|--|

| 11    | Comparator 2 Output sync_C2OUT<br>(optionally Timer1 synchronized output) |  |  |  |  |

| 10    | Comparator 1 Output sync_C1OUT<br>(optionally Timer1 synchronized output) |  |  |  |  |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                   |  |  |  |  |

| 00    | Timer1 Gate Pin                                                           |  |  |  |  |

#### 22.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 22.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 22.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (sync\_C1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization"**.

#### 22.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 gate control. The Comparator 2 output (sync\_C2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization**".

#### 22.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 22-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |  |  |  |

|-------|---------------------------------------------|--|--|--|

|       | as changing the gate polarity may result in |  |  |  |

|       | indeterminate operation.                    |  |  |  |

## 22.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single-pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 22-5 for timing details.

If the Single-Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 22-6 for timing details.

#### 22.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

#### 22.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

| R/W/HC-0/0        | R/W-0/0                      | R/W-0/0            | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|-------------------|------------------------------|--------------------|-----------------|------------------|------------------|----------------|--------------|

| ON <sup>(1)</sup> | CKPS<2:0>                    |                    |                 | OUTP             | S<3:0>           |                |              |

| bit 7             |                              |                    |                 |                  |                  |                | bit C        |

| Legend:           |                              |                    |                 |                  |                  |                |              |

| R = Readable      | bit                          | W = Writable       | bit             | U = Unimplen     | nented bit, read | d as '0'       |              |

| u = Bit is unch   | anged                        | x = Bit is unkr    | nown            | -n/n = Value a   | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set  |                              | '0' = Bit is clea  | ared            | HC = Bit is cle  | eared by hardv   | vare           |              |

|                   |                              |                    |                 |                  |                  |                |              |

| bit 7             | ON: Timerx                   | On bit             |                 |                  |                  |                |              |

|                   | 1 = Timerx                   | is on              |                 |                  |                  |                |              |

|                   | 0 = Timerx                   | is off: all counte | rs and state n  | nachines are res | set              |                |              |

| bit 6-4           | CKPS<2:0>                    | : Timer2-type Cl   | ock Prescale    | Select bits      |                  |                |              |

|                   | 111 = 1:128                  | Prescaler          |                 |                  |                  |                |              |

|                   | 110 = <b>1:64</b>            |                    |                 |                  |                  |                |              |

|                   | 101 = 1:32                   |                    |                 |                  |                  |                |              |

|                   | 100 = 1:16                   |                    |                 |                  |                  |                |              |

|                   | 011 = 1:8 P                  |                    |                 |                  |                  |                |              |

|                   | 010 = 1:4 P<br>001 = 1:2 P   |                    |                 |                  |                  |                |              |

|                   | 001 = 1.2 P<br>000 = 1:1 P   |                    |                 |                  |                  |                |              |

| bit 3-0           |                              | >: Timerx Outpu    | It Postscolor 9 | Soloct hite      |                  |                |              |

| DIL J-U           | 1111 = 1:16                  |                    |                 |                  |                  |                |              |

|                   | 1110 = 1:10<br>1110 = 1:15   |                    |                 |                  |                  |                |              |

|                   | 1101 = 1:14                  |                    |                 |                  |                  |                |              |

|                   | 1100 = 1:13                  | Postscaler         |                 |                  |                  |                |              |

|                   | 1011 <b>= 1:12</b>           | Postscaler         |                 |                  |                  |                |              |

|                   | 1010 <b>= 1:11</b>           | Postscaler         |                 |                  |                  |                |              |

|                   | 1001 = 1:10                  | Postscaler         |                 |                  |                  |                |              |

|                   | 1000 = 1:9 F                 |                    |                 |                  |                  |                |              |

|                   | 0111 = 1:8 Postscaler        |                    |                 |                  |                  |                |              |

|                   | 0110 = 1.7 F                 |                    |                 |                  |                  |                |              |

|                   | 0101 = 1:6 F<br>0100 = 1:5 F |                    |                 |                  |                  |                |              |

|                   | 0100 - 1.5 F                 |                    |                 |                  |                  |                |              |

|                   | 0011 = 1.4 T                 |                    |                 |                  |                  |                |              |

|                   | 0001 = 1:2 F                 |                    |                 |                  |                  |                |              |

|                   | 0000 = 1:1 F                 |                    |                 |                  |                  |                |              |

#### REGISTER 23-2: TxCON: TIMERx CONTROL REGISTER

Note 1: In certain modes, the ON bit will be auto-cleared by hardware. See Section 23.6 "Operation Examples".

DS40001819B-page 336

© 2015-2016 Microchip Technology Inc.

PIC16(L)F1777/8/9

#### 26.3 Offset Modes

The offset modes provide the means to adjust the waveform of a slave PWM module relative to the waveform of a master PWM module in the same device.

#### 26.3.1 INDEPENDENT RUN MODE

In Independent Run mode (OFM = 00), the PWM module is unaffected by the other PWM modules in the device. The PWMxTMR associated with the PWM module in this mode starts counting as soon as the EN bit associated with this PWM module is set and continues counting until the EN bit is cleared. Period events reset the PWMxTMR to zero after which the timer continues to count.

A detailed timing diagram of this mode used with Standard PWM mode is shown in Figure 26-8.

#### 26.3.2 SLAVE RUN MODE WITH SYNC START

In Slave Run mode with Sync Start (OFM = 01), the slave PWMxTMR waits for the master's OF\_match event. When this event occurs, if the EN bit is set, the PWMxTMR begins counting and continues to count until software clears the EN bit. Slave period events reset the PWMxTMR to zero after which the timer continues to count.

A detailed timing diagram of this mode used with Standard PWM mode is shown in Figure 26-9.

#### 26.3.3 ONE-SHOT SLAVE MODE WITH SYNC START

In One-Shot Slave mode with Synchronous Start (OFM = 10), the slave PWMxTMR waits until the master's OF\_match event. The timer then begins counting, starting from the value that is already in the timer, and continues to count until the period match event. When the period event occurs the timer resets to zero and stops counting. The timer then waits until the next master OF\_match event after which it begins counting again to repeat the cycle.

A detailed timing diagram of this mode used with Standard PWM mode is shown in Figure 26-10.

#### 26.3.4 CONTINUOUS RUN SLAVE MODE WITH SYNC START AND TIMER RESET

In Continuous Run Slave mode with Synchronous Start and Timer Reset (OFM = 11) the slave PWMxTMR is inhibited from counting after the slave PWM enable is set. The first master OF\_match event starts the slave PWMxTMR. Subsequent master OF\_match events reset the slave PWMxTMR timer value back to 1 after which the slave PWMxTMR continues to count. The next master OF\_match event resets the slave PWMxTMR back to 1 to repeat the cycle. Slave period events that occur before the master's OF\_match event will reset the slave PWMxTMR to zero after which the timer will continue to count. Slaves operating in this mode must have a PWMxPH register pair value equal to or greater than 1, otherwise the phase match event will not occur precluding the start of the PWM output duty cycle.

The offset timing will persist if both the master and slave PWMxPR values are the same and the Slave Offset mode is changed to Independent Run mode while the PWM module is operating.

A detailed timing diagram of this mode used in Standard PWM mode is shown in Figure 26-11.

| Note: | Unexpected results will occur if the slave |

|-------|--------------------------------------------|

|       | PWM_clock is a higher frequency than the   |

|       | master PWM_clock.                          |

#### 26.3.5 OFFSET MATCH IN CENTER ALIGNED MODE

When a master is operating in Center-Aligned mode the offset match event depends on which direction the PWMxTMR is counting. Clearing the OFO bit of the PWMxOFCON register will cause the OF\_match event to occur when the timer is counting up. Setting the OFO bit of the PWMxOFCON register will cause the OF\_match event to occur when the timer is counting down. The OFO bit is ignored in Non-Center-Aligned modes.

The OFO bit is double buffered and requires setting the LDA bit to take effect when the PWM module is operating.

Detailed timing diagrams of Center-Aligned mode using offset match control in Independent Slave with Sync Start mode can be seen in Figure 26-12 and Figure 26-13.

#### 27.5.2 RISING EVENT

The rising event starts the PWM output active duty cycle period. The rising event is the low-to-high transition of the rising\_event output. When the rising event phase delay and dead-band time values are zero, the primary output starts immediately. Otherwise, the primary output is delayed. The rising event source causes all the following actions:

- Start rising event phase delay counter (if enabled).

- Clear complementary output after phase delay.

- Start falling event input blanking (if enabled).

- Start dead-band delay (if enabled).

- · Set primary output after dead-band delay expires.

#### 27.5.3 FALLING EVENT

The falling event terminates the PWM output active duty cycle period. The falling event is the high-to-low transition of the falling\_event output. When the falling event phase delay and dead-band time values are zero, the complementary output starts immediately. Otherwise, the complementary output is delayed. The falling event source causes all the following actions:

- Start falling event phase delay counter (if enabled).

- · Clear primary output.

- Start rising event input blanking (if enabled).

- · Start falling event dead-band delay (if enabled).

- Set complementary output after dead-band delay expires.

### 27.6 Output Control

Upon disabling, or immediately after enabling the COG module, the primary COG outputs are inactive and complementary COG outputs are active.

#### 27.6.1 OUTPUT ENABLES

There are no output enable controls in the COG module. Instead, each device pin has an individual output selection control called the PPS register. All four COG outputs are available for selection in the PPS register of every pin.

When a COG output is enabled by PPS selection, the output on the pin has several possibilities which depend on the mode, steering control, EN bit, and shutdown state as shown in Table 27-2 and Table 27-3.

## TABLE 27-2: PIN OUTPUT STATES MD<2:0> = 00x

| EN | STR bit | Shutdown | Output               |

|----|---------|----------|----------------------|

| x  | 0       | Inactive | Static steering data |

| x  | 1       | Active   | Shutdown override    |

| 0  | 1       | Inactive | Inactive state       |

| 1  | 1       | Inactive | Active PWM signal    |

## TABLE 27-3: PIN OUTPUT STATES MD<2:0>> 001

| EN | STR bit | Shutdown | Output            |

|----|---------|----------|-------------------|

| х  | х       | Inactive | Inactive state    |

| x  | x       | Active   | Shutdown override |

| 1  | x       | Inactive | Active PWM signal |

#### 27.6.2 POLARITY CONTROL

The polarity of each COG output can be selected independently. When the output polarity bit is set, the corresponding output is active-low. Clearing the output polarity bit configures the corresponding output as active-high. However, polarity affects the outputs in only one of the four shutdown override modes. See **Section 27.10 "Auto-Shutdown Control"** for more details.

Output polarity is selected with the POLA through POLD bits of the COGxCON1 register (Register 27-2).

### 27.7 Dead-Band Control

The dead-band control provides for non-overlapping PWM output signals to prevent shoot-through current in the external power switches. Dead-band time affects the output only in the Half-Bridge mode and when changing direction in the Full-Bridge mode.

The COG contains two dead-band timers. One dead-band timer is used for rising event dead-band control. The other is used for falling event dead-band control. Timer modes are selectable as either:

- · Asynchronous delay chain

- Synchronous counter

The Dead-Band Timer mode is selected for the rising event and falling event dead-band times with the respective RDBS and FDBS bits of the COGxCON1 register (Register 27-2).

In Half-Bridge mode, the rising event dead-band time delays all selected primary outputs from going active for the selected dead-band time after the rising event. COGxA and COGxC are the primary outputs in Half-Bridge mode.

In Half-Bridge mode, the falling event dead-band time delays all selected complementary outputs from going active for the selected dead-band time after the falling event. COGxB and COGxD are the complementary outputs in Half-Bridge mode.

In Full-Bridge mode, the dead-band delay occurs only during direction changes. The modulated output is delayed for the falling event dead-band time after a direction change from forward to reverse. The modulated output is delayed for the rising event dead-band time after a direction change from reverse to forward.

#### 32.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low, effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSPxCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

#### 32.5.6.1 Normal Clock Stretching

Following an ACK if the R/W bit of SSPxSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPxBUF with data to transfer to the master. If the SEN bit of SSPxCON2 is set, the slave hardware will always stretch the clock after the ACK sequence. Once the slave is ready; CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on if the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPxBUF was read before the ninth falling edge of SCL.

- Previous versions of the module did not stretch the clock for a transmission if SSPxBUF was loaded before the ninth falling edge of SCL. It is now always cleared for read requests.

#### 32.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSPxADD.

| Note: | Previous versions of the module did not      |

|-------|----------------------------------------------|

|       | stretch the clock if the second address byte |

|       | did not match.                               |

#### 32.5.6.3 Byte NACKing

When AHEN bit of SSPxCON3 is set; CKP is cleared by hardware after the eighth falling edge of SCL for a received matching address byte. When DHEN bit of SSPxCON3 is set; CKP is cleared after the eighth falling edge of SCL for received data.

Stretching after the eighth falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

## 32.5.6.4 Clock Synchronization and the CKP Bit

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 32-23).

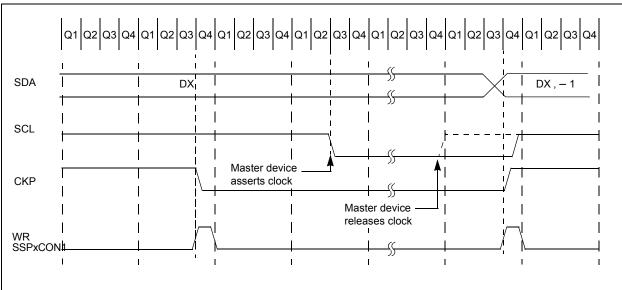

#### FIGURE 32-23: CLOCK SYNCHRONIZATION TIMING

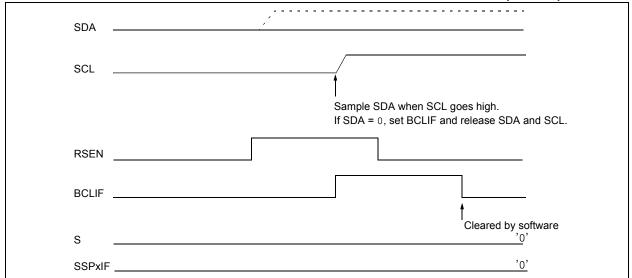

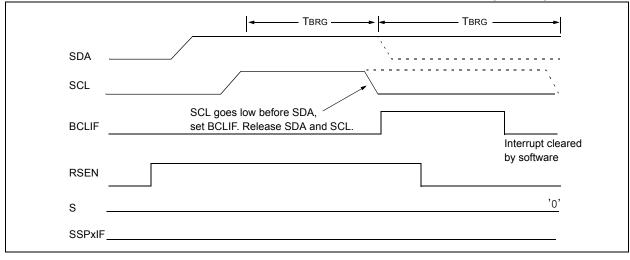

### 32.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 32-36). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 32-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

#### FIGURE 32-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 32-37: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

### 33.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 33.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXxSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART.

#### 33.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 33.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDxCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

#### 33.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXxREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXxREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXxREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

Note: The TSR register is not mapped in data memory, so it is not available to the user.

- 33.5.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPxBRGH:SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXxREG register.

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2015-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-1016-4