Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 × 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 3x5b, 3x10b                                                |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1778-i-mx |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 3: 28-PIN ALLOCATION TABLE (PIC16(L)F1778) (CONTINUED)

|                    | -                      |             |     |      |     |        | • • •                                              | • • | -/ ( |        | -                                             | ,                    |                                                                                                          |                                          |                            |                               |                                                        |           |          |              |       |

|--------------------|------------------------|-------------|-----|------|-----|--------|----------------------------------------------------|-----|------|--------|-----------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------|-------------------------------|--------------------------------------------------------|-----------|----------|--------------|-------|

| NO                 | 28-Pin SPDIP/SOIC/SSOP | 28-Pin UQFN | ADC | VREF | DAC | Op Amp | Comparator                                         | ZCD | PRG  | Timers | MMd                                           | CCP                  | 000                                                                                                      | CLC                                      | Modulator                  | EUSART                        | dssm                                                   | Interrupt | Pull-ups | High Current | Basic |

| OUT <sup>(2)</sup> | _                      | —           | _   | -    | _   | _      | C1OUT<br>C2OUT<br>C3OUT<br>C4OUT<br>C5OUT<br>C6OUT |     | _    | _      | PWM3<br>PWM4<br>PWM5<br>PWM6<br>PWM9<br>PWM11 | CCP1<br>CCP2<br>CCP7 | COG1A<br>COG1B<br>COG1C<br>COG1D<br>COG2A<br>COG2B<br>COG2C<br>COG2D<br>COG3A<br>COG3B<br>COG3C<br>COG3D | CLC1OUT<br>CLC2OUT<br>CLC3OUT<br>CLC4OUT | MD10UT<br>MD20UT<br>MD30UT | DT <sup>(3)</sup><br>ТХ<br>СК | SDO<br>SDA <sup>(3)</sup><br>SCK<br>SCL <sup>(3)</sup> | _         | _        | _            | _     |

Note 1:

Default peripheral input. Input can be moved to any other pin with the PPS input selection register. All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections. 2: 3:

| TABLE 1-3: | PIC16(L)F1777/9 PINOUT DESCRIPTION (CONTINUED) |

|------------|------------------------------------------------|

|------------|------------------------------------------------|

| Name                       | Function           | Input<br>Type | Output<br>Type | Description                                |

|----------------------------|--------------------|---------------|----------------|--------------------------------------------|

| OUT <sup>(2)</sup> (Cont.) | COG2B              |               | CMOS           | Complementary output generator 2 output B. |

|                            | COG2C              |               | CMOS           | Complementary output generator 2 output C. |

|                            | COG2D              |               | CMOS           | Complementary output generator 2 output D. |

|                            | COG3A              |               | CMOS           | Complementary output generator 3 output A. |

|                            | COG3B              |               | CMOS           | Complementary output generator 3 output B. |

|                            | COG3C              |               | CMOS           | Complementary output generator 3 output C. |

|                            | COG3D              |               | CMOS           | Complementary output generator 3 output D. |

|                            | COG4A              |               | CMOS           | Complementary output generator 4 output A. |

|                            | COG4B              |               | CMOS           | Complementary output generator 4 output B. |

|                            | COG4C              |               | CMOS           | Complementary output generator 4 output C. |

|                            | COG4D              |               | CMOS           | Complementary output generator 4 output D. |

|                            | SDA <sup>(3)</sup> |               | OD             | I <sup>2</sup> C data output.              |

|                            | SCK                |               | CMOS           | SPI clock output.                          |

|                            | SCL <sup>(3)</sup> |               | OD             | I <sup>2</sup> C clock output.             |

|                            | SDO                |               | CMOS           | SPI data output.                           |

|                            | TX                 |               | CMOS           | EUSART asynchronous TX data out.           |

|                            | СК                 |               | CMOS           | EUSART synchronous clock out.              |

|                            | DT <sup>(3)</sup>  |               | CMOS           | EUSART synchronous data output.            |

|                            | CLC1OUT            |               | CMOS           | Configurable logic cell 1 output.          |

|                            | CLC2OUT            |               | CMOS           | Configurable logic cell 2 output.          |

|                            | CLC3OUT            |               | CMOS           | Configurable logic cell 3 output.          |

|                            | CLC4OUT            |               | CMOS           | Configurable logic cell 4 output.          |

Legend:

AN = Analog input or output

CMOS = CMOS compatible input or output

OD = Open-Drain

TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

HP = High Power

XTAL = Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

# **1.2 Peripheral Connection Matrix**

Input selection multiplexers on many of the peripherals enable selecting the output of another peripheral such that the signal path is contained entirely within the device. Although the peripheral output can also be routed to a pin, with the PPS selection feature, it is not necessary to do so. Table 1-4 shows all the possible inter-peripheral signal connections. Please refer to corresponding peripheral section to obtain the multiplexer selection codes for the desired connection.

|      | LE 5-10. 51 | LOIALION      |        |                  |                                             |                  |         |         |       |                      |                              |

|------|-------------|---------------|--------|------------------|---------------------------------------------|------------------|---------|---------|-------|----------------------|------------------------------|

| Addr | Name        | Bit 7         | Bit 6  | Bit 5            | Bit 4                                       | Bit 3            | Bit 2   | Bit 1   | Bit 0 | Value on<br>POR, BOR | Value on all<br>other Resets |

| Bank | c 16        |               |        |                  |                                             |                  |         |         |       |                      |                              |

| 80Ch | —           | Unimplemented |        |                  |                                             |                  |         |         |       | —                    | —                            |

| 80Dh | COG3PHR     | —             |        | COG Rising Edge  | e Phase Delay Coι                           | int Register     |         |         |       | 00 0000              | 00 0000                      |

| 80Eh | COG3PHF     | _             | _      | COG Falling Edge | COG Falling Edge Phase Delay Count Register |                  |         |         |       |                      | 00 0000                      |

| 80Fh | COG3BLKR    | _             | _      | COG Rising Edge  | Blanking Count R                            |                  | 00 0000 | 00 0000 |       |                      |                              |

| 810h | COG3BLKF    | _             |        | COG Falling Edge | e Blanking Count F                          |                  | 00 0000 | 00 0000 |       |                      |                              |

| 811h | COG3DBR     | _             |        | COG Rising Edge  | e Dead-band Coun                            |                  | 00 0000 | 00 0000 |       |                      |                              |

| 812h | COG3DBF     | _             |        | COG Falling Edge | e Dead-band Cour                            |                  | 00 0000 | 00 0000 |       |                      |                              |

| 813h | COG3CON0    | EN            | LD     | _                | CS<                                         | <1:0> MD<2:0>    |         |         |       | 00-0 0000            | 00-0 0000                    |

| 814h | COG3CON1    | RDBS          | FDBS   | —                |                                             | POLD             | POLC    | POLB    | POLA  | 00 0000              | 00 0000                      |

| 815h | COG3RIS0    | RIS7          | RIS6   | RIS5             | RIS4                                        | RIS3             | RIS2    | RIS1    | RIS0  | 0000 0000            | 0000 0000                    |

| 816h | COG3RIS1    | RIS15         | RIS14  | RIS13            | RIS12                                       | RIS11            | RIS10   | RIS9    | RIS8  | 0000 0000            | 0000 0000                    |

| 817h | COG3RSIM0   | RSIM7         | RSIM6  | RSIM5            | RSIM4                                       | RSIM3            | RSIM2   | RSIM1   | RSIM0 | 0000 0000            | 0000 0000                    |

| 818h | COG3RSIM1   | RSIM15        | RSIM14 | RSIM13           | RSIM12                                      | RSIM11           | RSIM10  | RSIM9   | RSIM8 | 0000 0000            | 0000 0000                    |

| 819h | COG3FIS0    | FIS7          | FIS6   | FIS5             | FIS4                                        | FIS3             | FIS2    | FIS1    | FIS0  | 0000 0000            | 0000 0000                    |

| 81Ah | COG3FIS1    | FIS15         | FIS14  | FIS13            | FIS12                                       | FIS11            | FIS10   | FIS9    | FIS8  | 0000 0000            | 0000 0000                    |

| 81Bh | COG3FSIM0   | FSIM7         | FSIM6  | FSIM5            | FSIM4                                       | FSIM3            | FSIM2   | FSIM1   | FSIM0 | 0000 0000            | 0000 0000                    |

| 81Ch | COG3FSIM1   | FSIM15        | FSIM14 | FSIM13           | FSIM12                                      | FSIM11           | FSIM10  | FSIM9   | FSIM8 | 0000 0000            | 0000 0000                    |

| 81Dh | COG3ASD0    | ASE           | ARSEN  | ASDBI            | D<1:0>                                      | <1:0> ASDAC<1:0> |         |         | —     | 0001 01              | 0001 01                      |

| 81Eh | COG3ASD1    | AS7E          | AS6E   | AS5E             | AS4E                                        | AS3E             | AS2E    | AS1E    | AS0E  | 0000 0000            | 0000 0000                    |

| 81Fh | COG3STR     | SDATD         | SDATC  | SDATB            | SDATA                                       | STRD             | STRC    | STRB    | STRA  | 0000 0000            | 0000 0000                    |

#### TABLE 3-18: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** Unimplemented, read as '1'.

2: Unimplemented on PIC16LF1777/8/9.

3: Unimplemented on PIC16(L)F1778.

# 8.0 POWER-DOWN MODE (SLEEP)

The Power-Down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3. TO bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- Secondary oscillator

- 7. ADC is unaffected, if the dedicated FRC oscillator is selected.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or high-impedance).

- 9. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- Modules using secondary oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 17.0 "5-Bit Digital-to-Analog Converter (DAC) Module" and Section 14.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

#### 8.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 6.12 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

# REGISTER 17-2: DACxREF: DACx REFERENCE VOLTAGE OUTPUT SELECT REGISTER

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|----------|---------|---------|

| —     | —   | —   |         |         | REF<4:0> |         |         |

| bit 7 |     |     |         |         |          |         | bit 0   |

| -     |     |     |         |         |          |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **REF<4:0>:** DACx Reference Voltage Output Select bits (See Equation 17-1)

#### TABLE 17-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE DACX MODULE

| Name                    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2    | Bit 1    | Bit 0 | Register<br>on page |

|-------------------------|-------|-------|-------|-------|----------|----------|----------|-------|---------------------|

| DAC3CON0                | EN    | _     | OE1   | OE2   | PSS<1:0> |          | NSS<1:0> |       | 244                 |

| DAC4CON0                | EN    |       | OE1   | OE2   | PSS<1:0> |          | NSS<1:0> |       | 244                 |

| DAC7CON0                | EN    |       | OE1   | OE2   | PSS      | <1:0>    | NSS<1:0> |       | 244                 |

| DAC8CON0 <sup>(1)</sup> | EN    |       | OE1   | OE2   | PSS      | <1:0>    | NSS<1:0> |       | 244                 |

| DAC3REF                 |       |       |       |       |          | REF<4:0> |          |       | 245                 |

| DAC4REF                 |       |       |       |       |          | REF<4:0> |          |       | 245                 |

| DAC7REF                 |       |       |       |       | REF<4:0> |          | 245      |       |                     |

| DAC8REF <sup>(1)</sup>  |       |       |       |       |          | REF<4:0> |          |       | 245                 |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DACx module.

**Note 1:** PIC16LF1777/9 only.

# **19.3 Comparator Hysteresis**

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the HYS bit of the CMxCON0 register.

See Comparator Specifications in Table 36-19: Comparator Specifications for more information.

# **19.4 Timer1 Gate Operation**

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 22.6 "Timer1 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 19.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from a comparator can be synchronized with Timer1 by setting the SYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 19-2) and the Timer1 Block Diagram (Figure 22-1) for more information.

### **19.5 Comparator Interrupt**

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (INTP and/or INTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- ON and POL bits of the CMxCON0 register

- CxIE bit of the PIE2 register

- INTP bit of the CMxCON1 register (for a rising edge detection)

- INTN bit of the CMxCON1 register (for a falling edge detection)

- PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

**Note:** Although a comparator is disabled, an interrupt can be generated by changing the output polarity with the POL bit of the CMxCON0 register, or by switching the comparator on or off with the ON bit of the CMxCON0 register.

# 19.6 Comparator Positive Input Selection

Configuring the PCH<3:0> bits of the CMxPSEL register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- · CxIN+ analog pin

- Programmable ramp generator output

- DAC output

- FVR (Fixed Voltage Reference)

- Vss (Ground)

See **Section 14.0** "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 17.0 "5-Bit Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

# 19.7 Comparator Negative Input Selection

The NCH<3:0> bits of the CMxNSEL register direct an analog input pin and internal reference voltage or analog ground to the inverting input of the comparator:

- CxIN- pin

- FVR (Fixed Voltage Reference)

- Analog Ground

Some inverting input selections share a pin with the operational amplifier output function. Enabling both functions at the same time will direct the operational amplifier output to the comparator inverting input.

**Note:** To use CxINy+ and CxINy- pins as analog input, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

| R/W/HC-0/0        | R/W-0/0                                                                                                    | R/W-0/0            | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------|--------------------|----------------|------------------|------------------|----------------|--------------|--|--|--|--|--|

| ON <sup>(1)</sup> |                                                                                                            | CKPS<2:0>          |                |                  | OUTP             | S<3:0>         |              |  |  |  |  |  |

| bit 7             |                                                                                                            |                    |                |                  |                  |                | bit C        |  |  |  |  |  |

| Legend:           |                                                                                                            |                    |                |                  |                  |                |              |  |  |  |  |  |

| R = Readable      | bit                                                                                                        | W = Writable       | bit            | U = Unimplen     | nented bit, read | d as '0'       |              |  |  |  |  |  |

| u = Bit is unch   | anged                                                                                                      | x = Bit is unkr    | nown           | -n/n = Value a   | at POR and BC    | R/Value at all | other Resets |  |  |  |  |  |

| '1' = Bit is set  |                                                                                                            | '0' = Bit is clea  | ared           | HC = Bit is cle  | eared by hardv   | vare           |              |  |  |  |  |  |

|                   |                                                                                                            |                    |                |                  |                  |                |              |  |  |  |  |  |

| bit 7             | ON: Timerx                                                                                                 | On bit             |                |                  |                  |                |              |  |  |  |  |  |

|                   | <ul> <li>1 = Timerx is on</li> <li>0 = Timerx is off: all counters and state machines are reset</li> </ul> |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 0 = Timerx                                                                                                 | is off: all counte | rs and state n | nachines are res | set              |                |              |  |  |  |  |  |

| bit 6-4           | CKPS<2:0>                                                                                                  | : Timer2-type Cl   | ock Prescale   | Select bits      |                  |                |              |  |  |  |  |  |

|                   | 111 = 1:128 Prescaler                                                                                      |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 110 = 1:64  Prescaler                                                                                      |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 101 = 1:32  Prescaler                                                                                      |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 100 = 1:16 Prescaler<br>011 = 1:8 Prescaler                                                                |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 011 = 1:8 Prescaler<br>010 = 1:4 Prescaler                                                                 |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 010 = 1.4 Prescaler<br>001 = 1.2 Prescaler                                                                 |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   |                                                                                                            |                    |                |                  |                  |                |              |  |  |  |  |  |

| bit 3-0           | 000 = 1:1 Prescaler<br>OUTPS<3:0>: Timerx Output Postscaler Select bits                                    |                    |                |                  |                  |                |              |  |  |  |  |  |

| DIL J-U           | 1111 = 1:16                                                                                                |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   |                                                                                                            |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 1110 = 1:15 Postscaler<br>1101 = 1:14 Postscaler                                                           |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 1100 = 1:13                                                                                                | Postscaler         |                |                  |                  |                |              |  |  |  |  |  |

|                   | 1011 <b>= 1:12</b>                                                                                         | Postscaler         |                |                  |                  |                |              |  |  |  |  |  |

|                   | 1010 <b>= 1:11</b>                                                                                         | Postscaler         |                |                  |                  |                |              |  |  |  |  |  |

|                   | 1001 = 1:10                                                                                                | Postscaler         |                |                  |                  |                |              |  |  |  |  |  |

|                   | 1000 = 1:9 Postscaler                                                                                      |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 0111 = 1:8 Postscaler                                                                                      |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 0110 = 1.7  Postscaler                                                                                     |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 0101 = 1:6 Postscaler<br>0100 = 1:5 Postscaler                                                             |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 0100 - 1.5 F                                                                                               |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 0011 = 1.4 T                                                                                               |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 0001 = 1:2 F                                                                                               |                    |                |                  |                  |                |              |  |  |  |  |  |

|                   | 0000 = 1:1 F                                                                                               |                    |                |                  |                  |                |              |  |  |  |  |  |

### REGISTER 23-2: TxCON: TIMERx CONTROL REGISTER

Note 1: In certain modes, the ON bit will be auto-cleared by hardware. See Section 23.6 "Operation Examples".

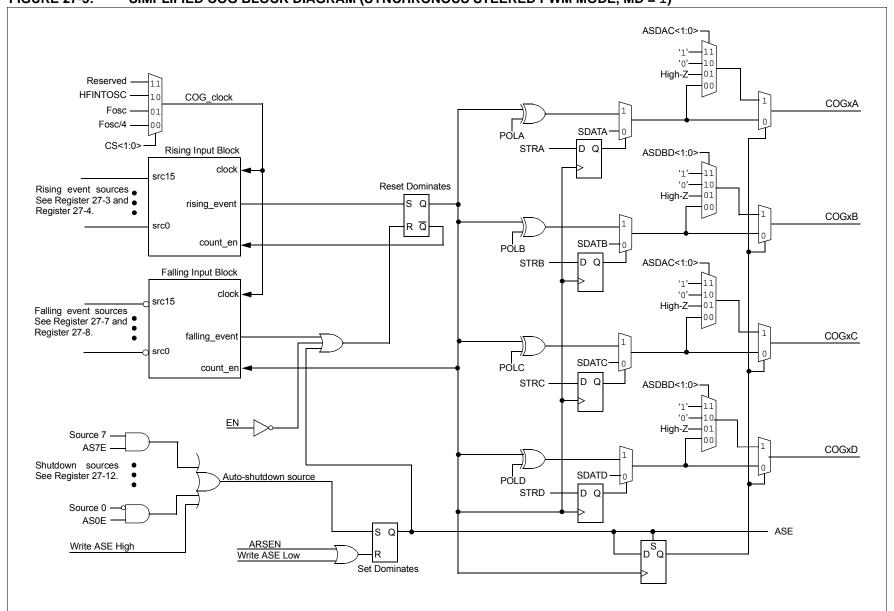

# 27.3.3 HALF-BRIDGE MODE

In Half-Bridge mode, the COG generates a two output complementary PWM waveform from rising and falling event sources. In the simplest configuration, the rising and falling event sources are the same signal, which is a PWM signal with the desired period and duty cycle. The COG converts this single PWM input into a dual complementary PWM output. The frequency and duty cycle of the dual PWM output match those of the single input PWM signal. The off-to-on transition of each output can be delayed from the on-to-off transition of the other output, thereby, creating a time immediately after the PWM transition where neither output is driven. This is referred to as dead-band time and is covered in **Section 27.7 "Dead-Band Control"**.

The half-bridge configuration is shown in Figure 27-5. A typical operating waveform, with dead band, generated from a single CCP1 input is shown in Figure 27-9.

The primary output is available on either, or both, COGxA and COGxC. The complementary output is available on either, or both, COGxB and COGxD.

Half-Bridge mode is selected by setting the MD<2:0> bits of the COGxCON0 register to '100'.

### 27.3.4 PUSH-PULL MODE

In Push-Pull mode, the COG generates a single PWM output that alternates between the two pairs of the COG outputs at every PWM period. COGxA has the same signal as COGxC. COGxB has the same signal as COGxD. The output drive activates with the rising input event and terminates with the falling event input. Each rising event starts a new period and causes the output to switch to the COG pair not used in the previous period.

The Push-Pull configuration is shown in Figure 27-6. A typical Push-Pull waveform generated from a single CCP1 input is shown in Figure 27-11.

Push-Pull mode is selected by setting the MD<2:0> bits of the COGxCON0 register to '101'.

# FIGURE 27-3: SIMPLIFIED COG BLOCK DIAGRAM (SYNCHRONOUS STEERED PWM MODE, MD = 1)

| R/W-0/0         | R/W-0/0                                                                                                                                                                                     | R/W-0/0           | R/W-1/1          | R/W-0/0              | R/W-1/1           | U-0               | U-0          |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|----------------------|-------------------|-------------------|--------------|--|--|--|--|

| ASE             | ARSEN                                                                                                                                                                                       | ASDBI             | D<1:0>           | ASDA                 | C<1:0>            | —                 | _            |  |  |  |  |

| bit 7           | ·                                                                                                                                                                                           | ·                 |                  | ÷                    |                   |                   | bit 0        |  |  |  |  |

|                 |                                                                                                                                                                                             |                   |                  |                      |                   |                   |              |  |  |  |  |

| Legend:         |                                                                                                                                                                                             |                   |                  |                      |                   |                   |              |  |  |  |  |

| R = Readable    | e bit                                                                                                                                                                                       | W = Writable      | bit              | U = Unimplem         | ented bit, read a | as '0'            |              |  |  |  |  |

| u = Bit is unc  | changed                                                                                                                                                                                     | x = Bit is unkr   | nown             | -n/n = Value at      | POR and BOR       | /Value at all oth | ner Resets   |  |  |  |  |

| '1' = Bit is se | t                                                                                                                                                                                           | '0' = Bit is clea | ared             | q = Value depe       | ends on conditio  | n                 |              |  |  |  |  |

|                 |                                                                                                                                                                                             |                   |                  |                      |                   |                   |              |  |  |  |  |

| bit 7           | ASE: Auto-S                                                                                                                                                                                 | hutdown Event     | Status bit       |                      |                   |                   |              |  |  |  |  |

|                 |                                                                                                                                                                                             | n the shutdown    |                  |                      |                   |                   |              |  |  |  |  |

|                 | 0 = COG is e                                                                                                                                                                                | either not in the | shutdown sta     | ate or will exit the | e shutdown state  | e on the next ris | sing event   |  |  |  |  |

| bit 6           | ARSEN: Auto                                                                                                                                                                                 | o-Restart Enabl   | e bit            |                      |                   |                   |              |  |  |  |  |

|                 |                                                                                                                                                                                             | tart is enabled   |                  |                      |                   |                   |              |  |  |  |  |

|                 | 0 = Auto-res                                                                                                                                                                                | tart is disabled  |                  |                      |                   |                   |              |  |  |  |  |

| bit 5-4         | ASDBD<1:0>: COGxB and COGxD Auto-shutdown Override Level Select bits                                                                                                                        |                   |                  |                      |                   |                   |              |  |  |  |  |

|                 | 11 = A logic '1' is placed on COGxB and COGxD when shutdown is active                                                                                                                       |                   |                  |                      |                   |                   |              |  |  |  |  |

|                 | 10 = A logic '0' is placed on COGxB and COGxD when shutdown is active                                                                                                                       |                   |                  |                      |                   |                   |              |  |  |  |  |

|                 | <ul> <li>01 = COGxB and COGxD are tri-stated when shutdown is active</li> <li>00 = The inactive state of the pin, including polarity, is placed on COGxB and COGxD when shutdowr</li> </ul> |                   |                  |                      |                   |                   |              |  |  |  |  |

|                 | is activ                                                                                                                                                                                    |                   | ie pin, includi  | ng polanty, is pla   |                   |                   | nen shuluowi |  |  |  |  |

| bit 3-2         | ASDAC<1:0:                                                                                                                                                                                  | -: COGxA and      | COGxC Auto       | -shutdown Overi      | ide Level Select  | t bits            |              |  |  |  |  |

|                 | 11 = A logic                                                                                                                                                                                | '1' is placed on  | COGxA and        | COGxC when s         | hutdown is activ  | 'e                |              |  |  |  |  |

|                 |                                                                                                                                                                                             |                   |                  | COGxC when s         |                   |                   |              |  |  |  |  |

|                 |                                                                                                                                                                                             |                   |                  | vhen shutdown i      |                   |                   |              |  |  |  |  |

|                 | 00 = The ina<br>is active                                                                                                                                                                   |                   | ie pin, includir | ng polarity, is pla  | ced on COGxA      | and COGxC wl      | hen shutdowr |  |  |  |  |

| bit 1-0         | Unimplemer                                                                                                                                                                                  | ted: Read as '    | 0'               |                      |                   |                   |              |  |  |  |  |

|                 |                                                                                                                                                                                             |                   |                  |                      |                   |                   |              |  |  |  |  |

#### REGISTER 27-11: COGxASD0: COG AUTO-SHUTDOWN CONTROL REGISTER 0

# 28.6 Register Definitions: CLC Control

Long bit name prefixes for the CLC peripherals are shown in Table 28-3. Refer to **Section 1.1** "**Register and Bit naming conventions**" for more information **TABLE 28-3:**

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| CLC1       | LC1             |

| CLC2       | LC2             |

| CLC3       | LC3             |

| CLC4       | LC4             |

### REGISTER 28-1: CLCxCON: CONFIGURABLE LOGIC CELL CONTROL REGISTER

| R/W-0/0 | U-0 | R-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|---------|-----|-------|---------|---------|---------|-----------|---------|

| EN      | —   | OUT   | INTP    | INTN    |         | MODE<2:0> |         |

| bit 7   |     |       |         |         |         |           | bit 0   |

| Legend:                                                           |                                                                                                                      |                                                                        |                                                       |  |  |  |  |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| R = Readable bit                                                  |                                                                                                                      | W = Writable bit                                                       | U = Unimplemented bit, read as '0'                    |  |  |  |  |

| u = Bit is unchanged                                              |                                                                                                                      | x = Bit is unknown                                                     | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |

| '1' = Bit is set                                                  |                                                                                                                      | '0' = Bit is cleared                                                   |                                                       |  |  |  |  |

|                                                                   |                                                                                                                      |                                                                        |                                                       |  |  |  |  |

| bit 7                                                             |                                                                                                                      | rable Logic Cell Enable bi                                             |                                                       |  |  |  |  |

|                                                                   | 0                                                                                                                    | rable logic cell is enabled                                            | 5 1 5                                                 |  |  |  |  |

| 0 = Configurable logic cell is disabled and has logic zero output |                                                                                                                      |                                                                        |                                                       |  |  |  |  |

| bit 6                                                             | -                                                                                                                    | nted: Read as '0'                                                      |                                                       |  |  |  |  |

| bit 5                                                             | OUT: Config                                                                                                          |                                                                        |                                                       |  |  |  |  |

|                                                                   | Read-only: I                                                                                                         | ogic cell output data, after                                           | POL; sampled from lcx_out wire.                       |  |  |  |  |

| bit 4                                                             | INTP: Configurable Logic Cell Positive Edge Going Interrupt Enable bit                                               |                                                                        |                                                       |  |  |  |  |

|                                                                   | <ul> <li>1 = CLCxIF will be set when a rising edge occurs on lcx_out</li> <li>0 = CLCxIF will not be set</li> </ul>  |                                                                        |                                                       |  |  |  |  |

| bit 3                                                             | INTN: Config                                                                                                         | INTN: Configurable Logic Cell Negative Edge Going Interrupt Enable bit |                                                       |  |  |  |  |

|                                                                   | <ul> <li>1 = CLCxIF will be set when a falling edge occurs on lcx_out</li> <li>0 = CLCxIF will not be set</li> </ul> |                                                                        |                                                       |  |  |  |  |

| bit 2-0                                                           | it 2-0 MODE<2:0>: Configurable Logic Cell Functional Mode bits                                                       |                                                                        |                                                       |  |  |  |  |

|                                                                   | 111 = Cell is 1-input transparent latch with S and R                                                                 |                                                                        |                                                       |  |  |  |  |

|                                                                   | 110 = Cell is J-K flip-flop with R                                                                                   |                                                                        |                                                       |  |  |  |  |

|                                                                   | 101 = Cell is 2-input D flip-flop with R                                                                             |                                                                        |                                                       |  |  |  |  |

|                                                                   | 100 = Cell is 1-input D flip-flop with S and R<br>011 = Cell is S-R latch                                            |                                                                        |                                                       |  |  |  |  |

|                                                                   |                                                                                                                      | s S-R latch<br>s 4-input AND                                           |                                                       |  |  |  |  |

|                                                                   | 010 = Cell i                                                                                                         | •                                                                      |                                                       |  |  |  |  |

|                                                                   |                                                                                                                      | 000 = Cell is AND-OR                                                   |                                                       |  |  |  |  |

| Name      | Bit7   | Bit6   | Bit5           | Bit4                    | Blt3    | Bit2    | Bit1    | Bit0     | Register<br>on Page |

|-----------|--------|--------|----------------|-------------------------|---------|---------|---------|----------|---------------------|

| ANSELA    | _      | _      | ANSA5          | ANSA4                   | ANSA3   | ANSA2   | ANSA1   | ANSA0    | 177                 |

| ANSELB    | _      | _      | ANSB5          | ANSB4                   | ANSB3   | ANSB2   | ANSB1   | ANSB0    | 182                 |

| ANSELC    | ANSC7  | ANSC6  | ANSC5          | ANSC4                   | ANSC3   | ANSC2   | —       | —        | 187                 |

| CLCxCON   | EN     | _      | OUT            | OUT INTP INTN MODE<2:0> |         |         |         |          | 397                 |

| CLCDATA   | _      | _      | _              | -                       | MLC4OUT | MLC3OUT | MLC2OUT | MLC1OUT  | 404                 |

| CLCxGLS0  | G1D4T  | G1D4N  | G1D3T          | G1D3N                   | G1D2T   | G1D2N   | G1D1T   | G1D1N    | 400                 |

| CLCxGLS1  | G2D4T  | G2D4N  | G2D3T          | G2D3N                   | G2D2T   | G2D2N   | G2D1T   | G2D1N    | 401                 |

| CLCxGLS2  | G3D4T  | G3D4N  | G3D3T          | G3D3N                   | G3D2T   | G3D2N   | G3D1T   | G3D1N    | 402                 |

| CLCxGLS3  | G4D4T  | G4D4N  | G4D3T          | G4D3N                   | G4D2T   | G4D2N   | G4D1T   | G4D1N    | 403                 |

| CLCxPOL   | POL    | _      | _              | _                       | G4POL   | G3POL   | G2POL   | G1POL    | 398                 |

| CLCxSEL0  | _      | —      |                | D1S<5:0>                |         |         |         |          | 399                 |

| CLCxSEL1  | —      | —      |                | D2S<5:0>                |         |         |         |          | 399                 |

| CLCxSEL2  |        |        |                | D3S<5:0>                |         |         |         |          | 399                 |

| CLCxSEL3  | _      | —      |                | D4S<5:0>                |         |         |         |          | 400                 |

| CLCINxPPS | -      | —      | CLCINxPPS<5:0> |                         |         |         |         | 205, 207 |                     |

| INTCON    | GIE    | PEIE   | TMR0IE         | INTE                    | IOCIE   | TMR0IF  | INTF    | IOCIF    | 132                 |

| PIE3      | _      | —      | COG2IE         | ZCDIE                   | CLC4IE  | CLC3IE  | CLC2IE  | CLC1IE   | 135                 |

| PIR3      | —      | —      | COG2IF         | ZCDIF                   | CLC4IF  | CLC3IF  | CLC2IF  | CLC1IF   | 141                 |

| RxyPPS    | _      | —      | RxyPPS<5:0>    |                         |         |         |         | 205      |                     |

| TRISA     | TRISA7 | TRISA6 | TRISA5         | TRISA4                  | TRISA3  | TRISA2  | TRISA1  | TRISA0   | 176                 |

| TRISB     | TRISB7 | TRISB6 | TRISB5         | TRISB4                  | TRISB3  | TRISB2  | TRISB1  | TRISB0   | 181                 |

| TRISC     | TRISC7 | TRISC6 | TRISC5         | TRISC4                  | TRISC3  | TRISC2  | TRISC1  | TRISC0   | 186                 |

Legend: — = unimplemented read as '0'. Shaded cells are not used for CLC module.

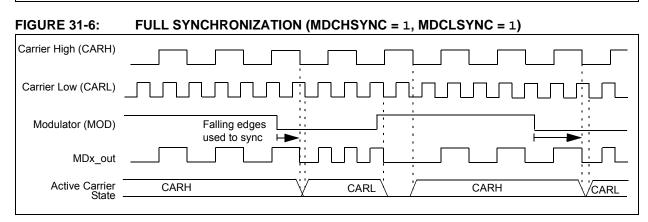

| FIGURE 31-5:              | CARRIER LOW SYNCHRONIZATION (MDCHSYNC = 0, MDCLSYNC = 1) |

|---------------------------|----------------------------------------------------------|

| Carrier High (CARH)       |                                                          |

| Carrier Low (CARL)        |                                                          |

| Modulator (MOD)           |                                                          |

| MDx_out                   |                                                          |

| Active Carrier<br>State - |                                                          |

# 31.5 Input and Output Through Pins

The modulation and carrier sources may be selected to come from any device pin with the PPS control logic. Selecting a pin requires two settings: The source selection determines that the PPS will be used and the PPS control selects the desired pin. Source and PPS registers are identified in Table 31-2. PPS register pin selections are shown in Register 12-1 and Register 12-2.

TABLE 31-2:

| Source       | Source<br>Register | PPS Register |  |

|--------------|--------------------|--------------|--|

| Modulation   | MDxSRC             | MDxMODPPS    |  |

| Carrier High | MDxCARH            | MDxCHPPS     |  |

| Carrier Low  | MDxCARL            | MDxCLPPS     |  |

Any device pin can be selected as the modulation output with the individual pin PPS controls. See Register 12-2 for the pin output selections.

### 31.6 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high source is enabled by setting the CHPOL bit of the MDxCON1 register. Inverting the signal for the carrier low source is enabled by setting the CLPOL bit of the MDxCON1 register.

### 31.7 Programmable Modulator Data

The BIT bit of the MDxCON0 register can be selected as the source for the modulator signal. When the BIT source is selected then software generates the modulation signal by setting and clearing the BIT bit at the respective desired modulation high and low times.

### 31.8 Modulated Output Polarity

The modulated output signal provided on the MDxOUT pin can also be inverted. Inverting the modulated output signal is enabled by setting the OPOL bit of the MDxCON0 register.

### 31.9 Operation in Sleep Mode

The DSM module is not affected by Sleep mode. The DSM will operate during Sleep provided that the Carrier and Modulator input sources are also active during Sleep.

### 31.10 Effects of a Reset

Upon any device Reset, the data signal modulator module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

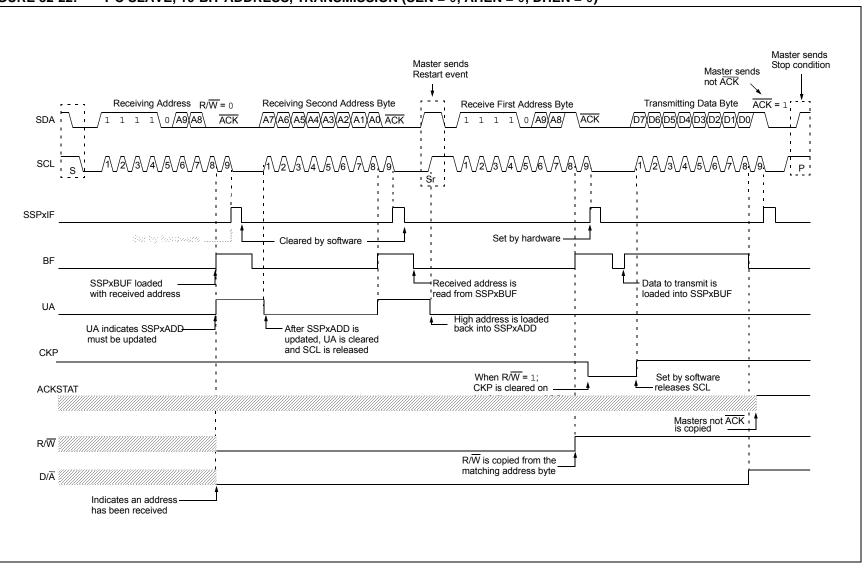

### FIGURE 32-22: $I^{2}C$ SLAVE, 10-BIT ADDRESS, TRANSMISSION (SEN = 0, AHEN = 0, DHEN = 0)

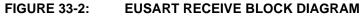

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXxSTA)

- Receive Status and Control (RCxSTA)

- Baud Rate Control (BAUDxCON)

These registers are detailed in Register 33-1, Register 33-2 and Register 33-3, respectively.

The RX and CK input pins are selected with the RXPPS and CKPPS registers, respectively. TX, CK, and DT output pins are selected with each pin's RxyPPS register. Since the RX input is coupled with the DT output in Synchronous mode, it is the user's responsibility to select the same pin for both of these functions when operating in Synchronous mode. The EUSART control logic will control the data direction drivers automatically.

| SWAPF            | Swap Nibbles in f                                                                                                                                                                  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] SWAPF f,d                                                                                                                                                                |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                            |  |  |  |

| Status Affected: | None                                                                                                                                                                               |  |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is '0',<br>the result is placed in the W register. If<br>'d' is '1', the result is placed in register<br>'f'. |  |  |  |

| XORLW            | Exclusive OR literal with W                                                                                         |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                            |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                   |  |  |  |  |

| Description:     | The contents of the W register are<br>XOR'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |

| TRIS             | Load TRIS Register with W                                                                                                                            |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] TRIS f                                                                                                                                       |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                    |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |  |  |  |

| Status Affected: | None                                                                                                                                                 |  |  |  |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |

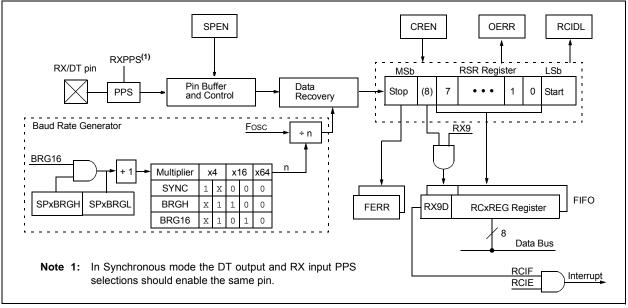

# 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                                  | MILLIMETERS     |      |          |      |  |

|----------------------------------|-----------------|------|----------|------|--|

| Dimension                        | MIN             | NOM  | MAX      |      |  |

| Contact Pitch                    | Contact Pitch E |      | 0.65 BSC |      |  |

| Optional Center Pad Width        | X2              |      |          | 6.60 |  |

| Optional Center Pad Length       | Y2              |      |          | 6.60 |  |

| Contact Pad Spacing              | C1              |      | 8.00     |      |  |

| Contact Pad Spacing              | C2              |      | 8.00     |      |  |

| Contact Pad Width (X44)          | X1              |      |          | 0.35 |  |

| Contact Pad Length (X44)         | Y1              |      |          | 0.85 |  |

| Contact Pad to Contact Pad (X40) | G1              | 0.30 |          |      |  |

| Contact Pad to Center Pad (X44)  | G2              | 0.28 |          |      |  |

| Thermal Via Diameter             | V               |      | 0.33     |      |  |

| Thermal Via Pitch                | EV              |      | 1.20     |      |  |

#### Notes:

- 1. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing No. C04-2103C