Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b; D/A 3x5b, 3x10b                                                 |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-UQFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1778t-i-mx |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

The PIC16(L)F1777/8/9 are described within this data sheet. See Table 2 for available package configurations.

Figure 1-1 shows a block diagram of the PIC16(L)F1777/8/9 devices. Table 1-2 shows the pinout descriptions.

Refer to Table 1-1 for peripherals available per device.

## TABLE 1-1:DEVICE PERIPHERAL<br/>SUMMARY

| Peripheral         group         group |                                          |       |               |                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------|---------------|-----------------|

| Fixed Voltage Reference (FVR)         •         •           Zero-Cross Detection (ZCD)         •         •           Temperature Indicator         •         •           Complementary Output Generator (COG)         •         •           COG2         •         •           COG3         •         •           Programmable Ramp Generator (PRG)         •         •           PRG1         •         •           PRG2         •         •           PRG3         •         •           PRG3         •         •           PRG2         •         •           10-bit Digital-to-Analog Converter (DAC)         •         •           DAC1         •         •           DAC2         •         •           DAC3         •         •           DAC4         •         •           DAC3         •         •           DAC3         •         •           DAC3         •         • <td>Peripheral</td> <td></td> <td>PIC16(L)F1778</td> <td>PIC16(L)F1777/9</td>                                                                                                                                                                 | Peripheral                               |       | PIC16(L)F1778 | PIC16(L)F1777/9 |

| Zero-Cross Detection (ZCD)         •         •           Temperature Indicator         •         •         •           Complementary Output Generator (COG)         •         •         •           COG1         •         •         •         •           COG2         •         •         •         •         •           COG3         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •                                                                                                                                                                         | Analog-to-Digital Converter (ADC)        |       | •             | ٠               |

| Temperature Indicator         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •                                                                                                                                                              | Fixed Voltage Reference (FVR)            |       | •             | •               |

| Complementary Output Generator (COG)         COG1         •           COG2         •         •           COG2         •         •           COG3         •         •           COG3         •         •           COG4         •         •           Programmable Ramp Generator (PRG)         •         •           PRG1         •         •           PRG2         •         •           PRG3         •         •           PRG3         •         •           PRG4         •         •           10-bit Digital-to-Analog Converter (DAC)         •         •           DAC1         •         •           DAC2         •         •           DAC3         •         •           DAC4         •         •           DAC3         •         •           Capture/Compare/PWM (CCP/EC                                                                                                                                                                                                                                                                      | Zero-Cross Detection (ZCD)               |       | •             | •               |

| COG1         •           COG2         •           COG3         •           COG3         •           COG3         •           COG3         •           COG4         •           Programmable Ramp Generator (PRG)         •           PRG1         •           PRG2         •           PRG3         •           PRG3         •           PRG4         •           10-bit Digital-to-Analog Converter (DAC)         •           DAC1         •           DAC2         •           DAC5         •           DAC6         •           5-bit Digital-to-Analog Converter (DAC)         •           DAC3         •           DAC4         •           DAC3         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •           CCP2         •           CCP8         •                                                                                                                                                                                                                                                                                                                  | Temperature Indicator                    |       | •             | ٠               |

| COG2         •         •           COG3         •         •           COG4         •         •           Programmable Ramp Generator (PRG)         •         •           PRG1         •         •           PRG2         •         •           PRG3         •         •           PRG3         •         •           PRG4         •         •           10-bit Digital-to-Analog Converter (DAC)         •         •           DAC1         •         •           DAC2         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           DAC3         •         •           DAC6         •         •           DAC4         •         •           DAC3         •         •           DAC4         •         •           DAC3         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •           CCP2         •         •         •     <                                                                                                                                                                                                                                                          | Complementary Output Generator (COG)     |       |               |                 |

| COG3         •           Programmable Ramp Generator (PRG)         •           PRG1         •           PRG2         •           PRG3         •           PRG3         •           PRG3         •           PRG4         •           10-bit Digital-to-Analog Converter (DAC)         •           DAC1         •           DAC2         •           DAC5         •           DAC6         •           5-bit Digital-to-Analog Converter (DAC)         •           DAC3         •           DAC4         •           DAC3         •           DAC4         •           DAC3         •           DAC4         •           DAC3         •           DAC4         •           DAC3         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •           CCP2         •           CCP7         •           CCP8         •                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          | COG1  | •             | ٠               |

| COG4         •           Programmable Ramp Generator (PRG)         PRG1         •           PRG2         •         •           PRG3         •         •           PRG3         •         •           PRG3         •         •           PRG4         •         •           10-bit Digital-to-Analog Converter (DAC)         •         •           DAC1         •         •           DAC2         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP2         •         •           CCP2         •         •           CCP2         •         •           CCP7         •         •           CCP8         •         •                                                                                                                                                                                                                                                                                                                     |                                          | COG2  | •             | ٠               |

| Programmable Ramp Generator (PRG)         PRG1         •           PRG2         •         •           PRG2         •         •           PRG3         •         •           PRG3         •         •           PRG4         •         •           10-bit Digital-to-Analog Converter (DAC)         •         •           DAC1         •         •           DAC2         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •           CCP2         •         •           CCP1         •         •           CCP2         •         •           CCP8         •         •                                                                                                                                                                                                                                                                                                                                              |                                          | COG3  | •             | ٠               |

| PRG1         •           PRG2         •           PRG3         •           PRG3         •           PRG4         •           10-bit Digital-to-Analog Converter (DAC)         DAC1         •           DAC2         •         •           DAC2         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           DAC6         •         •           DAC3         •         •           DAC4         •         •           DAC7         •         •           DAC3         •         •           DAC4         •         •           DAC3         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •         •           CCP2         •         • </td <td></td> <td>COG4</td> <td></td> <td>•</td>                                                                                                                                                                                                                                        |                                          | COG4  |               | •               |

| PRG1         •           PRG2         •           PRG3         •           PRG3         •           PRG4         •           10-bit Digital-to-Analog Converter (DAC)         DAC1         •           DAC2         •         •           DAC2         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           DAC6         •         •           DAC3         •         •           DAC4         •         •           DAC7         •         •           DAC3         •         •           DAC4         •         •           DAC3         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •         •           CCP2         •         • </td <td>Programmable Ramp Generator (PRG)</td> <td></td> <td></td> <td></td>                                                                                                                                                                                                            | Programmable Ramp Generator (PRG)        |       |               |                 |

| PRG3         •           PRG4         •           10-bit Digital-to-Analog Converter (DAC)         DAC1         •           DAC2         •         •           DAC2         •         •           DAC2         •         •           DAC2         •         •           DAC3         •         •           DAC4         •         •           DAC3         •         •           DAC4         •         •           DAC4         •         •           DAC3         •         •           DAC4         •         •           DAC3         •         •           DAC4         •         •           DAC3         •         •           DAC4         •         •           DAC4         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •         •           CCP2         •         •           CCP8         •         •                                                                                                                                                                                                                                                                                                                                                                     |                                          | PRG1  | •             | •               |

| PRG4         •           10-bit Digital-to-Analog Converter (DAC)         DAC1         •           DAC2         •         •           DAC2         •         •           DAC3         •         •           DAC4         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           DAC3         •         •           DAC4         •         •           DAC7         •         •           DAC7         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP2         •         •           CCP2         •         •           CCP2         •         •           CCP8         •         •           Comparators         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          | PRG2  | •             | •               |

| 10-bit Digital-to-Analog Converter (DAC)         DAC1         •           DAC2         •         •           DAC2         •         •           DAC5         •         •           DAC6         •         •           5-bit Digital-to-Analog Converter (DAC)         •         •           DAC3         •         •           DAC3         •         •           DAC4         •         •           DAC7         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •           CCP2         •         •           CCP7         •         •           CCP8         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                          | PRG3  | •             | •               |

| DAC1         •           DAC2         •           DAC5         •           DAC5         •           DAC6         •           5-bit Digital-to-Analog Converter (DAC)         DAC3           DAC3         •           DAC4         •           DAC7         •           DAC8         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •           CCP2         •           CCP7         •           CCP8         •           Comparators         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          |       |               | •               |

| DAC1         •           DAC2         •           DAC5         •           DAC5         •           DAC6         •           5-bit Digital-to-Analog Converter (DAC)         DAC3           DAC3         •           DAC4         •           DAC7         •           DAC8         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •           CCP2         •           CCP7         •           CCP8         •           Comparators         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10-bit Digital-to-Analog Converter (DAC) |       |               |                 |

| DAC5         •         •           DAC6         0         •         •           5-bit Digital-to-Analog Converter (DAC)         DAC3         •         •           DAC4         •         •         •           DAC4         •         •         •           DAC7         •         •         •           DAC8         •         •         •           DAC7         •         •         •           DAC8         •         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •         •           CCP1         •         •         •         •           CCP2         •         •         •         •           CCP7         •         •         •         •           CCP8         •         •         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                          | DAC1  | •             | •               |

| DAC6         •           5-bit Digital-to-Analog Converter (DAC)         DAC3         •           DAC3         •         •           DAC4         •         •           DAC7         •         •           DAC7         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •           CCP2         •         •           CCP7         •         •           CCP8         •         •           Comparators         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                          | DAC2  | •             | •               |

| DAC6         •           5-bit Digital-to-Analog Converter (DAC)         DAC3         •           DAC3         •         •           DAC4         •         •           DAC7         •         •           DAC7         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •           CCP2         •         •           CCP7         •         •           CCP8         •         •           Comparators         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                          | DAC5  | •             | •               |

| DAC3         •           DAC4         •           DAC7         •           DAC7         •           DAC8         •           DAC8         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •           CCP2         •           CCP7         •           CCP8         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          | DAC6  |               | •               |

| DAC3         •           DAC4         •           DAC7         •           DAC7         •           DAC8         •           DAC8         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •           CCP2         •           CCP7         •           CCP8         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-bit Digital-to-Analog Converter (DAC)  |       |               |                 |

| DAC7         •         •           DAC8         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •           CCP1         •         •           CCP2         •         •           CCP7         •         •           CCP8         •         •           Comparators         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          | DAC3  | •             | •               |

| DAC7         •         •           DAC8         •         •         •           Capture/Compare/PWM (CCP/ECCP) Modules         •         •         •           CCP1         •         •         •           CCP2         •         •         •           CCP7         •         •         •           CCP8         •         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                          |       | •             | •               |

| DAC8         •           Capture/Compare/PWM (CCP/ECCP) Modules         •           CCP1         •         •           CCP2         •         •           CCP7         •         •           CCP8         •         •           Comparators         •         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          |       | •             | •               |

| Capture/Compare/PWM (CCP/ECCP) Modules         CCP1         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •                                                                                                                                                    |                                          | DAC8  |               | •               |

| CCP1         •           CCP2         •           CCP7         •           CCP8         •           Comparators         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Capture/Compare/PWM (CCP/ECCP) Mod       | dules |               |                 |

| CCP2     •       CCP7     •       CCP8     •       CCP8     •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          | 1     | •             | •               |

| CCP8 • Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          | CCP2  | •             | •               |

| Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                          | CCP7  | •             | •               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          | CCP8  |               | •               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Comparators                              |       |               | . <u> </u>      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          | C1    | •             | ٠               |

| C2 • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          | C2    | •             | ٠               |

| C3 • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          | C3    | •             | ٠               |

| C4 • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          | C4    | •             | ٠               |

| C5 • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          | C5    | •             | ٠               |

| C6 • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          |       | •             | ٠               |

| C7 •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          |       |               | ٠               |

| C8 •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          | C8    |               | ٠               |

#### TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| SUMMARY                                                               | i        |               |                 |

|-----------------------------------------------------------------------|----------|---------------|-----------------|

| Peripheral                                                            |          | PIC16(L)F1778 | PIC16(L)F1777/9 |

| Configurable Logic Cell (CLC)                                         |          |               |                 |

|                                                                       | CLC1     | •             | ٠               |

|                                                                       | CLC2     | ٠             | ٠               |

|                                                                       | CLC3     | ٠             | ٠               |

|                                                                       | CLC4     | ٠             | ٠               |

| Data Signal Modulator (DSM)                                           |          |               |                 |

|                                                                       | DSM1     | •             | ٠               |

|                                                                       | DSM2     | •             | ٠               |

|                                                                       | DSM3     | ٠             | ٠               |

|                                                                       | DSM4     |               | ٠               |

| Enhanced Universal Synchronous/Async<br>Receiver/Transmitter (EUSART) | chronous |               |                 |

|                                                                       | EUSART   | ٠             | ٠               |

| Master Synchronous Serial Ports                                       |          |               |                 |

|                                                                       | MSSP     | •             | ٠               |

| Op Amps                                                               |          |               |                 |

|                                                                       | OPA1     | ٠             | ٠               |

|                                                                       | OPA2     | •             | •               |

|                                                                       | OPA3     | •             | ٠               |

|                                                                       | OPA4     |               | ٠               |

| 10-bit Pulse-Width Modulator (PWM)                                    | •        |               |                 |

|                                                                       | PWM3     | •             | ٠               |

|                                                                       | PWM4     | ٠             | •               |

|                                                                       | PWM9     | ٠             | ٠               |

|                                                                       | PWM10    |               | ٠               |

| 16-bit Pulse-Width Modulator (PWM)                                    |          |               |                 |

|                                                                       | PWM5     | ٠             | ٠               |

|                                                                       | PWM6     | ٠             | ٠               |

|                                                                       | PWM11    | ٠             | ٠               |

|                                                                       | PWM12    |               | ٠               |

| 8-bit Timers                                                          |          |               |                 |

|                                                                       | Timer0   | ٠             | ٠               |

|                                                                       | Timer2   | •             | ٠               |

|                                                                       | Timer4   | ٠             | ٠               |

|                                                                       | Timer6   | •             | ٠               |

|                                                                       | Timer8   | ٠             | ٠               |

| 16-bit Timers                                                         |          |               |                 |

|                                                                       | Timer1   | ٠             | ٠               |

|                                                                       | Timer3   | ٠             | ٠               |

|                                                                       | Timer5   | ٠             | ٠               |

| FIGURE 5-7:               | INTERNAL OSCILLATOR SWITCH TIMING                      |

|---------------------------|--------------------------------------------------------|

|                           |                                                        |

| MENEROSC/                 | LFINYOSC (FSCM and WOY disabled)                       |

| HFINTOSC/<br>MEINTOSC     | Citati vas Time Skovite Sync Risming                   |

| LFINTOSC                  |                                                        |

| IRCF <3:0>                | $\neq 0$ $X = 0$                                       |

| System Clock              |                                                        |

|                           |                                                        |

| 99998763867<br>8859876386 | LEWYCOCC (EMMOR FACIAL OF WOY specified)               |

| HFINTOSC/<br>MEENTOSC     |                                                        |

| LFINTOSC                  |                                                        |

| IRCF <3:0>                | $\neq 0$ $\chi = 0$                                    |

| System Clock              |                                                        |

|                           |                                                        |

|                           |                                                        |

| LEBELOSO                  | UPPER STATE OF UPPER STATE OF UPPER STATE STATE STATES |

| xx 224 (xxxxX)            | Barnand Bina (Broycle Synce) Recognize                 |

| HEINTOSO<br>MEINTOSO      |                                                        |

| \$\$\C\$\K\$\C\$\         | × 0 X V 0                                              |

| System Crook              |                                                        |

|                           |                                                        |

|                           |                                                        |

## 8.3 Register Definitions: Voltage Regulator Control

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-1/1  |

|-------|-----|-----|-----|-----|-----|---------|----------|

| —     | —   | —   | —   | —   | —   | VREGPM  | Reserved |

| bit 7 |     |     |     |     |     |         | bit 0    |

|       |     |     |     |     |     |         |          |

## REGISTER 8-1: VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | <ul> <li>VREGPM: Voltage Regulator Power Mode Selection bit</li> <li>1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup><br/>Draws lowest current in Sleep, slower wake-up</li> <li>0 = Normal Power mode enabled in Sleep<sup>(2)</sup><br/>Draws higher current in Sleep, faster wake-up</li> </ul> |

| bit 0   | Reserved: Read as '1'. Maintain this bit set.                                                                                                                                                                                                                                                             |

#### Note 1: PIC16F1777/8/9 only.

2: See Section 36.0 "Electrical Specifications".

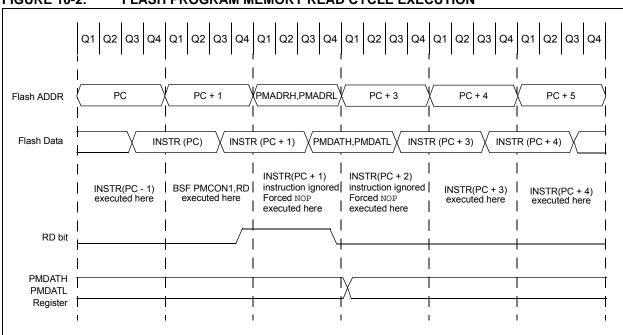

#### **FIGURE 10-2:** FLASH PROGRAM MEMORY READ CYCLE EXECUTION

#### EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

\* This code block will read 1 word of program

- \* memory at the memory address:

- PROG\_ADDR\_HI : PROG\_ADDR\_LO

- \* data will be returned in the variables;

- \* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL<br>MOVLW<br>MOVWF<br>MOVLW | PMADRL<br>PROG_ADDR_LO<br>PMADRL<br>PROG_ADDR_HI | ; Select Bank for PMCON registers<br>;<br>; Store LSB of address<br>;                                        |

|------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| MOVWF                              | PMADRH                                           | ; Store MSB of address                                                                                       |

| BCF<br>BSF<br>NOP<br>NOP           | PMCON1,CFGS<br>PMCON1,RD                         | ; Do not select Configuration Space<br>; Initiate read<br>; Ignored (Figure 10-1)<br>; Ignored (Figure 10-1) |

| MOVF                               | PMDATL,W                                         | ; Get LSB of word                                                                                            |

| MOVWF                              | PROG_DATA_LO                                     | ; Store in user location                                                                                     |

| MOVF                               | PMDATH,W                                         | ; Get MSB of word                                                                                            |

| MOVWF                              | PROG_DATA_HI                                     | ; Store in user location                                                                                     |

|                                    |                                                  |                                                                                                              |

| LATD7 LATD6 LATD5 LATD4 LATD3 LATD2 LATE |          |

|------------------------------------------|----------|

|                                          | D1 LATD0 |

| bit 7                                    | bit 0    |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATD<7:0>: PORTD Output Latch Value bits

#### REGISTER 11-29: ANSELD: PORTD ANALOG SELECT REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3   | ANSD2   | ANSD1   | ANSD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ANSD<7:0>**: Analog Select between Analog or Digital Function on pins RD<7:0><sup>(1)</sup>

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

-n/n = Value at POR and BOR/Value at all other Resets

| Legend: |         |         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

| bit 7   |         |         |         |         |         |         | bit 0   |

| SLRD7   | SLRD6   | SLRD5   | SLRD4   | SLRD3   | SLRD2   | SLRD1   | SLRD0   |

| R/W-1/1 |

#### REGISTER 11-32: SLRCOND: PORTD SLEW RATE CONTROL REGISTER

bit 7-0 SLRD<7:0>: PORTD Slew Rate Enable bits For RD<7:0> pins 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

u = Bit is unchanged

'1' = Bit is set

#### REGISTER 11-33: INLVLD: PORTD INPUT LEVEL CONTROL REGISTER

x = Bit is unknown

'0' = Bit is cleared

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2 | INLVLD1 | INLVLD0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLD<7:0>: PORTD Input Level Select bits

For RD<7:0> pins

1 = Port pin digital input operates with ST thresholds

0 = Port pin digital input operates with TTL thresholds

### 11.10 Register Definitions: PORTE

#### REGISTER 11-34: PORTE: PORTE REGISTER

| U-0                                   | U-0        | U-0             | U-0  | R-x/u                                                 | R/W-x/u            | R/W-x/u            | R/W-x/u            |  |

|---------------------------------------|------------|-----------------|------|-------------------------------------------------------|--------------------|--------------------|--------------------|--|

| —                                     | _          | _               | —    | RE3                                                   | RE2 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE0 <sup>(1)</sup> |  |

| bit 7                                 |            |                 | •    |                                                       |                    |                    | bit 0              |  |

|                                       |            |                 |      |                                                       |                    |                    |                    |  |

| Legend:                               |            |                 |      |                                                       |                    |                    |                    |  |

| R = Readable                          | e bit      | W = Writable    | bit  | U = Unimpler                                          | mented bit, read   | as '0'             |                    |  |

| u = Bit is uncl                       | nanged     | x = Bit is unkr | nown | -n/n = Value at POR and BOR/Value at all other Resets |                    |                    |                    |  |

| '1' = Bit is set '0' = Bit is cleared |            |                 |      |                                                       |                    |                    |                    |  |

|                                       |            |                 |      |                                                       |                    |                    |                    |  |

| bit 7-4                               | Unimplemen | ted: Read as '  | o'   |                                                       |                    |                    |                    |  |

|                                       |            |                 |      |                                                       |                    |                    |                    |  |

| bit 3-0 | RE<3:0>: PORTE I/O Pin bits <sup>(1)</sup> |

|---------|--------------------------------------------|

|         | 1 = Port pin is > Vін                      |

|         | 0 = Port pin is < VIL                      |

**Note 1:** RE<2:0> are not implemented on the PIC16(L)F1778. Read as '0'. Writes to RE<2:0> are actually written to corresponding LATE register. Reads from PORTE register is the return of actual I/O pin values.

#### REGISTER 11-35: TRISE: PORTE TRI-STATE REGISTER

| U-0   | U-0 | U-0 | U-0 | U-1 <sup>(2)</sup> | R/W-1                 | R/W-1                 | R/W-1                 |

|-------|-----|-----|-----|--------------------|-----------------------|-----------------------|-----------------------|

| —     | —   | —   | —   | —                  | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> |

| bit 7 |     |     |     | •                  |                       |                       | bit 0                 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'                                |

|---------|-----------------------------------------------------------|

| bit 3   | Unimplemented: Read as '1'                                |

| bit 2-0 | TRISE<2:0>: RE<2:0> Tri-State Control bits <sup>(1)</sup> |

|         | 1 = PORTE pin configured as an input (tri-stated)         |

|         | 0 = PORTE pin configured as an output                     |

- **Note 1:** TRISE<2:0> are not implemented on the PIC16(L)F1778.

- 2: Unimplemented, read as '1'.

| Name                     | Bit 7 | Bit 6 | Bit 5         | Bit 4         | Bit 3 | Bit 2     | Bit 1 | Bit 0     | Register<br>on page |

|--------------------------|-------|-------|---------------|---------------|-------|-----------|-------|-----------|---------------------|

| PPSLOCK                  | _     | _     | _             |               | _     | —         | —     | PPSLOCKED | 206                 |

| INTPPS                   | _     | _     |               |               | INTF  | PS<5:0>   |       |           | 205                 |

| TOCKIPPS                 | _     | _     |               |               | TOCK  | PPS<5:0>  |       |           | 205                 |

| T1CKIPPS                 | _     | _     |               |               | T1CK  | PPS<5:0>  |       |           | 205                 |

| T1GPPS                   | _     | —     |               |               | T1GF  | PPS<5:0>  |       |           | 205                 |

| T3CKIPPS                 | —     | _     |               |               | T3CK  | PPS<5:0>  |       |           | 205                 |

| T3GPPS                   |       | _     |               |               | T3GF  | PS<5:0>   |       |           | 205                 |

| T5CKIPPS                 | _     | _     |               |               | T5CK  | PPS<5:0>  |       |           | 205                 |

| T5GPPS                   | _     | _     |               |               | T5GF  | PPS<5:0>  |       |           | 205                 |

| T2INPPS                  | _     | _     |               |               | T2IN  | PPS<5:0>  |       |           | 205                 |

| T4INPPS                  | _     | _     |               |               | T4IN  | PPS<5:0>  |       |           | 205                 |

| T6INPPS                  | _     | _     |               |               | T6INI | PPS<5:0>  |       |           | 205                 |

| T8INPPS                  | _     | _     |               |               | T8INI | PPS<5:0>  |       |           | 205                 |

| CCP1PPS                  | _     | —     |               |               | CCP1  | PPS<5:0>  |       |           | 205                 |

| CCP2PPS                  | —     | —     |               |               | CCP2  | PPS<5:0>  |       |           | 205                 |

| CCP7PPS                  | _     | —     |               |               | CCP7  | PPS<5:0>  |       |           | 205                 |

| CCP8PPS <sup>(1)</sup>   | _     | _     |               | CCP8PPS<5:0>  |       |           |       |           | 205                 |

| COGIN1PPS                | _     | _     |               | COG1PPS<5:0>  |       |           |       |           |                     |

| COG2INPPS                | _     | _     |               | COG2PPS<5:0>  |       |           |       |           |                     |

| COG3INPPS                | _     | _     |               | COG3PPS<5:0>  |       |           |       |           |                     |