Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 72MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB             |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT             |

| Number of I/O              | 51                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 96K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103rgt6jtr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 44. | EMS characteristics                                                      |

|-----------|--------------------------------------------------------------------------|

| Table 45. | EMI characteristics                                                      |

| Table 46. | ESD absolute maximum ratings                                             |

| Table 47. | Electrical sensitivities                                                 |

| Table 48. | I/O current injection susceptibility                                     |

| Table 49. | I/O static characteristics                                               |

| Table 50. | Output voltage characteristics                                           |

| Table 51. | I/O AC characteristics                                                   |

| Table 52. | NRST pin characteristics                                                 |

| Table 53. | TIMx characteristics                                                     |

| Table 54. | I <sup>2</sup> C characteristics                                         |

| Table 55. | SCL frequency (f <sub>PCLK1</sub> = 36 MHz.,V <sub>DD I2C</sub> = 3.3 V) |

| Table 56. | SPI characteristics                                                      |

| Table 57. | I <sup>2</sup> S characteristics                                         |

| Table 58. | SD / MMC characteristics                                                 |

| Table 59. | USB startup time                                                         |

| Table 60. | USB DC electrical characteristics                                        |

| Table 61. | USB: full-speed electrical characteristics                               |

| Table 62. | ADC characteristics                                                      |

| Table 63. | $R_{AIN}$ max for $f_{ADC}$ = 14 MHz                                     |

| Table 64. | ADC accuracy - limited test conditions                                   |

| Table 65. | ADC accuracy                                                             |

| Table 66. | DAC characteristics                                                      |

| Table 67. | TS characteristics                                                       |

| Table 68. | LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm,  |

|           | 0.8 mm pitch, package mechanical data                                    |

| Table 69. | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package              |

|           | mechanical data                                                          |

| Table 70. | LQPF100 – 14 x 14 mm 100-pin low-profile quad flat package               |

|           | mechanical data                                                          |

| Table 71. | LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data |

| Table 72. | Package thermal characteristics                                          |

| Table 73. | STM32F103xF and STM32F103xG ordering information scheme                  |

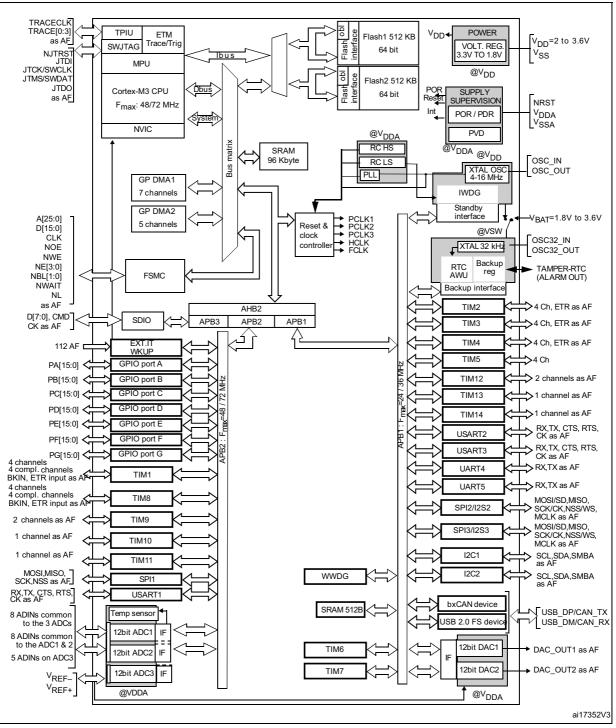

Figure 1. STM32F103xF and STM32F103xG performance line block diagram

T<sub>A</sub> = -40 °C to +85 °C (suffix 6, see *Table 73*) or -40 °C to +105 °C (suffix 7, see *Table 73*), junction temperature up to 105 °C or 125 °C, respectively.

2. AF = alternate function on I/O port pin.9

## 2.3.10 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-16 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example with failure of an indirectly used external oscillator).

Several prescalers allow the configuration of the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the high speed APB domains is 72 MHz. The maximum allowed frequency of the low speed APB domain is 36 MHz. See *Figure 2* for details on the clock tree.

## 2.3.11 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from user Flash: you have an option to boot from any of two memory banks. By default, boot from Flash memory bank 1 is selected. You can choose to boot from Flash memory bank 2 by setting a bit in the option bytes.

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1.

## 2.3.12 Power supply schemes

- V<sub>DD</sub> = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 2.0 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to VDDA is 2.4 V when the ADC or DAC is used). V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to Figure 10: Power supply scheme.

## 2.3.13 Power supply supervisor

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software. Refer to *Table 12: Embedded reset and power control block characteristics* for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

## 2.3.14 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop modes.

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode.

## 2.3.15 Low-power modes

The STM32F103xF and STM32F103xG performance line supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm or the USB wakeup.

• Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

## 2.3.16 DMA

The flexible 12-channel general-purpose DMAs (7 channels for DMA1 and 5 channels for DMA2) are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The two DMA controllers support circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

#### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

## 2.3.19 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support 7/10-bit addressing mode and 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

#### 2.3.20 Universal synchronous/asynchronous receiver transmitters (USARTs)

The STM32F103xF and STM32F103xG performance line embeds three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3) and two universal asynchronous receiver transmitters (UART4 and UART5).

These five interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability.

The USART1 interface is able to communicate at speeds of up to 4.5 Mbit/s. The other available interfaces communicate at up to 2.25 Mbit/s.

USART1, USART2 and USART3 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller except for UART5.

|      |        | I      | able 6. FSMC |               |             |                        |

|------|--------|--------|--------------|---------------|-------------|------------------------|

| Pins |        |        | NOR/PSRAM/   |               |             | LQFP100 <sup>(1)</sup> |

|      | CF     | CF/IDE | SRAM         | NOR/PSRAM Mux | NAND 16 bit |                        |

| PE2  | -      | -      | A23          | A23           | -           | Yes                    |

| PE3  | -      | -      | A19          | A19           | -           | Yes                    |

| PE4  | -      | -      | A20          | A20           | -           | Yes                    |

| PE5  | -      | -      | A21          | A21           | -           | Yes                    |

| PE6  | -      | -      | A22          | A22           | -           | Yes                    |

| PF0  | A0     | A0     | A0           | -             | -           | -                      |

| PF1  | A1     | A1     | A1           | -             | -           | -                      |

| PF2  | A2     | A2     | A2           | -             | -           | -                      |

| PF3  | A3     | -      | A3           | -             | -           | -                      |

| PF4  | A4     | -      | A4           | -             | -           | -                      |

| PF5  | A5     | -      | A5           | -             | -           | -                      |

| PF6  | NIORD  | NIORD  |              | -             | -           | -                      |

| PF7  | NREG   | NREG   |              | -             | -           | -                      |

| PF8  | NIOWR  | NIOWR  |              | -             | -           | -                      |

| PF9  | CD     | CD     |              | -             | -           | -                      |

| PF10 | INTR   | INTR   |              | -             | -           | -                      |

| PF11 | NIOS16 | NIOS16 |              | -             | -           | -                      |

| PF12 | A6     | -      | A6           | -             | -           | -                      |

| PF13 | A7     | -      | A7           | -             | -           | -                      |

| PF14 | A8     | -      | A8           | -             | -           | -                      |

| PF15 | A9     | -      | A9           | -             | -           | -                      |

| PG0  | A10    | -      | A10          | -             | -           | -                      |

| PG1  | -      | -      | A11          | -             | -           | -                      |

| PE7  | D4     | D4     | D4           | DA4           | D4          | Yes                    |

| PE8  | D5     | D5     | D5           | DA5           | D5          | Yes                    |

| PE9  | D6     | D6     | D6           | DA6           | D6          | Yes                    |

| PE10 | D7     | D7     | D7           | DA7           | D7          | Yes                    |

| PE11 | D8     | D8     | D8           | DA8           | D8          | Yes                    |

| PE12 | D9     | D9     | D9           | DA9           | D9          | Yes                    |

| PE13 | D10    | D10    | D10          | DA10          | D10         | Yes                    |

| PE14 | D11    | D11    | D11          | DA11          | D11         | Yes                    |

| PE15 | D12    | D12    | D12          | DA12          | D12         | Yes                    |

| PD8  | D13    | D13    | D13          | DA13          | D13         | Yes                    |

|      |        |        |              |               |             |                        |

## Table 6. FSMC pin definition

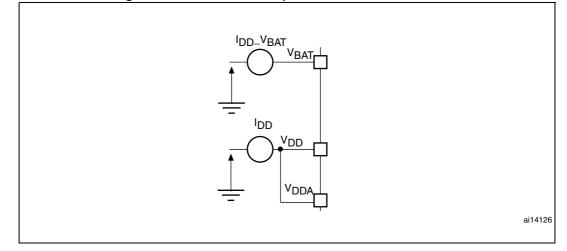

## 5.1.7 Current consumption measurement

#### Figure 11. Current consumption measurement scheme

## 5.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 11* are derived from tests performed under the ambient temperature condition summarized in *Table 10*.

| Symbol           | Parameter                      | Conditions | Min | Max | Unit  |

|------------------|--------------------------------|------------|-----|-----|-------|

|                  | V <sub>DD</sub> rise time rate | _          | 0   | ¥   | us/V  |

| <sup>I</sup> VDD | V <sub>DD</sub> fall time rate | -          | 20  | ¥   | μ5/ ν |

Table 11. Operating conditions at power-up / power-down

## 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 12* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| Symbol                               | Parameter                                        | Conditions                  | Min                | Тур  | Мах  | Unit |

|--------------------------------------|--------------------------------------------------|-----------------------------|--------------------|------|------|------|

|                                      |                                                  | PLS[2:0]=000 (rising edge)  | 2.1                | 2.18 | 2.26 | V    |

|                                      |                                                  | PLS[2:0]=000 (falling edge) | 2                  | 2.08 | 2.16 | V    |

|                                      |                                                  | PLS[2:0]=001 (rising edge)  | 2.19               | 2.28 | 2.37 | V    |

|                                      | Programmable voltage<br>detector level selection | PLS[2:0]=001 (falling edge) | 2.09               | 2.18 | 2.27 | V    |

|                                      |                                                  | PLS[2:0]=010 (rising edge)  | 2.28               | 2.38 | 2.48 | V    |

|                                      |                                                  | PLS[2:0]=010 (falling edge) | 2.18               | 2.28 | 2.38 | V    |

|                                      |                                                  | PLS[2:0]=011 (rising edge)  | 2.38               | 2.48 | 2.58 | V    |

| V                                    |                                                  | PLS[2:0]=011 (falling edge) | 2.28               | 2.38 | 2.48 | V    |

| V <sub>PVD</sub>                     |                                                  | PLS[2:0]=100 (rising edge)  | 2.47               | 2.58 | 2.69 | V    |

|                                      |                                                  | PLS[2:0]=100 (falling edge) | 2.37               | 2.48 | 2.59 | V    |

|                                      |                                                  | PLS[2:0]=101 (rising edge)  | 2.57               | 2.68 | 2.79 | V    |

|                                      |                                                  | PLS[2:0]=101 (falling edge) | 2.47               | 2.58 | 2.69 | V    |

|                                      |                                                  | PLS[2:0]=110 (rising edge)  | 2.66               | 2.78 | 2.9  | V    |

|                                      |                                                  | PLS[2:0]=110 (falling edge) | 2.56               | 2.68 | 2.8  | V    |

|                                      |                                                  | PLS[2:0]=111 (rising edge)  | 2.76               | 2.88 | 3    | V    |

|                                      |                                                  | PLS[2:0]=111 (falling edge) | 2.66               | 2.78 | 2.9  | V    |

| V <sub>PVDhyst</sub> <sup>(2)</sup>  | PVD hysteresis                                   | -                           | -                  | 100  | -    | mV   |

|                                      | Power on/power down                              | Falling edge                | 1.8 <sup>(1)</sup> | 1.88 | 1.96 | V    |

| V <sub>POR/PDR</sub>                 | reset threshold                                  | Rising edge                 | 1.84               | 1.92 | 2.0  | V    |

| V <sub>PDRhyst</sub> <sup>(2)</sup>  | PDR hysteresis                                   | -                           | -                  | 40   | -    | mV   |

| T <sub>RSTTEMPO</sub> <sup>(2)</sup> | Reset temporization                              | -                           | 1                  | 2.5  | 4.5  | mS   |

Table 12. Embedded reset and power control block characteristics

1. The product behavior is guaranteed by design down to the minimum  $V_{\text{POR/PDR}}$  value.

2. Guaranteed by design, not tested in production.

| Symbol | Parameter      | Conditions                                              |                     | Ма                     | ıx <sup>(1)</sup>       | Unit                |                     |                     |        |    |      |

|--------|----------------|---------------------------------------------------------|---------------------|------------------------|-------------------------|---------------------|---------------------|---------------------|--------|----|------|

| Symbol | Parameter      | Conditions                                              | f <sub>HCLK</sub>   | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Onit                |                     |                     |        |    |      |

|        |                |                                                         | 72 MHz              | 47.5                   | 48.5                    |                     |                     |                     |        |    |      |

|        |                |                                                         | 48 MHz              | 34                     | 35                      |                     |                     |                     |        |    |      |

|        |                | External clock <sup>(2)</sup> , all peripherals enabled | 36 MHz              | 27.5                   | 27.5                    |                     |                     |                     |        |    |      |

|        |                |                                                         | peripherals enabled | peripherals enabled    | peripherals enabled     | peripherals enabled | peripherals enabled | peripherals enabled | 24 MHz | 20 | 20.5 |

|        |                |                                                         | 16 MHz              | 15                     | 16                      |                     |                     |                     |        |    |      |

|        | Supply current | urrent                                                  | 8 MHz               | 9                      | 11                      | mA                  |                     |                     |        |    |      |

| IDD    | in Sleep mode  |                                                         | 72 MHz              | 9.5                    | 11.2                    | IIIA                |                     |                     |        |    |      |

|        |                |                                                         | 48 MHz              | 7.7                    | 9.5                     |                     |                     |                     |        |    |      |

|        |                | External clock <sup>(2)</sup> , all                     | 36 MHz              | 6.9                    | 8.5                     |                     |                     |                     |        |    |      |

|        |                | peripherals disabled                                    | 24 MHz              | 5.9                    | 7.8                     |                     |                     |                     |        |    |      |

|        |                |                                                         | 16 MHz              | 5.4                    | 7.2                     |                     |                     |                     |        |    |      |

|        |                |                                                         | 8 MHz               | 4.7                    | 6.4                     |                     |                     |                     |        |    |      |

# Table 16. Maximum current consumption in Sleep mode, code running from Flash or RAM

1. Guaranteed by characterization results, not tested in production at  $V_{DD}$  max,  $f_{HCLK}$  max with peripherals enabled.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

## 5.3.10 FSMC characteristics

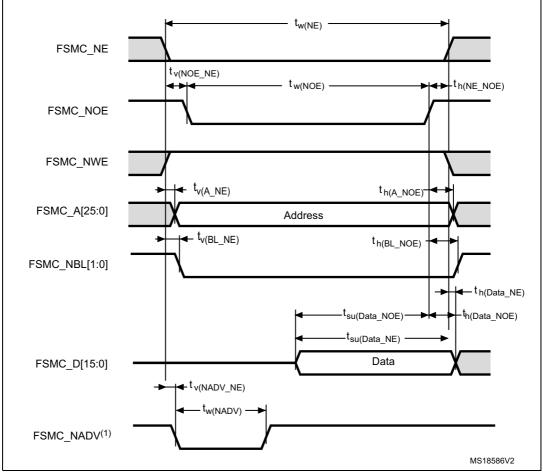

#### Asynchronous waveforms and timings

*Figure 22* through *Figure 25* represent asynchronous waveforms and *Table 31* through *Table 35* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- AddressSetupTime = 0

- AddressHoldTime = 1

- DataSetupTime = 1

Note: On all tables, the  $t_{HCLK}$  is the HCLK clock period.

#### Figure 22. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

FSMC\_BusTurnAroundDuration = 0.

Note:

DocID16554 Rev 4

| Symbol                    | Parameter                             | Min                     | Мах                   | Unit |

|---------------------------|---------------------------------------|-------------------------|-----------------------|------|

| t <sub>h(A_NWE)</sub>     | Address hold time after FSMC_NWE high | 4t <sub>HCLK</sub> – 2  | -                     | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid         | -                       | 0.5                   | ns   |

| t <sub>h(BL_NWE)</sub>    | FSMC_BL hold time after FSMC_NWE high | t <sub>HCLK</sub> – 1.5 | -                     | ns   |

| t <sub>v(Data_NADV)</sub> | FSMC_NADV high to Data valid          | -                       | t <sub>HCLK</sub> + 6 | ns   |

| t <sub>h(Data_NWE)</sub>  | Data hold time after FSMC_NWE high    | t <sub>HCLK</sub> – 0.5 | -                     | ns   |

Table 35. Asynchronous multiplexed PSRAM/NOR write timings<sup>(1)</sup>

1. C<sub>L</sub> = 15 pF.

#### Synchronous waveforms and timings

*Figure 26* through *Figure 29* represent synchronous waveforms and *Table 37* through *Table 39* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- BurstAccessMode = FSMC\_BurstAccessMode\_Enable;

- MemoryType = FSMC\_MemoryType\_CRAM;

- WriteBurst = FSMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F10xxx reference manual)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

1. C<sub>L</sub> = 15 pF.

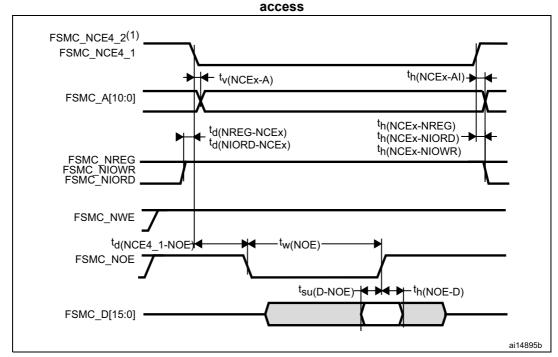

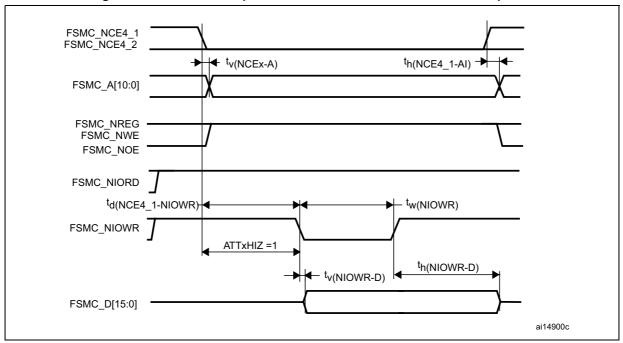

#### PC Card/CompactFlash controller waveforms and timings

*Figure 30* through *Figure 35* represent synchronous waveforms and *Table 42* provides the corresponding timings. The results shown in this table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x04;

- COM.FSMC\_WaitSetupTime = 0x07;

- COM.FSMC\_HoldSetupTime = 0x04;

- COM.FSMC\_HiZSetupTime = 0x00;

- ATT.FSMC\_SetupTime = 0x04;

- ATT.FSMC\_WaitSetupTime = 0x07;

- ATT.FSMC\_HoldSetupTime = 0x04;

- ATT.FSMC\_HiZSetupTime = 0x00;

- IO.FSMC\_SetupTime = 0x04;

- IO.FSMC WaitSetupTime = 0x07;

- IO.FSMC\_HoldSetupTime = 0x04;

- IO.FSMC\_HiZSetupTime = 0x00;

- TCLRSetupTime = 0;

- TARSetupTime = 0;

#### Figure 30. PC Card/CompactFlash controller waveforms for common memory read

#### 1. FSMC\_NCE4\_2 remains high (inactive during 8-bit access.

Figure 35. PC Card/CompactFlash controller waveforms for I/O space write access

# Table 40. Switching characteristics for PC Card/CF read and write cycles in attribute/common space

| Symbol                    | Parameter                                    | Min                       | Max                    | Unit |

|---------------------------|----------------------------------------------|---------------------------|------------------------|------|

| t <sub>v(NCEx-A)</sub>    | FSMC_NCEx low to FSMC_Ay valid               | -                         | 0                      |      |

| t <sub>h(NCEx-AI)</sub>   | FSMC_NCEx high to FSMC_Ax invalid            | 0                         | -                      |      |

| t <sub>d(NREG-NCEx)</sub> | FSMC_NCEx low to FSMC_NREG valid             | -                         | 2                      |      |

| t <sub>h(NCEx-NREG)</sub> | FSMC_NCEx high to FSMC_NREG invalid          | t <sub>HCLK</sub> + 4     | -                      |      |

| t <sub>d(NCEx_NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                         | 5t <sub>HCLK</sub> + 1 |      |

| t <sub>d(NCEx_NOE)</sub>  | FSMC_NCEx low to FSMC_NOE low                | -                         | 5t <sub>HCLK</sub> + 1 |      |

| t <sub>w(NOE)</sub>       | FSMC_NOE low width                           | 8t <sub>HCLK</sub> - 0.5  | 8t <sub>HCLK</sub> + 1 |      |

| t <sub>d(NOE-NCEx</sub>   | FSMC_NOE high to FSMC_NCEx high              | 5t <sub>HCLK</sub> - 0.5  | -                      |      |

| t <sub>su(D-NOE)</sub>    | FSMC_D[15:0] valid data before FSMC_NOE high | 32                        | -                      | ns   |

| t <sub>h(NOE-D)</sub>     | FSMC_NOE high to FSMC_D[15:0] invalid        | t <sub>HCLK</sub>         | -                      |      |

| t <sub>w(NWE)</sub>       | FSMC_NWE low width                           | 8t <sub>HCLK</sub> – 1    | 8t <sub>HCLK</sub> + 4 |      |

| t <sub>d(NWE_NCEx)</sub>  | FSMC_NWE high to FSMC_NCEx high              | 5t <sub>HCLK</sub> + 1.5  | -                      |      |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                         | 5t <sub>HCLK</sub> + 1 |      |

| t <sub>v(NWE-D)</sub>     | FSMC_NWE low to FSMC_D[15:0] valid           | -                         | 0                      |      |

| t <sub>h(NWE-D)</sub>     | FSMC_NWE high to FSMC_D[15:0] invalid        | 11t <sub>HCLK</sub>       | -                      |      |

| t <sub>d(D-NWE)</sub>     | FSMC_D[15:0] valid before FSMC_NWE high      | 13t <sub>HCLK</sub> + 2.5 | -                      |      |

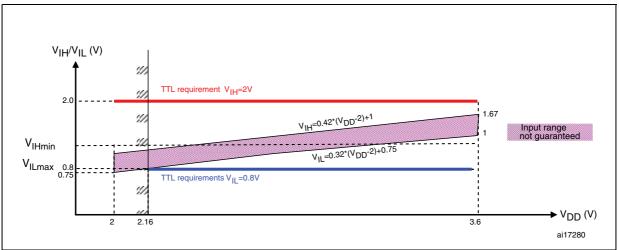

Figure 43. 5 V tolerant I/O input characteristics - TTL port

## **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to ±8 mA, and sink or source up to ± 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ) except PC13, PC14 and PC15 which can sink or source up to ±3 mA. When using the GPIOs PC13 to PC15 in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 8*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 8*).

## **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 50* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*. All I/Os are CMOS and TTL compliant.

| Symbol                         | Parameter                                                                     | Conditions                                                | Min                  | Max | Unit |

|--------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | TTL port <sup>(3)</sup><br>I <sub>IO</sub> = +8 mA        | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | $2.7 V < V_{DD} < 3.6 V$                                  | V <sub>DD</sub> -0.4 | -   | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | CMOS port <sup>(3)</sup>                                  | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | I <sub>IO</sub> =+ 8mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | 2.4                  | -   | V    |

| Table 50  | Output | voltogo | oboroctoriction |

|-----------|--------|---------|-----------------|

| Table 50. | Output | voitage | characteristics |

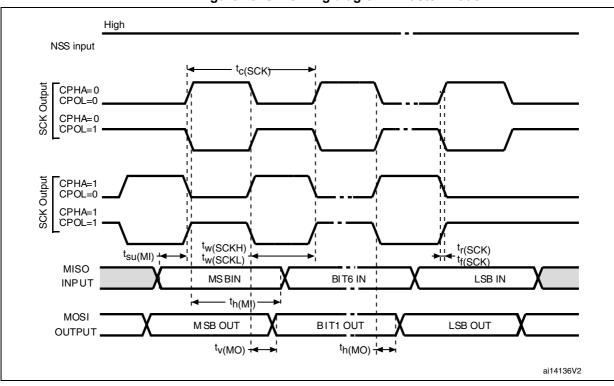

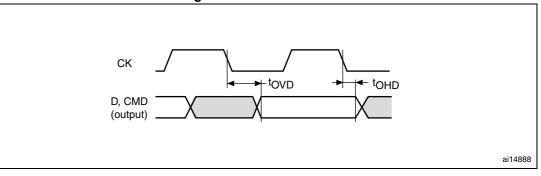

Figure 49. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

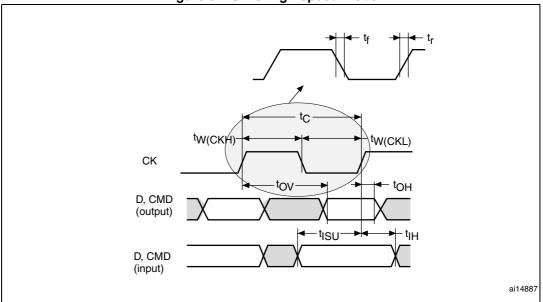

#### SD/SDIO MMC card host interface (SDIO) characteristics

Unless otherwise specified, the parameters given in *Table 58* are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

Refer to Section 5.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (D[7:0], CMD, CK).

Figure 52. SDIO high-speed mode

Figure 53. SD default mode

Table 58. SD / MMC characteristics

| Symbol          | Parameter                                 | Conditions              | Min | Мах | Unit |

|-----------------|-------------------------------------------|-------------------------|-----|-----|------|

| f <sub>PP</sub> | Clock frequency in data transfer mode     | $C_L \le 30 \text{ pF}$ | 0   | 48  | MHz  |

| tW(CKL)         | Clock low time, f <sub>PP</sub> = 16 MHz  | $C_L \le 30 \text{ pF}$ | 32  | -   |      |

| tW(CKH)         | Clock high time, f <sub>PP</sub> = 16 MHz | $C_L \le 30 \text{ pF}$ | 30  | -   | ne   |

| t <sub>r</sub>  | Clock rise time                           | $C_L \le 30 \text{ pF}$ | -   | 4   | ns   |

| t <sub>f</sub>  | Clock fall time                           | $C_L \le 30 \text{ pF}$ | -   | 5   |      |

DocID16554 Rev 4

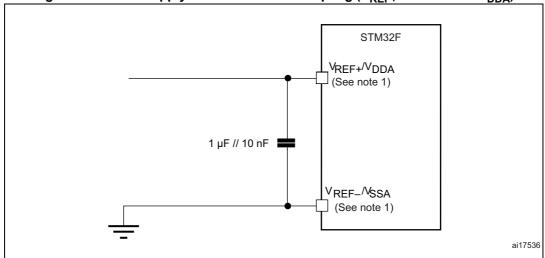

Figure 58. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

1.  $V_{\mathsf{REF+}}$  and  $V_{\mathsf{REF-}}$  inputs are available only on 100-pin packages.

# 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

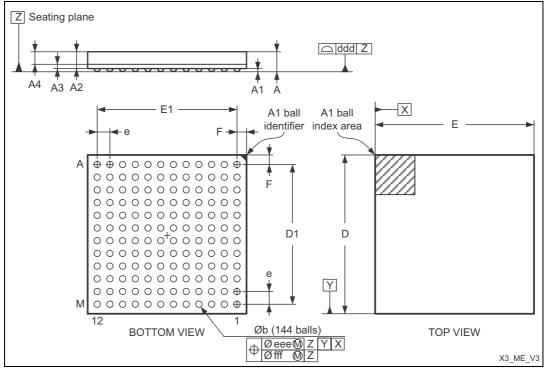

## 6.1 LFBGA144 package information

Figure 60. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package outline

1. Drawing is not to scale.

| Table 68. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, |

|-----------------------------------------------------------------------------------|

| 0.8 mm pitch, package mechanical data                                             |

| Symbol           | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|------------------|-------------|--------|--------|-----------------------|--------|--------|

|                  | Min         | Тур    | Max    | Тур                   | Min    | Max    |

| A <sup>(2)</sup> | -           | -      | 1.700  |                       |        | 0.0669 |

| A1               | 0.210       | -      | -      | 0.0083                |        |        |

| A2               | -           | 1.060  | -      |                       | 0.0417 |        |

| A3               |             | 0.026  |        |                       | 0.0010 |        |

| A4               | -           | 0.800  | -      | -                     | 0.0315 | -      |

| b                | 0.350       | 0.400  | 0.450  | 0.0138                | 0.0157 | 0.0177 |

| D                | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |

| D1               | -           | 8.800  | -      | -                     | 0.3465 | -      |

| E                | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |

| E1               | -           | 8.800  | -      | -                     | 0.3465 | -      |

| е                | -           | 0.800  | -      | -                     | 0.0315 | -      |

| F                | -           | 0.600  | -      | -                     | 0.0236 | -      |

| ddd              | -           | -      | 0.100  | -                     | -      | 0.0039 |

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах    | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| D1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| D3     | -           | 17.500 | -      | -                     | 0.6890 | -      |

| E      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| E1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| E3     | -           | 17.500 | -      | -                     | 0.6890 | -      |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°   | 7°     | 0°                    | 3.5°   | 7°     |

| ССС    | -           | -      | 0.080  | -                     | -      | 0.0031 |

| Table 69. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

1. Values in inches are converted from mm and rounded to 4 decimal digits.