# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 80                                                                    |

| Program Memory Size        | 768KB (768K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 96K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103vft6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.                | STM32F103xF and STM32F103xG performance line block diagram.                                 | 12         |

|--------------------------|---------------------------------------------------------------------------------------------|------------|

| Figure 2.                | Clock tree                                                                                  | 13         |

| Figure 3.                | STM32F103xF/G BGA144 ballout                                                                | 25         |

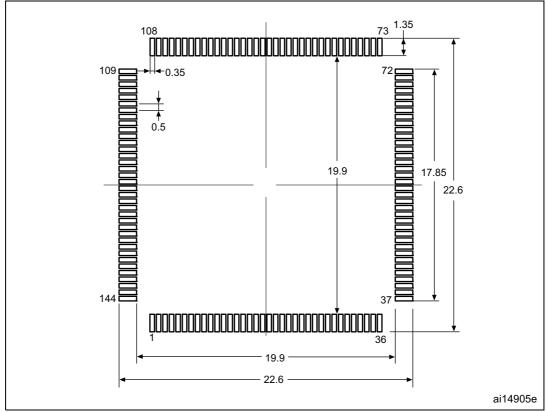

| Figure 4.                | STM32F103xF/G performance line LQFP144 pinout                                               |            |

| Figure 5.                | STM32F103xF/G performance line LQFP100 pinout                                               |            |

| Figure 6.                | STM32F103xF/G performance line LQFP64 pinout                                                | 28         |

| Figure 7.                | Memory map.                                                                                 |            |

| Figure 8.                | Pin loading conditions.                                                                     |            |

| Figure 9.                | Pin input voltage                                                                           |            |

| Figure 10.               | Power supply scheme.                                                                        |            |

| Figure 11.               | Current consumption measurement scheme                                                      |            |

| Figure 12.               | Typical current consumption in Run mode versus frequency (at 3.6 V) -                       |            |

| 0                        | code with data processing running from RAM, peripherals enabled                             | 48         |

| Figure 13.               | Typical current consumption in Run mode versus frequency (at 3.6 V)-                        | -          |

| - gai e i ei             | code with data processing running from RAM, peripherals disabled                            | 48         |

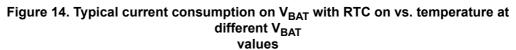

| Figure 14.               | Typical current consumption on $V_{BAT}$ with RTC on vs. temperature at different $V_{BAT}$ |            |

| i iguro i ii             | values                                                                                      | 50         |

| Figure 15.               | Typical current consumption in Stop mode with regulator in run mode                         | 00         |

| rigare re.               | versus temperature at different $V_{DD}$ values                                             | 51         |

| Figure 16.               | Typical current consumption in Stop mode with regulator in low-power                        | 01         |

| rigure ro.               | mode versus temperature at different V <sub>DD</sub> values                                 | 52         |

| Figure 17.               | Typical current consumption in Standby mode versus temperature at                           | 52         |

| riguie i7.               | different V <sub>DD</sub> values                                                            | 52         |

| Figure 18.               | High-speed external clock source AC timing diagram                                          |            |

| Figure 19.               | Low-speed external clock source AC timing diagram                                           |            |

| Figure 19.               | Typical application with an 8 MHz crystal.                                                  |            |

| Figure 20.<br>Figure 21. | Typical application with a 32.768 kHz crystal                                               |            |

| Figure 21.               | Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms                                  |            |

|                          |                                                                                             |            |

| Figure 23.               | Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms                                 |            |

| Figure 24.               | Asynchronous multiplexed PSRAM/NOR read waveforms.                                          |            |

| Figure 25.               | Asynchronous multiplexed PSRAM/NOR write waveforms                                          |            |

| Figure 26.               | Synchronous multiplexed NOR/PSRAM read timings                                              |            |

| Figure 27.               | Synchronous multiplexed PSRAM write timings.                                                |            |

| Figure 28.               | Synchronous non-multiplexed NOR/PSRAM read timings                                          |            |

| Figure 29.               | Synchronous non-multiplexed PSRAM write timings                                             |            |

| Figure 30.               | PC Card/CompactFlash controller waveforms for common memory read access                     |            |

| Figure 31.               | PC Card/CompactFlash controller waveforms for common memory write access                    | 80         |

| Figure 32.               | PC Card/CompactFlash controller waveforms for attribute memory read                         | <b>.</b> . |

|                          | access                                                                                      | 81         |

| Figure 33.               | PC Card/CompactFlash controller waveforms for attribute memory write                        |            |

|                          | access                                                                                      |            |

| Figure 34.               | PC Card/CompactFlash controller waveforms for I/O space read access                         |            |

| Figure 35.               | PC Card/CompactFlash controller waveforms for I/O space write access                        |            |

| Figure 36.               | NAND controller waveforms for read access                                                   |            |

| Figure 37.               | NAND controller waveforms for write access                                                  |            |

| Figure 38.               | NAND controller waveforms for common memory read access                                     |            |

| Figure 39.               | NAND controller waveforms for common memory write access                                    |            |

| Figure 40.               | Standard I/O input characteristics - CMOS port                                              | 92         |

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F103xF and STM32F103xG XL-density performance line microcontrollers. For more details on the whole STMicroelectronics STM32F103xF/G family, please refer to *Section 2.2: Full compatibility throughout the family*.

The XL-density STM32F103xF/G datasheet should be read in conjunction with the STM32F10xxx reference manual.

For information on programming, erasing and protection of the internal Flash memory please refer to the *STM32F10xxx* Flash programming manual. The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the *www.arm.com* website at the following address: *http://infocenter.arm.com*.

# 2.1 Device overview

The STM32F103xF/G XL-density performance line family offers devices in four different package types: from 64 pins to 144 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

*Figure 1* shows the general block diagram of the device family.

| Table 2. STM32F103XF and STM32F103XG features and peripheral counts |                   |                                                                                                                                            |      |             |                  |             |        |  |  |

|---------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|------------------|-------------|--------|--|--|

| I                                                                   | Peripherals       | STM32F103Rx                                                                                                                                |      | STM32F103Vx |                  | STM32F103Zx |        |  |  |

| Flash m                                                             | emory             | 768 KB                                                                                                                                     | 1 MB | 768 KB      | 1 MB             | 768 KB 1 ME |        |  |  |

| SRAM i                                                              | n Kbytes          | 9                                                                                                                                          | 6    | 96          |                  | 90          | 6      |  |  |

| FSMC                                                                |                   | N                                                                                                                                          | lo   | Yes         | S <sup>(1)</sup> | Ye          | s      |  |  |

|                                                                     | General-purpose   |                                                                                                                                            |      | 1(          | )                |             |        |  |  |

| Timers                                                              | Advanced-control  |                                                                                                                                            | 2    |             |                  |             |        |  |  |

|                                                                     | Basic             |                                                                                                                                            |      | 2           |                  |             |        |  |  |

| SPI(I <sup>2</sup> S) <sup>(2)</sup>                                |                   |                                                                                                                                            |      | 3(2         | 2)               |             |        |  |  |

| Comm                                                                | I <sup>2</sup> C  |                                                                                                                                            | 2    |             |                  |             |        |  |  |

|                                                                     | USART             | 5                                                                                                                                          |      |             |                  |             |        |  |  |

|                                                                     | USB               | 1                                                                                                                                          |      |             |                  |             |        |  |  |

|                                                                     | CAN               | 1                                                                                                                                          |      |             |                  |             |        |  |  |

|                                                                     | SDIO              | 1                                                                                                                                          |      |             |                  |             |        |  |  |

| GPIOs                                                               | •                 | 51                                                                                                                                         |      | 80          |                  | 112         |        |  |  |

| 12-bit A                                                            |                   | 3                                                                                                                                          |      | 3           |                  | 3           |        |  |  |

| Number                                                              | of channels       | 1                                                                                                                                          | 6    | 16          |                  | 21          |        |  |  |

| 12-bit D<br>Number                                                  | AC<br>of channels | 2 2                                                                                                                                        |      |             |                  |             |        |  |  |

| CPU fre                                                             | quency            | 72 MHz                                                                                                                                     |      |             |                  |             |        |  |  |

| Operatir                                                            | ng voltage        | 2.0 to 3.6 V                                                                                                                               |      |             |                  |             |        |  |  |

| Operatir                                                            | ng temperatures   | Ambient temperatures: -40 to +85 °C /-40 to +105 °C (see <i>Table 10</i> )<br>Junction temperature: -40 to + 125 °C (see <i>Table 10</i> ) |      |             |                  |             |        |  |  |

| Package                                                             | 9                 | LQF                                                                                                                                        | P64  | LQFI        | P100             | LQFP144,    | BGA144 |  |  |

|                                                                     |                   |                                                                                                                                            |      |             |                  |             |        |  |  |

Table 2. STM32F103xF and STM32F103xG features and peripheral counts

For the LQFP100 package, only FSMC Bank1 and Bank2 are available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package.

2. The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the  $l^2S$  audio mode.

# 2.3.5 Embedded SRAM

96 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

# 2.3.6 FSMC (flexible static memory controller)

The FSMC is embedded in the STM32F103xF and STM32F103xG performance line family. It has four Chip Select outputs supporting the following modes: PC Card/Compact Flash, SRAM, PSRAM, NOR and NAND.

Functionality overview:

- The three FSMC interrupt lines are ORed in order to be connected to the NVIC

- Write FIFO

- Code execution from external memory except for NAND Flash and PC Card

- The targeted frequency, f<sub>CLK</sub>, is HCLK/2, so external access is at 36 MHz when HCLK is at 72 MHz and external access is at 24 MHz when HCLK is at 48 MHz

# 2.3.7 LCD parallel interface

The FSMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost-effective graphic applications using LCD modules with embedded controllers or high-performance solutions using external controllers with dedicated acceleration.

# 2.3.8 Nested vectored interrupt controller (NVIC)

The STM32F103xF and STM32F103xG performance line embeds a nested vectored interrupt controller able to handle up to 60 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>®</sup>-M3) and 16 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of *late arriving* higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

# 2.3.9 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 19 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 112 GPIOs can be connected to the 16 external interrupt lines.

# 2.3.21 Serial peripheral interface (SPI)

Up to three SPIs are able to communicate up to 18 Mbits/s in slave and master modes in full-duplex and simplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

All SPIs can be served by the DMA controller.

# 2.3.22 Inter-integrated sound (I<sup>2</sup>S)

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI2 and SPI3) are available, that can be operated in master or slave mode. These interfaces can be configured to operate with 16/32 bit resolution, as input or output channels. Audio sampling frequencies from 8 kHz up to 48 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

# 2.3.23 SDIO

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit. The interface allows data transfer at up to 48 MHz in 8-bit mode, and is compliant with SD Memory Card Specifications Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is also fully compliant with the CE-ATA digital protocol Rev1.1.

#### 2.3.24 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

# 2.3.25 Universal serial bus (USB)

The STM32F103xF and STM32F103xG performance line embed a USB device peripheral compatible with the USB full-speed 12 Mbs. The USB interface implements a full-speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and suspend/resume support. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator).

# 2.3.26 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current-capable.

DocID16554 Rev 4

|          | Pir    | าร      |         |                    |                     |                            |                                                  | Alternate function                                                       | -                              |  |

|----------|--------|---------|---------|--------------------|---------------------|----------------------------|--------------------------------------------------|--------------------------------------------------------------------------|--------------------------------|--|

| LFBGA144 | LQFP64 | LQFP100 | LQFP144 | Pin name           | Type <sup>(1)</sup> | I / O level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                  | Remap                          |  |

| E11      | 40     | 66      | 99      | PC9                | I/O                 | FT                         | PC9                                              | TIM8_CH4 / SDIO_D1                                                       | TIM3_CH4                       |  |

| E12      | 41     | 67      | 100     | PA8                | I/O                 | FT                         | PA8                                              | USART1_CK / TIM1_CH1 <sup>(7)</sup> /<br>MCO                             | -                              |  |

| D12      | 42     | 68      | 101     | PA9                | I/O                 | FT                         | PA9                                              | USART1_TX <sup>(7)</sup> / TIM1_CH2 <sup>(7)</sup>                       | -                              |  |

| D11      | 43     | 69      | 102     | PA10               | I/O                 | FT                         | PA10                                             | USART1_RX <sup>(7)</sup> / TIM1_CH3 <sup>(7)</sup>                       | -                              |  |

| C12      | 44     | 70      | 103     | PA11               | I/O                 | FT                         | PA11                                             | USART1_CTS / USB_DM /<br>CAN_RX <sup>(7)</sup> / TIM1_CH4 <sup>(7)</sup> | -                              |  |

| B12      | 45     | 71      | 104     | PA12               | I/O                 | FT                         | PA12                                             | USART1_RTS / USB_DP /<br>CAN_TX <sup>(7)</sup> / TIM1_ETR <sup>(7)</sup> | -                              |  |

| A12      | 46     | 72      | 105     | PA13               | I/O                 | FT                         | JTMS-<br>SWDIO                                   | -                                                                        | PA13                           |  |

| C11      | -      | 73      | 106     |                    |                     |                            | Nc                                               | Not connected                                                            |                                |  |

| G9       | 47     | 74      | 107     | V <sub>SS_2</sub>  | S                   |                            | V <sub>SS_2</sub>                                | -                                                                        | -                              |  |

| F9       | 48     | 75      | 108     | V <sub>DD_2</sub>  | S                   |                            | V <sub>DD_2</sub>                                | -                                                                        | -                              |  |

| A11      | 49     | 76      | 109     | PA14               | I/O                 | FT                         | JTCK-<br>SWCLK                                   | -                                                                        | PA14                           |  |

| A10      | 50     | 77      | 110     | PA15               | I/O                 | FT                         | JTDI                                             | SPI3_NSS / 12S3_WS                                                       | TIM2_CH1_ETR<br>PA15/ SPI1_NSS |  |

| B11      | 51     | 78      | 111     | PC10               | I/O                 | FT                         | PC10                                             | UART4_TX / SDIO_D2                                                       | USART3_TX                      |  |

| B10      | 52     | 79      | 112     | PC11               | I/O                 | FT                         | PC11                                             | UART4_RX / SDIO_D3                                                       | USART3_RX                      |  |

| C10      | 53     | 80      | 113     | PC12               | I/O                 | FT                         | PC12                                             | UART5_TX / SDIO_CK                                                       | USART3_CK                      |  |

| E10      | -      | 81      | 114     | PD0                | I/O                 | FT                         | PD0                                              | FSMC_D2 <sup>(9)</sup>                                                   | CAN_RX                         |  |

| D10      | -      | 82      | 115     | PD1                | I/O                 | FT                         | PD1                                              | FSMC_D3 <sup>(9)</sup>                                                   | CAN_TX                         |  |

| E9       | 54     | 83      | 116     | PD2                | I/O                 | FT                         | PD2                                              | TIM3_ETR / UART5_RX /<br>SDIO_CMD                                        | -                              |  |

| D9       | -      | 84      | 117     | PD3                | I/O                 | FT                         | PD3                                              | FSMC_CLK                                                                 | USART2_CTS                     |  |

| C9       | -      | 85      | 118     | PD4                | I/O                 | FT                         | PD4                                              | FSMC_NOE                                                                 | USART2_RTS                     |  |

| B9       | -      | 86      | 119     | PD5                | I/O                 | FT                         | PD5                                              | FSMC_NWE                                                                 | USART2_TX                      |  |

| E7       | -      | -       | 120     | V <sub>SS_10</sub> | S                   |                            | V <sub>SS_10</sub>                               | -                                                                        | -                              |  |

| F7       | -      | -       | 121     | V <sub>DD_10</sub> | S                   |                            | $V_{DD_{10}}$                                    | -                                                                        | -                              |  |

| A8       | -      | 87      | 122     | PD6                | I/O                 | FT                         | PD6                                              | FSMC_NWAIT                                                               | USART2_RX                      |  |

# Table 5. STM32F103xF and STM32F103xG pin definitions (continued)

- 4. If several peripherals share the same I/O pin, to avoid conflict between these alternate functions only one peripheral should be enabled at a time through the peripheral clock enable bit (in the corresponding RCC peripheral clock enable register).

- PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these IOs must not be used as a current source (e.g. to drive an LED).

- 6. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

- 7. For the LQFP64 package, the pins number 5 and 6 are configured as OSC\_IN/OSC\_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For the LQFP100 and LQFP144/BGA144 packages, PD0 and PD1 are available by default, so there is no need for remapping. For more details, refer to Alternate function I/O and debug configuration section in the STM32F10xxx reference manual.

- This alternate function can be remapped by software to some other port pins (if available on the used package). For more

details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual,

available from the STMicroelectronics website: www.st.com.

- 9. For devices delivered in LQFP64 packages, the FSMC function is not available.

|                          |                                   |                                                                                                                                                                     | Typ <sup>(1)</sup>                                       |                                                          |                                                          | Μ                        | ax                         |      |

|--------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|--------------------------|----------------------------|------|

| Symbol                   | Parameter                         | Conditions                                                                                                                                                          | V <sub>DD</sub> /V <sub>BA</sub><br><sub>T</sub> = 2.0 V | V <sub>DD</sub> /V <sub>BA</sub><br><sub>T</sub> = 2.4 V | V <sub>DD</sub> /V <sub>BA</sub><br><sub>T</sub> = 3.3 V | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °C | Unit |

|                          |                                   | Regulator in run mode, low-speed<br>and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog),<br>f <sub>CK</sub> =8 MHz | 44.8                                                     | 45.3                                                     | 46.4                                                     | 810                      | 1680                       |      |

| I <sub>DD</sub>          |                                   | Regulator in low-power mode, low-<br>speed and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog)                     | 37.4                                                     | 37.8                                                     | 38.7                                                     | 790                      | 1660                       | μA   |

|                          | Supply current in<br>Standby mode | Low-speed internal RC oscillator<br>and independent watchdog OFF,<br>low-speed oscillator and RTC OFF                                                               | 1.8                                                      | 2.0                                                      | 2.5                                                      | 5 <sup>(2)</sup>         | 8 <sup>(2)</sup>           |      |

| I <sub>DD_VBA</sub><br>T | Backup domain<br>supply current   | Low-speed oscillator and RTC ON                                                                                                                                     | 1.05                                                     | 1.1                                                      | 1.4                                                      | 2 <sup>(2)</sup>         | 2.3 <sup>(2)</sup>         |      |

| Table 17. Typical and maximum current consum | ptions in Stop and Standby modes |

|----------------------------------------------|----------------------------------|

|                                              |                                  |

1. Typical values are measured at  $T_A$  = 25 °C.

2. Guaranteed by characterization results, not tested in production..

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 20*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 7

| Perip              | Current consumption      |       |

|--------------------|--------------------------|-------|

|                    | DMA1                     | 23,06 |

|                    | DMA2                     | 18,47 |

| AHB (up to 72 MHz) | FSMC                     | 55,14 |

|                    | CRC                      | 2,08  |

|                    | SDIO                     | 32,22 |

|                    | BusMatrix <sup>(2)</sup> | 11,67 |

#### Table 20. Peripheral current consumption<sup>(1)</sup>

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 24*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                                                                               | Conditions                       |                                       | Min | Тур | Max | Unit |  |  |

|-------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------|-----|-----|-----|------|--|--|

| R <sub>F</sub>                      | Feedback resistor                                                                                       |                                  | -                                     | -   | 5   | -   | MΩ   |  |  |

| C <sup>(2)</sup>                    | Recommended load capacitance<br>versus equivalent serial<br>resistance of the crystal (R <sub>S</sub> ) | R <sub>S</sub> = 30 kΩ           |                                       | -   | -   | 15  | pF   |  |  |

| I <sub>2</sub>                      | LSE driving current                                                                                     | V <sub>DD</sub> =                | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ |     | -   | 1.4 | μA   |  |  |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                             | -                                |                                       | 5   | -   | -   | µA/V |  |  |

|                                     | Startup time                                                                                            | V <sub>DD</sub> is<br>stabilized | T <sub>A</sub> = 50 °C                | -   | 1.5 | -   |      |  |  |

|                                     |                                                                                                         |                                  | T <sub>A</sub> = 25 °C                | -   | 2.5 | -   |      |  |  |

|                                     |                                                                                                         |                                  | T <sub>A</sub> = 10 °C                | -   | 4   | -   |      |  |  |

| <b>↓</b> (3)                        |                                                                                                         |                                  | T <sub>A</sub> = 0 °C                 | -   | 6   | -   |      |  |  |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> |                                                                                                         |                                  | T <sub>A</sub> = -10 °C               | -   | 10  | -   |      |  |  |

|                                     |                                                                                                         |                                  | T <sub>A</sub> = -20 °C               | -   | 17  | -   |      |  |  |

|                                     |                                                                                                         |                                  | T <sub>A</sub> = -30 °C               | -   | 32  | -   |      |  |  |

|                                     |                                                                                                         |                                  | T <sub>A</sub> = -40 °C               | -   | 60  | -   |      |  |  |

| Table 24. LSE oscillator characteristic | s (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)(2)</sup> |

|-----------------------------------------|-----------------------------------------------------|

|-----------------------------------------|-----------------------------------------------------|

1. Guaranteed by characterization results, not tested in production.

Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) until a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer, PCB layout and humidity.

**Caution:** To avoid exceeding the maximum value of  $C_{L1}$  and  $C_{L2}$  (15 pF) it is strongly recommended to use a resonator with a load capacitance  $C_L \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF. **Example:** if you choose a resonator with a load capacitance of  $C_L = 6$  pF, and  $C_{stray} = 2$  pF, then  $C_{L1} = C_{L2} = 8$  pF.

Note: For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 21).  $C_{L1}$  and  $C_{L2}$ , are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . Load capacitance  $C_L$  has the following formula:  $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

| Symbol           | Parameter      | Conditions                                                                              | Value              | 11:::4  |

|------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|---------|

|                  |                | Conditions                                                                              | Min <sup>(1)</sup> | Unit    |

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 |         |

Table 30. Flash memory endurance and data retention

1. Guaranteed by characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

| Table 34. Asynchronous multiplexed TortAlin/Norr read unings (continued) |                                    |     |     |      |  |  |

|--------------------------------------------------------------------------|------------------------------------|-----|-----|------|--|--|

| Symbol Parameter                                                         |                                    | Min | Мах | Unit |  |  |

| t <sub>h(Data_NE)</sub>                                                  | Data hold time after FSMC_NEx high | 0   | -   | ns   |  |  |

| t <sub>h(Data_NOE)</sub>                                                 | Data hold time after FSMC_NOE high | 0   | -   | ns   |  |  |

| 1. C <sub>L</sub> = 15 pF.                                               |                                    | 1   | 1   | 1    |  |  |

| Table 34. Asynchronous multiplexed PSRAM/NOR read timings <sup>(1)</sup> (contin | ued) |

|----------------------------------------------------------------------------------|------|

|----------------------------------------------------------------------------------|------|

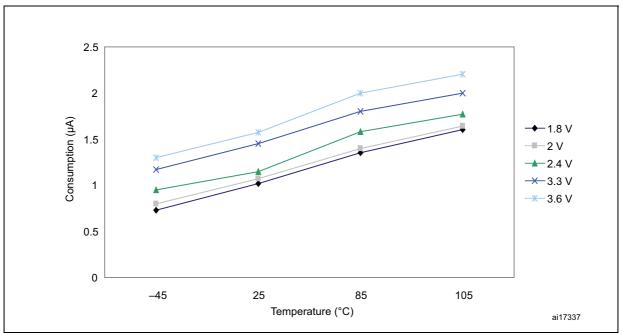

Figure 25. Asynchronous multiplexed PSRAM/NOR write waveforms

| Symbol                  | Parameter                                                 | Min                      | Мах                     | Unit |

|-------------------------|-----------------------------------------------------------|--------------------------|-------------------------|------|

| t <sub>w(NE)</sub>      | FSMC_NE low time                                          | 5t <sub>HCLK</sub> + 0.5 | 5t <sub>HCLK</sub> + 2  | ns   |

| t <sub>v(NWE_NE)</sub>  | FSMC_NEx low to FSMC_NWE low                              | t <sub>HCLK</sub> + 1    | t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>w(NWE)</sub>     | FSMC_NWE low time                                         | 3t <sub>HCLK</sub> + 0.5 | 3t <sub>HCLK</sub> + 1  | ns   |

| t <sub>h(NE_NWE)</sub>  | FSMC_NWE high to FSMC_NE high hold time                   | t <sub>HCLK</sub> – 0.5  | -                       | ns   |

| t <sub>v(A_NE)</sub>    | FSMC_NEx low to FSMC_A valid                              | -                        | 3.5                     | ns   |

| t <sub>v(NADV_NE)</sub> | FSMC_NEx low to FSMC_NADV low                             | 0                        | 1                       | ns   |

| t <sub>w(NADV)</sub>    | FSMC_NADV low time                                        | t <sub>HCLK</sub> + 0.5  | t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>h(AD_NADV)</sub> | FSMC_AD (address) valid hold time after<br>FSMC_NADV high | t <sub>HCLK</sub> – 0.5  | -                       | ns   |

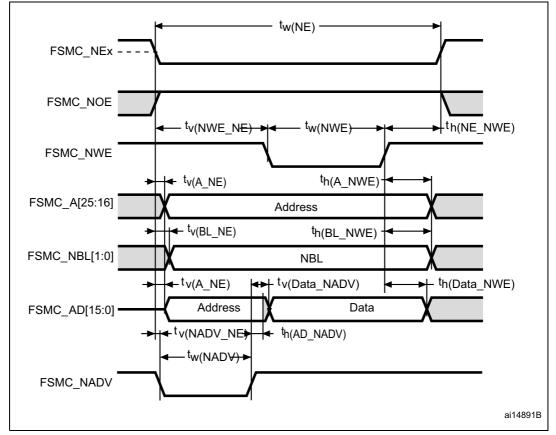

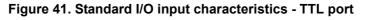

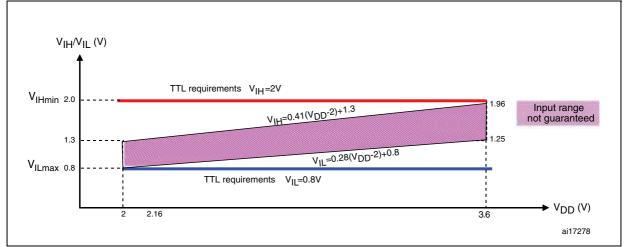

Figure 40. Standard I/O input characteristics - CMOS port

Figure 42. 5 V tolerant I/O input characteristics - CMOS port

DocID16554 Rev 4

| Symbol                            | Parameter                                                                     | Conditions                                                  | Min                  | Max | Unit |

|-----------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> = +20 mA                                    | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(2)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | I <sub>IO</sub> = +20 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | V <sub>DD</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> = +6 mA                                     | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(2)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2 V < V <sub>DD</sub> < 2.7 V                               | V <sub>DD</sub> 0.4  | -   | V    |

Table 50. Output voltage characteristics (continued)

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 8* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 8* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

3. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

4. Guaranteed by characterization results, not tested in production.

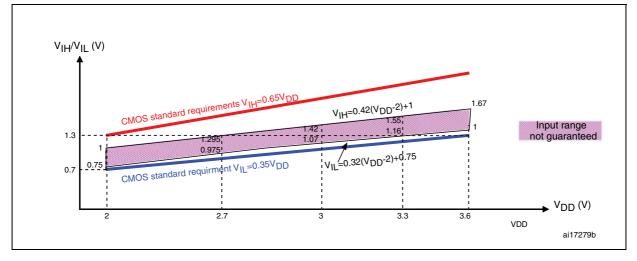

#### Figure 44. I/O AC characteristics definition

# 5.3.15 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 49*).

Unless otherwise specified, the parameters given in *Table 52* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| Symbol                               | Parameter                                       | Conditions        | Min  | Тур | Max                  | Unit |

|--------------------------------------|-------------------------------------------------|-------------------|------|-----|----------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | -                 | -0.5 | -   | 0.8                  | v    |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | -                 | 2    | -   | V <sub>DD</sub> +0.5 | v    |

| V <sub>hys(NRST)</sub>               | NRST Schmitt trigger voltage<br>hysteresis      | -                 | -    | 200 | -                    | mV   |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 30   | 40  | 50                   | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>  | NRST Input filtered pulse                       | -                 | -    | -   | 100                  | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup> | NRST Input not filtered pulse                   | -                 | 300  | -   | -                    | ns   |

Table 52. NRST pin characteristics

1. Guaranteed by design, not tested in production.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

| Table 50. 3D / MMC Characteristics |                                                                     |                         |     |     |      |  |  |

|------------------------------------|---------------------------------------------------------------------|-------------------------|-----|-----|------|--|--|

| Symbol                             | Parameter                                                           | Conditions              | Min | Мах | Unit |  |  |

|                                    | CMD, D inputs (referenced to CK)                                    |                         |     |     |      |  |  |

| t <sub>ISU</sub>                   | Input setup time                                                    | $C_L \le 30 \text{ pF}$ | 2   | -   |      |  |  |

| t <sub>IH</sub>                    | Input hold time                                                     | $C_L \le 30 \text{ pF}$ | 0   | -   | ns   |  |  |

| CMD, D out                         | CMD, D outputs (referenced to CK) in MMC and SD HS mode             |                         |     |     |      |  |  |

| t <sub>OV</sub>                    | Output valid time                                                   | $C_L \le 30 \text{ pF}$ | -   | 6   |      |  |  |

| t <sub>OH</sub>                    | Output hold time                                                    | $C_L \le 30 \text{ pF}$ | 0   | -   | ns   |  |  |

|                                    | CMD, D outputs (referenced to CK) in SD default mode <sup>(1)</sup> |                         |     |     |      |  |  |

| t <sub>OVD</sub>                   | Output valid default time                                           | $C_L \le 30 \text{ pF}$ | -   | 7   | ne   |  |  |

| t <sub>OHD</sub>                   | Output hold default time                                            | $C_L \le 30 \text{ pF}$ | 0.5 | -   | — ns |  |  |

#### Table 58. SD / MMC characteristics

1. Refer to SDIO\_CLKCR, the SDI clock control register to control the CK output.

#### **USB** characteristics

The USB interface is USB-IF certified (Full Speed).

#### Table 59. USB startup time

| Symbol                              | Parameter                    | Мах | Unit |

|-------------------------------------|------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |

1. Guaranteed by design, not tested in production.

# 5.3.18 CAN (controller area network) interface

Refer to Section 5.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

#### 5.3.19 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 62* are preliminary values derived from tests performed under ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 10*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                           | Parameter                                 | Conditions                                            | Min                                                         | Тур | Max                | Unit               |

|----------------------------------|-------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|-----|--------------------|--------------------|

| V <sub>DDA</sub>                 | Power supply                              | -                                                     | 2.4                                                         | -   | 3.6                | V                  |

| V <sub>REF+</sub>                | Positive reference voltage                | -                                                     | 2.4                                                         | -   | V <sub>DDA</sub>   | V                  |

| I <sub>VREF</sub>                | Current on the V <sub>REF</sub> input pin | -                                                     | -                                                           | 160 | 220 <sup>(1)</sup> | μA                 |

| f <sub>ADC</sub>                 | ADC clock frequency                       | -                                                     | 0.6                                                         | -   | 14                 | MHz                |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate                             | -                                                     | 0.05                                                        | -   | 1                  | MHz                |

| f (2)                            | External trigger frequency                | f <sub>ADC</sub> = 14 MHz                             | -                                                           | -   | 823                | kHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> | External ingger frequency                 | -                                                     | -                                                           | -   | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                 | Conversion voltage range <sup>(3)</sup>   | -                                                     | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -   | V <sub>REF+</sub>  | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                  | See <i>Equation 1</i> and <i>Table 63</i> for details | -                                                           | -   | 50                 | κΩ                 |

| R <sub>ADC</sub> <sup>(2)</sup>  | Sampling switch resistance                | -                                                     | -                                                           | -   | 1                  | κΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor        | -                                                     | -                                                           | -   | 8                  | pF                 |

| <b>4</b> (2)                     | Colibration time                          | f <sub>ADC</sub> = 14 MHz                             | 5.9                                                         |     |                    | μs                 |

| t <sub>CAL</sub> <sup>(2)</sup>  | Calibration time                          | -                                                     | 83                                                          |     |                    | 1/f <sub>ADC</sub> |

| + (2)                            | Injection trigger conversion              | f <sub>ADC</sub> = 14 MHz                             | -                                                           | -   | 0.214              | μs                 |

| $t_{lat}^{(2)}$                  | latency                                   | -                                                     | -                                                           | -   | 3 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (2)            | Regular trigger conversion                | f <sub>ADC</sub> = 14 MHz                             | -                                                           | -   | 0.143              | μs                 |

| 'latr` ´                         | latency                                   | -                                                     | -                                                           | -   | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| ts <sup>(2)</sup>                | Sampling time                             | f <sub>ADC</sub> = 14 MHz                             | 0.107                                                       | -   | 17.1               | μs                 |

| 'S` '                            |                                           | -                                                     | 1.5                                                         | -   | 239.5              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                             | -                                                     | 0                                                           | 0   | 1                  | μs                 |

|                                  | Total conversion time                     | f <sub>ADC</sub> = 14 MHz                             | 1                                                           |     | 18                 | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | (including sampling time)                 | -                                                     | 14 to 252 (t <sub>S</sub> for sa<br>successive approx       |     |                    | 1/f <sub>ADC</sub> |

| Table | 62. | ADC | characteristics |

|-------|-----|-----|-----------------|

|-------|-----|-----|-----------------|

1. Guaranteed by characterization results, not tested in production.

| Symbol |        | millimeters |        |        | inches <sup>(1)</sup> |        |  |

|--------|--------|-------------|--------|--------|-----------------------|--------|--|

| Symbol | Min    | Тур         | Мах    | Min    | Тур                   | Max    |  |

| А      | -      | -           | 1.600  | -      | -                     | 0.0630 |  |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551                | 0.0571 |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087                | 0.0106 |  |

| с      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |  |

| D      | 21.800 | 22.000      | 22.200 | 0.8583 | 0.8661                | 0.8740 |  |

| D1     | 19.800 | 20.000      | 20.200 | 0.7795 | 0.7874                | 0.7953 |  |

| D3     | -      | 17.500      | -      | -      | 0.6890                | -      |  |

| E      | 21.800 | 22.000      | 22.200 | 0.8583 | 0.8661                | 0.8740 |  |

| E1     | 19.800 | 20.000      | 20.200 | 0.7795 | 0.7874                | 0.7953 |  |

| E3     | -      | 17.500      | -      | -      | 0.6890                | -      |  |

| е      | -      | 0.500       | -      | -      | 0.0197                | -      |  |

| L      | 0.450  | 0.600       | 0.750  | 0.0177 | 0.0236                | 0.0295 |  |

| L1     | -      | 1.000       | -      | -      | 0.0394                | -      |  |

| k      | 0°     | 3.5°        | 7°     | 0°     | 3.5°                  | 7°     |  |

| ССС    | -      | -           | 0.080  | -      | -                     | 0.0031 |  |

| Table 69. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 63. LQFP144 - 144-pin,20 x 20 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-May-2015 | 4        | Added document status on first page.<br>Replace DAC1_OUT/DAC2_OUT by DAC_OUT1/DAC_OUT2, and<br>updated TIM5 in <i>Figure 1: STM32F103xF and STM32F103xG</i><br><i>performance line block diagram on page 12.</i><br>Replaced USBDP/USBDM by USB_DP/USB_DM in the whole<br>document.<br>Updated notes related to electrical values guaranteed by<br>characterization results.<br>Updated <i>Table 20: Peripheral current consumption.</i><br>Updated <i>Table 36: Synchronous multiplexed NOR/PSRAM read</i><br><i>timings</i> to <i>Table 39: Synchronous non-multiplexed PSRAM write</i><br><i>timings</i> to <i>Table 39: Synchronous non-multiplexed PSRAM write</i><br><i>timings</i> to <i>Table 39: Synchronous non-multiplexed PSRAM read</i><br><i>timings</i> on <i>Dage 73</i> and<br><i>Figure 28: Synchronous non-multiplexed NOR/PSRAM read timings on</i><br><i>page 77</i> and <i>Figure 35: PC Card/CompactFlash controller</i> waveforms<br><i>for I/O space write access on page 83.</i><br>Updated CDM class in <i>Table 46: ESD absolute maximum ratings.</i><br>Updated Figure 49: <i>SPI timing diagram - master mode</i> <sup>(1)</sup> on <i>page 96</i> and<br><i>Figure 45: Recommended NRST pin protection on page 97.</i><br>Updated <i>Figure 49: SPI timing diagram - master mode</i> <sup>(1)</sup> on <i>page 96.</i><br>Modified note 3 in <i>Table 56: SPI characteristics.</i><br><i>Section : I2C interface characteristics:</i> Updated introduction, updated<br><i>Table 54: I<sup>2</sup>C characteristics and Figure 46: I<sup>2</sup>C bus AC waveforms and</i><br><i>measurement circuit on page 99.</i><br>Modified note 2 in <i>Table 64: ADC accuracy - limited test conditions,</i><br><i>Figure 55: ADC accuracy characteristics on page 110</i> and <i>Figure 56:</i><br><i>Typical connection diagram using the ADC on page 111.</i> Updated<br><i>Figure 57: Power supply and reference decoupling</i> (V <sub><i>REF+</i></sub> not<br><i>connected to V<sub>DDA</sub>) on page 111 and Figure 58: Power supply and</i><br><i>reference decoupling</i> (V <sub><i>REF+</i></sub> connected to V <sub>DDA</sub> ) on page 112.<br>Updated Section 6.1: <i>LFBGA144 package information</i> and added<br>Section <i>: Device marking for LFBGA144 package.</i><br>Updated Section 6.3: <i>LQFP144 package.</i><br>Updated Section 6.3: <i>LQFP144 package.</i><br>Updated Section 6.3: <i>LQFP144 package.</i><br>Updated Section 6.4: <i>LQF</i> |

Table 74. Document revision history