Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 112                                                                   |

| Program Memory Size        | 768KB (768K × 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 96K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 21x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 144-LFBGA                                                             |

| Supplier Device Package    | 144-LFBGA (10x10)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103zfh6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | oduction |                                                                            |

|---|-------|----------|----------------------------------------------------------------------------|

| 2 | Dese  | cription |                                                                            |

|   | 2.1   | Device   | overview                                                                   |

|   | 2.2   | Full co  | mpatibility throughout the family                                          |

|   | 2.3   | Overvie  | ew                                                                         |

|   |       | 2.3.1    | ARM <sup>®</sup> Cortex <sup>®</sup> -M3 core with embedded Flash and SRAM |

|   |       | 2.3.2    | Memory protection unit                                                     |

|   |       | 2.3.3    | Embedded Flash memory                                                      |

|   |       | 2.3.4    | CRC (cyclic redundancy check) calculation unit                             |

|   |       | 2.3.5    | Embedded SRAM                                                              |

|   |       | 2.3.6    | FSMC (flexible static memory controller)                                   |

|   |       | 2.3.7    | LCD parallel interface                                                     |

|   |       | 2.3.8    | Nested vectored interrupt controller (NVIC)                                |

|   |       | 2.3.9    | External interrupt/event controller (EXTI)                                 |

|   |       | 2.3.10   | Clocks and startup                                                         |

|   |       | 2.3.11   | Boot modes                                                                 |

|   |       | 2.3.12   | Power supply schemes                                                       |

|   |       | 2.3.13   | Power supply supervisor                                                    |

|   |       | 2.3.14   | Voltage regulator                                                          |

|   |       | 2.3.15   | Low-power modes                                                            |

|   |       | 2.3.16   | DMA                                                                        |

|   |       | 2.3.17   | RTC (real-time clock) and backup registers                                 |

|   |       | 2.3.18   | Timers and watchdogs                                                       |

|   |       | 2.3.19   | I <sup>2</sup> C bus                                                       |

|   |       | 2.3.20   | Universal synchronous/asynchronous receiver transmitters (USARTs) . 21     |

|   |       | 2.3.21   | Serial peripheral interface (SPI) 22                                       |

|   |       | 2.3.22   | Inter-integrated sound (I <sup>2</sup> S)                                  |

|   |       | 2.3.23   | SDIO                                                                       |

|   |       | 2.3.24   | Controller area network (CAN)                                              |

|   |       | 2.3.25   | Universal serial bus (USB) 22                                              |

|   |       | 2.3.26   | GPIOs (general-purpose inputs/outputs)                                     |

|   |       | 2.3.27   | ADC (analog to digital converter)                                          |

|   |       | 2.3.28   | DAC (digital-to-analog converter)                                          |

DocID16554 Rev 4

| Figure 41. | Standard I/O input characteristics - TTL port                                                |   |

|------------|----------------------------------------------------------------------------------------------|---|

| Figure 42. | 5 V tolerant I/O input characteristics - CMOS port                                           |   |

| Figure 43. | 5 V tolerant I/O input characteristics - TTL port93                                          | 3 |

| Figure 44. | I/O AC characteristics definition                                                            | 6 |

| Figure 45. | Recommended NRST pin protection                                                              |   |

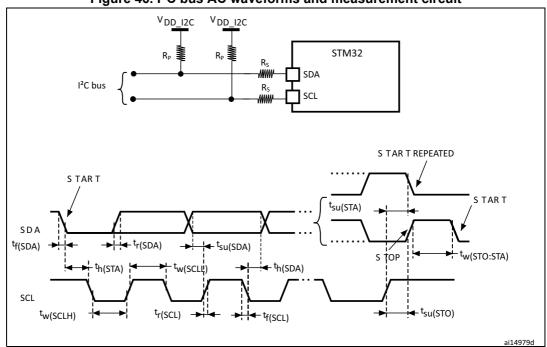

| Figure 46. | I <sup>2</sup> C bus AC waveforms and measurement circuit                                    | 9 |

| Figure 47. | SPI timing diagram - slave mode and CPHA = 0 10                                              |   |

| Figure 48. | SPI timing diagram - slave mode and CPHA = $1^{(1)}$                                         | 1 |

| Figure 49. | SPI timing diagram - master mode <sup>(1)</sup> 102                                          | 2 |

| Figure 50. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup> 104                  | 4 |

| Figure 51. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup> 104                 | 4 |

| Figure 52. | SDIO high-speed mode                                                                         | 5 |

| Figure 53. | SD default mode                                                                              | 5 |

| Figure 54. | USB timings: definition of data signal rise and fall time                                    | 7 |

| Figure 55. | ADC accuracy characteristics                                                                 | 0 |

| Figure 56. | Typical connection diagram using the ADC                                                     | 1 |

| Figure 57. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) |   |

| Figure 58. | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )     | 2 |

| Figure 59. | 12-bit buffered /non-buffered DAC                                                            |   |

| Figure 60. | LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm,                      |   |

|            | 0.8 mm pitch, package outline                                                                | 7 |

| Figure 61. | LFBGA144 marking example (package top view)                                                  | 8 |

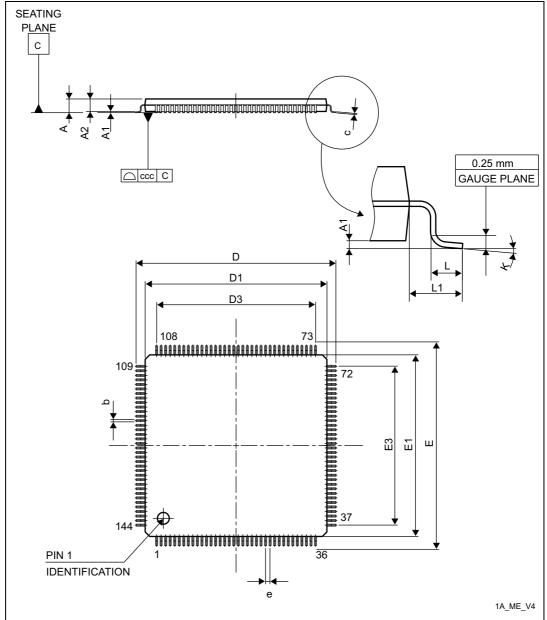

| Figure 62. | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline                          | 9 |

| Figure 63. | LQFP144 - 144-pin,20 x 20 mm low-profile quad flat package                                   |   |

|            | recommended footprint                                                                        | 1 |

| Figure 64. | LQFP144 marking example (package top view)122                                                | 2 |

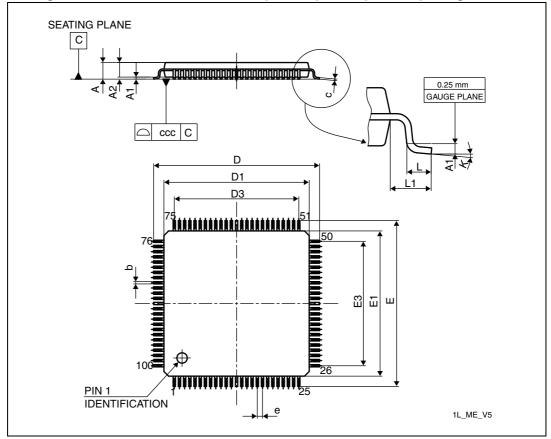

| Figure 65. | LFP100 – 14 x 14 mm 100 pin low-profile quad flat package outline                            | 3 |

| Figure 66. | LQFP100 recommended footprint                                                                | 4 |

| Figure 67. | LQFP100 marking example (package top view)12                                                 | 5 |

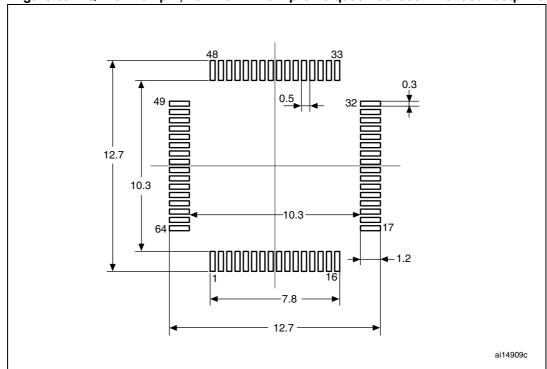

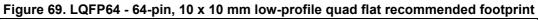

| Figure 68. | LFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline                              | 6 |

| Figure 69. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint                      |   |

| Figure 70. | LQFP64 marking example (package top view)128                                                 |   |

| Figure 71. | LQFP100 P <sub>D</sub> max vs. T <sub>A</sub>                                                | 1 |

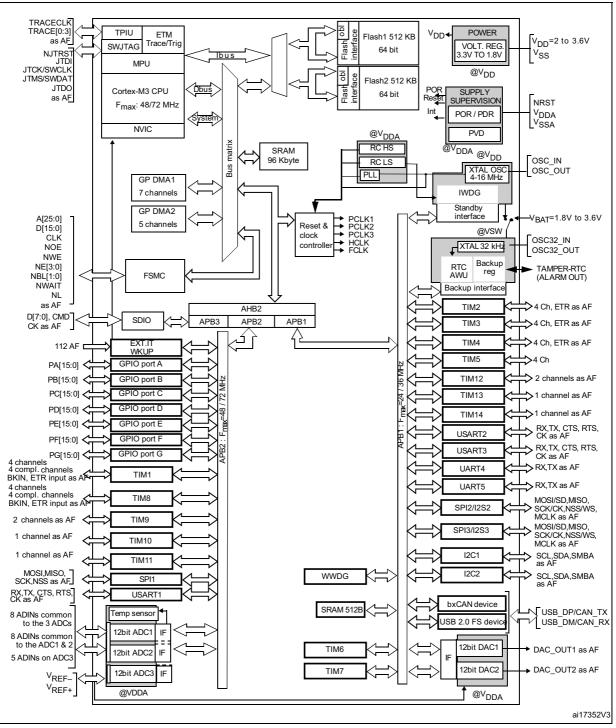

Figure 1. STM32F103xF and STM32F103xG performance line block diagram

T<sub>A</sub> = -40 °C to +85 °C (suffix 6, see *Table 73*) or -40 °C to +105 °C (suffix 7, see *Table 73*), junction temperature up to 105 °C or 125 °C, respectively.

2. AF = alternate function on I/O port pin.9

# 2.3.10 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-16 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example with failure of an indirectly used external oscillator).

Several prescalers allow the configuration of the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the high speed APB domains is 72 MHz. The maximum allowed frequency of the low speed APB domain is 36 MHz. See *Figure 2* for details on the clock tree.

## 2.3.11 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from user Flash: you have an option to boot from any of two memory banks. By default, boot from Flash memory bank 1 is selected. You can choose to boot from Flash memory bank 2 by setting a bit in the option bytes.

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1.

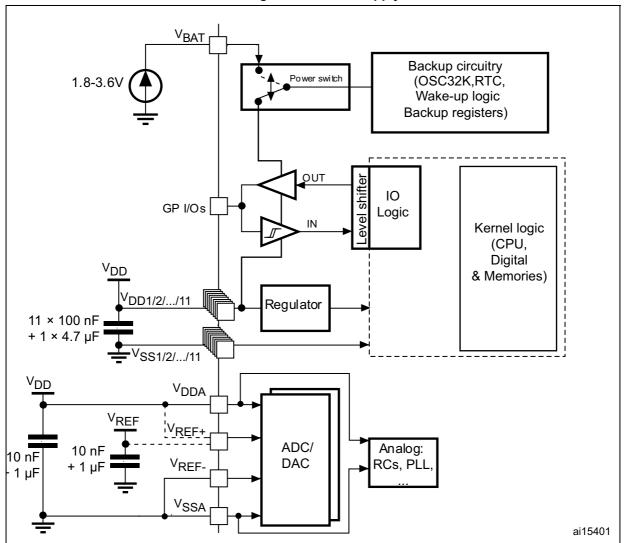

# 2.3.12 Power supply schemes

- V<sub>DD</sub> = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 2.0 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to VDDA is 2.4 V when the ADC or DAC is used). V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to Figure 10: Power supply scheme.

## 2.3.13 Power supply supervisor

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software. Refer to *Table 12: Embedded reset and power control block characteristics* for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, general-purpose, basic and advanced-control timers TIMx, DAC, I<sup>2</sup>S, SDIO and ADC.

# 2.3.17 RTC (real-time clock) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are forty-two 16-bit registers used to store 84 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset, and they are not reset when the device wakes up from the Standby mode.

The real-time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and a periodic interrupt. It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-speed RC has a typical frequency of 40 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation. The RTC features a 32-bit programmable counter for long term measurement using the Compare register to generate an alarm. A 20-bit prescaler is used for the time base clock and is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

## 2.3.18 Timers and watchdogs

The XL-density STM32F103xF/G performance line devices include up to two advancedcontrol timers, up to ten general-purpose timers, two basic timers, two watchdog timers and a SysTick timer.

*Table 4* compares the features of the advanced-control, general-purpose and basic timers.

| Timer                        | Counter resolution | Counter<br>type         | Prescaler factor                   | DMA request generation | Capture/compare<br>channels | Complementary<br>outputs |

|------------------------------|--------------------|-------------------------|------------------------------------|------------------------|-----------------------------|--------------------------|

| TIM1, TIM8                   | 16-bit             | Up,<br>down,<br>up/down | Any integer between<br>1 and 65536 | Yes                    | 4                           | Yes                      |

| TIM2, TIM3,<br>TIM4, TIM5    | 16-bit             | Up,<br>down,<br>up/down | Any integer between<br>1 and 65536 | Yes                    | 4                           | No                       |

| TIM9, TIM12                  | 16-bit             | Up                      | Any integer between<br>1 and 65536 | No                     | 2                           | No                       |

| TIM10, TIM11<br>TIM13, TIM14 | 16-bit             | Up                      | Any integer between<br>1 and 65536 | No                     | 1                           | No                       |

| TIM6, TIM7                   | 16-bit             | Up                      | Any integer between<br>1 and 65536 | Yes                    | 0                           | No                       |

Table 4. STM32F103xF and STM32F103xG timer feature comparison

- 4. If several peripherals share the same I/O pin, to avoid conflict between these alternate functions only one peripheral should be enabled at a time through the peripheral clock enable bit (in the corresponding RCC peripheral clock enable register).

- PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these IOs must not be used as a current source (e.g. to drive an LED).

- 6. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

- 7. For the LQFP64 package, the pins number 5 and 6 are configured as OSC\_IN/OSC\_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For the LQFP100 and LQFP144/BGA144 packages, PD0 and PD1 are available by default, so there is no need for remapping. For more details, refer to Alternate function I/O and debug configuration section in the STM32F10xxx reference manual.

- This alternate function can be remapped by software to some other port pins (if available on the used package). For more

details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual,

available from the STMicroelectronics website: www.st.com.

- 9. For devices delivered in LQFP64 packages, the FSMC function is not available.

# 5.1.6 Power supply scheme

Figure 10. Power supply scheme

Caution: In Figure 10, the 4.7 µF capacitor must be connected to V<sub>DD3</sub>.

| Symbol | Parameter         | Conditions                          | £      | Ма                     | Unit                    |      |

|--------|-------------------|-------------------------------------|--------|------------------------|-------------------------|------|

| Symbol | Falailletei       | Conditions                          | fhclk  | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Onit |

|        |                   |                                     | 72 MHz | 68                     | 69                      |      |

|        |                   |                                     | 48 MHz | 51                     | 51                      |      |

|        |                   | External clock <sup>(2)</sup> , all | 36 MHz | 41                     | 41                      |      |

|        |                   | peripherals enabled                 | 24 MHz | 29                     | 30                      | -    |

|        |                   |                                     | 16 MHz | 22                     | 22.5                    |      |

|        | Supply current in |                                     | 8 MHz  | 12.5                   | 14                      | mA   |

| IDD    | Run mode          |                                     | 72 MHz | 39                     | 39                      | IIIA |

|        |                   |                                     | 48 MHz | 29.5                   | 30                      |      |

|        |                   | External clock <sup>(2)</sup> , all | 36 MHz | 24                     | 24.5                    | -    |

|        |                   | peripherals disabled                | 24 MHz | 17.5                   | 19                      |      |

|        |                   |                                     | 16 MHz | 14                     | 15                      |      |

|        |                   |                                     | 8 MHz  | 8.5                    | 10.5                    |      |

# Table 14. Maximum current consumption in Run mode, code with data processingrunning from Flash

1. Guaranteed by characterization results, not tested in production.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

| Symbol   | Parameter      | Conditions                                               | £                 | Ма                     | Unit                    |      |

|----------|----------------|----------------------------------------------------------|-------------------|------------------------|-------------------------|------|

| Symbol   | Farameter      | Conditions                                               | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|          |                |                                                          | 72 MHz            | 65                     | 65.5                    |      |

|          |                |                                                          | 48 MHz            | 46.5                   | 47                      |      |

|          |                | External clock <sup>(2)</sup> , all                      | 36 MHz            | 37                     | 37                      |      |

| , Supply |                | peripherals enabled                                      | 24 MHz            | 26.5                   | 27                      |      |

|          |                |                                                          | 16 MHz            | 19                     | 20                      |      |

|          | Supply current |                                                          | 8 MHz             | 11.5                   | 13                      | mA   |

| IDD      | in Run mode    | External clock <sup>(2)</sup> , all peripherals disabled | 72 MHz            | 34.5                   | 36                      | mA   |

|          |                |                                                          | 48 MHz            | 25                     | 26                      |      |

|          |                |                                                          | 36 MHz            | 20.5                   | 21                      |      |

|          |                |                                                          | 24 MHz            | 15                     | 16                      |      |

|          |                |                                                          | 16 MHz            | 11                     | 13                      | 1    |

|          |                |                                                          | 8 MHz             | 7.5                    | 9                       | 1    |

# Table 15. Maximum current consumption in Run mode, code with data processing running from RAM

1. Guaranteed by characterization results, not tested in production at  $V_{\text{DD}}$  max,  $f_{\text{HCLK}}$  max.

2. External clock is 8 MHz and PLL is on when  $f_{\text{HCLK}}$  > 8 MHz.

|                 |                   |                                   |                              | Туј  | Тур <sup>(1)</sup>                                             |      |  |       |     |     |  |

|-----------------|-------------------|-----------------------------------|------------------------------|------|----------------------------------------------------------------|------|--|-------|-----|-----|--|

| Symbol          | Parameter         | Conditions                        | Conditions f <sub>HCLK</sub> |      | ons f <sub>HCLK</sub> All peripherals All peripherals disabled |      |  | Unit  |     |     |  |

|                 |                   |                                   | 72 MHz                       | 32.5 | 7                                                              |      |  |       |     |     |  |

|                 |                   |                                   | 48 MHz                       | 23   | 5                                                              |      |  |       |     |     |  |

|                 |                   |                                   | 36 MHz                       | 17.7 | 4                                                              |      |  |       |     |     |  |

|                 |                   |                                   | 24 MHz                       | 12.2 | 3.1                                                            |      |  |       |     |     |  |

|                 |                   |                                   | 16 MHz                       | 8.4  | 2.3                                                            |      |  |       |     |     |  |

|                 |                   | External clock <sup>(3)</sup>     | 8 MHz                        | 4.6  | 1.5                                                            |      |  |       |     |     |  |

|                 |                   |                                   | 4 MHz                        | 3    | 1.3                                                            |      |  |       |     |     |  |

|                 |                   |                                   | 2 MHz                        | 2.15 | 1.25                                                           |      |  |       |     |     |  |

|                 |                   |                                   |                              |      |                                                                |      |  | 1 MHz | 1.7 | 1.2 |  |

|                 |                   |                                   | 500 kHz 1.5                  | 1.15 |                                                                |      |  |       |     |     |  |

|                 | Supply current in |                                   | 125 kHz                      | 1.35 | 1.15                                                           | mA   |  |       |     |     |  |

| I <sub>DD</sub> | Sleep mode        | Running on high speed internal RC | 64 MHz                       | 28.7 | 5.7                                                            | IIIA |  |       |     |     |  |

|                 |                   |                                   | 48 MHz                       | 22   | 4.4                                                            |      |  |       |     |     |  |

|                 |                   |                                   | 36 MHz                       | 17   | 3.35                                                           |      |  |       |     |     |  |

|                 |                   |                                   | 24 MHz                       | 11.6 | 2.3                                                            |      |  |       |     |     |  |

|                 |                   |                                   | 16 MHz                       | 7.7  | 1.6                                                            |      |  |       |     |     |  |

|                 |                   | (HSI), AHB prescaler              | 8 MHz                        | 3.9  | 0.8                                                            |      |  |       |     |     |  |

|                 |                   | used to reduce the<br>frequency   | 4 MHz                        | 2.3  | 0.7                                                            |      |  |       |     |     |  |

|                 |                   |                                   | 2 MHz                        | 1.5  | 0.6                                                            |      |  |       |     |     |  |

|                 |                   |                                   | 1 MHz                        | 1.1  | 0.5                                                            |      |  |       |     |     |  |

|                 |                   |                                   | 500 kHz                      | 0.9  | 0.5                                                            |      |  |       |     |     |  |

|                 |                   |                                   | 125 kHz                      | 0.7  | 0.5                                                            |      |  |       |     |     |  |

Table 19. Typical current consumption in Sleep mode, code running from Flash or RAM

1. Typical values are measures at T\_A = 25 °C, V\_{DD} = 3.3 V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

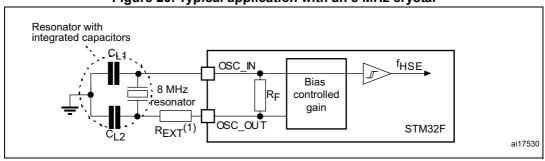

### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 23*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol              | Parameter                                                                                     | Parameter Conditions                                                          |    | Тур | Max | Unit |

|---------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----|-----|-----|------|

| f <sub>OSC_IN</sub> | Oscillator frequency                                                                          | -                                                                             | 4  | 8   | 16  | MHz  |

| R <sub>F</sub>      | Feedback resistor                                                                             | -                                                                             | -  | 200 | -   | kΩ   |

| С                   | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 Ω                                                         | -  | 30  | -   | pF   |

| i <sub>2</sub>      | HSE driving current                                                                           | V <sub>DD</sub> = 3.3 V, V <sub>IN</sub> = V <sub>SS</sub><br>with 30 pF load | -  | -   | 1   | mA   |

| 9 <sub>m</sub>      | Oscillator transconductance                                                                   | Startup                                                                       | 25 | -   | -   | mA/V |

| $t_{SU(HSE)}^{(4)}$ | Startup time                                                                                  | $V_{DD}$ is stabilized                                                        | -  | 2   | -   | ms   |

| Table 23. HSE 4-16 MHz oscillator chara | cteristics <sup>(1)(2)</sup> |

|-----------------------------------------|------------------------------|

|-----------------------------------------|------------------------------|

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by characterization results, not tested in production.

3. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

4. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 20*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

Figure 20. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

1. C<sub>L</sub> = 15 pF.

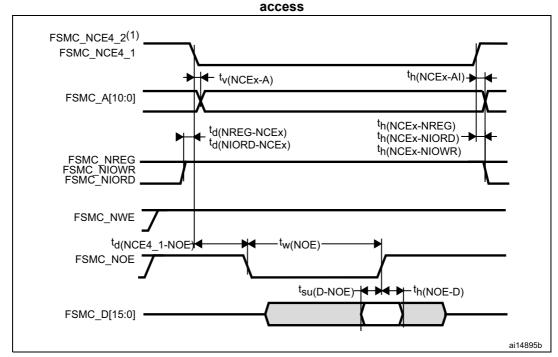

#### PC Card/CompactFlash controller waveforms and timings

*Figure 30* through *Figure 35* represent synchronous waveforms and *Table 42* provides the corresponding timings. The results shown in this table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x04;

- COM.FSMC\_WaitSetupTime = 0x07;

- COM.FSMC\_HoldSetupTime = 0x04;

- COM.FSMC\_HiZSetupTime = 0x00;

- ATT.FSMC\_SetupTime = 0x04;

- ATT.FSMC\_WaitSetupTime = 0x07;

- ATT.FSMC\_HoldSetupTime = 0x04;

- ATT.FSMC\_HiZSetupTime = 0x00;

- IO.FSMC\_SetupTime = 0x04;

- IO.FSMC WaitSetupTime = 0x07;

- IO.FSMC\_HoldSetupTime = 0x04;

- IO.FSMC\_HiZSetupTime = 0x00;

- TCLRSetupTime = 0;

- TARSetupTime = 0;

## Figure 30. PC Card/CompactFlash controller waveforms for common memory read

#### 1. FSMC\_NCE4\_2 remains high (inactive during 8-bit access.

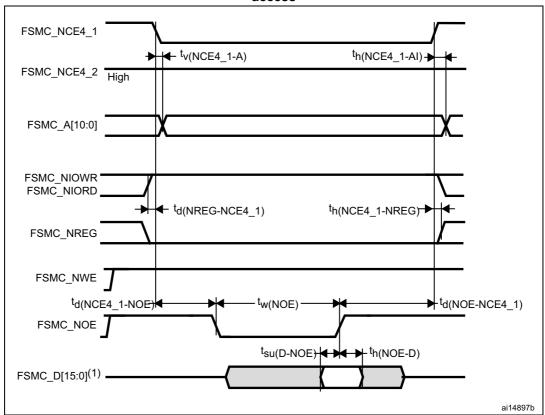

Figure 32. PC Card/CompactFlash controller waveforms for attribute memory read access

1. Only data bits 0...7 are read (bits 8...15 are disregarded).

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 44* and *Table 51*, respectively.

Unless otherwise specified, the parameters given in *Table 51* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| MODEx[1:0]<br>bit value <sup>(1)</sup> | Symbol                  | Parameter                                                             | Conditions                                                                | Min | Max                | Unit |

|----------------------------------------|-------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------|-----|--------------------|------|

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V                                  | -   | 2                  | MHz  |

| 10                                     | t <sub>f(IO)out</sub>   | Output high to low<br>level fall time                                 | C <sub>1</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V                    | -   | 125 <sup>(3)</sup> | ns   |

|                                        | t <sub>r(IO)out</sub>   | Output low to high<br>level rise time                                 | CL - 30 μι, νDD - 2 ν 10 3.0 ν                                            | -   | 125 <sup>(3)</sup> | 115  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V                                  | -   | 10                 | MHz  |

| 01                                     | t <sub>f(IO)out</sub>   | Output high to low<br>level fall time                                 | C <sub>1</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V                    | -   | 25 <sup>(3)</sup>  | nc   |

|                                        | t <sub>r(IO)out</sub>   | Output low to high<br>level rise time                                 | $V_{\rm L} = 50  \text{pr},  v_{\rm DD} = 2  \text{v}  10  3.0  \text{v}$ |     | 25 <sup>(3)</sup>  | ns   |

|                                        |                         | Maximum frequency <sup>(2)</sup>                                      | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                                  | -   | 50                 | MHz  |

|                                        | F <sub>max(IO)out</sub> |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                                | -   | 30                 | MHz  |

|                                        |                         |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                                  |     | 20                 | MHz  |

|                                        |                         |                                                                       | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                                  | -   | 5 <sup>(3)</sup>   |      |

| 11                                     | t <sub>f(IO)out</sub>   | Output high to low<br>level fall time                                 | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                                  | -   | 8 <sup>(3)</sup>   |      |

|                                        |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                                    | -   | 12 <sup>(3)</sup>  | ns   |

|                                        |                         |                                                                       | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                                  | -   | 5 <sup>(3)</sup>   | 115  |

|                                        | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                                  | -   | 8 <sup>(3)</sup>   |      |

|                                        |                         |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                                  |     | 12 <sup>(3)</sup>  |      |

| -                                      | t <sub>EXTIpw</sub>     | Pulse width of external<br>signals detected by<br>the EXTI controller | -                                                                         | 10  | -                  | ns   |

Table 51. I/O AC characteristics<sup>(1)</sup>

1. The I/O speed is configured using the MODEx[1:0] bits. Refer to the STM32F10xxx reference manual for a description of GPIO Port configuration register.

2. The maximum frequency is defined in Figure 44.

3. Guaranteed by design, not tested in production.

- 1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

- 2. Rs: Series protection resistors.

- 3. Rp: Pull-up resistors.

- 4. VDD\_I2C : I2C bus supply

| f <sub>SCL</sub> (kHz) | I2C_CCR value                  |

|------------------------|--------------------------------|

|                        | <b>R<sub>P</sub> = 4.7 k</b> Ω |

| 400                    | 0x801E                         |

| 300                    | 0x8028                         |

| 200                    | 0x803C                         |

| 100                    | 0x00B4                         |

| 50                     | 0x0168                         |

| 20                     | 0x0384                         |

# Table 55. SCL frequency (f<sub>PCLK1</sub>= 36 MHz.,V<sub>DD I2C</sub> = 3.3 V)<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  = I<sup>2</sup>C speed.

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

# 5.3.20 DAC electrical specifications

| Symbol                                         | Parameter                                                         | Min | Тур | Мах                          | Unit | Comments                                                                                                                                       |

|------------------------------------------------|-------------------------------------------------------------------|-----|-----|------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                               | Analog supply voltage                                             | 2.4 | -   | 3.6                          | V    |                                                                                                                                                |

| V <sub>REF+</sub>                              | Reference supply voltage                                          | 2.4 | -   | 3.6                          | V    | V <sub>REF+</sub> must always be below V <sub>DDA</sub>                                                                                        |

| V <sub>SSA</sub>                               | Ground                                                            | 0   | -   | 0                            | V    |                                                                                                                                                |

| р (1)                                          | Resistive load vs. V <sub>SSA</sub> with<br>buffer ON             | 5   | -   | -                            | kΩ   |                                                                                                                                                |

| R <sub>LOAD</sub> <sup>(1)</sup>               | Resistive load vs. V <sub>DDA</sub> with<br>buffer ON             | 15  | -   | -                            | kΩ   |                                                                                                                                                |

| R <sub>O</sub> <sup>(1)</sup>                  | Impedance output with buffer<br>OFF                               | -   | -   | 15                           | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 $M\Omega$                         |

| C <sub>LOAD</sub> <sup>(1)</sup>               | Capacitive load                                                   | -   | -   | 50                           | pF   | Maximum capacitive load at<br>DAC_OUT pin (when the buffer is<br>ON).                                                                          |

| DAC_OUT<br>min <sup>(1)</sup>                  | Lower DAC_OUT voltage<br>with buffer ON                           | 0.2 | -   | -                            | v    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input code<br>(0x0E0) to (0xF1C) at V <sub>REF+</sub> = 3.6 V |

| DAC_OUT<br>max <sup>(1)</sup>                  | Higher DAC_OUT voltage with buffer ON                             | -   | -   | V <sub>DDA</sub> – 0.2       | V    | and (0x155) and (0xEAB) at $V_{REF+} = 3.0 \text{ V}$<br>2.4 V                                                                                 |

| DAC_OUT<br>min <sup>(1)</sup>                  | Lower DAC_OUT voltage with buffer OFF                             | -   | 0.5 |                              | mV   | It gives the maximum output                                                                                                                    |

| DAC_ <sup>(1)</sup> OU<br>T max <sup>(1)</sup> | Higher DAC_OUT voltage with buffer OFF                            | -   |     | V <sub>REF+</sub> –<br>10 mV | V    | excursion of the DAC.                                                                                                                          |

| I <sub>DDVREF+</sub>                           | DAC DC current<br>consumption in quiescent<br>mode (Standby mode) | -   |     | 380                          |      | With no load, worst code (0x0E4) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs                                   |

|                                                | DAC DC current                                                    | -   |     | 380                          | μA   | With no load, middle code (0x800) on the inputs                                                                                                |

| I <sub>DDA</sub>                               | consumption in quiescent<br>mode <sup>(2)</sup>                   | -   |     | 480                          | μA   | With no load, worst code (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs                                   |

| DNL <sup>(3)</sup>                             | Differential non linearity<br>Difference between two              | -   |     | ±0.5                         | LSB  | Given for the DAC in 10-bit configuration                                                                                                      |

|                                                | consecutive code-1LSB)                                            | -   |     | ±3                           | LSB  | Given for the DAC in 12-bit configuration                                                                                                      |

#### Table 66. DAC characteristics

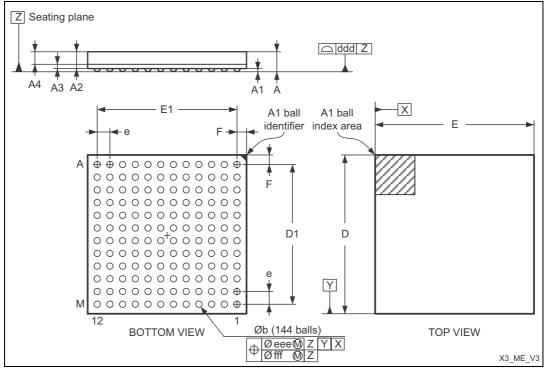

# 6.1 LFBGA144 package information

Figure 60. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package outline

1. Drawing is not to scale.

| Table 68. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, |

|-----------------------------------------------------------------------------------|

| 0.8 mm pitch, package mechanical data                                             |

| Symbol           | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|------------------|-------------|--------|--------|-----------------------|--------|--------|

|                  | Min         | Тур    | Max    | Тур                   | Min    | Max    |

| A <sup>(2)</sup> | -           | -      | 1.700  |                       |        | 0.0669 |

| A1               | 0.210       | -      | -      | 0.0083                |        |        |

| A2               | -           | 1.060  | -      |                       | 0.0417 |        |

| A3               |             | 0.026  |        |                       | 0.0010 |        |

| A4               | -           | 0.800  | -      | -                     | 0.0315 | -      |

| b                | 0.350       | 0.400  | 0.450  | 0.0138                | 0.0157 | 0.0177 |

| D                | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |

| D1               | -           | 8.800  | -      | -                     | 0.3465 | -      |

| E                | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |

| E1               | -           | 8.800  | -      | -                     | 0.3465 | -      |

| е                | -           | 0.800  | -      | -                     | 0.0315 | -      |

| F                | -           | 0.600  | -      | -                     | 0.0236 | -      |

| ddd              | -           | -      | 0.100  | -                     | -      | 0.0039 |

# 6.2 LQFP144 package information

Figure 62. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline

1. Drawing is not to scale.

# 6.3 LQFP100 package information

Figure 65. LFP100 – 14 x 14 mm 100 pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 70. LQPF100 – 14 x 14 mm 100-pin low-profile quad flat package |

|----------------------------------------------------------------------|

| mechanical data                                                      |

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах    | Min                   | Тур    | Мах    |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| D3     | -           | 12.000 | -      | -                     | 0.4724 | -      |

| Е      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| E3     | -           | 12.000 | -      | -                     | 0.4724 | -      |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| E3     | -           | 7.500 | -     | -                     | 0.2953 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| θ      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| ссс    | -           | -     | 0.080 | -                     | -      | 0.0031 |

### Table 71. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.