#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 112                                                                   |

| Program Memory Size        | 1MB (1M x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 96K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 21x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 144-LQFP                                                              |

| Supplier Device Package    | 144-LQFP (20x20)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103zgt6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.3.5 Embedded SRAM

96 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

## 2.3.6 FSMC (flexible static memory controller)

The FSMC is embedded in the STM32F103xF and STM32F103xG performance line family. It has four Chip Select outputs supporting the following modes: PC Card/Compact Flash, SRAM, PSRAM, NOR and NAND.

Functionality overview:

- The three FSMC interrupt lines are ORed in order to be connected to the NVIC

- Write FIFO

- Code execution from external memory except for NAND Flash and PC Card

- The targeted frequency, f<sub>CLK</sub>, is HCLK/2, so external access is at 36 MHz when HCLK is at 72 MHz and external access is at 24 MHz when HCLK is at 48 MHz

## 2.3.7 LCD parallel interface

The FSMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost-effective graphic applications using LCD modules with embedded controllers or high-performance solutions using external controllers with dedicated acceleration.

## 2.3.8 Nested vectored interrupt controller (NVIC)

The STM32F103xF and STM32F103xG performance line embeds a nested vectored interrupt controller able to handle up to 60 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>®</sup>-M3) and 16 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of *late arriving* higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 2.3.9 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 19 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 112 GPIOs can be connected to the 16 external interrupt lines.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, general-purpose, basic and advanced-control timers TIMx, DAC, I<sup>2</sup>S, SDIO and ADC.

#### 2.3.17 RTC (real-time clock) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are forty-two 16-bit registers used to store 84 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset, and they are not reset when the device wakes up from the Standby mode.

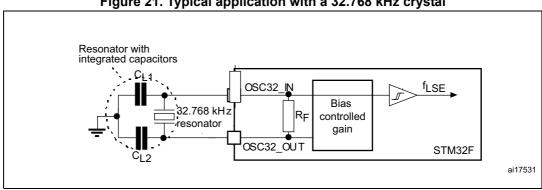

The real-time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and a periodic interrupt. It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-speed RC has a typical frequency of 40 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation. The RTC features a 32-bit programmable counter for long term measurement using the Compare register to generate an alarm. A 20-bit prescaler is used for the time base clock and is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

#### 2.3.18 Timers and watchdogs

The XL-density STM32F103xF/G performance line devices include up to two advancedcontrol timers, up to ten general-purpose timers, two basic timers, two watchdog timers and a SysTick timer.

*Table 4* compares the features of the advanced-control, general-purpose and basic timers.

| Timer                        | Counter resolution | Counter<br>type         | Prescaler factor                   | DMA request generation | Capture/compare<br>channels | Complementary<br>outputs |

|------------------------------|--------------------|-------------------------|------------------------------------|------------------------|-----------------------------|--------------------------|

| TIM1, TIM8                   | 16-bit             | Up,<br>down,<br>up/down | Any integer between<br>1 and 65536 | Yes                    | 4                           | Yes                      |

| TIM2, TIM3,<br>TIM4, TIM5    | 16-bit             | Up,<br>down,<br>up/down | Any integer between Yes 4          |                        | 4                           | No                       |

| TIM9, TIM12                  | 16-bit             | Up                      | Any integer between<br>1 and 65536 | No                     | 2                           | No                       |

| TIM10, TIM11<br>TIM13, TIM14 | 16-bit             | Up                      | Any integer between<br>1 and 65536 | No                     | 1                           | No                       |

| TIM6, TIM7                   | 16-bit             | Up                      | Any integer between<br>1 and 65536 | Yes                    | 0                           | No                       |

Table 4. STM32F103xF and STM32F103xG timer feature comparison

#### 2.3.29 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 2 V <  $V_{DDA}$  < 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

## 2.3.30 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

#### 2.3.31 Embedded Trace Macrocell™

The ARM<sup>®</sup> Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F10xxx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

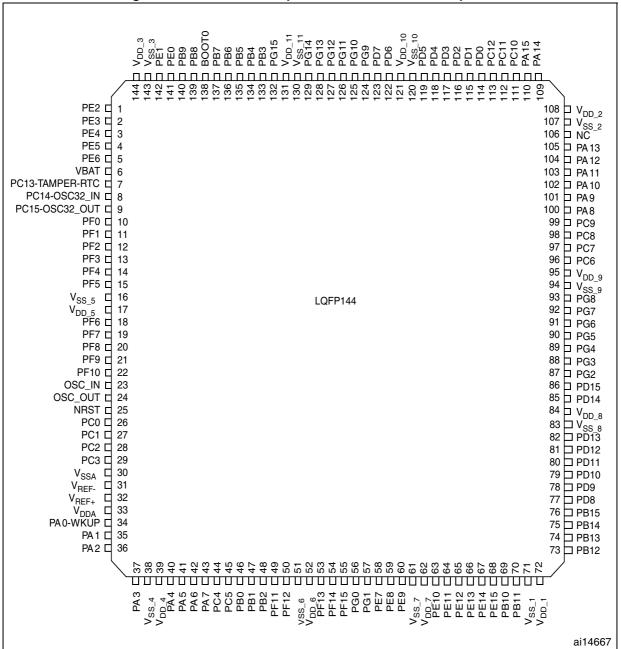

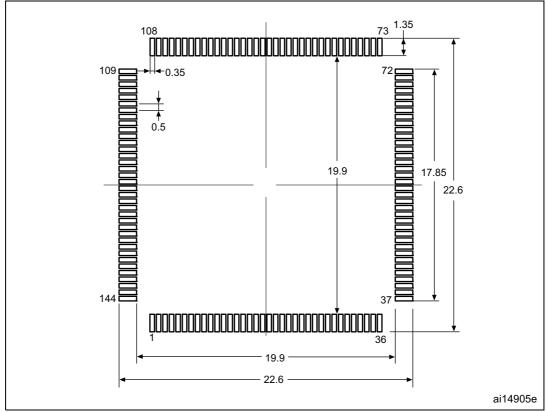

Figure 4. STM32F103xF/G performance line LQFP144 pinout

1. The above figure shows the package top view.

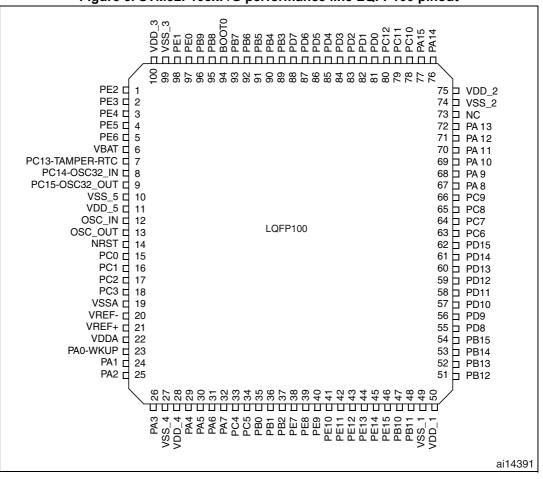

#### Figure 5. STM32F103xF/G performance line LQFP100 pinout

1. The above figure shows the package top view.

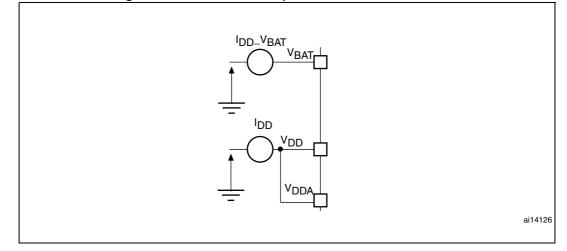

## 5.1.7 Current consumption measurement

#### Figure 11. Current consumption measurement scheme

| Symbol                                     | Parameter                                              | Conditions                       | Min         | Тур | Max             | Unit |  |  |

|--------------------------------------------|--------------------------------------------------------|----------------------------------|-------------|-----|-----------------|------|--|--|

| f <sub>HSE_ext</sub>                       | User external clock source<br>frequency <sup>(1)</sup> |                                  | 1           | 8   | 25              | MHz  |  |  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                    |                                  | $0.7V_{DD}$ | -   | V <sub>DD</sub> | V    |  |  |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                     | _                                | $V_{SS}$    | -   | $0.3V_{DD}$     | v    |  |  |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>                 |                                  | 5           | -   | -               | ns   |  |  |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>                |                                  | -           | -   | 20              | 115  |  |  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>                | -                                | -           | 5   | -               | pF   |  |  |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                                             | -                                | 45          | -   | 55              | %    |  |  |

| ١ <sub>L</sub>                             | OSC_IN Input leakage current                           | $V_{SS}{\leq}V_{IN}{\leq}V_{DD}$ | -           | -   | ±1              | μA   |  |  |

Table 21. High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

#### Low-speed external user clock generated from an external source

The characteristics given in *Table 22* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 10*.

| Symbol                                     | Parameter                                              | Conditions                  | Min                | Тур    | Мах                | Unit |

|--------------------------------------------|--------------------------------------------------------|-----------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                             | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                             | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   | -                           | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                             | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                             | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              | -                           | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             | -                           | 30                 | -      | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage current                         | $V_{SS} \le V_{IN} \le V_D$ | -                  | -      | ±1                 | μA   |

Table 22. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

Figure 21. Typical application with a 32.768 kHz crystal

#### 5.3.7 Internal clock source characteristics

The parameters given in Table 25 are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 10*.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                        | Conditions                            |                                | Min  | Тур | Max              | Unit |

|-------------------------------------|----------------------------------|---------------------------------------|--------------------------------|------|-----|------------------|------|

| f <sub>HSI</sub>                    | Frequency                        | -                                     |                                | -    | 8   |                  | MHz  |

| DuCy <sub>(HSI)</sub>               | Duty cycle                       | -                                     |                                | 45   | -   | 55               | %    |

|                                     |                                  | User-trimmed register <sup>(2)</sup>  | with the RCC_CR                | -    | -   | 1 <sup>(3)</sup> | %    |

|                                     | Accuracy of the HSI oscillator   | Factory-<br>calibrated <sup>(4)</sup> | T <sub>A</sub> = -40 to 105 °C | -2   | -   | 2.5              | %    |

| ACC <sub>HSI</sub>                  |                                  |                                       | T <sub>A</sub> = −10 to 85 °C  | -1.5 | -   | 2.2              | %    |

|                                     |                                  |                                       | T <sub>A</sub> = 0 to 70 °C    | -1.3 | -   | 2                | %    |

|                                     |                                  |                                       | T <sub>A</sub> = 25 °C         | -1.1 | -   | 1.8              | %    |

| t <sub>su(HSI)</sub> <sup>(4)</sup> | HSI oscillator<br>startup time   | -                                     |                                | 1    | -   | 2                | μs   |

| I <sub>DD(HSI)</sub> <sup>(4)</sup> | HSI oscillator power consumption | -                                     |                                | -    | 80  | 100              | μA   |

Table 25. HSI oscillator characteristics<sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V, T<sub>A</sub> = -40 to 105 °C unless otherwise specified.

Refer to application note AN2868 "STM32F10xxx internal RC oscillator (HSI) calibration" available from 2. the ST website www.st.com.

3. Guaranteed by design, not tested in production.

4. Guaranteed by characterization results, not tested in production.

| Symbol                       | Parameter                                         | Min  | Max | Unit |

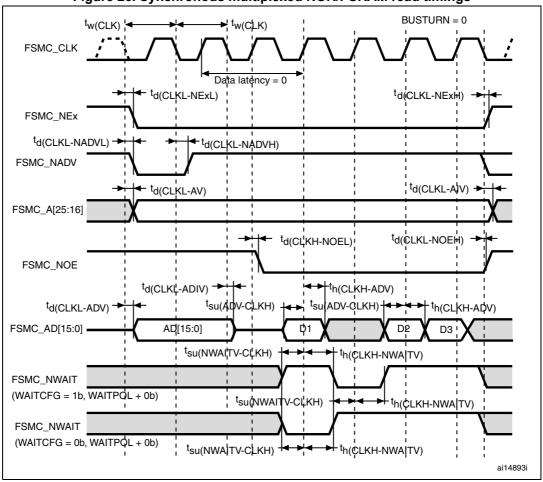

|------------------------------|---------------------------------------------------|------|-----|------|

| t <sub>w(CLK)</sub>          | FSMC_CLK period                                   | 27.6 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>    | FSMC_CLK low to FSMC_NEx low (x = 02)             | -    | 0.5 | ns   |

| t <sub>d(CLKL-NExH)</sub>    | FSMC_CLK low to FSMC_NEx high (x = 02)            | 1    | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>   | FSMC_CLK low to FSMC_NADV low                     | -    | 1   | ns   |

| t <sub>d(CLKL-NADVH)</sub>   | FSMC_CLK low to FSMC_NADV high                    | 0.5  | -   | ns   |

| t <sub>d(CLKL-AV)</sub>      | FSMC_CLK low to FSMC_Ax valid (x = 1625)          | -    | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>     | FSMC_CLK low to FSMC_Ax invalid (x = 1625)        | 1.5  | -   | ns   |

| t <sub>d(CLKL-NOEL)</sub>    | FSMC_CLK low to FSMC_NOE low                      | -    | 14  | ns   |

| t <sub>d(CLKL-NOEH)</sub>    | FSMC_CLK low to FSMC_NOE high                     | 1    | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>     | FSMC_CLK low to FSMC_AD[15:0] valid               | -    | 11  | ns   |

| t <sub>d(CLKL-ADIV)</sub>    | FSMC_CLK low to FSMC_AD[15:0] invalid             | 0.5  | -   | ns   |

| t <sub>su(ADV-CLKH)</sub>    | FSMC_A/D[15:0] valid data before FSMC_CLK<br>high | 2    | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>     | FSMC_A/D[15:0] valid data after FSMC_CLK high     | 0    | -   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high             | 8    | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high              | 2    | -   | ns   |

Table 36. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)</sup>

1. C<sub>L</sub> = 15 pF.

1. C<sub>L</sub> = 15 pF.

#### PC Card/CompactFlash controller waveforms and timings

*Figure 30* through *Figure 35* represent synchronous waveforms and *Table 42* provides the corresponding timings. The results shown in this table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x04;

- COM.FSMC\_WaitSetupTime = 0x07;

- COM.FSMC\_HoldSetupTime = 0x04;

- COM.FSMC\_HiZSetupTime = 0x00;

- ATT.FSMC\_SetupTime = 0x04;

- ATT.FSMC\_WaitSetupTime = 0x07;

- ATT.FSMC\_HoldSetupTime = 0x04;

- ATT.FSMC\_HiZSetupTime = 0x00;

- IO.FSMC\_SetupTime = 0x04;

- IO.FSMC WaitSetupTime = 0x07;

- IO.FSMC\_HoldSetupTime = 0x04;

- IO.FSMC\_HiZSetupTime = 0x00;

- TCLRSetupTime = 0;

- TARSetupTime = 0;

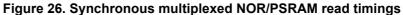

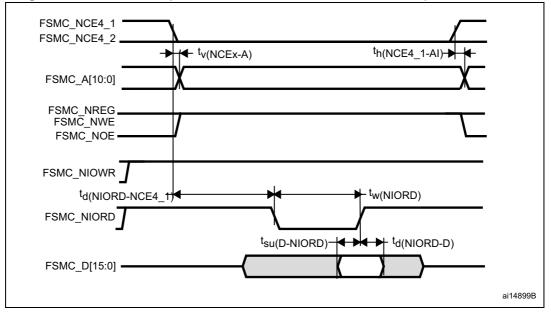

#### Figure 30. PC Card/CompactFlash controller waveforms for common memory read

#### 1. FSMC\_NCE4\_2 remains high (inactive during 8-bit access.

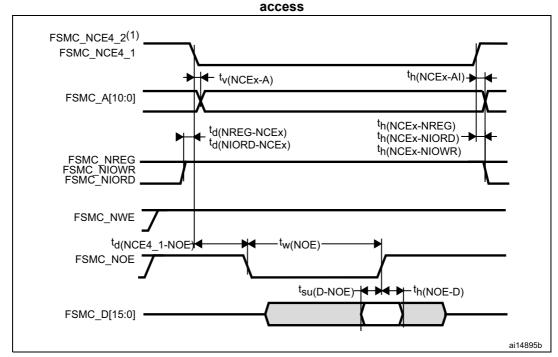

Figure 33. PC Card/CompactFlash controller waveforms for attribute memory write access

1. Only data bits 0...7 are driven (bits 8...15 remains HiZ).

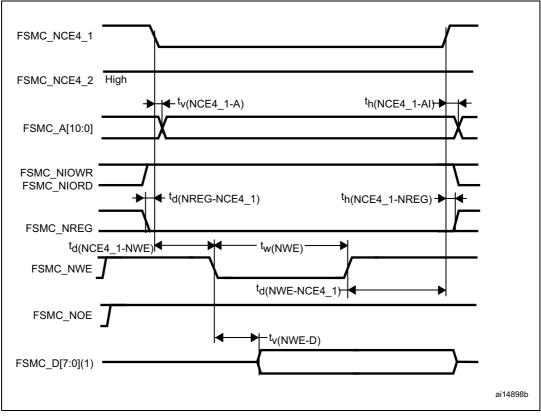

#### Figure 34. PC Card/CompactFlash controller waveforms for I/O space read access

| Symbol                       | Parameter                                 | Min              | Мах             | Unit |

|------------------------------|-------------------------------------------|------------------|-----------------|------|

| tw <sub>(NIOWR)</sub>        | FSMC_NIOWR low width                      | 8 THCLK          | -               | ns   |

| tv <sub>(NIOWR-D)</sub>      | FSMC_NIOWR low to FSMC_D[15:0] valid      | -                | 5 THCLK -<br>4  | ns   |

| th <sub>(NIOWR-D)</sub>      | FSMC_NIOWR high to FSMC_D[15:0] invalid   | 11THCLK-<br>7    | -               | ns   |

| td <sub>(NCE4_1-NIOWR)</sub> | FSMC_NCE4_1 low to FSMC_NIOWR valid       | -                | 5THCLK +<br>1   | ns   |

| th <sub>(NCEx-NIOWR)</sub>   | FSMC_NCEx high to FSMC_NIOWR invalid      | 5THCLK -<br>2.5  | -               | ns   |

| td <sub>(NIORD-NCEx)</sub>   | FSMC_NCEx low to FSMC_NIORD valid         | -                | 5THCLK -<br>0.5 | ns   |

| th <sub>(NCEx-NIORD)</sub>   | FSMC_NCEx high to FSMC_NIORD) valid       | 5 THCLK -<br>0.5 | -               | ns   |

| tw <sub>(NIORD)</sub>        | FSMC_NIORD low width                      | 8THCLK           | -               | ns   |

| tsu <sub>(D-NIORD)</sub>     | FSMC_D[15:0] valid before FSMC_NIORD high | 28               | -               | ns   |

| td <sub>(NIORD-D)</sub>      | FSMC_D[15:0] valid after FSMC_NIORD high  | 3                | -               | ns   |

Table 41. Switching characteristics for PC Card/CF read and write cycles in I/O space

#### NAND controller waveforms and timings

*Figure 36* through *Figure 39* represent synchronous waveforms and *Table 43* provides the corresponding timings. The results shown in this table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x00;

- COM.FSMC\_WaitSetupTime = 0x02;

- COM.FSMC\_HoldSetupTime = 0x01;

- COM.FSMC\_HiZSetupTime = 0x00;

- ATT.FSMC\_SetupTime = 0x00;

- ATT.FSMC\_WaitSetupTime = 0x02;

- ATT.FSMC\_HoldSetupTime = 0x01;

- ATT.FSMC\_HiZSetupTime = 0x00;

- Bank = FSMC\_Bank\_NAND;

- MemoryDataWidth = FSMC\_MemoryDataWidth\_16b;

- ECC = FSMC\_ECC\_Enable;

- ECCPageSize = FSMC\_ECCPageSize\_512Bytes;

- TCLRSetupTime = 0;

- TARSetupTime = 0;

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 44* and *Table 51*, respectively.

Unless otherwise specified, the parameters given in *Table 51* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| MODEx[1:0]<br>bit value <sup>(1)</sup> | Symbol                  | Parameter                                                             | Conditions                                                      | Min | Max                | Unit |

|----------------------------------------|-------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------|-----|--------------------|------|

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V                        | -   | 2                  | MHz  |

| 10                                     | t <sub>f(IO)out</sub>   | Output high to low level fall time                                    | C <sub>1</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V          | -   | 125 <sup>(3)</sup> | ns   |

|                                        | t <sub>r(IO)out</sub>   | Output low to high<br>level rise time                                 | CL - 30 μι, νDD - 2 ν 10 3.0 ν                                  | -   | 125 <sup>(3)</sup> | 115  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V                        | -   | 10                 | MHz  |

| 01                                     | t <sub>f(IO)out</sub>   | Output high to low<br>level fall time                                 | C = 50  pE V = 2  V to  3.6  V                                  | -   | 25 <sup>(3)</sup>  | nc   |

|                                        | t <sub>r(IO)out</sub>   | Output low to high<br>level rise time                                 | $C_{L} = 50 \text{ pF}, V_{DD} = 2 \text{ V to } 3.6 \text{ V}$ |     | 25 <sup>(3)</sup>  | ns   |

|                                        |                         |                                                                       | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                        | -   | 50                 | MHz  |

|                                        | F <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                      | -   | 30                 | MHz  |

|                                        |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                          | -   | 20                 | MHz  |

|                                        |                         |                                                                       | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                        | -   | 5 <sup>(3)</sup>   |      |

| 11                                     | t <sub>f(IO)out</sub>   | Output high to low<br>level fall time                                 | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                        | -   | 8 <sup>(3)</sup>   |      |

|                                        |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                          | -   | 12 <sup>(3)</sup>  | ns   |

|                                        |                         |                                                                       | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                        | -   | 5 <sup>(3)</sup>   | 115  |

|                                        | t <sub>r(IO)out</sub>   | Output low to high level rise time                                    | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                        | -   | 8 <sup>(3)</sup>   |      |

|                                        |                         |                                                                       | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                          | -   | 12 <sup>(3)</sup>  |      |

| -                                      | t <sub>EXTIpw</sub>     | Pulse width of external<br>signals detected by<br>the EXTI controller | -                                                               | 10  | -                  | ns   |

Table 51. I/O AC characteristics<sup>(1)</sup>

1. The I/O speed is configured using the MODEx[1:0] bits. Refer to the STM32F10xxx reference manual for a description of GPIO Port configuration register.

2. The maximum frequency is defined in Figure 44.

3. Guaranteed by design, not tested in production.

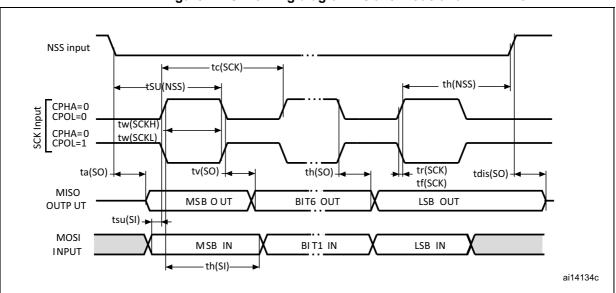

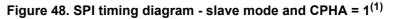

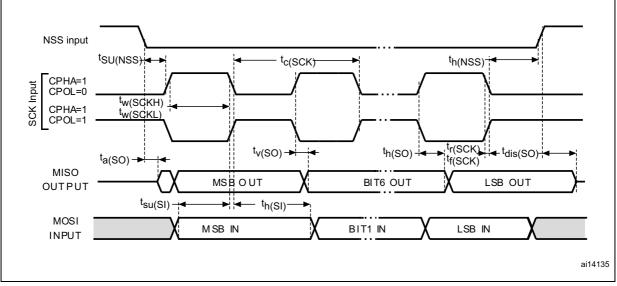

Figure 47. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$ .

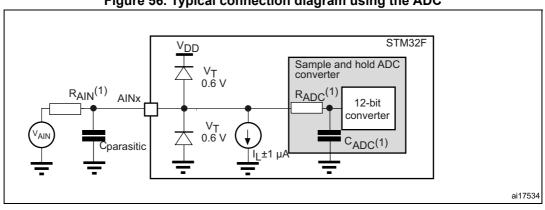

Figure 56. Typical connection diagram using the ADC

Refer to Table 62 for the values of RAIN, RADC and CADC. 1.

$C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

#### **General PCB design guidelines**

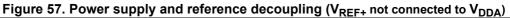

Power supply decoupling should be performed as shown in Figure 57 or Figure 58, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

1. V<sub>REF+</sub> and V<sub>REF-</sub> inputs are available only on 100-pin packages.

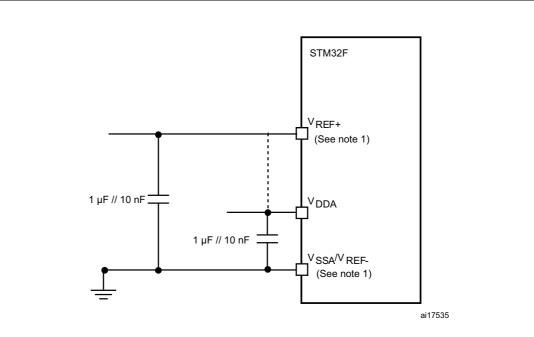

# 6.1 LFBGA144 package information

Figure 60. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package outline

1. Drawing is not to scale.

| Table 68. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, |

|-----------------------------------------------------------------------------------|

| 0.8 mm pitch, package mechanical data                                             |

| Symbol           |       | millimeters |        |        | inches <sup>(1)</sup> |        |  |  |

|------------------|-------|-------------|--------|--------|-----------------------|--------|--|--|

| Symbol           | Min   | Тур         | Max    | Тур    | Min                   | Max    |  |  |

| A <sup>(2)</sup> | -     | -           | 1.700  |        |                       | 0.0669 |  |  |

| A1               | 0.210 | -           | -      | 0.0083 |                       |        |  |  |

| A2               | -     | 1.060       | -      |        | 0.0417                |        |  |  |

| A3               |       | 0.026       |        |        | 0.0010                |        |  |  |

| A4               | -     | 0.800       | -      | -      | 0.0315                | -      |  |  |

| b                | 0.350 | 0.400       | 0.450  | 0.0138 | 0.0157                | 0.0177 |  |  |

| D                | 9.850 | 10.000      | 10.150 | 0.3878 | 0.3937                | 0.3996 |  |  |

| D1               | -     | 8.800       | -      | -      | 0.3465                | -      |  |  |

| E                | 9.850 | 10.000      | 10.150 | 0.3878 | 0.3937                | 0.3996 |  |  |

| E1               | -     | 8.800       | -      | -      | 0.3465                | -      |  |  |

| е                | -     | 0.800       | -      | -      | 0.0315                | -      |  |  |

| F                | -     | 0.600       | -      | -      | 0.0236                | -      |  |  |

| ddd              | -     | -           | 0.100  | -      | -                     | 0.0039 |  |  |

# Table 68. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm,0.8 mm pitch, package mechanical data (continued)

| Symbol | millimeters |     |       |     |     |        |

|--------|-------------|-----|-------|-----|-----|--------|

| Symbol | Min         | Тур | Мах   | Тур | Min | Мах    |

| eee    | -           | -   | 0.150 | -   | -   | 0.0059 |

| fff    | -           | -   | 0.080 | -   | -   | 0.0031 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. STATSChipPAC package dimensions.

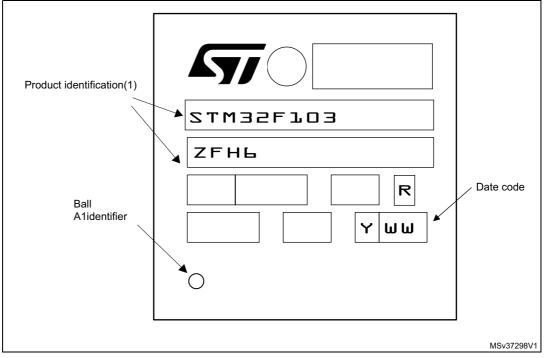

#### Device marking for LFBGA144 package

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 61. LFBGA144 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

Figure 63. LQFP144 - 144-pin,20 x 20 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

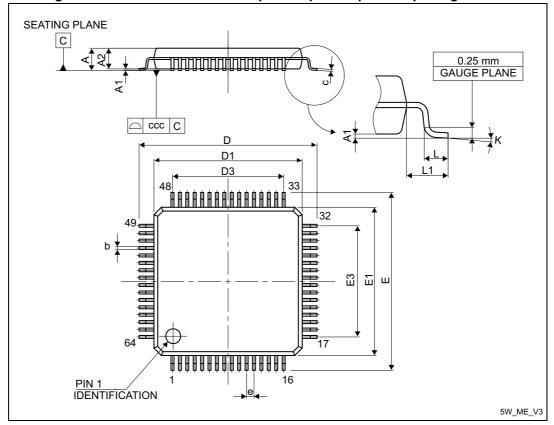

# 6.4 LQFP64 package information

Figure 68. LFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline

1. Drawing is not in scale.

Table 71. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data

| Cumula al |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|-----------|-------|-------------|-------|--------|-----------------------|--------|--|

| Symbol    | Min   | Тур         | Мах   | Min    | Тур                   | Max    |  |

| А         | -     | -           | 1.600 | -      | -                     | 0.0630 |  |

| A1        | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |  |

| A2        | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |  |

| b         | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |  |

| С         | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |  |

| D         | -     | 12.000      | -     | -      | 0.4724                | -      |  |

| D1        | -     | 10.000      | -     | -      | 0.3937                | -      |  |

| D3        | -     | 7.500       | -     | -      | 0.2953                | -      |  |

| E         | -     | 12.000      | -     | -      | 0.4724                | -      |  |

| E1        | -     | 10.000      | -     | -      | 0.3937                | -      |  |