# EXF

#### AMD Xilinx - XC2S100-6PQ208C Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| De | ta | IS |

|----|----|----|

|    |    |    |

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 600                                                         |

| Number of Logic Elements/Cells | 2700                                                        |

| Total RAM Bits                 | 40960                                                       |

| Number of I/O                  | 140                                                         |

| Number of Gates                | 100000                                                      |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 208-BFQFP                                                   |

| Supplier Device Package        | 208-PQFP (28x28)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s100-6pq208c |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

drivers are disabled. Maintaining a valid logic level in this way helps eliminate bus chatter.

Because the weak-keeper circuit uses the IOB input buffer to monitor the input level, an appropriate  $V_{REF}$  voltage must be provided if the signaling standard requires one. The provision of this voltage must comply with the I/O banking rules.

## I/O Banking

Some of the I/O standards described above require  $V_{CCO}$  and/or  $V_{REF}$  voltages. These voltages are externally connected to device pins that serve groups of IOBs, called banks. Consequently, restrictions exist about which I/O standards can be combined within a given bank.

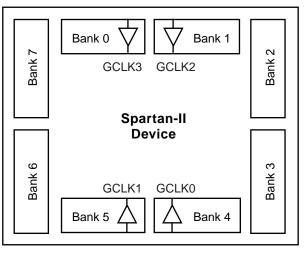

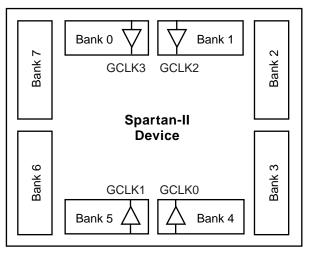

Eight I/O banks result from separating each edge of the FPGA into two banks (see Figure 3). Each bank has multiple  $V_{CCO}$  pins which must be connected to the same voltage. Voltage is determined by the output standards in use.

DS001\_03\_060100

Figure 3: Spartan-II I/O Banks

Within a bank, output standards may be mixed only if they use the same  $V_{CCO}$ . Compatible standards are shown in Table 4. GTL and GTL+ appear under all voltages because their open-drain outputs do not depend on  $V_{CCO}$ .

#### Table 4: Compatible Output Standards

| V <sub>cco</sub> | Compatible Standards                                  |

|------------------|-------------------------------------------------------|

| 3.3V             | PCI, LVTTL, SSTL3 I, SSTL3 II, CTT, AGP,<br>GTL, GTL+ |

| 2.5V             | SSTL2 I, SSTL2 II, LVCMOS2, GTL, GTL+                 |

| 1.5V             | HSTL I, HSTL III, HSTL IV, GTL, GTL+                  |

Some input standards require a user-supplied threshold voltage,  $V_{\text{REF}}$  In this case, certain user-I/O pins are

automatically configured as inputs for the V<sub>REF</sub> voltage. About one in six of the I/O pins in the bank assume this role.

$V_{\text{REF}}$  pins within a bank are interconnected internally and consequently only one  $V_{\text{REF}}$  voltage can be used within each bank. All  $V_{\text{REF}}$  pins in the bank, however, must be connected to the external voltage source for correct operation.

In a bank, inputs requiring V<sub>REF</sub> can be mixed with those that do not but only one V<sub>REF</sub> voltage may be used within a bank. Input buffers that use V<sub>REF</sub> are not 5V tolerant. LVTTL, LVCMOS2, and PCI are 5V tolerant. The V<sub>CCO</sub> and V<sub>REF</sub> pins for each bank appear in the device pinout tables.

Within a given package, the number of  $V_{REF}$  and  $V_{CCO}$  pins can vary depending on the size of device. In larger devices, more I/O pins convert to  $V_{REF}$  pins. Since these are always a superset of the  $V_{REF}$  pins used for smaller devices, it is possible to design a PCB that permits migration to a larger device. All  $V_{REF}$  pins for the largest device anticipated must be connected to the  $V_{REF}$  voltage, and not used for I/O.

Independent Banks Available

| Package           | VQ100 | CS144 | FG256 |  |

|-------------------|-------|-------|-------|--|

|                   | PQ208 | TQ144 | FG456 |  |

| Independent Banks | 1     | 4     | 8     |  |

## **Configurable Logic Block**

The basic building block of the Spartan-II FPGA CLB is the logic cell (LC). An LC includes a 4-input function generator, carry logic, and storage element. Output from the function generator in each LC drives the CLB output and the D input of the flip-flop. Each Spartan-II FPGA CLB contains four LCs, organized in two similar slices; a single slice is shown in Figure 4.

In addition to the four basic LCs, the Spartan-II FPGA CLB contains logic that combines function generators to provide functions of five or six inputs.

## Look-Up Tables

Spartan-II FPGA function generators are implemented as 4-input look-up tables (LUTs). In addition to operating as a function generator, each LUT can provide a 16 x 1-bit synchronous RAM. Furthermore, the two LUTs within a slice can be combined to create a 16 x 2-bit or 32 x 1-bit synchronous RAM, or a 16 x 1-bit dual-port synchronous RAM.

The Spartan-II FPGA LUT can also provide a 16-bit shift register that is ideal for capturing high-speed or burst-mode data. This mode can also be used to store data in applications such as Digital Signal Processing.

## **∑** XILINX<sup>®</sup>

## Local Routing

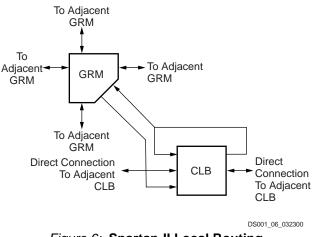

The local routing resources, as shown in Figure 6, provide the following three types of connections:

- Interconnections among the LUTs, flip-flops, and General Routing Matrix (GRM)

- Internal CLB feedback paths that provide high-speed connections to LUTs within the same CLB, chaining them together with minimal routing delay

- Direct paths that provide high-speed connections between horizontally adjacent CLBs, eliminating the delay of the GRM

Figure 6: Spartan-II Local Routing

## General Purpose Routing

Most Spartan-II FPGA signals are routed on the general purpose routing, and consequently, the majority of interconnect resources are associated with this level of the routing hierarchy. The general routing resources are located in horizontal and vertical routing channels associated with the rows and columns CLBs. The general-purpose routing resources are listed below.

- Adjacent to each CLB is a General Routing Matrix (GRM). The GRM is the switch matrix through which horizontal and vertical routing resources connect, and is also the means by which the CLB gains access to the general purpose routing.

- 24 single-length lines route GRM signals to adjacent GRMs in each of the four directions.

- 96 buffered Hex lines route GRM signals to other GRMs six blocks away in each one of the four directions. Organized in a staggered pattern, Hex lines may be driven only at their endpoints. Hex-line signals can be accessed either at the endpoints or at the midpoint (three blocks from the source). One third of the Hex lines are bidirectional, while the remaining ones are unidirectional.

- 12 Longlines are buffered, bidirectional wires that distribute signals across the device quickly and

efficiently. Vertical Longlines span the full height of the device, and horizontal ones span the full width of the device.

## I/O Routing

Spartan-II devices have additional routing resources around their periphery that form an interface between the CLB array and the IOBs. This additional routing, called the VersaRing, facilitates pin-swapping and pin-locking, such that logic redesigns can adapt to existing PCB layouts. Time-to-market is reduced, since PCBs and other system components can be manufactured while the logic design is still in progress.

## **Dedicated Routing**

Some classes of signal require dedicated routing resources to maximize performance. In the Spartan-II architecture, dedicated routing resources are provided for two classes of signal.

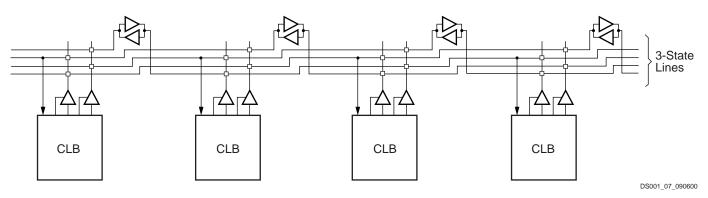

- Horizontal routing resources are provided for on-chip 3-state busses. Four partitionable bus lines are provided per CLB row, permitting multiple busses within a row, as shown in Figure 7.

- Two dedicated nets per CLB propagate carry signals vertically to the adjacent CLB.

## **Global Routing**

Global Routing resources distribute clocks and other signals with very high fanout throughout the device. Spartan-II devices include two tiers of global routing resources referred to as primary and secondary global routing resources.

- The primary global routing resources are four dedicated global nets with dedicated input pins that are designed to distribute high-fanout clock signals with minimal skew. Each global clock net can drive all CLB, IOB, and block RAM clock pins. The primary global nets may only be driven by global buffers. There are four global buffers, one for each global net.

- The secondary global routing resources consist of 24 backbone lines, 12 across the top of the chip and 12 across bottom. From these lines, up to 12 unique signals per column can be distributed via the 12 longlines in the column. These secondary resources are more flexible than the primary resources since they are not restricted to routing only to clock pins.

Figure 7: BUFT Connections to Dedicated Horizontal Bus Lines

## **Clock Distribution**

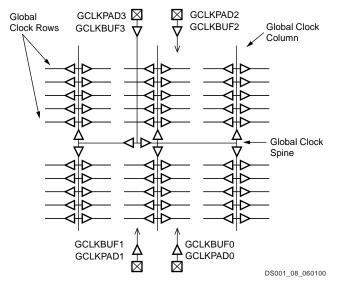

The Spartan-II family provides high-speed, low-skew clock distribution through the primary global routing resources described above. A typical clock distribution net is shown in Figure 8.

Four global buffers are provided, two at the top center of the device and two at the bottom center. These drive the four primary global nets that in turn drive any clock pin.

Four dedicated clock pads are provided, one adjacent to each of the global buffers. The input to the global buffer is selected either from these pads or from signals in the general purpose routing. Global clock pins do not have the option for internal, weak pull-up resistors.

Figure 8: Global Clock Distribution Network

## Delay-Locked Loop (DLL)

Associated with each global clock input buffer is a fully digital Delay-Locked Loop (DLL) that can eliminate skew between the clock input pad and internal clock-input pins throughout the device. Each DLL can drive two global clock networks. The DLL monitors the input clock and the distributed clock, and automatically adjusts a clock delay element. Additional delay is introduced such that clock edges reach internal flip-flops exactly one clock period after they arrive at the input. This closed-loop system effectively eliminates clock-distribution delay by ensuring that clock edges arrive at internal flip-flops in synchronism with clock edges arriving at the input.

In addition to eliminating clock-distribution delay, the DLL provides advanced control of multiple clock domains. The DLL provides four quadrature phases of the source clock, can double the clock, or divide the clock by 1.5, 2, 2.5, 3, 4, 5, 8, or 16. It has six outputs.

The DLL also operates as a clock mirror. By driving the output from a DLL off-chip and then back on again, the DLL can be used to deskew a board level clock among multiple Spartan-II devices.

In order to guarantee that the system clock is operating correctly prior to the FPGA starting up after configuration, the DLL can delay the completion of the configuration process until after it has achieved lock.

## **Boundary Scan**

Spartan-II devices support all the mandatory boundaryscan instructions specified in the IEEE standard 1149.1. A Test Access Port (TAP) and registers are provided that implement the EXTEST, SAMPLE/PRELOAD, and BYPASS instructions. The TAP also supports two USERCODE instructions and internal scan chains.

The TAP uses dedicated package pins that always operate using LVTTL. For TDO to operate using LVTTL, the V<sub>CCO</sub> for Bank 2 must be 3.3V. Otherwise, TDO switches rail-to-rail between ground and V<sub>CCO</sub>. TDI, TMS, and TCK have a default internal weak pull-up resistor, and TDO has no default resistor. Bitstream options allow setting any of the four TAP pins to have an internal pull-up, pull-down, or neither.

Boundary-scan operation is independent of individual IOB configurations, and unaffected by package type. All IOBs, including unbonded ones, are treated as independent 3-state bidirectional pins in a single scan chain. Retention of the bidirectional test capability after configuration facilitates the testing of external interconnections.

Table 7 lists the boundary-scan instructions supported in Spartan-II FPGAs. Internal signals can be captured during EXTEST by connecting them to unbonded or unused IOBs. They may also be connected to the unused outputs of IOBs defined as unidirectional input pins.

| Boundary-Scan<br>Command | Binary<br>Code[4:0] | Description                                                   |

|--------------------------|---------------------|---------------------------------------------------------------|

| EXTEST                   | 00000               | Enables boundary-scan<br>EXTEST operation                     |

| SAMPLE                   | 00001               | Enables boundary-scan<br>SAMPLE operation                     |

| USR1                     | 00010               | Access user-defined<br>register 1                             |

| USR2                     | 00011               | Access user-defined<br>register 2                             |

| CFG_OUT                  | 00100               | Access the<br>configuration bus for<br>Readback               |

| CFG_IN                   | 00101               | Access the<br>configuration bus for<br>Configuration          |

| INTEST                   | 00111               | Enables boundary-scan<br>INTEST operation                     |

| USRCODE                  | 01000               | Enables shifting out<br>USER code                             |

| IDCODE                   | 01001               | Enables shifting out of<br>ID Code                            |

| HIZ                      | 01010               | Disables output pins<br>while enabling the<br>Bypass Register |

| JSTART                   | 01100               | Clock the start-up<br>sequence when<br>StartupClk is TCK      |

| BYPASS                   | 11111               | Enables BYPASS                                                |

| RESERVED                 | All other codes     | Xilinx <sup>®</sup> reserved<br>instructions                  |

## Table 7: Boundary-Scan Instructions

The public boundary-scan instructions are available prior to configuration. After configuration, the public instructions remain available together with any USERCODE instructions installed during the configuration. While the SAMPLE and BYPASS instructions are available during configuration, it is recommended that boundary-scan operations not be performed during this transitional period.

In addition to the test instructions outlined above, the boundary-scan circuitry can be used to configure the FPGA, and also to read back the configuration data.

To facilitate internal scan chains, the User Register provides three outputs (Reset, Update, and Shift) that represent the corresponding states in the boundary-scan internal state machine.

DS001\_16\_032300

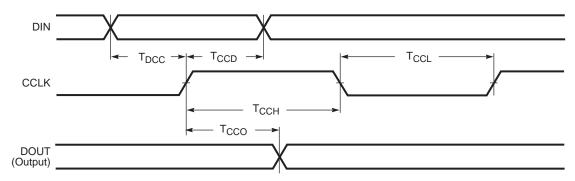

| Symbol           |      | Description       |    | Units    |

|------------------|------|-------------------|----|----------|

| T <sub>DCC</sub> |      | DIN setup         | 5  | ns, min  |

| T <sub>CCD</sub> |      | DIN hold          | 0  | ns, min  |

| T <sub>CCO</sub> | CCLK | DOUT              | 12 | ns, max  |

| ТССН             |      | High time         | 5  | ns, min  |

| T <sub>CCL</sub> |      | Low time          | 5  | ns, min  |

| F <sub>CC</sub>  |      | Maximum frequency | 66 | MHz, max |

Figure 16: Slave Serial Mode Timing

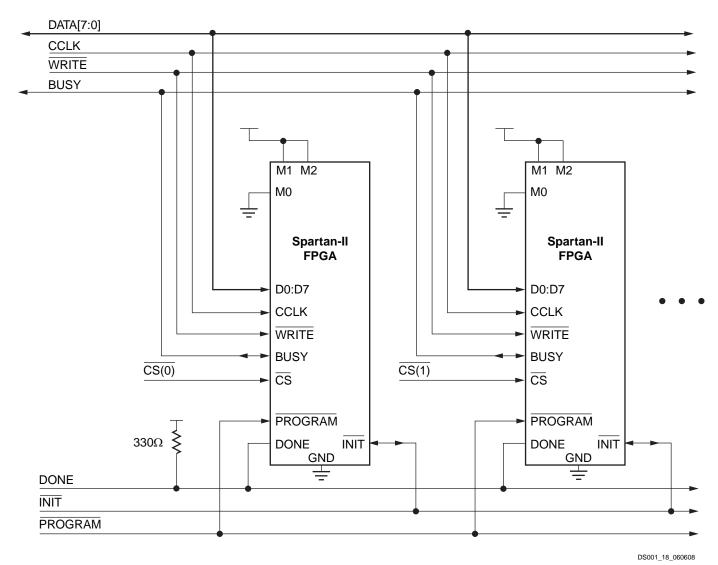

Figure 18: Slave Parallel Configuration Circuit Diagram

Multiple Spartan-II FPGAs can be configured using the Slave Parallel mode, and be made to start-up simultaneously. To configure multiple devices in this way, wire the individual CCLK, Data, WRITE, and BUSY pins of all the devices in parallel. The individual devices are loaded separately by asserting the CS pin of each device in turn and writing the appropriate data. Sync-to-DONE start-up timing is used to ensure that the start-up sequence does not begin until all the FPGAs have been loaded. See "Start-up," page 19.

#### Write

When using the Slave Parallel Mode, write operations send packets of byte-wide configuration data into the FPGA. Figure 19, page 25 shows a flowchart of the write sequence used to load data into the Spartan-II FPGA. This is an expansion of the "Load Configuration Data Frames" block in Figure 11, page 18. The timing for write operations is shown in Figure 20, page 26. For the present example, the user holds  $\overline{\text{WRITE}}$  and  $\overline{\text{CS}}$ Low throughout the sequence of write operations. Note that when  $\overline{\text{CS}}$  is asserted on successive CCLKs,  $\overline{\text{WRITE}}$  must remain either asserted or de-asserted. Otherwise an abort will be initiated, as in the next section.

- 1. Drive data onto D0-D7. Note that to avoid contention, the data source should not be enabled while  $\overline{CS}$  is Low and  $\overline{WRITE}$  is High. Similarly, while  $\overline{WRITE}$  is High, no more than one device's  $\overline{CS}$  should be asserted.

- 2. On the rising edge of CCLK: If BUSY is Low, the data is accepted on this clock. If BUSY is High (from a previous write), the data is not accepted. Acceptance will instead occur on the first clock after BUSY goes Low, and the data must be held until this happens.

- 3. Repeat steps 1 and 2 until all the data has been sent.

- 4. De-assert  $\overline{\text{CS}}$  and  $\overline{\text{WRITE}}$ .

the LOC property is described below. Table 16 summarizes the input standards compatibility requirements.

An optional delay element is associated with each IBUF. When the IBUF drives a flip-flop within the IOB, the delay element by default activates to ensure a zero hold-time requirement. The NODELAY=TRUE property overrides this default.

When the IBUF does not drive a flip-flop within the IOB, the delay element de-activates by default to provide higher performance. To delay the input signal, activate the delay element with the DELAY=TRUE property.

DS001\_03\_060100

Figure 36: I/O Banks

## Table 16: Xilinx Input Standards CompatibilityRequirements

| Rule 1 | All differential amplifier input signals within a bank are required to be of the same standard.         |

|--------|---------------------------------------------------------------------------------------------------------|

| Rule 2 | There are no placement restrictions for inputs with standards that require a single-ended input buffer. |

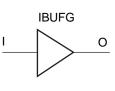

#### IBUFG

Signals used as high fanout clock inputs to the Spartan-II device should drive a global clock input buffer (IBUFG) via an external input port in order to take advantage of one of the four dedicated global clock distribution networks. The output of the IBUFG primitive can only drive a CLKDLL, CLKDLLHF, or a BUFG primitive. The generic IBUFG primitive appears in Figure 37.

DS001\_37\_061200

Figure 37: Global Clock Input Buffer (IBUFG) Primitive

With no extension or property specified for the generic IBUFG primitive, the assumed standard is LVTTL.

The voltage reference signal is "banked" within the Spartan-II device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 36 for a representation of the I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input.

IBUFG placement restrictions require any differential amplifier input signals within a bank be of the same standard. The LOC property can specify a location for the IBUFG.

As an added convenience, the BUFGP can be used to instantiate a high fanout clock input. The BUFGP primitive represents a combination of the LVTTL IBUFG and BUFG primitives, such that the output of the BUFGP can connect directly to the clock pins throughout the design.

The Spartan-II FPGA BUFGP primitive can only be placed in a global clock pad location. The LOC property can specify a location for the BUFGP.

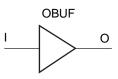

#### OBUF

An OBUF must drive outputs through an external output port. The generic output buffer (OBUF) primitive appears in Figure 38.

DS001\_38\_061200

#### Figure 38: Output Buffer (OBUF) Primitive

With no extension or property specified for the generic OBUF primitive, the assumed standard is slew rate limited LVTTL with 12 mA drive strength.

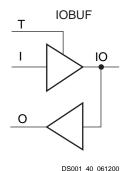

The LVTTL OBUF additionally can support one of two slew rate modes to minimize bus transients. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals. IOBUF\_<slew\_rate>\_<drive\_strength>

<slew\_rate> can be either F (Fast), or S (Slow) and <drive\_strength> is specified in milliamps (2, 4, 6, 8, 12, 16, or 24).

When the IOBUF primitive supports an I/O standard such as LVTTL, LVCMOS, or PCI33\_5, the IBUF automatically configures as a 5V tolerant input buffer unless the V<sub>CCO</sub> for the bank is less than 2V. If the single-ended IBUF is placed in a bank with an HSTL standard (V<sub>CCO</sub> < 2V), the input buffer is not 5V tolerant.

The voltage reference signal is "banked" within the Spartan-II device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 36, page 39 for a representation of the Spartan-II FPGA I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input.

Additional restrictions on the Versatile I/O IOBUF placement require that within a given  $V_{CCO}$  bank each IOBUF must share the same output source drive voltage. Input buffers of any type and output buffers that do not require  $V_{CCO}$  can be placed within the same  $V_{CCO}$  bank. The LOC property can specify a location for the IOBUF.

An optional delay element is associated with the input path in each IOBUF. When the IOBUF drives an input flip-flop within the IOB, the delay element activates by default to ensure a zero hold-time requirement. Override this default with the NODELAY=TRUE property.

In the case when the IOBUF does not drive an input flip-flop within the IOB, the delay element de-activates by default to provide higher performance. To delay the input signal, activate the delay element with the DELAY=TRUE property.

3-state output buffers and bidirectional buffers can have either a weak pull-up resistor, a weak pull-down resistor, or a weak "keeper" circuit. Control this feature by adding the appropriate primitive to the output net of the IOBUF (PULLUP, PULLDOWN, or KEEPER).

### **Versatile I/O Properties**

Access to some of the Versatile I/O features (for example, location constraints, input delay, output drive strength, and slew rate) is available through properties associated with these features.

#### Input Delay Properties

An optional delay element is associated with each IBUF. When the IBUF drives a flip-flop within the IOB, the delay element activates by default to ensure a zero hold-time requirement. Use the NODELAY=TRUE property to override this default.

In the case when the IBUF does not drive a flip-flop within the IOB, the delay element by default de-activates to provide higher performance. To delay the input signal, activate the delay element with the DELAY=TRUE property.

#### IOB Flip-Flop/Latch Property

The I/O Block (IOB) includes an optional register on the input path, an optional register on the output path, and an optional register on the 3-state control pin. The design implementation software automatically takes advantage of these registers when the following option for the Map program is specified:

#### map -pr b <filename>

Alternatively, the IOB = TRUE property can be placed on a register to force the mapper to place the register in an IOB.

#### **Location Constraints**

Specify the location of each Versatile I/O primitive with the location constraint LOC attached to the Versatile I/O primitive. The external port identifier indicates the value of the location constrain. The format of the port identifier depends on the package chosen for the specific design.

The LOC properties use the following form:

LOC=A42 LOC=P37

## **Output Slew Rate Property**

In the case of the LVTTL output buffers (OBUF, OBUFT, and IOBUF), slew rate control can be programmed with the SLEW= property. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals. The SLEW= property has one of the two following values.

SLEW=SLOW

SLEW=FAST

## **Output Drive Strength Property**

For the LVTTL output buffers (OBUF, OBUFT, and IOBUF, the desired drive strength can be specified with the DRIVE=

ground metallization. The IC internal ground level deviates from the external system ground level for a short duration (a few nanoseconds) after multiple outputs change state simultaneously.

Ground bounce affects stable Low outputs and all inputs because they interpret the incoming signal by comparing it to the internal ground. If the ground bounce amplitude exceeds the actual instantaneous noise margin, then a non-changing input can be interpreted as a short pulse with a polarity opposite to the ground bounce.

Table 18 provides the guidelines for the maximum numberof simultaneously switching outputs allowed per outputpower/ground pair to avoid the effects of ground bounce.Refer to Table 19 for the number of effective outputpower/ground pairs for each Spartan-II device and packagecombination.

## Table 18: Maximum Number of Simultaneously Switching Outputs per Power/Ground Pair

|                                   | Package |               |

|-----------------------------------|---------|---------------|

| Standard                          | CS, FG  | PQ,<br>TQ, VQ |

| LVTTL Slow Slew Rate, 2 mA drive  | 68      | 36            |

| LVTTL Slow Slew Rate, 4 mA drive  | 41      | 20            |

| LVTTL Slow Slew Rate, 6 mA drive  | 29      | 15            |

| LVTTL Slow Slew Rate, 8 mA drive  | 22      | 12            |

| LVTTL Slow Slew Rate, 12 mA drive | 17      | 9             |

| LVTTL Slow Slew Rate, 16 mA drive | 14      | 7             |

| LVTTL Slow Slew Rate, 24 mA drive | 9       | 5             |

| LVTTL Fast Slew Rate, 2 mA drive  | 40      | 21            |

| LVTTL Fast Slew Rate, 4 mA drive  | 24      | 12            |

| LVTTL Fast Slew Rate, 6 mA drive  | 17      | 9             |

| LVTTL Fast Slew Rate, 8 mA drive  | 13      | 7             |

| LVTTL Fast Slew Rate, 12 mA drive | 10      | 5             |

| LVTTL Fast Slew Rate, 16 mA drive | 8       | 4             |

| LVTTL Fast Slew Rate, 24 mA drive | 5       | 3             |

| LVCMOS2                           | 10      | 5             |

| PCI                               | 8       | 4             |

| GTL                               | 4       | 4             |

| GTL+                              | 4       | 4             |

| HSTL Class I                      | 18      | 9             |

| HSTL Class III                    | 9       | 5             |

| HSTL Class IV                     | 5       | 3             |

| SSTL2 Class I                     | 15      | 8             |

## Table 18: Maximum Number of SimultaneouslySwitching Outputs per Power/Ground Pair

|                | Package |               |

|----------------|---------|---------------|

| Standard       | CS, FG  | PQ,<br>TQ, VQ |

| SSTL2 Class II | 10      | 5             |

| SSTL3 Class I  | 11      | 6             |

| SSTL3 Class II | 7       | 4             |

| СТТ            | 14      | 7             |

| AGP            | 9       | 5             |

Notes:

1. This analysis assumes a 35 pF load for each output.

## Table 19: Effective Output Power/Ground Pairs for Spartan-II Devices

|       | Spartan-II Devices                                        |    |    |    |    |    |  |

|-------|-----------------------------------------------------------|----|----|----|----|----|--|

| Pkg.  | XC2S XC2S XC2S XC2S XC2S XC2S XC2<br>15 30 50 100 150 200 |    |    |    |    |    |  |

| VQ100 | 8                                                         | 8  | -  | -  | -  | -  |  |

| CS144 | 12                                                        | 12 | -  | -  | -  | -  |  |

| TQ144 | 12                                                        | 12 | 12 | 12 | -  | -  |  |

| PQ208 | -                                                         | 16 | 16 | 16 | 16 | 16 |  |

| FG256 | -                                                         | -  | 16 | 16 | 16 | 16 |  |

| FG456 | -                                                         | -  | -  | 48 | 48 | 48 |  |

## **Termination Examples**

Creating a design with the Versatile I/O features requires the instantiation of the desired library primitive within the design code. At the board level, designers need to know the termination techniques required for each I/O standard.

This section describes some common application examples illustrating the termination techniques recommended by each of the standards supported by the Versatile I/O features. For a full range of accepted values for the DC voltage specifications for each standard, refer to the table associated with each figure.

The resistors used in each termination technique example and the transmission lines depicted represent board level components and are not meant to represent components on the device.

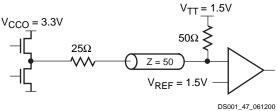

## SSTL3 Class I

A sample circuit illustrating a valid termination technique for SSTL3\_I appears in Figure 47. DC voltage specifications appear in Table 25 for the SSTL3\_I standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

#### SSTL3 Class I

Figure 47: Terminated SSTL3 Class I

| Table 2 | 25: | SSTL3_ | I Voltage | <b>Specifications</b> |

|---------|-----|--------|-----------|-----------------------|

|---------|-----|--------|-----------|-----------------------|

| Parameter                               | Min     | Тур | Max                |

|-----------------------------------------|---------|-----|--------------------|

| V <sub>CCO</sub>                        | 3.0     | 3.3 | 3.6                |

| $V_{REF} = 0.45 \times V_{CCO}$         | 1.3     | 1.5 | 1.7                |

| V <sub>TT</sub> = V <sub>REF</sub>      | 1.3     | 1.5 | 1.7                |

| $V_{IH} \ge V_{REF} + 0.2$              | 1.5     | 1.7 | 3.9 <sup>(1)</sup> |

| $V_{IL} \leq V_{REF} - 0.2$             | -0.3(2) | 1.3 | 1.5                |

| $V_{OH} \ge V_{REF} + 0.6$              | 1.9     | -   | -                  |

| $V_{OL} \leq V_{REF} - 0.6$             | -       | -   | 1.1                |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -8      | -   | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 8       | -   | -                  |

#### Notes:

1.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3.

2. V<sub>IL</sub> minimum does not conform to the formula.

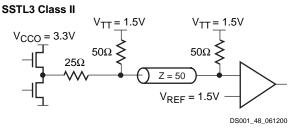

#### SSTL3 Class II

A sample circuit illustrating a valid termination technique for SSTL3\_II appears in Figure 48. DC voltage specifications appear in Table 26 for the SSTL3\_II standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 48: Terminated SSTL3 Class II

#### Table 26: SSTL3\_II Voltage Specifications

| Parameter                                | 3.0     3.3     3.6 $0.45 \times V_{CCO}$ 1.3     1.5     1.7 $r_{REF}$ 1.3     1.5     1.7 $r_{REF}$ + 0.2     1.5     1.7     3.9 <sup>(1)</sup> $r_{REF}$ + 0.2     -0.3 <sup>(2)</sup> 1.3     1.5 $r_{REF}$ + 0.8     2.1     -     - $V_{REF}$ - 0.8     -     0.9 $V_{OH}$ (mA)     -16     -     - |     |                    |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|

| V <sub>CCO</sub>                         | 3.0                                                                                                                                                                                                                                                                                                        | 3.3 | 3.6                |

| $V_{REF} = 0.45 \times V_{CCO}$          | 1.3                                                                                                                                                                                                                                                                                                        | 1.5 | 1.7                |

| V <sub>TT</sub> = V <sub>REF</sub>       | 1.3                                                                                                                                                                                                                                                                                                        | 1.5 | 1.7                |

| V <sub>IH</sub> ≥ V <sub>REF</sub> + 0.2 | 1.5                                                                                                                                                                                                                                                                                                        | 1.7 | 3.9 <sup>(1)</sup> |

| $V_{IL} \leq V_{REF} - 0.2$              | -0.3(2)                                                                                                                                                                                                                                                                                                    | 1.3 | 1.5                |

| $V_{OH} \ge V_{REF} + 0.8$               | 2.1                                                                                                                                                                                                                                                                                                        | -   | -                  |

| $V_{OL} \leq V_{REF} - 0.8$              | -                                                                                                                                                                                                                                                                                                          | -   | 0.9                |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)  | -16                                                                                                                                                                                                                                                                                                        | -   | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA)  | 16                                                                                                                                                                                                                                                                                                         | -   | -                  |

Notes:

1.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3

2. V<sub>IL</sub> minimum does not conform to the formula

## **IOB Output Switching Characteristics**

Output delays terminating at a pad are specified for LVTTL with 12 mA drive and fast slew rate. For other standards, adjust the delays with the values shown in "IOB Output Delay Adjustments for Different Standards," page 59.

|                                                |                                                                    |            | Speed | Grade                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |    |

|------------------------------------------------|--------------------------------------------------------------------|------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|

|                                                |                                                                    | -6         |       | -5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |    |

| Symbol                                         | Description                                                        | Min        | Max   | ax         Min         Max         Units           .9         -         3.4         ns           .4         -         4.0         ns           .4         -         4.0         ns           .0         -         2.3         ns           .0         -         3.6         ns           .5         -         2.9         ns           .5         -         4.2         ns           .0         -         5.9         ns           .5         -         2.7         ns           .3         -         2.7         ns           .3         -         4.0         ns           -         1.3/0         -         ns |      |    |

| Propagation Delay                              | S                                                                  |            |       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |    |

| T <sub>IOOP</sub>                              | O input to pad                                                     | -          | 2.9   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.4  | ns |

| T <sub>IOOLP</sub>                             | O input to pad via transparent latch                               | -          | 3.4   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.0  | ns |

| 3-state Delays                                 | 1                                                                  | 1          |       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |    |

| T <sub>IOTHZ</sub>                             | T input to pad high-impedance <sup>(1)</sup>                       | -          | 2.0   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.3  | ns |

| T <sub>IOTON</sub>                             | T input to valid data on pad                                       | -          | 3.0   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.6  | ns |

| T <sub>IOTLPHZ</sub>                           | T input to pad high impedance via transparent latch <sup>(1)</sup> | -          | 2.5   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.9  | ns |

| TIOTLPON                                       | T input to valid data on pad via transparent latch                 | -          | 3.5   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.2  | ns |

| T <sub>GTS</sub>                               | GTS to pad high impedance <sup>(1)</sup>                           | -          | 5.0   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5.9  | ns |

| Sequential Delays                              | ;<br>;                                                             |            |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |    |

| T <sub>IOCKP</sub>                             | Clock CLK to pad                                                   | -          | 2.9   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.4  | ns |

| T <sub>IOCKHZ</sub>                            | Clock CLK to pad high impedance (synchronous) <sup>(1)</sup>       | -          | 2.3   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.7  | ns |

| TIOCKON                                        | Clock CLK to valid data on pad (synchronous)                       | -          | 3.3   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.0  | ns |

|                                                | with Respect to Clock CLK <sup>(2)</sup>                           |            |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |    |

| TIOOCK / TIOCKO                                | O input                                                            | 1.1/0      | -     | 1.3/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -    | ns |

| T <sub>IOOCECK</sub> /<br>T <sub>IOCKOCE</sub> | OCE input                                                          | 0.9 / 0.01 | -     | 0.9 / 0.01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -    | ns |

| T <sub>IOSRCKO</sub> /<br>T <sub>IOCKOSR</sub> | SR input (OFF)                                                     | 1.2/0      | -     | 1.3 / 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -    | ns |

| TIOTCK / TIOCKT                                | 3-state setup times, T input                                       | 0.8/0      | -     | 0.9/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -    | ns |

| T <sub>IOTCECK</sub> /<br>T <sub>IOCKTCE</sub> | 3-state setup times, TCE input                                     | 1.0 / 0    | -     | 1.0 / 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -    | ns |

| T <sub>IOSRCKT</sub> /<br>T <sub>IOCKTSR</sub> | 3-state setup times, SR input (TFF)                                | 1.1/0      | -     | 1.2/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -    | ns |

| Set/Reset Delays                               |                                                                    | 1          |       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | 1  |

| T <sub>IOSRP</sub>                             | SR input to pad (asynchronous)                                     | -          | 3.7   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.4  | ns |

| T <sub>IOSRHZ</sub>                            | SR input to pad high impedance (asynchronous) <sup>(1)</sup>       | -          | 3.1   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.7  | ns |

| T <sub>IOSRON</sub>                            | SR input to valid data on pad (asynchronous)                       | -          | 4.1   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.9  | ns |

| T <sub>IOGSRQ</sub>                            | GSR to pad                                                         | -          | 9.9   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11.7 | ns |

Notes:

1. Three-state turn-off delays should not be adjusted.

2. A zero hold time listing indicates no hold time or a negative hold time.

## IOB Output Delay Adjustments for Different Standards<sup>(1)</sup>

Output delays terminating at a pad are specified for LVTTL with 12 mA drive and fast slew rate. For other standards, adjust the delays by the values shown. A delay adjusted in this way constitutes a worst-case limit.

|                         |                                                                    |                   | Speed | d Grade |       |

|-------------------------|--------------------------------------------------------------------|-------------------|-------|---------|-------|

| Symbol                  | Description                                                        | Standard          | -6    | -5      | Units |

| Output Delay Adj        | ustments (Adj)                                                     |                   |       |         |       |

| T <sub>OLVTTL_S2</sub>  | Standard-specific adjustments for                                  | LVTTL, Slow, 2 mA | 14.2  | 16.9    | ns    |

| T <sub>OLVTTL_S4</sub>  | output delays terminating at pads<br>(based on standard capacitive | 4 mA              | 7.2   | 8.6     | ns    |

| T <sub>OLVTTL_S6</sub>  | load, C <sub>SI</sub> )                                            | 6 mA              | 4.7   | 5.5     | ns    |

| T <sub>OLVTTL_S8</sub>  |                                                                    | 8 mA              | 2.9   | 3.5     | ns    |

| T <sub>OLVTTL_S12</sub> |                                                                    | 12 mA             | 1.9   | 2.2     | ns    |

| T <sub>OLVTTL_S16</sub> |                                                                    | 16 mA             | 1.7   | 2.0     | ns    |

| T <sub>OLVTTL_S24</sub> |                                                                    | 24 mA             | 1.3   | 1.5     | ns    |

| T <sub>OLVTTL_F2</sub>  |                                                                    | LVTTL, Fast, 2 mA | 12.6  | 15.0    | ns    |

| T <sub>OLVTTL_F4</sub>  |                                                                    | 4 mA              | 5.1   | 6.1     | ns    |

| T <sub>OLVTTL_F6</sub>  |                                                                    | 6 mA              | 3.0   | 3.6     | ns    |

| T <sub>OLVTTL_F8</sub>  |                                                                    | 8 mA              | 1.0   | 1.2     | ns    |

| T <sub>OLVTTL_F12</sub> |                                                                    | 12 mA             | 0     | 0       | ns    |

| T <sub>OLVTTL_F16</sub> | _                                                                  | 16 mA             | -0.1  | -0.1    | ns    |

| T <sub>OLVTTL_F24</sub> |                                                                    | 24 mA             | -0.1  | -0.2    | ns    |

| T <sub>OLVCMOS2</sub>   |                                                                    | LVCMOS2           | 0.2   | 0.2     | ns    |

| T <sub>OPCI33_3</sub>   |                                                                    | PCI, 33 MHz, 3.3V | 2.4   | 2.9     | ns    |

| T <sub>OPCI33_5</sub>   |                                                                    | PCI, 33 MHz, 5.0V | 2.9   | 3.5     | ns    |

| T <sub>OPCI66_3</sub>   |                                                                    | PCI, 66 MHz, 3.3V | -0.3  | -0.4    | ns    |

| T <sub>OGTL</sub>       |                                                                    | GTL               | 0.6   | 0.7     | ns    |

| T <sub>OGTLP</sub>      |                                                                    | GTL+              | 0.9   | 1.1     | ns    |

| T <sub>OHSTL_I</sub>    |                                                                    | HSTL I            | -0.4  | -0.5    | ns    |

| T <sub>OHSTL_III</sub>  |                                                                    | HSTL III          | -0.8  | -1.0    | ns    |

| T <sub>OHSTL_IV</sub>   |                                                                    | HSTL IV           | -0.9  | -1.1    | ns    |

| T <sub>OSSTL2_I</sub>   | —                                                                  | SSTL2 I           | -0.4  | -0.5    | ns    |

| T <sub>OSSLT2_II</sub>  |                                                                    | SSTL2 II          | -0.8  | -1.0    | ns    |

| T <sub>OSSTL3_I</sub>   |                                                                    | SSTL3 I           | -0.4  | -0.5    | ns    |

| T <sub>OSSTL3_II</sub>  |                                                                    | SSTL3 II          | -0.9  | -1.1    | ns    |

| T <sub>OCTT</sub>       |                                                                    | CTT               | -0.5  | -0.6    | ns    |

| T <sub>OAGP</sub>       |                                                                    | AGP               | -0.8  | -1.0    | ns    |

Notes:

1. Output timing is measured at 1.4V with 35 pF external capacitive load for LVTTL. For other I/O standards and different loads, see the tables "Constants for Calculating TIOOP" and "Delay Measurement Methodology," page 60.

## Calculation of T<sub>IOOP</sub> as a Function of Capacitance

$T_{\rm IOOP}$  is the propagation delay from the O Input of the IOB to the pad. The values for  $T_{\rm IOOP}$  are based on the standard capacitive load (C<sub>SL</sub>) for each I/O standard as listed in the table "Constants for Calculating TIOOP", below.

For other capacitive loads, use the formulas below to calculate an adjusted propagation delay,  $T_{IOOP1}$ .

$$T_{IOOP1} = T_{IOOP} + Adj + (C_{LOAD} - C_{SL}) * F_{L}$$

Where:

Adj is selected from "IOB Output Delay Adjustments for Different Standards", page 59, according to the I/O standard used

$C_{\text{LOAD}}\,$  is the capacitive load for the design

F<sub>L</sub> is the capacitance scaling factor

### **Delay Measurement Methodology**

| Standard       | V <sub>L</sub> (1)                            | V <sub>H</sub> (1)                            | Meas.<br>Point   | V <sub>REF</sub><br>Typ <sup>(2)</sup> |

|----------------|-----------------------------------------------|-----------------------------------------------|------------------|----------------------------------------|

| LVTTL          | 0                                             | 3                                             | 1.4              | -                                      |

| LVCMOS2        | 0                                             | 2.5                                           | 1.125            | -                                      |

| PCI33_5        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| PCI33_3        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| PCI66_3        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| GTL            | V <sub>REF</sub> – 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 0.80                                   |

| GTL+           | V <sub>REF</sub> – 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 1.0                                    |

| HSTL Class I   | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.75                                   |

| HSTL Class III | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.90                                   |

| HSTL Class IV  | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.90                                   |

| SSTL3 I and II | V <sub>REF</sub> – 1.0                        | V <sub>REF</sub> + 1.0                        | $V_{REF}$        | 1.5                                    |

| SSTL2 I and II | V <sub>REF</sub> -0.75                        | V <sub>REF</sub> + 0.75                       | $V_{REF}$        | 1.25                                   |

| СТТ            | V <sub>REF</sub> – 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 1.5                                    |

| AGP            | V <sub>REF</sub> –<br>(0.2xV <sub>CCO</sub> ) | V <sub>REF</sub> +<br>(0.2xV <sub>CCO</sub> ) | V <sub>REF</sub> | Per AGP<br>Spec                        |

#### Notes:

- 1. Input waveform switches between V<sub>L</sub> and V<sub>H</sub>.

- 2. Measurements are made at V<sub>REF</sub> Typ, Maximum, and Minimum. Worst-case values are reported.

- I/O parameter measurements are made with the capacitance values shown in the table, "Constants for Calculating TIOOP". See Xilinx application note <u>XAPP179</u> for the appropriate terminations.

- 4. I/O standard measurements are reflected in the IBIS model information except where the IBIS format precludes it.

## Constants for Calculating T<sub>IOOP</sub>

| Standard                          | C <sub>SL</sub> <sup>(1)</sup><br>(pF) | F <sub>L</sub><br>(ns/pF) |

|-----------------------------------|----------------------------------------|---------------------------|

| LVTTL Fast Slew Rate, 2 mA drive  | 35                                     | 0.41                      |

| LVTTL Fast Slew Rate, 4 mA drive  | 35                                     | 0.20                      |

| LVTTL Fast Slew Rate, 6 mA drive  | 35                                     | 0.13                      |

| LVTTL Fast Slew Rate, 8 mA drive  | 35                                     | 0.079                     |

| LVTTL Fast Slew Rate, 12 mA drive | 35                                     | 0.044                     |

| LVTTL Fast Slew Rate, 16 mA drive | 35                                     | 0.043                     |

| LVTTL Fast Slew Rate, 24 mA drive | 35                                     | 0.033                     |

| LVTTL Slow Slew Rate, 2 mA drive  | 35                                     | 0.41                      |

| LVTTL Slow Slew Rate, 4 mA drive  | 35                                     | 0.20                      |

| LVTTL Slow Slew Rate, 6 mA drive  | 35                                     | 0.100                     |

| LVTTL Slow Slew Rate, 8 mA drive  | 35                                     | 0.086                     |

| LVTTL Slow Slew Rate, 12 mA drive | 35                                     | 0.058                     |

| LVTTL Slow Slew Rate, 16 mA drive | 35                                     | 0.050                     |

| LVTTL Slow Slew Rate, 24 mA drive | 35                                     | 0.048                     |

| LVCMOS2                           | 35                                     | 0.041                     |

| PCI 33 MHz 5V                     | 50                                     | 0.050                     |

| PCI 33 MHZ 3.3V                   | 10                                     | 0.050                     |

| PCI 66 MHz 3.3V                   | 10                                     | 0.033                     |

| GTL                               | 0                                      | 0.014                     |

| GTL+                              | 0                                      | 0.017                     |

| HSTL Class I                      | 20                                     | 0.022                     |

| HSTL Class III                    | 20                                     | 0.016                     |

| HSTL Class IV                     | 20                                     | 0.014                     |

| SSTL2 Class I                     | 30                                     | 0.028                     |

| SSTL2 Class II                    | 30                                     | 0.016                     |

| SSTL3 Class I                     | 30                                     | 0.029                     |

| SSTL3 Class II                    | 30                                     | 0.016                     |

| СТТ                               | 20                                     | 0.035                     |

| AGP                               | 10                                     | 0.037                     |

#### Notes:

- 1. I/O parameter measurements are made with the capacitance values shown above. See Xilinx application note <u>XAPP179</u> for the appropriate terminations.

- 2. I/O standard measurements are reflected in the IBIS model information except where the IBIS format precludes it.

## Clock Distribution Guidelines<sup>(1)</sup>

|                       |                                          | Speed    | l Grade |       |

|-----------------------|------------------------------------------|----------|---------|-------|

|                       |                                          | -6       | -5      |       |

| Symbol                | Description                              | Max      | Max     | Units |

| GCLK Clock Skew       |                                          | <u>.</u> |         |       |

| T <sub>GSKEWIOB</sub> | Global clock skew between IOB flip-flops | 0.13     | 0.14    | ns    |

Notes:

1. These clock distribution delays are provided for guidance only. They reflect the delays encountered in a typical design under worst-case conditions. Precise values for a particular design are provided by the timing analyzer.

## **Clock Distribution Switching Characteristics**

T<sub>GPIO</sub> is specified for LVTTL levels. For other standards, adjust T<sub>GPIO</sub> with the values shown in "I/O Standard Global Clock Input Adjustments".

|                   |                                                                       | Speed | Grade |       |

|-------------------|-----------------------------------------------------------------------|-------|-------|-------|

|                   |                                                                       | -6    | -5    |       |

| Symbol            | Description                                                           | Max   | Max   | Units |

| GCLK IOB and Bu   | ffer                                                                  |       |       |       |

| T <sub>GPIO</sub> | Global clock pad to output                                            | 0.7   | 0.8   | ns    |

| T <sub>GIO</sub>  | CLK IOB and Buffer       T <sub>GPIO</sub> Global clock pad to output |       | 0.8   | ns    |

## I/O Standard Global Clock Input Adjustments

Delays associated with a global clock input pad are specified for LVTTL levels. For other standards, adjust the delays by the values shown. A delay adjusted in this way constitutes a worst-case limit.

|                        |                                |                   | Speed |       |       |

|------------------------|--------------------------------|-------------------|-------|-------|-------|

| Symbol                 | Description                    | Standard          | -6    | -5    | Units |

| Data Input Delay       | Adjustments                    |                   |       |       | -     |

| T <sub>GPLVTTL</sub>   | Standard-specific global clock | LVTTL             | 0     | 0     | ns    |

| T <sub>GPLVCMOS2</sub> | input delay adjustments        | LVCMOS2           | -0.04 | -0.05 | ns    |

| T <sub>GPPCI33_3</sub> |                                | PCI, 33 MHz, 3.3V | -0.11 | -0.13 | ns    |

| T <sub>GPPCI33_5</sub> |                                | PCI, 33 MHz, 5.0V | 0.26  | 0.30  | ns    |

| T <sub>GPPCI66_3</sub> |                                | PCI, 66 MHz, 3.3V | -0.11 | -0.13 | ns    |

| T <sub>GPGTL</sub>     |                                | GTL               | 0.80  | 0.84  | ns    |

| T <sub>GPGTLP</sub>    | _                              | GTL+              | 0.71  | 0.73  | ns    |

| T <sub>GPHSTL</sub>    | _                              | HSTL              | 0.63  | 0.64  | ns    |

| T <sub>GPSSTL2</sub>   |                                | SSTL2             | 0.52  | 0.51  | ns    |

| T <sub>GPSSTL3</sub>   | -                              | SSTL3             | 0.56  | 0.55  | ns    |

| T <sub>GPCTT</sub>     |                                | CTT               | 0.62  | 0.62  | ns    |

| T <sub>GPAGP</sub>     |                                | AGP               | 0.54  | 0.53  | ns    |

Notes:

1. Input timing for GPLVTTL is measured at 1.4V. For other I/O standards, see the table "Delay Measurement Methodology," page 60.

## **Package Thermal Characteristics**

Table 39 provides the thermal characteristics for the various Spartan-II FPGA package offerings. This information is also available using the Thermal Query tool on xilinx.com (www.xilinx.com/cgi-bin/thermal/thermal.pl).

The junction-to-case thermal resistance  $(\theta_{JC})$  indicates the difference between the temperature measured on the package body (case) and the die junction temperature per watt of power consumption. The junction-to-board  $(\theta_{JB})$

value similarly reports the difference between the board and junction temperature. The junction-to-ambient ( $\theta_{JA}$ ) value reports the temperature difference between the ambient environment and the junction temperature. The  $\theta_{JA}$  value is reported at different air velocities, measured in linear feet per minute (LFM). The "Still Air (0 LFM)" column shows the  $\theta_{JA}$  value in a system without a fan. The thermal resistance drops with increasing air flow.

|                 |         |                                        |                                          | J                    | unction-to-A<br>at Differen | Ambient (θ <sub>J</sub><br>t Air Flows | )       |         |