# E·XFL

#### AMD Xilinx - XC2S100-6TQ144C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details |

|---------|

|---------|

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | 600                                                         |

| Number of Logic Elements/Cells | 2700                                                        |

| Total RAM Bits                 | 40960                                                       |

| Number of I/O                  | 92                                                          |

| Number of Gates                | 100000                                                      |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 144-LQFP                                                    |

| Supplier Device Package        | 144-TQFP (20x20)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s100-6tq144c |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The three IOB registers function either as edge-triggered D-type flip-flops or as level-sensitive latches. Each IOB has a clock signal (CLK) shared by the three registers and independent Clock Enable (CE) signals for each register. In addition to the CLK and CE control signals, the three registers share a Set/Reset (SR). For each register, this signal can be independently configured as a synchronous Set, a synchronous Reset, an asynchronous Preset, or an asynchronous Clear.

A feature not shown in the block diagram, but controlled by the software, is polarity control. The input and output buffers and all of the IOB control signals have independent polarity controls.

Optional pull-up and pull-down resistors and an optional weak-keeper circuit are attached to each pad. Prior to configuration all outputs not involved in configuration are forced into their high-impedance state. The pull-down resistors and the weak-keeper circuits are inactive, but inputs may optionally be pulled up.

| Table 3: | Standards | Supported by | / I/O ( <sup>-</sup> | Typical Va | lues) |

|----------|-----------|--------------|----------------------|------------|-------|

|----------|-----------|--------------|----------------------|------------|-------|

| I/O Standard                  | Input<br>Reference<br>Voltage<br>(V <sub>REF</sub> ) | Output<br>Source<br>Voltage<br>(V <sub>CCO</sub> ) | Board<br>Termination<br>Voltage<br>(V <sub>TT</sub> ) |

|-------------------------------|------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|

| LVTTL (2-24 mA)               | N/A                                                  | 3.3                                                | N/A                                                   |

| LVCMOS2                       | N/A                                                  | 2.5                                                | N/A                                                   |

| PCI (3V/5V,<br>33 MHz/66 MHz) | N/A                                                  | 3.3                                                | N/A                                                   |

| GTL                           | 0.8                                                  | N/A                                                | 1.2                                                   |

| GTL+                          | 1.0                                                  | N/A                                                | 1.5                                                   |

| HSTL Class I                  | 0.75                                                 | 1.5                                                | 0.75                                                  |

| HSTL Class III                | 0.9                                                  | 1.5                                                | 1.5                                                   |

| HSTL Class IV                 | 0.9                                                  | 1.5                                                | 1.5                                                   |

| SSTL3 Class I<br>and II       | 1.5                                                  | 3.3                                                | 1.5                                                   |

| SSTL2 Class I<br>and II       | 1.25                                                 | 2.5                                                | 1.25                                                  |

| СТТ                           | 1.5                                                  | 3.3                                                | 1.5                                                   |

| AGP-2X                        | 1.32                                                 | 3.3                                                | N/A                                                   |

The activation of pull-up resistors prior to configuration is controlled on a global basis by the configuration mode pins. If the pull-up resistors are not activated, all the pins will float. Consequently, external pull-up or pull-down resistors must be provided on pins required to be at a well-defined logic level prior to configuration. All pads are protected against damage from electrostatic discharge (ESD) and from over-voltage transients. Two forms of over-voltage protection are provided, one that permits 5V compliance, and one that does not. For 5V compliance, a zener-like structure connected to ground turns on when the output rises to approximately 6.5V. When 5V compliance is not required, a conventional clamp diode may be connected to the output supply voltage, V<sub>CCO</sub>. The type of over-voltage protection can be selected independently for each pad.

All Spartan-II FPGA IOBs support IEEE 1149.1-compatible boundary scan testing.

#### Input Path

A buffer In the Spartan-II FPGA IOB input path routes the input signal either directly to internal logic or through an optional input flip-flop.

An optional delay element at the D-input of this flip-flop eliminates pad-to-pad hold time. The delay is matched to the internal clock-distribution delay of the FPGA, and when used, assures that the pad-to-pad hold time is zero.

Each input buffer can be configured to conform to any of the low-voltage signaling standards supported. In some of these standards the input buffer utilizes a user-supplied threshold voltage,  $V_{REF}$ . The need to supply  $V_{REF}$  imposes constraints on which standards can used in close proximity to each other. See "I/O Banking," page 9.

There are optional pull-up and pull-down resistors at each input for use after configuration.

#### **Output Path**

The output path includes a 3-state output buffer that drives the output signal onto the pad. The output signal can be routed to the buffer directly from the internal logic or through an optional IOB output flip-flop.

The 3-state control of the output can also be routed directly from the internal logic or through a flip-flip that provides synchronous enable and disable.

Each output driver can be individually programmed for a wide range of low-voltage signaling standards. Each output buffer can source up to 24 mA and sink up to 48 mA. Drive strength and slew rate controls minimize bus transients.

In most signaling standards, the output high voltage depends on an externally supplied V<sub>CCO</sub> voltage. The need to supply V<sub>CCO</sub> imposes constraints on which standards can be used in close proximity to each other. See "I/O Banking".

An optional weak-keeper circuit is connected to each output. When selected, the circuit monitors the voltage on the pad and weakly drives the pin High or Low to match the input signal. If the pin is connected to a multiple-source signal, the weak keeper holds the signal in its last state if all

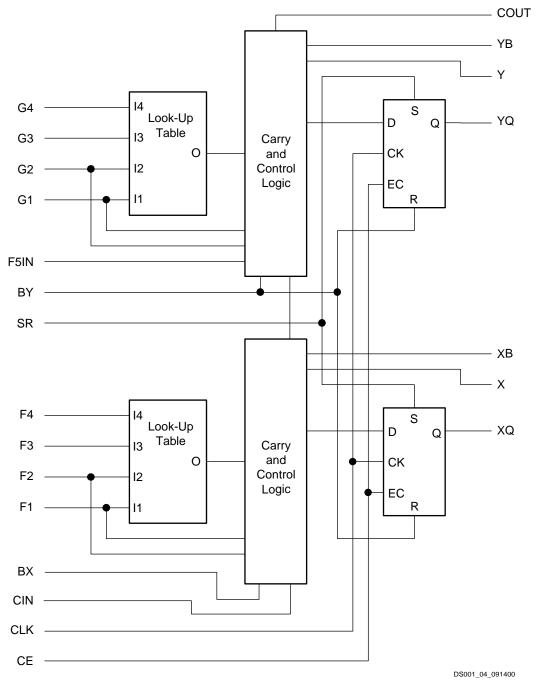

Figure 4: Spartan-II CLB Slice (two identical slices in each CLB)

## Storage Elements

Storage elements in the Spartan-II FPGA slice can be configured either as edge-triggered D-type flip-flops or as level-sensitive latches. The D inputs can be driven either by function generators within the slice or directly from slice inputs, bypassing the function generators.

In addition to Clock and Clock Enable signals, each slice has synchronous set and reset signals (SR and BY). SR forces a storage element into the initialization state specified for it in the configuration. BY forces it into the opposite state. Alternatively, these signals may be configured to operate asynchronously.

All control signals are independently invertible, and are shared by the two flip-flops within the slice.

#### Additional Logic

The F5 multiplexer in each slice combines the function generator outputs. This combination provides either a function generator that can implement any 5-input function, a 4:1 multiplexer, or selected functions of up to nine inputs.

#

# Signals

There are two kinds of pins that are used to configure Spartan-II devices: Dedicated pins perform only specific configuration-related functions; the other pins can serve as general purpose I/Os once user operation has begun.

The dedicated pins comprise the mode pins (M2, M1, M0), the configuration clock pin (CCLK), the PROGRAM pin, the DONE pin and the boundary-scan pins (TDI, TDO, TMS, TCK). Depending on the selected configuration mode, CCLK may be an output generated by the FPGA, or may be generated externally, and provided to the FPGA as an input.

Note that some configuration pins can act as outputs. For correct operation, these pins require a V<sub>CCO</sub> of 3.3V to drive an LVTTL signal or 2.5V to drive an LVCMOS signal. All the relevant pins fall in banks 2 or 3. The  $\overline{\text{CS}}$  and  $\overline{\text{WRITE}}$  pins for Slave Parallel mode are located in bank 1.

For a more detailed description than that given below, see "Pinout Tables" in Module 4 and XAPP176, Spartan-II FPGA Series Configuration and Readback.

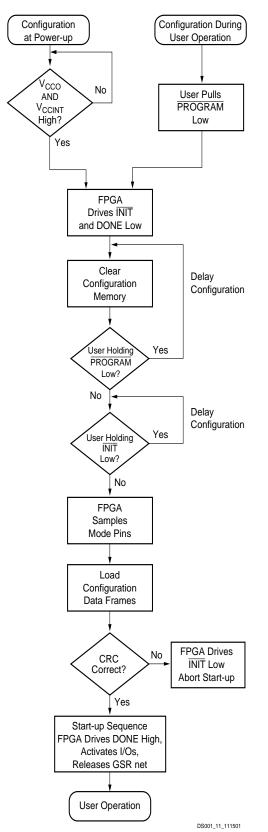

# The Process

The sequence of steps necessary to configure Spartan-II devices are shown in Figure 11. The overall flow can be divided into three different phases.

- Initiating Configuration

- Configuration memory clear

- Loading data frames

- Start-up

The memory clearing and start-up phases are the same for all configuration modes; however, the steps for the loading of data frames are different. Thus, the details for data frame loading are described separately in the sections devoted to each mode.

#### Initiating Configuration

There are two different ways to initiate the configuration process: applying power to the device or asserting the PROGRAM input.

Configuration on power-up occurs automatically unless it is delayed by the user, as described in a separate section below. The waveform for configuration on power-up is shown in Figure 12, page 19. Before configuration can begin,  $V_{CCO}$  Bank 2 must be greater than 1.0V. Furthermore, all  $V_{CCINT}$  power pins must be connected to a 2.5V supply. For more information on delaying configuration, see "Clearing Configuration Memory," page 19.

Once in user operation, the device can be re-configured simply by pulling the PROGRAM pin Low. The device acknowledges the beginning of the configuration process

by driving DONE Low, then enters the memory-clearing phase.

Figure 11: Configuration Flow Diagram

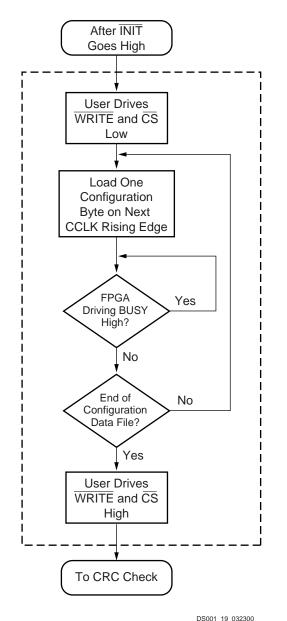

If CCLK is slower than  $\rm F_{CCNH},$  the FPGA will never assert BUSY. In this case, the above handshake is unnecessary, and data can simply be entered into the FPGA every CCLK cycle.

#### Figure 19: Loading Configuration Data for the Slave Parallel Mode

A configuration packet does not have to be written in one continuous stretch, rather it can be split into many write sequences. Each sequence would involve assertion of  $\overline{CS}$ .

In applications where multiple clock cycles may be required to access the configuration data before each byte can be loaded into the Slave Parallel interface, a new byte of data may not be ready for each consecutive CCLK edge. In such a case the  $\overline{CS}$  signal may be de-asserted until the next byte is valid on D0-D7. While  $\overline{CS}$  is High, the Slave Parallel interface does not expect any data and ignores all CCLK transitions. However, to avoid aborting configuration, WRITE must continue to be asserted while CS is asserted.

#### Abort

To abort configuration during a write sequence, de-assert  $\overline{\text{WRITE}}$  while holding  $\overline{\text{CS}}$  Low. The abort operation is initiated at the rising edge of CCLK, as shown in Figure 21, page 26. The device will remain BUSY until the aborted operation is complete. After aborting configuration, data is assumed to be unaligned to word boundaries and the FPGA requires a new synchronization word prior to accepting any new packets.

#### **Boundary-Scan Mode**

In the boundary-scan mode, no nondedicated pins are required, configuration being done entirely through the IEEE 1149.1 Test Access Port.

Configuration through the TAP uses the special CFG\_IN instruction. This instruction allows data input on TDI to be converted into data packets for the internal configuration bus.

The following steps are required to configure the FPGA through the boundary-scan port.

- 1. Load the CFG\_IN instruction into the boundary-scan instruction register (IR)

- 2. Enter the Shift-DR (SDR) state

- 3. Shift a standard configuration bitstream into TDI

- 4. Return to Run-Test-Idle (RTI)

- 5. Load the JSTART instruction into IR

- 6. Enter the SDR state

- 7. Clock TCK through the sequence (the length is programmable)

- 8. Return to RTI

Configuration and readback via the TAP is always available. The boundary-scan mode simply locks out the other modes. The boundary-scan mode is selected by a <10x> on the mode pins (M0, M1, M2).

# Readback

The configuration data stored in the Spartan-II FPGA configuration memory can be readback for verification. Along with the configuration data it is possible to readback the contents of all flip-flops/latches, LUT RAMs, and block RAMs. This capability is used for real-time debugging.

For more detailed information see <u>XAPP176</u>, Spartan-II FPGA Family Configuration and Readback.

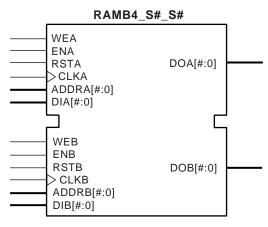

# **Using Block RAM Features**

The Spartan-II FPGA family provides dedicated blocks of on-chip, true dual-read/write port synchronous RAM, with 4096 memory cells. Each port of the block RAM memory can be independently configured as a read/write port, a read port, a write port, and can be configured to a specific data width. The block RAM memory offers new capabilities allowing the FPGA designer to simplify designs.

## **Operating Modes**

Block RAM memory supports two operating modes.

- Read Through

- Write Back

#### Read Through (One Clock Edge)

The read address is registered on the read port clock edge and data appears on the output after the RAM access time. Some memories may place the latch/register at the outputs depending on the desire to have a faster clock-to-out versus setup time. This is generally considered to be an inferior solution since it changes the read operation to an asynchronous function with the possibility of missing an address/control line transition during the generation of the read pulse clock.

#### Write Back (One Clock Edge)

The write address is registered on the write port clock edge and the data input is written to the memory and mirrored on the write port input.

## **Block RAM Characteristics**

- 1. All inputs are registered with the port clock and have a setup to clock timing specification.

- 2. All outputs have a read through or write back function depending on the state of the port WE pin. The outputs relative to the port clock are available after the clock-to-out timing specification.

- 3. The block RAM are true SRAM memories and do not have a combinatorial path from the address to the output. The LUT cells in the CLBs are still available with this function.

- 4. The ports are completely independent from each other (*i.e.*, clocking, control, address, read/write function, and data width) without arbitration.

- 5. A write operation requires only one clock edge.

- 6. A read operation requires only one clock edge.

The output ports are latched with a self timed circuit to guarantee a glitch free read. The state of the output port will not change until the port executes another read or write operation.

#### **Library Primitives**

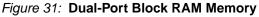

Figure 31 and Figure 32 show the two generic library block RAM primitives. Table 11 describes all of the available primitives for synthesis and simulation.

DS001\_31\_061200

DS001\_32\_061200

Figure 32: Single-Port Block RAM Memory

#### Table 11: Available Library Primitives

| Primitive    | Port A Width | Port B Width |

|--------------|--------------|--------------|

| RAMB4_S1     | 1            | N/A          |

| RAMB4_S1_S1  |              | 1            |

| RAMB4_S1_S2  |              | 2            |

| RAMB4_S1_S4  |              | 4            |

| RAMB4_S1_S8  |              | 8            |

| RAMB4_S1_S16 |              | 16           |

| RAMB4_S2     | 2            | N/A          |

| RAMB4_S2_S2  |              | 2            |

| RAMB4_S2_S4  |              | 4            |

| RAMB4_S2_S8  |              | 8            |

| RAMB4_S2_S16 |              | 16           |

At the third rising edge of CLKA, the  $T_{BCCS}$  parameter is violated with two writes to memory location 0x0F. The DOA and DOB busses reflect the contents of the DIA and DIB busses, but the stored value at 0x7E is invalid.

At the fourth rising edge of CLKA, a read operation is performed at memory location 0x0F and invalid data is present on the DOA bus. Port B also executes a read operation to memory location 0x0F and also reads invalid data.

At the fifth rising edge of CLKA a read operation is performed that does not violate the  $T_{BCCS}$  parameter to the previous write of 0x7E by Port B. THe DOA bus reflects the recently written value by Port B.

#### Initialization

The block RAM memory can initialize during the device configuration sequence. The 16 initialization properties of 64 hex values each (a total of 4096 bits) set the initialization of each RAM. These properties appear in Table 14. Any initialization properties not explicitly set configure as zeros. Partial initialization strings pad with zeros. Initialization strings greater than 64 hex values generate an error. The RAMs can be simulated with the initialization values using generics in VHDL simulators and parameters in Verilog simulators.

#### **Initialization in VHDL**

The block RAM structures may be initialized in VHDL for both simulation and synthesis for inclusion in the EDIF output file. The simulation of the VHDL code uses a generic to pass the initialization.

## **Initialization in Verilog**

The block RAM structures may be initialized in Verilog for both simulation and synthesis for inclusion in the EDIF output file. The simulation of the Verilog code uses a defparam to pass the initialization.

#### **Block Memory Generation**

The CORE Generator<sup>™</sup> software generates memory structures using the block RAM features. This program outputs VHDL or Verilog simulation code templates and an EDIF file for inclusion in a design.

| Property | Memory Cells |

|----------|--------------|

| INIT_00  | 255 to 0     |

| INIT_01  | 511 to 256   |

| INIT_02  | 767 to 512   |

| INIT_03  | 1023 to 768  |

| INIT_04  | 1279 to 1024 |

|          |              |

| Property | Memory Cells |

|----------|--------------|

| INIT_05  | 1535 to 1280 |

| INIT_06  | 1791 to 1536 |

| INIT_07  | 2047 to 1792 |

| INIT_08  | 2303 to 2048 |

| INIT_09  | 2559 to 2304 |

| INIT_0a  | 2815 to 2560 |

| INIT_0b  | 3071 to 2816 |

| INIT_0c  | 3327 to 3072 |

| INIT_0d  | 3583 to 3328 |

| INIT_0e  | 3839 to 3584 |

| INIT_0f  | 4095 to 3840 |

For design examples and more information on using the Block RAM, see <u>XAPP173</u>, Using Block SelectRAM+ Memory in Spartan-II FPGAs.

# **Using Versatile I/O**

The Spartan-II FPGA family includes a highly configurable, high-performance I/O resource called Versatile I/O to provide support for a wide variety of I/O standards. The Versatile I/O resource is a robust set of features including programmable control of output drive strength, slew rate, and input delay and hold time. Taking advantage of the flexibility and Versatile I/O features and the design considerations described in this document can improve and simplify system level design.

## Introduction

As FPGAs continue to grow in size and capacity, the larger and more complex systems designed for them demand an increased variety of I/O standards. Furthermore, as system clock speeds continue to increase, the need for high-performance I/O becomes more important. While chip-to-chip delays have an increasingly substantial impact on overall system speed, the task of achieving the desired system performance becomes more difficult with the proliferation of low-voltage I/O standards. Versatile I/O, the revolutionary input/output resources of Spartan-II devices, has resolved this potential problem by providing a highly configurable, high-performance alternative to the I/O resources of more conventional programmable devices. The Spartan-II FPGA Versatile I/O features combine the flexibility and time-to-market advantages of programmable logic with the high performance previously available only with ASICs and custom ICs.

Each Versatile I/O block can support up to 16 I/O standards. Supporting such a variety of I/O standards allows the

support of a wide variety of applications, from general purpose standard applications to high-speed low-voltage memory busses.

Versatile I/O blocks also provide selectable output drive strengths and programmable slew rates for the LVTTL output buffers, as well as an optional, programmable weak pull-up, weak pull-down, or weak "keeper" circuit ideal for use in external bussing applications.

Each Input/Output Block (IOB) includes three registers, one each for the input, output, and 3-state signals within the IOB. These registers are optionally configurable as either a D-type flip-flop or as a level sensitive latch.

The input buffer has an optional delay element used to guarantee a zero hold time requirement for input signals registered within the IOB.

The Versatile I/O features also provide dedicated resources for input reference voltage ( $V_{REF}$ ) and output source voltage ( $V_{CCO}$ ), along with a convenient banking system that simplifies board design.

By taking advantage of the built-in features and wide variety of I/O standards supported by the Versatile I/O features, system-level design and board design can be greatly simplified and improved.

## **Fundamentals**

Modern bus applications, pioneered by the largest and most influential companies in the digital electronics industry, are commonly introduced with a new I/O standard tailored specifically to the needs of that application. The bus I/O standards provide specifications to other vendors who create products designed to interface with these applications. Each standard often has its own specifications for current, voltage, I/O buffering, and termination techniques.

The ability to provide the flexibility and time-to-market advantages of programmable logic is increasingly dependent on the capability of the programmable logic device to support an ever increasing variety of I/O standards

The Versatile I/O resources feature highly configurable input and output buffers which provide support for a wide variety of I/O standards. As shown in Table 15, each buffer type can support a variety of voltage requirements.

# Table 15: Versatile I/O Supported Standards (Typical Values)

| ,                             | 1                                                    |                                                    | , , , , , , , , , , , , , , , , , , , ,               |

|-------------------------------|------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|

| I/O Standard                  | Input<br>Reference<br>Voltage<br>(V <sub>REF</sub> ) | Output<br>Source<br>Voltage<br>(V <sub>CCO</sub> ) | Board<br>Termination<br>Voltage<br>(V <sub>TT</sub> ) |

| LVTTL (2-24 mA)               | N/A                                                  | 3.3                                                | N/A                                                   |

| LVCMOS2                       | N/A                                                  | 2.5                                                | N/A                                                   |

| PCI (3V/5V,<br>33 MHz/66 MHz) | N/A                                                  | 3.3                                                | N/A                                                   |

| GTL                           | 0.8                                                  | N/A                                                | 1.2                                                   |

| GTL+                          | 1.0                                                  | N/A                                                | 1.5                                                   |

| HSTL Class I                  | 0.75                                                 | 1.5                                                | 0.75                                                  |

| HSTL Class III                | 0.9                                                  | 1.5                                                | 1.5                                                   |

| HSTL Class IV                 | 0.9                                                  | 1.5                                                | 1.5                                                   |

| SSTL3 Class I<br>and II       | 1.5                                                  | 3.3                                                | 1.5                                                   |

| SSTL2 Class I<br>and II       | 1.25                                                 | 2.5                                                | 1.25                                                  |

| CTT                           | 1.5                                                  | 3.3                                                | 1.5                                                   |

| AGP-2X                        | 1.32                                                 | 3.3                                                | N/A                                                   |

## **Overview of Supported I/O Standards**

This section provides a brief overview of the I/O standards supported by all Spartan-II devices.

While most I/O standards specify a range of allowed voltages, this document records typical voltage values only. Detailed information on each specification may be found on the Electronic Industry Alliance JEDEC website at <a href="http://www.jedec.org">http://www.jedec.org</a>. For more details on the I/O standards and termination application examples, see <a href="http://www.seetandards">XAPP179</a>, "Using SelectIO Interfaces in Spartan-II and Spartan-IIE FPGAs."

## LVTTL — Low-Voltage TTL

The Low-Voltage TTL (LVTTL) standard is a general purpose EIA/JESDSA standard for 3.3V applications that uses an LVTTL input buffer and a Push-Pull output buffer. This standard requires a 3.3V output source voltage ( $V_{CCO}$ ), but does not require the use of a reference voltage ( $V_{REF}$ ) or a termination voltage ( $V_{TT}$ ).

#### LVCMOS2 — Low-Voltage CMOS for 2.5V

The Low-Voltage CMOS for 2.5V or lower (LVCMOS2) standard is an extension of the LVCMOS standard (JESD 8.5) used for general purpose 2.5V applications. This standard requires a 2.5V output source voltage ( $V_{CCO}$ ), but does not require the use of a reference voltage ( $V_{REF}$ ) or a board termination voltage ( $V_{TT}$ ).

the LOC property is described below. Table 16 summarizes the input standards compatibility requirements.

An optional delay element is associated with each IBUF. When the IBUF drives a flip-flop within the IOB, the delay element by default activates to ensure a zero hold-time requirement. The NODELAY=TRUE property overrides this default.

When the IBUF does not drive a flip-flop within the IOB, the delay element de-activates by default to provide higher performance. To delay the input signal, activate the delay element with the DELAY=TRUE property.

DS001\_03\_060100

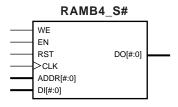

Figure 36: I/O Banks

# Table 16: Xilinx Input Standards CompatibilityRequirements

| Rule 1 | All differential amplifier input signals within a bank are required to be of the same standard.         |

|--------|---------------------------------------------------------------------------------------------------------|

| Rule 2 | There are no placement restrictions for inputs with standards that require a single-ended input buffer. |

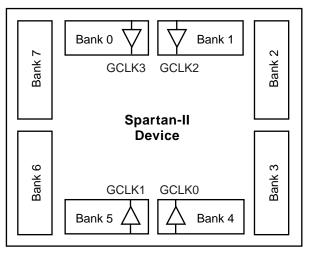

#### IBUFG

Signals used as high fanout clock inputs to the Spartan-II device should drive a global clock input buffer (IBUFG) via an external input port in order to take advantage of one of the four dedicated global clock distribution networks. The output of the IBUFG primitive can only drive a CLKDLL, CLKDLLHF, or a BUFG primitive. The generic IBUFG primitive appears in Figure 37.

DS001\_37\_061200

Figure 37: Global Clock Input Buffer (IBUFG) Primitive

With no extension or property specified for the generic IBUFG primitive, the assumed standard is LVTTL.

The voltage reference signal is "banked" within the Spartan-II device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 36 for a representation of the I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input.

IBUFG placement restrictions require any differential amplifier input signals within a bank be of the same standard. The LOC property can specify a location for the IBUFG.

As an added convenience, the BUFGP can be used to instantiate a high fanout clock input. The BUFGP primitive represents a combination of the LVTTL IBUFG and BUFG primitives, such that the output of the BUFGP can connect directly to the clock pins throughout the design.

The Spartan-II FPGA BUFGP primitive can only be placed in a global clock pad location. The LOC property can specify a location for the BUFGP.

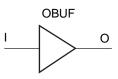

#### OBUF

An OBUF must drive outputs through an external output port. The generic output buffer (OBUF) primitive appears in Figure 38.

DS001\_38\_061200

#### Figure 38: Output Buffer (OBUF) Primitive

With no extension or property specified for the generic OBUF primitive, the assumed standard is slew rate limited LVTTL with 12 mA drive strength.

The LVTTL OBUF additionally can support one of two slew rate modes to minimize bus transients. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals.

#### SSTL3 Class I

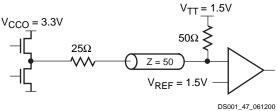

A sample circuit illustrating a valid termination technique for SSTL3\_I appears in Figure 47. DC voltage specifications appear in Table 25 for the SSTL3\_I standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

#### SSTL3 Class I

Figure 47: Terminated SSTL3 Class I

| Table 2 | 25: | SSTL3_ | I Voltage | Specifications |

|---------|-----|--------|-----------|----------------|

|---------|-----|--------|-----------|----------------|

| Parameter                               | Min     | Тур | Max                |

|-----------------------------------------|---------|-----|--------------------|

| V <sub>CCO</sub>                        | 3.0     | 3.3 | 3.6                |

| $V_{REF} = 0.45 \times V_{CCO}$         | 1.3     | 1.5 | 1.7                |

| V <sub>TT</sub> = V <sub>REF</sub>      | 1.3     | 1.5 | 1.7                |

| $V_{IH} \ge V_{REF} + 0.2$              | 1.5     | 1.7 | 3.9 <sup>(1)</sup> |

| $V_{IL} \leq V_{REF} - 0.2$             | -0.3(2) | 1.3 | 1.5                |

| $V_{OH} \ge V_{REF} + 0.6$              | 1.9     | -   | -                  |

| $V_{OL} \leq V_{REF} - 0.6$             | -       | -   | 1.1                |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -8      | -   | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 8       | -   | -                  |

#### Notes:

1.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3.

2. V<sub>IL</sub> minimum does not conform to the formula.

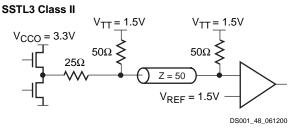

#### SSTL3 Class II

A sample circuit illustrating a valid termination technique for SSTL3\_II appears in Figure 48. DC voltage specifications appear in Table 26 for the SSTL3\_II standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 48: Terminated SSTL3 Class II

#### Table 26: SSTL3\_II Voltage Specifications

| Parameter                                | Min     | Тур | Max                |

|------------------------------------------|---------|-----|--------------------|

| V <sub>CCO</sub>                         | 3.0     | 3.3 | 3.6                |

| $V_{REF} = 0.45 \times V_{CCO}$          | 1.3     | 1.5 | 1.7                |

| V <sub>TT</sub> = V <sub>REF</sub>       | 1.3     | 1.5 | 1.7                |

| V <sub>IH</sub> ≥ V <sub>REF</sub> + 0.2 | 1.5     | 1.7 | 3.9 <sup>(1)</sup> |

| $V_{IL} \leq V_{REF} - 0.2$              | -0.3(2) | 1.3 | 1.5                |

| $V_{OH} \ge V_{REF} + 0.8$               | 2.1     | -   | -                  |

| $V_{OL} \leq V_{REF} - 0.8$              | -       | -   | 0.9                |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)  | -16     | -   | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA)  | 16      | -   | -                  |

Notes:

1.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3

2. V<sub>IL</sub> minimum does not conform to the formula

# IOB Input Switching Characteristics<sup>(1)</sup>

Input delays associated with the pad are specified for LVTTL levels. For other standards, adjust the delays with the values shown in "IOB Input Delay Adjustments for Different Standards," page 57.

|                                           |                                                  |          |            | Speed | d Grade    |      |       |

|-------------------------------------------|--------------------------------------------------|----------|------------|-------|------------|------|-------|

|                                           |                                                  |          | -6         |       | -5         |      | 1     |

| Symbol                                    | Description                                      | Device   | Min        | Max   | Min        | Max  | Units |

| Propagation Delays                        |                                                  | ·        |            |       |            |      |       |

| T <sub>IOPI</sub>                         | Pad to I output, no delay                        | All      | -          | 0.8   | -          | 1.0  | ns    |

| T <sub>IOPID</sub>                        | Pad to I output, with delay                      | All      | -          | 1.5   | -          | 1.8  | ns    |

| T <sub>IOPLI</sub>                        | Pad to output IQ via transparent latch, no delay | All      | -          | 1.7   | -          | 2.0  | ns    |

| T <sub>IOPLID</sub>                       | Pad to output IQ via transparent latch,          | XC2S15   | -          | 3.8   | -          | 4.5  | ns    |

|                                           | with delay                                       | XC2S30   | -          | 3.8   | -          | 4.5  | ns    |

|                                           |                                                  | XC2S50   | -          | 3.8   | -          | 4.5  | ns    |

|                                           |                                                  | XC2S100  | -          | 3.8   | -          | 4.5  | ns    |

|                                           |                                                  | XC2S150  | -          | 4.0   | -          | 4.7  | ns    |

|                                           |                                                  | XC2S200  | -          | 4.0   | -          | 4.7  | ns    |

| Sequential Delays                         | 1                                                | 1        |            |       | 1          |      |       |

| TIOCKIQ                                   | Clock CLK to output IQ                           | All      | -          | 0.7   | -          | 0.8  | ns    |

| Setup/Hold Times w                        | ith Respect to Clock CLK <sup>(2)</sup>          | <b>I</b> | 1          |       |            |      |       |

| T <sub>IOPICK</sub> / T <sub>IOICKP</sub> | Pad, no delay                                    | All      | 1.7 / 0    | -     | 1.9/0      | -    | ns    |

| TIOPICKD / TIOICKPD                       | Pad, with delay <sup>(1)</sup>                   | XC2S15   | 3.8 / 0    | -     | 4.4 / 0    | -    | ns    |

|                                           |                                                  | XC2S30   | 3.8 / 0    | -     | 4.4 / 0    | -    | ns    |

|                                           |                                                  | XC2S50   | 3.8 / 0    | -     | 4.4 / 0    | -    | ns    |

|                                           |                                                  | XC2S100  | 3.8 / 0    | -     | 4.4 / 0    | -    | ns    |

|                                           |                                                  | XC2S150  | 3.9 / 0    | -     | 4.6 / 0    | -    | ns    |

|                                           |                                                  | XC2S200  | 3.9 / 0    | -     | 4.6 / 0    | -    | ns    |

| TIOICECK / TIOCKICE                       | ICE input                                        | All      | 0.9 / 0.01 | -     | 0.9 / 0.01 | -    | ns    |

| Set/Reset Delays                          |                                                  |          |            |       | 1          | 1    |       |

| T <sub>IOSRCKI</sub>                      | SR input (IFF, synchronous)                      | All      | -          | 1.1   | -          | 1.2  | ns    |

| T <sub>IOSRIQ</sub>                       | SR input to IQ (asynchronous)                    | All      | -          | 1.5   | -          | 1.7  | ns    |

| T <sub>GSRQ</sub>                         | GSR to output IQ                                 | All      | -          | 9.9   | -          | 11.7 | ns    |

Notes:

1. Input timing for LVTTL is measured at 1.4V. For other I/O standards, see the table "Delay Measurement Methodology," page 60.

2. A zero hold time listing indicates no hold time or a negative hold time.

# IOB Input Delay Adjustments for Different Standards<sup>(1)</sup>

Input delays associated with the pad are specified for LVTTL. For other standards, adjust the delays by the values shown. A delay adjusted in this way constitutes a worst-case limit.

|                       |                                    |                   | Speed Grade |       |       |

|-----------------------|------------------------------------|-------------------|-------------|-------|-------|

| Symbol                | Description                        | Standard          | -6          | -5    | Units |

| Data Input            | Delay Adjustments                  |                   |             | ·     |       |

| T <sub>ILVTTL</sub>   | Standard-specific data input delay | LVTTL             | 0           | 0     | ns    |

| T <sub>ILVCMOS2</sub> | adjustments                        | LVCMOS2           | -0.04       | -0.05 | ns    |

| T <sub>IPCI33_3</sub> | -                                  | PCI, 33 MHz, 3.3V | -0.11       | -0.13 | ns    |

| T <sub>IPCI33_5</sub> | -                                  | PCI, 33 MHz, 5.0V | 0.26        | 0.30  | ns    |

| T <sub>IPCI66_3</sub> | -                                  | PCI, 66 MHz, 3.3V | -0.11       | -0.13 | ns    |

| T <sub>IGTL</sub>     | -                                  | GTL               | 0.20        | 0.24  | ns    |

| T <sub>IGTLP</sub>    | -                                  | GTL+              | 0.11        | 0.13  | ns    |

| T <sub>IHSTL</sub>    | -                                  | HSTL              | 0.03        | 0.04  | ns    |

| T <sub>ISSTL2</sub>   | -                                  | SSTL2             | -0.08       | -0.09 | ns    |

| T <sub>ISSTL3</sub>   | -                                  | SSTL3             | -0.04       | -0.05 | ns    |

| T <sub>ICTT</sub>     |                                    | CTT               | 0.02        | 0.02  | ns    |

| T <sub>IAGP</sub>     | ]                                  | AGP               | -0.06       | -0.07 | ns    |

Notes:

1. Input timing for LVTTL is measured at 1.4V. For other I/O standards, see the table "Delay Measurement Methodology," page 60.

### **IOB Output Switching Characteristics**

Output delays terminating at a pad are specified for LVTTL with 12 mA drive and fast slew rate. For other standards, adjust the delays with the values shown in "IOB Output Delay Adjustments for Different Standards," page 59.

|                                                |                                                                    |            |     | Speed Grade |      |       |  |  |

|------------------------------------------------|--------------------------------------------------------------------|------------|-----|-------------|------|-------|--|--|

|                                                |                                                                    | -6         |     | -5          |      | 1     |  |  |

| Symbol                                         | Description                                                        | Min        | Max | Min         | Max  | Units |  |  |

| Propagation Delay                              | S                                                                  |            |     | 1           |      |       |  |  |

| T <sub>IOOP</sub>                              | O input to pad                                                     | -          | 2.9 | -           | 3.4  | ns    |  |  |

| T <sub>IOOLP</sub>                             | O input to pad via transparent latch                               | -          | 3.4 | -           | 4.0  | ns    |  |  |

| 3-state Delays                                 | 1                                                                  | 1          |     | 1           |      | -1    |  |  |

| T <sub>IOTHZ</sub>                             | T input to pad high-impedance <sup>(1)</sup>                       | -          | 2.0 | -           | 2.3  | ns    |  |  |

| T <sub>IOTON</sub>                             | T input to valid data on pad                                       | -          | 3.0 | -           | 3.6  | ns    |  |  |

| T <sub>IOTLPHZ</sub>                           | T input to pad high impedance via transparent latch <sup>(1)</sup> | -          | 2.5 | -           | 2.9  | ns    |  |  |

| T <sub>IOTLPON</sub>                           | T input to valid data on pad via transparent latch                 | -          | 3.5 | -           | 4.2  | ns    |  |  |

| T <sub>GTS</sub>                               | GTS to pad high impedance <sup>(1)</sup>                           | -          | 5.0 | -           | 5.9  | ns    |  |  |

| Sequential Delays                              | ;<br>;                                                             |            |     |             |      | 1     |  |  |

| T <sub>IOCKP</sub>                             | Clock CLK to pad                                                   | -          | 2.9 | -           | 3.4  | ns    |  |  |

| T <sub>IOCKHZ</sub>                            | Clock CLK to pad high impedance (synchronous) <sup>(1)</sup>       | -          | 2.3 | -           | 2.7  | ns    |  |  |

| T <sub>IOCKON</sub>                            | Clock CLK to valid data on pad (synchronous)                       | -          | 3.3 | -           | 4.0  | ns    |  |  |

|                                                | with Respect to Clock CLK <sup>(2)</sup>                           |            |     |             |      |       |  |  |

| Т <sub>ЮОСК</sub> / Т <sub>ЮСКО</sub>          | O input                                                            | 1.1/0      | -   | 1.3/0       | -    | ns    |  |  |

| T <sub>IOOCECK</sub> /<br>T <sub>IOCKOCE</sub> | OCE input                                                          | 0.9 / 0.01 | -   | 0.9 / 0.01  | -    | ns    |  |  |

| T <sub>IOSRCKO</sub> /<br>T <sub>IOCKOSR</sub> | SR input (OFF)                                                     | 1.2/0      | -   | 1.3 / 0     | -    | ns    |  |  |

| T <sub>IOTCK</sub> / T <sub>IOCKT</sub>        | 3-state setup times, T input                                       | 0.8/0      | -   | 0.9/0       | -    | ns    |  |  |

| T <sub>IOTCECK</sub> /<br>T <sub>IOCKTCE</sub> | 3-state setup times, TCE input                                     | 1.0/0      | -   | 1.0 / 0     | -    | ns    |  |  |

| T <sub>IOSRCKT</sub> /<br>T <sub>IOCKTSR</sub> | 3-state setup times, SR input (TFF)                                | 1.1/0      | -   | 1.2/0       | -    | ns    |  |  |

| Set/Reset Delays                               | 1                                                                  | 1          |     | 1           |      | _1    |  |  |

| T <sub>IOSRP</sub>                             | SR input to pad (asynchronous)                                     | -          | 3.7 | -           | 4.4  | ns    |  |  |

| T <sub>IOSRHZ</sub>                            | SR input to pad high impedance (asynchronous) <sup>(1)</sup>       | -          | 3.1 | -           | 3.7  | ns    |  |  |

| T <sub>IOSRON</sub>                            | SR input to valid data on pad (asynchronous)                       | -          | 4.1 | -           | 4.9  | ns    |  |  |

| T <sub>IOGSRQ</sub>                            | GSR to pad                                                         | -          | 9.9 | -           | 11.7 | ns    |  |  |

Notes:

1. Three-state turn-off delays should not be adjusted.

2. A zero hold time listing indicates no hold time or a negative hold time.

# Calculation of T<sub>IOOP</sub> as a Function of Capacitance

$T_{\rm IOOP}$  is the propagation delay from the O Input of the IOB to the pad. The values for  $T_{\rm IOOP}$  are based on the standard capacitive load (C<sub>SL</sub>) for each I/O standard as listed in the table "Constants for Calculating TIOOP", below.

For other capacitive loads, use the formulas below to calculate an adjusted propagation delay,  $T_{IOOP1}$ .

$$T_{IOOP1} = T_{IOOP} + Adj + (C_{LOAD} - C_{SL}) * F_{L}$$

Where:

Adj is selected from "IOB Output Delay Adjustments for Different Standards", page 59, according to the I/O standard used

$C_{\text{LOAD}}\,$  is the capacitive load for the design

F<sub>L</sub> is the capacitance scaling factor

#### **Delay Measurement Methodology**

| Standard       | V <sub>L</sub> (1)                            | V <sub>H</sub> (1)                            | Meas.<br>Point   | V <sub>REF</sub><br>Typ <sup>(2)</sup> |

|----------------|-----------------------------------------------|-----------------------------------------------|------------------|----------------------------------------|

| LVTTL          | 0                                             | 3                                             | 1.4              | -                                      |

| LVCMOS2        | 0                                             | 2.5                                           | 1.125            | -                                      |

| PCI33_5        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| PCI33_3        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| PCI66_3        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| GTL            | V <sub>REF</sub> – 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 0.80                                   |

| GTL+           | V <sub>REF</sub> – 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 1.0                                    |

| HSTL Class I   | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.75                                   |

| HSTL Class III | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.90                                   |

| HSTL Class IV  | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.90                                   |

| SSTL3 I and II | V <sub>REF</sub> – 1.0                        | V <sub>REF</sub> + 1.0                        | $V_{REF}$        | 1.5                                    |

| SSTL2 I and II | V <sub>REF</sub> -0.75                        | V <sub>REF</sub> + 0.75                       | $V_{REF}$        | 1.25                                   |

| СТТ            | V <sub>REF</sub> – 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 1.5                                    |

| AGP            | V <sub>REF</sub> –<br>(0.2xV <sub>CCO</sub> ) | V <sub>REF</sub> +<br>(0.2xV <sub>CCO</sub> ) | V <sub>REF</sub> | Per AGP<br>Spec                        |

#### Notes:

- 1. Input waveform switches between V<sub>L</sub> and V<sub>H</sub>.

- 2. Measurements are made at V<sub>REF</sub> Typ, Maximum, and Minimum. Worst-case values are reported.

- I/O parameter measurements are made with the capacitance values shown in the table, "Constants for Calculating TIOOP". See Xilinx application note <u>XAPP179</u> for the appropriate terminations.

- 4. I/O standard measurements are reflected in the IBIS model information except where the IBIS format precludes it.

#### Constants for Calculating T<sub>IOOP</sub>

| Standard                          | C <sub>SL</sub> <sup>(1)</sup><br>(pF) | F <sub>L</sub><br>(ns/pF) |

|-----------------------------------|----------------------------------------|---------------------------|

| LVTTL Fast Slew Rate, 2 mA drive  | 35                                     | 0.41                      |

| LVTTL Fast Slew Rate, 4 mA drive  | 35                                     | 0.20                      |

| LVTTL Fast Slew Rate, 6 mA drive  | 35                                     | 0.13                      |

| LVTTL Fast Slew Rate, 8 mA drive  | 35                                     | 0.079                     |

| LVTTL Fast Slew Rate, 12 mA drive | 35                                     | 0.044                     |

| LVTTL Fast Slew Rate, 16 mA drive | 35                                     | 0.043                     |

| LVTTL Fast Slew Rate, 24 mA drive | 35                                     | 0.033                     |

| LVTTL Slow Slew Rate, 2 mA drive  | 35                                     | 0.41                      |

| LVTTL Slow Slew Rate, 4 mA drive  | 35                                     | 0.20                      |

| LVTTL Slow Slew Rate, 6 mA drive  | 35                                     | 0.100                     |

| LVTTL Slow Slew Rate, 8 mA drive  | 35                                     | 0.086                     |

| LVTTL Slow Slew Rate, 12 mA drive | 35                                     | 0.058                     |

| LVTTL Slow Slew Rate, 16 mA drive | 35                                     | 0.050                     |

| LVTTL Slow Slew Rate, 24 mA drive | 35                                     | 0.048                     |

| LVCMOS2                           | 35                                     | 0.041                     |

| PCI 33 MHz 5V                     | 50                                     | 0.050                     |

| PCI 33 MHZ 3.3V                   | 10                                     | 0.050                     |

| PCI 66 MHz 3.3V                   | 10                                     | 0.033                     |

| GTL                               | 0                                      | 0.014                     |

| GTL+                              | 0                                      | 0.017                     |

| HSTL Class I                      | 20                                     | 0.022                     |

| HSTL Class III                    | 20                                     | 0.016                     |

| HSTL Class IV                     | 20                                     | 0.014                     |

| SSTL2 Class I                     | 30                                     | 0.028                     |

| SSTL2 Class II                    | 30                                     | 0.016                     |

| SSTL3 Class I                     | 30                                     | 0.029                     |

| SSTL3 Class II                    | 30                                     | 0.016                     |

| СТТ                               | 20                                     | 0.035                     |

| AGP                               | 10                                     | 0.037                     |

#### Notes:

- 1. I/O parameter measurements are made with the capacitance values shown above. See Xilinx application note <u>XAPP179</u> for the appropriate terminations.

- 2. I/O standard measurements are reflected in the IBIS model information except where the IBIS format precludes it.

## **DLL Timing Parameters**

All devices are 100 percent functionally tested. Because of the difficulty in directly measuring many internal timing parameters, those parameters are derived from benchmark timing patterns. The following guidelines reflect worst-case values across the recommended operating conditions.

|                      |                                    | Speed Grade |     |     |     |       |

|----------------------|------------------------------------|-------------|-----|-----|-----|-------|

|                      |                                    |             | ·6  | -   | ·5  |       |

| Symbol               | Description                        | Min         | Max | Min | Max | Units |

| F <sub>CLKINHF</sub> | Input clock frequency (CLKDLLHF)   | 60          | 200 | 60  | 180 | MHz   |

| F <sub>CLKINLF</sub> | Input clock frequency (CLKDLL)     | 25          | 100 | 25  | 90  | MHz   |

| T <sub>DLLPWHF</sub> | Input clock pulse width (CLKDLLHF) | 2.0         | -   | 2.4 | -   | ns    |

| T <sub>DLLPWLF</sub> | Input clock pulse width (CLKDLL)   | 2.5         | -   | 3.0 | -   | ns    |

#### **DLL Clock Tolerance, Jitter, and Phase Information**

All DLL output jitter and phase specifications were determined through statistical measurement at the package pins using a clock mirror configuration and matched drivers.

Figure 52, page 63, provides definitions for various parameters in the table below.

|                     |                                                                |                               | CLKE | DLLHF | CLK | DLL  |       |

|---------------------|----------------------------------------------------------------|-------------------------------|------|-------|-----|------|-------|

| Symbol              | Description                                                    | F <sub>CLKIN</sub>            | Min  | Max   | Min | Max  | Units |

| T <sub>IPTOL</sub>  | Input clock period tolerance                                   |                               | -    | 1.0   | -   | 1.0  | ns    |

| T <sub>IJITCC</sub> | Input clock jitter tolerance (cycle-to-cycle)                  |                               | -    | ±150  | -   | ±300 | ps    |

| T <sub>LOCK</sub>   | Time required for DLL to acquire lock                          | > 60 MHz                      | -    | 20    | -   | 20   | μs    |

|                     |                                                                | 50-60 MHz                     | -    | -     | -   | 25   | μs    |

|                     |                                                                | 40-50 MHz                     | -    | -     | -   | 50   | μs    |

|                     |                                                                | 30-40 MHz                     | -    | -     | -   | 90   | μs    |

|                     |                                                                | 25-30 MHz                     | -    | -     | -   | 120  | μs    |

| T <sub>OJITCC</sub> | Output jitter (cycle-to-cycle) for any DLL clock c             | output <sup>(1)</sup>         | -    | ±60   | -   | ±60  | ps    |

| T <sub>PHIO</sub>   | Phase offset between CLKIN and CLKO <sup>(2)</sup>             |                               | -    | ±100  | -   | ±100 | ps    |

| T <sub>PHOO</sub>   | Phase offset between clock outputs on the DLL <sup>(3)</sup>   |                               | -    | ±140  | -   | ±140 | ps    |

| T <sub>PHIOM</sub>  | Maximum phase difference between CLKIN and CLKO <sup>(4)</sup> |                               | -    | ±160  | -   | ±160 | ps    |

| T <sub>PHOOM</sub>  | Maximum phase difference between clock outp                    | uts on the DLL <sup>(5)</sup> | -    | ±200  | -   | ±200 | ps    |

Notes:

1. **Output Jitter** is cycle-to-cycle jitter measured on the DLL output clock, *excluding* input clock jitter.

2. Phase Offset between CLKIN and CLKO is the worst-case fixed time difference between rising edges of CLKIN and CLKO, *excluding* output jitter and input clock jitter.

3. Phase Offset between Clock Outputs on the DLL is the worst-case fixed time difference between rising edges of any two DLL outputs, *excluding* Output Jitter and input clock jitter.

4. Maximum Phase Difference between CLKIN an CLKO is the sum of Output Jitter and Phase Offset between CLKIN and CLKO, or the greatest difference between CLKIN and CLKO rising edges due to DLL alone (*excluding* input clock jitter).

5. **Maximum Phase Difference between Clock Outputs on the DLL** is the sum of Output JItter and Phase Offset between any DLL clock outputs, or the greatest difference between any two DLL output rising edges due to DLL alone (*excluding* input clock jitter).

| Package        | Leads | Туре                               | Maximum<br>I/O | Lead Pitch<br>(mm) | Footprint<br>Area (mm) | Height<br>(mm) | Mass <sup>(1)</sup><br>(g) |

|----------------|-------|------------------------------------|----------------|--------------------|------------------------|----------------|----------------------------|

| VQ100 / VQG100 | 100   | Very Thin Quad Flat Pack (VQFP)    | 60             | 0.5                | 16 x 16                | 1.20           | 0.6                        |

| TQ144 / TQG144 | 144   | Thin Quad Flat Pack (TQFP)         | 92             | 0.5                | 22 x 22                | 1.60           | 1.4                        |

| CS144 / CSG144 | 144   | Chip Scale Ball Grid Array (CSBGA) | 92             | 0.8                | 12 x 12                | 1.20           | 0.3                        |

| PQ208 / PQG208 | 208   | Plastic Quad Flat Pack (PQFP)      | 140            | 0.5                | 30.6 x 30.6            | 3.70           | 5.3                        |

| FG256 / FGG256 | 256   | Fine-pitch Ball Grid Array (FBGA)  | 176            | 1.0                | 17 x 17                | 2.00           | 0.9                        |

| FG456 / FGG456 | 456   | Fine-pitch Ball Grid Array (FBGA)  | 284            | 1.0                | 23 x 23                | 2.60           | 2.2                        |

#### Table 36: Spartan-II Family Package Options

#### Notes:

1. Package mass is  $\pm 10\%$ .

Note: Some early versions of Spartan-II devices, including the XC2S15 and XC2S30 ES devices and the XC2S150 with date code 0045 or earlier, included a power-down pin. For more information, see <u>Answer Record 10500</u>.

# VCCO Banks

Some of the I/O standards require specific V<sub>CCO</sub> voltages. These voltages are externally connected to device pins that serve groups of IOBs, called banks. Eight I/O banks result from separating each edge of the FPGA into two banks (see Figure 3 in Module 2). Each bank has multiple V<sub>CCO</sub> pins which must be connected to the same voltage. In the smaller packages, the V<sub>CCO</sub> pins are connected between banks, effectively reducing the number of independent banks available (see Table 37). These interconnected banks are shown in the Pinout Tables with V<sub>CCO</sub> pads for multiple banks connected to the same pin.

#### Table 37: Independent VCCO Banks Available

| Package           | VQ100 | CS144 | FG256 |

|-------------------|-------|-------|-------|

|                   | PQ208 | TQ144 | FG456 |

| Independent Banks | 1     | 4     | 8     |

# Package Overview

Table 36 shows the six low-cost, space-saving productionpackage styles for the Spartan-II family.

Each package style is available in an environmentally friendly lead-free (Pb-free) option. The Pb-free packages include an extra 'G' in the package style name. For example, the standard "CS144" package becomes "CSG144" when ordered as the Pb-free option. Leaded (non-Pb-free) packages may be available for selected devices, with the same pin-out and without the "G" in the ordering code; contact Xilinx sales for more information. The mechanical dimensions of the standard and Pb-free packages are similar, as shown in the mechanical drawings provided in Table 38. For additional package information, see <u>UG112</u>: *Device Package User Guide*.

## **Mechanical Drawings**

Detailed mechanical drawings for each package type are available from the Xilinx web site at the specified location in Table 38.

Material Declaration Data Sheets (MDDS) are also available on the <u>Xilinx web site</u> for each package.

#### Table 38: Xilinx Package Documentation

| Package | Drawing         | MDDS         |

|---------|-----------------|--------------|

| VQ100   | Package Drawing | PK173_VQ100  |

| VQG100  |                 | PK130_VQG100 |

| TQ144   | Package Drawing | PK169_TQ144  |

| TQG144  |                 | PK126_TQG144 |

| CS144   | Package Drawing | PK149_CS144  |

| CSG144  | _               | PK103_CSG144 |

| PQ208   | Package Drawing | PK166_PQ208  |

| PQG208  | _               | PK123_PQG208 |

| FG256   | Package Drawing | PK151_FG256  |

| FGG256  |                 | PK105_FGG256 |

| FG456   | Package Drawing | PK154_FG456  |

| FGG456  |                 | PK109_FGG456 |

# **Package Thermal Characteristics**

Table 39 provides the thermal characteristics for the various Spartan-II FPGA package offerings. This information is also available using the Thermal Query tool on xilinx.com (www.xilinx.com/cgi-bin/thermal/thermal.pl).

The junction-to-case thermal resistance  $(\theta_{JC})$  indicates the difference between the temperature measured on the package body (case) and the die junction temperature per watt of power consumption. The junction-to-board  $(\theta_{JB})$

value similarly reports the difference between the board and junction temperature. The junction-to-ambient ( $\theta_{JA}$ ) value reports the temperature difference between the ambient environment and the junction temperature. The  $\theta_{JA}$  value is reported at different air velocities, measured in linear feet per minute (LFM). The "Still Air (0 LFM)" column shows the  $\theta_{JA}$  value in a system without a fan. The thermal resistance drops with increasing air flow.

|                 |         |                                        |                                          | Junction-to-Ambient (θ <sub>JA</sub> )<br>at Different Air Flows |         |         |         |         |

|-----------------|---------|----------------------------------------|------------------------------------------|------------------------------------------------------------------|---------|---------|---------|---------|

| Package         | Device  | Junction-to-Case<br>(θ <sub>JC</sub> ) | Junction-to-<br>Board (θ <sub>JB</sub> ) | Still Air<br>(0 LFM)                                             | 250 LFM | 500 LFM | 750 LFM | Units   |

| VQ100           | XC2S15  | 11.3                                   | N/A                                      | 44.1                                                             | 36.7    | 34.2    | 33.3    | °C/Watt |

| VQG100          | XC2S30  | 10.1                                   | N/A                                      | 40.7                                                             | 33.9    | 31.5    | 30.8    | °C/Watt |

|                 | XC2S15  | 7.3                                    | N/A                                      | 38.6                                                             | 30.0    | 25.7    | 24.1    | °C/Watt |

| TQ144           | XC2S30  | 6.7                                    | N/A                                      | 34.7                                                             | 27.0    | 23.1    | 21.7    | °C/Watt |

| TQG144          | XC2S50  | 5.8                                    | N/A                                      | 32.2                                                             | 25.1    | 21.4    | 20.1    | °C/Watt |

|                 | XC2S100 | 5.3                                    | N/A                                      | 31.4                                                             | 24.4    | 20.9    | 19.6    | °C/Watt |

| CS144<br>CSG144 | XC2S30  | 2.8                                    | N/A                                      | 34.0                                                             | 26.0    | 23.9    | 23.2    | °C/Watt |

|                 | XC2S50  | 6.7                                    | N/A                                      | 25.2                                                             | 18.6    | 16.4    | 15.2    | °C/Watt |

| PQ208           | XC2S100 | 5.9                                    | N/A                                      | 24.6                                                             | 18.1    | 16.0    | 14.9    | °C/Watt |

| PQG208          | XC2S150 | 5.0                                    | N/A                                      | 23.8                                                             | 17.6    | 15.6    | 14.4    | °C/Watt |

| -               | XC2S200 | 4.1                                    | N/A                                      | 23.0                                                             | 17.0    | 15.0    | 13.9    | °C/Watt |

|                 | XC2S50  | 7.1                                    | 17.6                                     | 27.2                                                             | 21.4    | 20.3    | 19.8    | °C/Watt |

| FG256           | XC2S100 | 5.8                                    | 15.1                                     | 25.1                                                             | 19.5    | 18.3    | 17.8    | °C/Watt |

| FGG256          | XC2S150 | 4.6                                    | 12.7                                     | 23.0                                                             | 17.6    | 16.3    | 15.8    | °C/Watt |

|                 | XC2S200 | 3.5                                    | 10.7                                     | 21.4                                                             | 16.1    | 14.7    | 14.2    | °C/Watt |

| FG456           | XC2S150 | 2.0                                    | N/A                                      | 21.9                                                             | 17.3    | 15.8    | 15.2    | °C/Watt |

| FGG456          | XC2S200 | 2.0                                    | N/A                                      | 21.0                                                             | 16.6    | 15.1    | 14.5    | °C/Watt |

# **Pinout Tables**

The following device-specific pinout tables include all packages available for each Spartan<sup>®</sup>-II device. They follow the pad locations around the die, and include Boundary Scan register locations.

### **XC2S15 Device Pinouts**

| XC2S15 Pad Name          |      |       |       |       | Bndry |

|--------------------------|------|-------|-------|-------|-------|

| Function                 | Bank | VQ100 | TQ144 | CS144 | Scan  |

| GND                      | -    | P1    | P143  | A1    | -     |

| TMS                      | -    | P2    | P142  | B1    | -     |

| I/O                      | 7    | P3    | P141  | C2    | 77    |

| I/O                      | 7    | -     | P140  | C1    | 80    |

| I/O, V <sub>REF</sub>    | 7    | P4    | P139  | D4    | 83    |

| I/O                      | 7    | P5    | P137  | D2    | 86    |

| I/O                      | 7    | P6    | P136  | D1    | 89    |

| GND                      | -    | -     | P135  | E4    | -     |

| I/O                      | 7    | P7    | P134  | E3    | 92    |

| I/O                      | 7    | -     | P133  | E2    | 95    |

| I/O, V <sub>REF</sub>    | 7    | P8    | P132  | E1    | 98    |

| I/O                      | 7    | P9    | P131  | F4    | 101   |

| I/O                      | 7    | -     | P130  | F3    | 104   |

| I/O, IRDY <sup>(1)</sup> | 7    | P10   | P129  | F2    | 107   |

| GND                      | -    | P11   | P128  | F1    | -     |

| V <sub>CCO</sub>         | 7    | P12   | P127  | G2    | -     |

| V <sub>CCO</sub>         | 6    | P12   | P127  | G2    | -     |

| I/O, TRDY <sup>(1)</sup> | 6    | P13   | P126  | G1    | 110   |

| V <sub>CCINT</sub>       | -    | P14   | P125  | G3    | -     |

| I/O                      | 6    | -     | P124  | G4    | 113   |

| I/O                      | 6    | P15   | P123  | H1    | 116   |

| I/O, V <sub>REF</sub>    | 6    | P16   | P122  | H2    | 119   |

| I/O                      | 6    | -     | P121  | H3    | 122   |

| I/O                      | 6    | P17   | P120  | H4    | 125   |

| GND                      | -    | -     | P119  | J1    | -     |

| I/O                      | 6    | P18   | P118  | J2    | 128   |

| I/O                      | 6    | P19   | P117  | J3    | 131   |

| I/O, V <sub>REF</sub>    | 6    | P20   | P115  | K1    | 134   |

| I/O                      | 6    | -     | P114  | K2    | 137   |

| I/O                      | 6    | P21   | P113  | K3    | 140   |

| I/O                      | 6    | P22   | P112  | L1    | 143   |

| M1                       | -    | P23   | P111  | L2    | 146   |

| GND                      | -    | P24   | P110  | L3    | -     |

| M0                       | -    | P25   | P109  | M1    | 147   |

| V <sub>CCO</sub>         | 6    | P26   | P108  | M2    | -     |

| V <sub>CCO</sub>         | 5    | P26   | P107  | N1    | -     |

### XC2S15 Device Pinouts (Continued)

| XC2S15 Pad Name       |      |       |       |       | Bndry |

|-----------------------|------|-------|-------|-------|-------|

| Function              | Bank | VQ100 | TQ144 | CS144 | Scan  |

| M2                    | -    | P27   | P106  | N2    | 148   |

| I/O                   | 5    | -     | P103  | K4    | 155   |

| I/O, V <sub>REF</sub> | 5    | P30   | P102  | L4    | 158   |

| I/O                   | 5    | P31   | P100  | N4    | 161   |

| I/O                   | 5    | P32   | P99   | K5    | 164   |

| GND                   | -    | -     | P98   | L5    | -     |

| V <sub>CCINT</sub>    | -    | P33   | P97   | M5    | -     |

| I/O                   | 5    | -     | P96   | N5    | 167   |

| I/O                   | 5    | -     | P95   | K6    | 170   |

| I/O, V <sub>REF</sub> | 5    | P34   | P94   | L6    | 173   |

| I/O                   | 5    | -     | P93   | M6    | 176   |

| V <sub>CCINT</sub>    | -    | P35   | P92   | N6    | -     |

| I, GCK1               | 5    | P36   | P91   | M7    | 185   |

| V <sub>CCO</sub>      | 5    | P37   | P90   | N7    | -     |

| V <sub>CCO</sub>      | 4    | P37   | P90   | N7    | -     |

| GND                   | -    | P38   | P89   | L7    | -     |

| I, GCK0               | 4    | P39   | P88   | K7    | 186   |

| I/O                   | 4    | P40   | P87   | N8    | 190   |

| I/O                   | 4    | -     | P86   | M8    | 193   |

| I/O, V <sub>REF</sub> | 4    | P41   | P85   | L8    | 196   |

| I/O                   | 4    | -     | P84   | K8    | 199   |

| I/O                   | 4    | -     | P83   | N9    | 202   |

| V <sub>CCINT</sub>    | -    | P42   | P82   | M9    | -     |

| GND                   | -    | -     | P81   | L9    | -     |

| I/O                   | 4    | P43   | P80   | K9    | 205   |

| I/O                   | 4    | P44   | P79   | N10   | 208   |

| I/O, V <sub>REF</sub> | 4    | P45   | P77   | L10   | 211   |

| I/O                   | 4    | -     | P76   | N11   | 214   |

| I/O                   | 4    | P46   | P75   | M11   | 217   |

| I/O                   | 4    | P47   | P74   | L11   | 220   |

| GND                   | -    | P48   | P73   | N12   | -     |

| DONE                  | 3    | P49   | P72   | M12   | 223   |

| V <sub>cco</sub>      | 4    | P50   | P71   | N13   | -     |

| V <sub>CCO</sub>      | 3    | P50   | P70   | M13   | -     |

| PROGRAM               | -    | P51   | P69   | L12   | 226   |

| I/O (INIT)            | 3    | P52   | P68   | L13   | 227   |

| I/O (D7)              | 3    | P53   | P67   | K10   | 230   |

| I/O                   | 3    | -     | P66   | K11   | 233   |

| I/O, V <sub>REF</sub> | 3    | P54   | P65   | K12   | 236   |

| I/O                   | 3    | P55   | P63   | J10   | 239   |

| I/O (D6)              | 3    | P56   | P62   | J11   | 233   |

| "O (DO)               | 5    | 1.00  | 102   | 011   | 272   |

# XC2S100 Device Pinouts (Continued)

| XC2S100 Pad<br>Name   |      |       |       |                             |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-----------------------------|-------|