# E·XFL

#### AMD Xilinx - XC2S15-5CS144C Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 96                                                         |

| Number of Logic Elements/Cells | 432                                                        |

| Total RAM Bits                 | 16384                                                      |

| Number of I/O                  | 86                                                         |

| Number of Gates                | 15000                                                      |

| Voltage - Supply               | 2.375V ~ 2.625V                                            |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 144-TFBGA, CSPBGA                                          |

| Supplier Device Package        | 144-LCSBGA (12x12)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s15-5cs144c |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

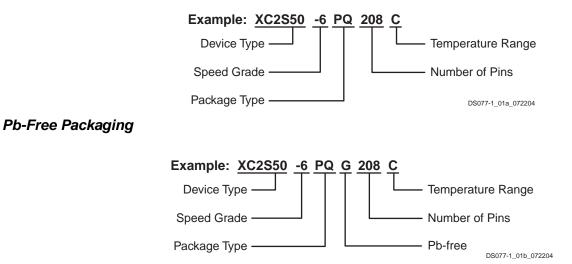

## **Ordering Information**

Spartan-II devices are available in both standard and Pb-free packaging options for all device/package combinations. The Pb-free packages include a special "G" character in the ordering code.

#### Standard Packaging

## **Device Ordering Options**

| Device  | Speed Grade |                                   | Numb     | per of Pins / Package Type    | Temperature Range (T <sub>J</sub> ) |                 |

|---------|-------------|-----------------------------------|----------|-------------------------------|-------------------------------------|-----------------|

| XC2S15  | -5          | Standard Performance              | VQ(G)100 | 100-pin Plastic Very Thin QFP | C = Commercial                      | 0°C to +85°C    |

| XC2S30  | -6          | Higher Performance <sup>(1)</sup> | CS(G)144 | 144-ball Chip-Scale BGA       | I = Industrial                      | -40°C to +100°C |

| XC2S50  |             |                                   | TQ(G)144 | 144-pin Plastic Thin QFP      |                                     | 1               |

| XC2S100 |             |                                   | PQ(G)208 | 208-pin Plastic QFP           |                                     |                 |

| XC2S150 |             |                                   | FG(G)256 | 256-ball Fine Pitch BGA       |                                     |                 |

| XC2S200 |             |                                   | FG(G)456 | 456-ball Fine Pitch BGA       |                                     |                 |

#### Notes:

1. The -6 speed grade is exclusively available in the Commercial temperature range.

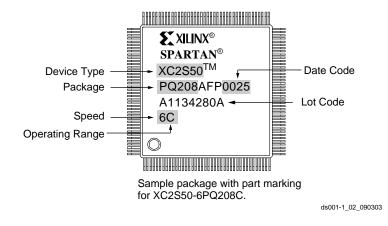

## **Device Part Marking**

www.xilinx.com

Similarly, the F6 multiplexer combines the outputs of all four function generators in the CLB by selecting one of the F5-multiplexer outputs. This permits the implementation of any 6-input function, an 8:1 multiplexer, or selected functions of up to 19 inputs.

Each CLB has four direct feedthrough paths, one per LC. These paths provide extra data input lines or additional local routing that does not consume logic resources.

#### Arithmetic Logic

Dedicated carry logic provides capability for high-speed arithmetic functions. The Spartan-II FPGA CLB supports two separate carry chains, one per slice. The height of the carry chains is two bits per CLB.

The arithmetic logic includes an XOR gate that allows a 1-bit full adder to be implemented within an LC. In addition, a dedicated AND gate improves the efficiency of multiplier implementation.

The dedicated carry path can also be used to cascade function generators for implementing wide logic functions.

#### **BUFT**s

Each Spartan-II FPGA CLB contains two 3-state drivers (BUFTs) that can drive on-chip busses. See "Dedicated Routing," page 12. Each Spartan-II FPGA BUFT has an independent 3-state control pin and an independent input pin.

#### **Block RAM**

Spartan-II FPGAs incorporate several large block RAM memories. These complement the distributed RAM Look-Up Tables (LUTs) that provide shallow memory structures implemented in CLBs.

Block RAM memory blocks are organized in columns. All Spartan-II devices contain two such columns, one along each vertical edge. These columns extend the full height of the chip. Each memory block is four CLBs high, and consequently, a Spartan-II device eight CLBs high will contain two memory blocks per column, and a total of four blocks.

Table 5: Spartan-II Block RAM Amounts

| Spartan-II<br>Device | # of Blocks | Total Block RAM<br>Bits |

|----------------------|-------------|-------------------------|

| XC2S15               | 4           | 16K                     |

| XC2S30               | 6           | 24K                     |

| XC2S50               | 8           | 32K                     |

| XC2S100              | 10          | 40K                     |

| XC2S150              | 12          | 48K                     |

| XC2S200              | 14          | 56K                     |

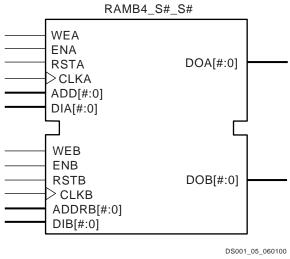

Each block RAM cell, as illustrated in Figure 5, is a fully synchronous dual-ported 4096-bit RAM with independent control signals for each port. The data widths of the two ports can be configured independently, providing built-in bus-width conversion.

Figure 5: Dual-Port Block RAM

Table 6 shows the depth and width aspect ratios for the block RAM.

| Table | 6: | Block | RAM | Port | Aspect  | Ratios |

|-------|----|-------|-----|------|---------|--------|

| iabio | Ο. | BIOOK |     |      | 7.0p00t | 1.000  |

| Width | Depth | ADDR Bus   | Data Bus   |

|-------|-------|------------|------------|

| 1     | 4096  | ADDR<11:0> | DATA<0>    |

| 2     | 2048  | ADDR<10:0> | DATA<1:0>  |

| 4     | 1024  | ADDR<9:0>  | DATA<3:0>  |

| 8     | 512   | ADDR<8:0>  | DATA<7:0>  |

| 16    | 256   | ADDR<7:0>  | DATA<15:0> |

The Spartan-II FPGA block RAM also includes dedicated routing to provide an efficient interface with both CLBs and other block RAMs.

## **Programmable Routing Matrix**

It is the longest delay path that limits the speed of any worst-case design. Consequently, the Spartan-II routing architecture and its place-and-route software were defined in a single optimization process. This joint optimization minimizes long-path delays, and consequently, yields the best system performance.

The joint optimization also reduces design compilation times because the architecture is software-friendly. Design cycles are correspondingly reduced due to shorter design iteration times.

## **∑** XILINX<sup>®</sup>

## Local Routing

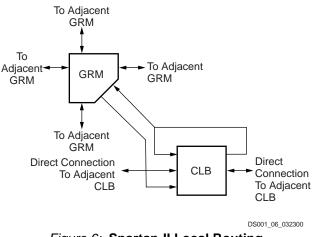

The local routing resources, as shown in Figure 6, provide the following three types of connections:

- Interconnections among the LUTs, flip-flops, and General Routing Matrix (GRM)

- Internal CLB feedback paths that provide high-speed connections to LUTs within the same CLB, chaining them together with minimal routing delay

- Direct paths that provide high-speed connections between horizontally adjacent CLBs, eliminating the delay of the GRM

Figure 6: Spartan-II Local Routing

## General Purpose Routing

Most Spartan-II FPGA signals are routed on the general purpose routing, and consequently, the majority of interconnect resources are associated with this level of the routing hierarchy. The general routing resources are located in horizontal and vertical routing channels associated with the rows and columns CLBs. The general-purpose routing resources are listed below.

- Adjacent to each CLB is a General Routing Matrix (GRM). The GRM is the switch matrix through which horizontal and vertical routing resources connect, and is also the means by which the CLB gains access to the general purpose routing.

- 24 single-length lines route GRM signals to adjacent GRMs in each of the four directions.

- 96 buffered Hex lines route GRM signals to other GRMs six blocks away in each one of the four directions. Organized in a staggered pattern, Hex lines may be driven only at their endpoints. Hex-line signals can be accessed either at the endpoints or at the midpoint (three blocks from the source). One third of the Hex lines are bidirectional, while the remaining ones are unidirectional.

- 12 Longlines are buffered, bidirectional wires that distribute signals across the device quickly and

efficiently. Vertical Longlines span the full height of the device, and horizontal ones span the full width of the device.

## I/O Routing

Spartan-II devices have additional routing resources around their periphery that form an interface between the CLB array and the IOBs. This additional routing, called the VersaRing, facilitates pin-swapping and pin-locking, such that logic redesigns can adapt to existing PCB layouts. Time-to-market is reduced, since PCBs and other system components can be manufactured while the logic design is still in progress.

## **Dedicated Routing**

Some classes of signal require dedicated routing resources to maximize performance. In the Spartan-II architecture, dedicated routing resources are provided for two classes of signal.

- Horizontal routing resources are provided for on-chip 3-state busses. Four partitionable bus lines are provided per CLB row, permitting multiple busses within a row, as shown in Figure 7.

- Two dedicated nets per CLB propagate carry signals vertically to the adjacent CLB.

## **Global Routing**

Global Routing resources distribute clocks and other signals with very high fanout throughout the device. Spartan-II devices include two tiers of global routing resources referred to as primary and secondary global routing resources.

- The primary global routing resources are four dedicated global nets with dedicated input pins that are designed to distribute high-fanout clock signals with minimal skew. Each global clock net can drive all CLB, IOB, and block RAM clock pins. The primary global nets may only be driven by global buffers. There are four global buffers, one for each global net.

- The secondary global routing resources consist of 24 backbone lines, 12 across the top of the chip and 12 across bottom. From these lines, up to 12 unique signals per column can be distributed via the 12 longlines in the column. These secondary resources are more flexible than the primary resources since they are not restricted to routing only to clock pins.

## **∑**XILINX<sup>®</sup>

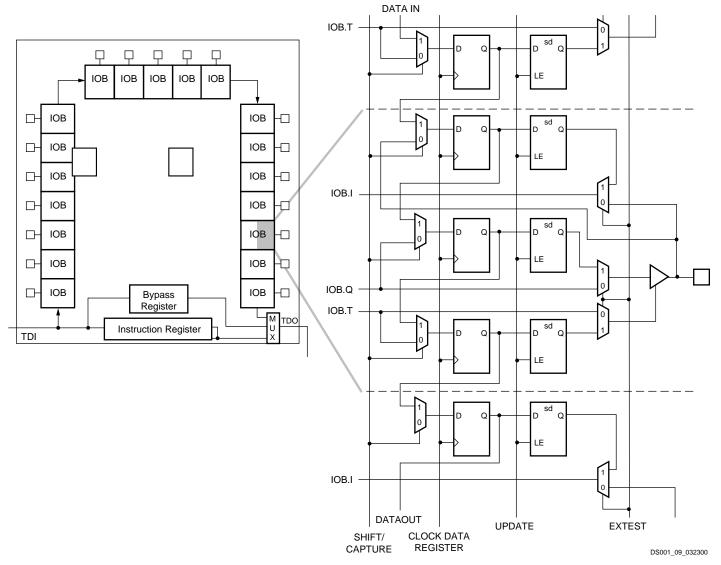

Figure 9 is a diagram of the Spartan-II family boundary scan logic. It includes three bits of Data Register per IOB, the IEEE 1149.1 Test Access Port controller, and the Instruction Register with decodes.

#### **Bit Sequence**

The bit sequence within each IOB is: In, Out, 3-State. The input-only pins contribute only the In bit to the boundary scan I/O data register, while the output-only pins contributes all three bits.

From a cavity-up view of the chip (as shown in the FPGA Editor), starting in the upper right chip corner, the boundary scan data-register bits are ordered as shown in Figure 10.

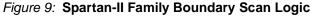

BSDL (Boundary Scan Description Language) files for Spartan-II family devices are available on the Xilinx website, in the <u>Downloads</u> area. By default, these operations are synchronized to CCLK. The entire start-up sequence lasts eight cycles, called C0-C7, after which the loaded design is fully functional. The default timing for start-up is shown in the top half of Figure 13. The four operations can be selected to switch on any CCLK cycle C1-C6 through settings in the Xilinx software. Heavy lines show default settings.

Figure 13: Start-Up Waveforms

The bottom half of Figure 13 shows another commonly used version of the start-up timing known as Sync-to-DONE. This version makes the GTS, GSR, and GWE events conditional upon the DONE pin going High. This timing is important for a daisy chain of multiple FPGAs in serial mode, since it ensures that all FPGAs go through start-up together, after all their DONE pins have gone High.

Sync-to-DONE timing is selected by setting the GTS, GSR, and GWE cycles to a value of DONE in the configuration options. This causes these signals to transition one clock cycle after DONE externally transitions High.

#### **Serial Modes**

There are two serial configuration modes: In Master Serial mode, the FPGA controls the configuration process by driving CCLK as an output. In Slave Serial mode, the FPGA passively receives CCLK as an input from an external agent (e.g., a microprocessor, CPLD, or second FPGA in master mode) that is controlling the configuration process. In both modes, the FPGA is configured by loading one bit per CCLK cycle. The MSB of each configuration data byte is always written to the DIN pin first.

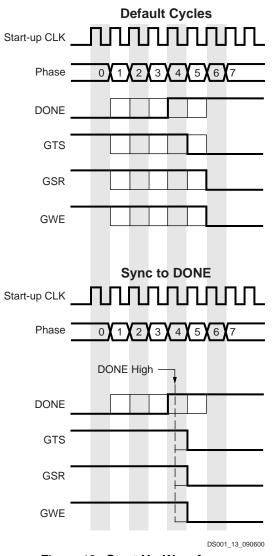

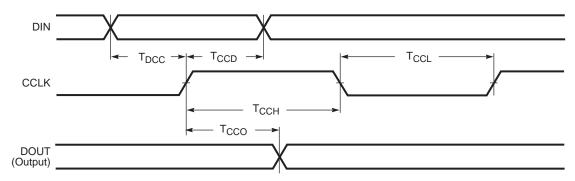

See Figure 14 for the sequence for loading data into the Spartan-II FPGA serially. This is an expansion of the "Load Configuration Data Frames" block in Figure 11. Note that CS and WRITE normally are not used during serial configuration. To ensure successful loading of the FPGA, do not toggle WRITE with CS Low during serial configuration.

DS001\_16\_032300

| Symbol           |      | Description       |    | Units    |

|------------------|------|-------------------|----|----------|

| T <sub>DCC</sub> |      | DIN setup         | 5  | ns, min  |

| T <sub>CCD</sub> |      | DIN hold          | 0  | ns, min  |

| T <sub>CCO</sub> | CCLK | DOUT              | 12 | ns, max  |

| ТССН             |      | High time         | 5  | ns, min  |

| T <sub>CCL</sub> |      | Low time          | 5  | ns, min  |

| F <sub>CC</sub>  |      | Maximum frequency | 66 | MHz, max |

Figure 16: Slave Serial Mode Timing

LVTTL output buffers have selectable drive strengths.

The format for LVTTL OBUF primitive names is as follows.

OBUF <slew rate> <drive strength>

<slew\_rate> is either F (Fast), or S (Slow) and <drive\_strength> is specified in milliamps (2, 4, 6, 8, 12, 16, or 24). The default is slew rate limited with 12 mA drive.

OBUF placement restrictions require that within a given  $V_{CCO}$  bank each OBUF share the same output source drive voltage. Input buffers of any type and output buffers that do not require  $V_{CCO}$  can be placed within any  $V_{CCO}$  bank. Table 17 summarizes the output compatibility requirements. The LOC property can specify a location for the OBUF.

## Table 17: Output Standards Compatibility Requirements

| Rule 1           | Only outputs with standards which share compatible $\rm V_{\rm CCO}$ may be used within the same bank.  |

|------------------|---------------------------------------------------------------------------------------------------------|

| Rule 2           | There are no placement restrictions for outputs with standards that do not require a $\rm V_{\rm CCO}.$ |

| V <sub>CCO</sub> | Compatible Standards                                                                                    |

| 3.3              | LVTTL, SSTL3_I, SSTL3_II, CTT, AGP, GTL, GTL+, PCI33_3, PCI66_3                                         |

| 2.5              | SSTL2_I, SSTL2_II, LVCMOS2, GTL, GTL+                                                                   |

| 1.5              | HSTL_I, HSTL_III, HSTL_IV, GTL, GTL+                                                                    |

#### OBUFT

The generic 3-state output buffer OBUFT, shown in Figure 39, typically implements 3-state outputs or bidirectional I/O.

With no extension or property specified for the generic OBUFT primitive, the assumed standard is slew rate limited LVTTL with 12 mA drive strength.

The LVTTL OBUFT can support one of two slew rate modes to minimize bus transients. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals.

LVTTL 3-state output buffers have selectable drive strengths.

The format for LVTTL OBUFT primitive names is as follows.

OBUFT\_<slew\_rate>\_<drive\_strength>

<slew\_rate> can be either F (Fast), or S (Slow) and <drive\_strength> is specified in milliamps (2, 4, 6, 8, 12, 16, or 24).

DS001\_39\_032300

Figure 39: 3-State Output Buffer Primitive (OBUFT

The Versatile I/O OBUFT placement restrictions require that within a given V<sub>CCO</sub> bank each OBUFT share the same output source drive voltage. Input buffers of any type and output buffers that do not require V<sub>CCO</sub> can be placed within the same V<sub>CCO</sub> bank.

The LOC property can specify a location for the OBUFT.

3-state output buffers and bidirectional buffers can have either a weak pull-up resistor, a weak pull-down resistor, or a weak "keeper" circuit. Control this feature by adding the appropriate primitive to the output net of the OBUFT (PULLUP, PULLDOWN, or KEEPER).

The weak "keeper" circuit requires the input buffer within the IOB to sample the I/O signal. So, OBUFTs programmed for an I/O standard that requires a  $V_{REF}$  have automatic placement of a  $V_{REF}$  in the bank with an OBUFT configured with a weak "keeper" circuit. This restriction does not affect most circuit design as applications using an OBUFT configured with a weak "keeper" typically implement a bidirectional I/O. In this case the IBUF (and the corresponding  $V_{REF}$ ) are explicitly placed.

The LOC property can specify a location for the OBUFT.

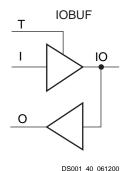

#### IOBUF

Use the IOBUF primitive for bidirectional signals that require both an input buffer and a 3-state output buffer with an active high 3-state pin. The generic input/output buffer IOBUF appears in Figure 40.

With no extension or property specified for the generic IOBUF primitive, the assumed standard is LVTTL input buffer and slew rate limited LVTTL with 12 mA drive strength for the output buffer.

The LVTTL IOBUF can support one of two slew rate modes to minimize bus transients. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals.

LVTTL bidirectional buffers have selectable output drive strengths.

The format for LVTTL IOBUF primitive names is as follows:

IOBUF\_<slew\_rate>\_<drive\_strength>

<slew\_rate> can be either F (Fast), or S (Slow) and <drive\_strength> is specified in milliamps (2, 4, 6, 8, 12, 16, or 24).

When the IOBUF primitive supports an I/O standard such as LVTTL, LVCMOS, or PCI33\_5, the IBUF automatically configures as a 5V tolerant input buffer unless the V<sub>CCO</sub> for the bank is less than 2V. If the single-ended IBUF is placed in a bank with an HSTL standard (V<sub>CCO</sub> < 2V), the input buffer is not 5V tolerant.

The voltage reference signal is "banked" within the Spartan-II device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 36, page 39 for a representation of the Spartan-II FPGA I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input.

Additional restrictions on the Versatile I/O IOBUF placement require that within a given  $V_{CCO}$  bank each IOBUF must share the same output source drive voltage. Input buffers of any type and output buffers that do not require  $V_{CCO}$  can be placed within the same  $V_{CCO}$  bank. The LOC property can specify a location for the IOBUF.

An optional delay element is associated with the input path in each IOBUF. When the IOBUF drives an input flip-flop within the IOB, the delay element activates by default to ensure a zero hold-time requirement. Override this default with the NODELAY=TRUE property.

In the case when the IOBUF does not drive an input flip-flop within the IOB, the delay element de-activates by default to provide higher performance. To delay the input signal, activate the delay element with the DELAY=TRUE property.

3-state output buffers and bidirectional buffers can have either a weak pull-up resistor, a weak pull-down resistor, or a weak "keeper" circuit. Control this feature by adding the appropriate primitive to the output net of the IOBUF (PULLUP, PULLDOWN, or KEEPER).

#### **Versatile I/O Properties**

Access to some of the Versatile I/O features (for example, location constraints, input delay, output drive strength, and slew rate) is available through properties associated with these features.

#### Input Delay Properties

An optional delay element is associated with each IBUF. When the IBUF drives a flip-flop within the IOB, the delay element activates by default to ensure a zero hold-time requirement. Use the NODELAY=TRUE property to override this default.

In the case when the IBUF does not drive a flip-flop within the IOB, the delay element by default de-activates to provide higher performance. To delay the input signal, activate the delay element with the DELAY=TRUE property.

#### IOB Flip-Flop/Latch Property

The I/O Block (IOB) includes an optional register on the input path, an optional register on the output path, and an optional register on the 3-state control pin. The design implementation software automatically takes advantage of these registers when the following option for the Map program is specified:

#### map -pr b <filename>

Alternatively, the IOB = TRUE property can be placed on a register to force the mapper to place the register in an IOB.

#### **Location Constraints**

Specify the location of each Versatile I/O primitive with the location constraint LOC attached to the Versatile I/O primitive. The external port identifier indicates the value of the location constrain. The format of the port identifier depends on the package chosen for the specific design.

The LOC properties use the following form:

LOC=A42 LOC=P37

#### **Output Slew Rate Property**

In the case of the LVTTL output buffers (OBUF, OBUFT, and IOBUF), slew rate control can be programmed with the SLEW= property. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals. The SLEW= property has one of the two following values.

SLEW=SLOW

SLEW=FAST

#### **Output Drive Strength Property**

For the LVTTL output buffers (OBUF, OBUFT, and IOBUF, the desired drive strength can be specified with the DRIVE=

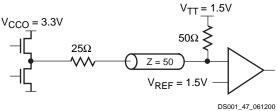

### SSTL3 Class I

A sample circuit illustrating a valid termination technique for SSTL3\_I appears in Figure 47. DC voltage specifications appear in Table 25 for the SSTL3\_I standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

#### SSTL3 Class I

Figure 47: Terminated SSTL3 Class I

| Table 2 | 25: | SSTL3_ | I Voltage | Specifications |

|---------|-----|--------|-----------|----------------|

|---------|-----|--------|-----------|----------------|

| Parameter                               | Min     | Тур | Max                |

|-----------------------------------------|---------|-----|--------------------|

| V <sub>CCO</sub>                        | 3.0     | 3.3 | 3.6                |

| $V_{REF} = 0.45 \times V_{CCO}$         | 1.3     | 1.5 | 1.7                |

| V <sub>TT</sub> = V <sub>REF</sub>      | 1.3     | 1.5 | 1.7                |

| $V_{IH} \ge V_{REF} + 0.2$              | 1.5     | 1.7 | 3.9 <sup>(1)</sup> |

| $V_{IL} \leq V_{REF} - 0.2$             | -0.3(2) | 1.3 | 1.5                |

| $V_{OH} \ge V_{REF} + 0.6$              | 1.9     | -   | -                  |

| $V_{OL} \leq V_{REF} - 0.6$             | -       | -   | 1.1                |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -8      | -   | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 8       | -   | -                  |

#### Notes:

1.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3.

2. V<sub>IL</sub> minimum does not conform to the formula.

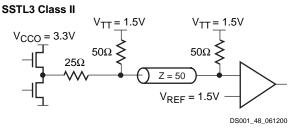

#### SSTL3 Class II

A sample circuit illustrating a valid termination technique for SSTL3\_II appears in Figure 48. DC voltage specifications appear in Table 26 for the SSTL3\_II standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 48: Terminated SSTL3 Class II

#### Table 26: SSTL3\_II Voltage Specifications

| Parameter                                | Min     | Тур | Max                |

|------------------------------------------|---------|-----|--------------------|

| V <sub>CCO</sub>                         | 3.0     | 3.3 | 3.6                |

| $V_{REF} = 0.45 \times V_{CCO}$          | 1.3     | 1.5 | 1.7                |

| V <sub>TT</sub> = V <sub>REF</sub>       | 1.3     | 1.5 | 1.7                |

| V <sub>IH</sub> ≥ V <sub>REF</sub> + 0.2 | 1.5     | 1.7 | 3.9 <sup>(1)</sup> |

| $V_{IL} \leq V_{REF} - 0.2$              | -0.3(2) | 1.3 | 1.5                |

| $V_{OH} \ge V_{REF} + 0.8$               | 2.1     | -   | -                  |

| $V_{OL} \leq V_{REF} - 0.8$              | -       | -   | 0.9                |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)  | -16     | -   | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA)  | 16      | -   | -                  |

Notes:

1.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3

2. V<sub>IL</sub> minimum does not conform to the formula

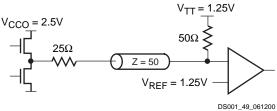

#### SSTL2\_I

A sample circuit illustrating a valid termination technique for SSTL2\_I appears in Figure 49. DC voltage specifications appear in Table 27 for the SSTL2\_I standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics

#### SSTL2 Class I

Figure 49: Terminated SSTL2 Class I

| Table | 27: | SSTL2_I | Voltage | Specifications |

|-------|-----|---------|---------|----------------|

|-------|-----|---------|---------|----------------|

| Parameter                                 | Min                 | Тур  | Max                |

|-------------------------------------------|---------------------|------|--------------------|

| V <sub>CCO</sub>                          | 2.3                 | 2.5  | 2.7                |

| $V_{REF} = 0.5 \times V_{CCO}$            | 1.15                | 1.25 | 1.35               |

| $V_{TT} = V_{REF} + N^{(1)}$              | 1.11                | 1.25 | 1.39               |

| $V_{IH} \ge V_{REF} + 0.18$               | 1.33                | 1.43 | 3.0 <sup>(2)</sup> |

| $V_{IL} \leq V_{REF} - 0.18$              | -0.3 <sup>(3)</sup> | 1.07 | 1.17               |

| V <sub>OH</sub> ≥ V <sub>REF</sub> + 0.61 | 1.76                | -    | -                  |

| $V_{OL} \leq V_{REF} - 0.61$              | -                   | -    | 0.74               |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)   | -7.6                | -    | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA)   | 7.6                 | -    | -                  |

#### Notes:

- 1. N must be greater than or equal to -0.04 and less than or equal to 0.04.

- 2.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3.

- 3. V<sub>IL</sub> minimum does not conform to the formula.

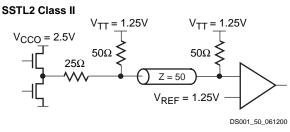

#### SSTL2 Class II

A sample circuit illustrating a valid termination technique for SSTL2\_II appears in Figure 50. DC voltage specifications appear in Table 28 for the SSTL2\_II standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 50: Terminated SSTL2 Class II

#### Table 28: SSTL2\_II Voltage Specifications

| Parameter                               | Min                 | Тур  | Max                |

|-----------------------------------------|---------------------|------|--------------------|

| V <sub>CCO</sub>                        | 2.3                 | 2.5  | 2.7                |

| $V_{REF} = 0.5 \times V_{CCO}$          | 1.15                | 1.25 | 1.35               |

| $V_{TT} = V_{REF} + N^{(1)}$            | 1.11                | 1.25 | 1.39               |

| $V_{IH} \ge V_{REF} + 0.18$             | 1.33                | 1.43 | 3.0 <sup>(2)</sup> |

| $V_{IL} \leq V_{REF} - 0.18$            | -0.3 <sup>(3)</sup> | 1.07 | 1.17               |

| $V_{OH} \ge V_{REF} + 0.8$              | 1.95                | -    | -                  |

| $V_{OL} \leq V_{REF} - 0.8$             | -                   | -    | 0.55               |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -15.2               | -    | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 15.2                | -    | -                  |

#### Notes:

- 1. N must be greater than or equal to -0.04 and less than or equal to 0.04.

- 2.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3.

- 3. V<sub>IL</sub> minimum does not conform to the formula.

## XILINX<sup>®</sup>

## LVTTL

LVTTL requires no termination. DC voltage specifications appears in Table 32 for the LVTTL standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

| Table | 32: | LVTTL | Voltage | Specifications |

|-------|-----|-------|---------|----------------|

|-------|-----|-------|---------|----------------|

| Parameter                               | Min  | Тур | Max |

|-----------------------------------------|------|-----|-----|

| V <sub>CCO</sub>                        | 3.0  | 3.3 | 3.6 |

| V <sub>REF</sub>                        | -    | -   | -   |

| V <sub>TT</sub>                         | -    | -   | -   |

| V <sub>IH</sub>                         | 2.0  | -   | 5.5 |

| V <sub>IL</sub>                         | -0.5 | -   | 0.8 |

| V <sub>OH</sub>                         | 2.4  | -   | -   |

| V <sub>OL</sub>                         | -    | -   | 0.4 |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -24  | -   | -   |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 24   | -   | -   |

#### Notes:

1.  $V_{OL}$  and  $V_{OH}$  for lower drive currents sample tested.

#### LVCMOS2

LVCMOS2 requires no termination. DC voltage specifications appear in Table 33 for the LVCMOS2 standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

#### Table 33: LVCMOS2 Voltage Specifications

| Parameter                               | Min  | Тур | Max |

|-----------------------------------------|------|-----|-----|

| V <sub>CCO</sub>                        | 2.3  | 2.5 | 2.7 |

| V <sub>REF</sub>                        | -    | -   | -   |

| V <sub>TT</sub>                         | -    | -   | -   |

| V <sub>IH</sub>                         | 1.7  | -   | 5.5 |

| V <sub>IL</sub>                         | -0.5 | -   | 0.7 |

| V <sub>OH</sub>                         | 1.9  | -   | -   |

| V <sub>OL</sub>                         | -    | -   | 0.4 |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -12  | -   | -   |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 12   | -   | -   |

#### AGP-2X

The specification for the AGP-2X standard does not document a recommended termination technique. DC voltage specifications appear in Table 34 for the AGP-2X standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

#### Table 34: AGP-2X Voltage Specifications

| Parameter                               | Min    | Тур  | Max  |

|-----------------------------------------|--------|------|------|

| V <sub>CCO</sub>                        | 3.0    | 3.3  | 3.6  |

| $V_{REF} = N \times V_{CCO}^{(1)}$      | 1.17   | 1.32 | 1.48 |

| V <sub>TT</sub>                         | -      | -    | -    |

| $V_{IH} \ge V_{REF} + 0.2$              | 1.37   | 1.52 | -    |

| $V_{IL} \le V_{REF} - 0.2$              | -      | 1.12 | 1.28 |

| $V_{OH} \ge 0.9 \times V_{CCO}$         | 2.7    | 3.0  | -    |

| $V_{OL} \le 0.1 \times V_{CCO}$         | -      | 0.33 | 0.36 |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | Note 2 | -    | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | Note 2 | -    | -    |

#### Notes:

For design examples and more information on using the I/O, see <u>XAPP179</u>, Using SelectIO Interfaces in Spartan-II and Spartan-IIE FPGAs.

<sup>1.</sup> N must be greater than or equal to 0.39 and less than or equal to 0.41.

<sup>2.</sup> Tested according to the relevant specification.

## Spartan-II FPGA Family: DC and Switching Characteristics

DS001-3 (v2.8) June 13, 2008

**Product Specification**

## **Definition of Terms**

In this document, some specifications may be designated as Advance or Preliminary. These terms are defined as follows:

Advance: Initial estimates based on simulation and/or extrapolation from other speed grades, devices, or families. Values are subject to change. Use as estimates, not for production.

Preliminary: Based on preliminary characterization. Further changes are not expected.

Unmarked: Specifications not identified as either Advance or Preliminary are to be considered Final.

Except for pin-to-pin input and output parameters, the AC parameter delay specifications included in this document are derived from measuring internal test patterns. All limits are representative of worst-case supply voltage and junction temperature conditions. Typical numbers are based on measurements taken at a nominal  $V_{CCINT}$  level of 2.5V and a junction temperature of 25°C. The parameters included are common to popular designs and typical applications. All specifications are subject to change without notice.

## **DC Specifications**

#### Absolute Maximum Ratings<sup>(1)</sup>

| Symbol             | Descriptio                                    | Description                    |      |                       | Units |

|--------------------|-----------------------------------------------|--------------------------------|------|-----------------------|-------|

| V <sub>CCINT</sub> | Supply voltage relative to GND <sup>(2)</sup> |                                | -0.5 | 3.0                   | V     |

| V <sub>CCO</sub>   | Supply voltage relative to GND <sup>(2)</sup> |                                | -0.5 | 4.0                   | V     |

| V <sub>REF</sub>   | Input reference voltage                       | Input reference voltage        |      |                       | V     |

| V <sub>IN</sub>    | Input voltage relative to GND <sup>(3)</sup>  | 5V tolerant I/O <sup>(4)</sup> | -0.5 | 5.5                   | V     |

|                    |                                               | No 5V tolerance <sup>(5)</sup> | -0.5 | V <sub>CCO</sub> +0.5 | V     |

| V <sub>TS</sub>    | Voltage applied to 3-state output             | 5V tolerant I/O <sup>(4)</sup> | -0.5 | 5.5                   | V     |

|                    |                                               | No 5V tolerance <sup>(5)</sup> | -0.5 | V <sub>CCO</sub> +0.5 | V     |

| T <sub>STG</sub>   | Storage temperature (ambient)                 | Storage temperature (ambient)  |      |                       | °C    |

| TJ                 | Junction temperature                          | Junction temperature           |      |                       | °C    |

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

2. Power supplies may turn on in any order.

3. V<sub>IN</sub> should not exceed V<sub>CCO</sub> by more than 3.6V over extended periods of time (e.g., longer than a day).

4. Spartan<sup>®</sup>-II device I/Os are 5V Tolerant whenever the LVTTL, LVCMOS2, or PCI33\_5 signal standard has been selected. With 5V Tolerant I/Os selected, the Maximum DC overshoot must be limited to either +5.5V or 10 mA, and undershoot must be limited to either -0.5V or 10 mA, whichever is easier to achieve. The Maximum AC conditions are as follows: The device pins may undershoot to -2.0V or overshoot to +7.0V, provided this over/undershoot lasts no more than 11 ns with a forcing current no greater than 100 mA.

5. Without 5V Tolerant I/Os selected, the Maximum DC overshoot must be limited to either V<sub>CCO</sub> + 0.5V or 10 mA, and undershoot must be limited to -0.5V or 10 mA, whichever is easier to achieve. The Maximum AC conditions are as follows: The device pins may undershoot to -2.0V or overshoot to V<sub>CCO</sub> + 2.0V, provided this over/undershoot lasts no more than 11 ns with a forcing current no greater than 100 mA.

6. For soldering guidelines, see the <u>Packaging Information</u> on the Xilinx<sup>®</sup> web site.

© 2000-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

Bndry

Scan

203

206

209

212

215

218

-

219

-

-

220

227

230

233

236

239

242

-

-

\_

245

248

251

254

257

-

260

263

266

-

275

-

-

-

276

280

283

286

289

-

292

## **XC2S30 Device Pinouts**

| <b>XC2S30 Device Pinouts</b> | (Continued) |

|------------------------------|-------------|

|------------------------------|-------------|

|                          |      | Fillou | .3    |       |       |       |                       |      |       |       |       |   |

|--------------------------|------|--------|-------|-------|-------|-------|-----------------------|------|-------|-------|-------|---|

| XC2S30 Pad               | Name |        |       |       |       | Bndry | XC2S30 Pad            | Name |       |       |       |   |

| Function                 | Bank | VQ100  | TQ144 | CS144 | PQ208 | Scan  | Function              | Bank | VQ100 | TQ144 | CS144 | ŀ |

| GND                      | -    | P1     | P143  | A1    | P1    | -     | I/O, V <sub>REF</sub> | 6    | P20   | P115  | K1    |   |

| TMS                      | -    | P2     | P142  | B1    | P2    | -     | I/O                   | 6    | -     | -     | -     |   |

| I/O                      | 7    | P3     | P141  | C2    | P3    | 113   | I/O                   | 6    | -     | P114  | K2    |   |

| I/O                      | 7    | -      | P140  | C1    | P4    | 116   | I/O                   | 6    | P21   | P113  | K3    |   |

| I/O                      | 7    | -      | -     | -     | P5    | 119   | I/O                   | 6    | P22   | P112  | L1    |   |

| I/O, V <sub>REF</sub>    | 7    | P4     | P139  | D4    | P6    | 122   | M1                    | -    | P23   | P111  | L2    |   |

| I/O                      | 7    | -      | P138  | D3    | P8    | 125   | GND                   | -    | P24   | P110  | L3    |   |

| I/O                      | 7    | P5     | P137  | D2    | P9    | 128   | MO                    | -    | P25   | P109  | M1    |   |

| I/O                      | 7    | P6     | P136  | D1    | P10   | 131   | V <sub>CCO</sub>      | 6    | P26   | P108  | M2    |   |

| GND                      | -    | -      | P135  | E4    | P11   | -     | V <sub>CCO</sub>      | 5    | P26   | P107  | N1    |   |

| V <sub>CCO</sub>         | 7    | -      | -     | -     | P12   | -     | M2                    | -    | P27   | P106  | N2    |   |

| 1/0                      | 7    | P7     | P134  | E3    | P14   | 134   | I/O                   | 5    | -     | P103  | K4    |   |

| I/O                      | 7    | -      | P133  | E2    | P15   | 137   | I/O                   | 5    | -     | -     | -     |   |

| I/O                      | 7    | -      | -     | -     | P16   | 140   | I/O, V <sub>REF</sub> | 5    | P30   | P102  | L4    |   |

| I/O                      | 7    | -      | -     | -     | P17   | 143   | I/O                   | 5    | -     | P101  | M4    |   |

| I/O                      | 7    | -      | -     | -     | P18   | 146   | I/O                   | 5    | P31   | P100  | N4    |   |

| GND                      | -    | -      | -     | -     | P19   | -     | I/O                   | 5    | P32   | P99   | K5    |   |

| I/O, V <sub>REF</sub>    | 7    | P8     | P132  | E1    | P20   | 149   | GND                   | -    | -     | P98   | L5    |   |

| I/O                      | 7    | P9     | P131  | F4    | P21   | 152   | V <sub>CCO</sub>      | 5    | -     | -     | -     |   |

| I/O                      | 7    | -      | P130  | F3    | P22   | 155   | V <sub>CCINT</sub>    | -    | P33   | P97   | M5    |   |

| I/O                      | 7    | -      | -     | -     | P23   | 158   | I/O                   | 5    | -     | P96   | N5    |   |

| I/O, IRDY <sup>(1)</sup> | 7    | P10    | P129  | F2    | P24   | 161   | I/O                   | 5    | -     | P95   | K6    |   |

| GND                      | -    | P11    | P128  | F1    | P25   | -     | I/O                   | 5    | -     | -     | -     |   |

| V <sub>CCO</sub>         | 7    | P12    | P127  | G2    | P26   | -     | I/O                   | 5    | -     | -     | -     |   |

| V <sub>CCO</sub>         | 6    | P12    | P127  | G2    | P26   | -     | I/O                   | 5    | -     | -     | -     |   |

| I/O, TRDY <sup>(1)</sup> | 6    | P13    | P126  | G1    | P27   | 164   | GND                   | -    | -     | -     | -     |   |

| V <sub>CCINT</sub>       | -    | P14    | P125  | G3    | P28   | -     | I/O, V <sub>REF</sub> | 5    | P34   | P94   | L6    |   |

| I/O                      | 6    | -      | P124  | G4    | P29   | 170   | I/O                   | 5    | -     | -     | -     |   |

| I/O                      | 6    | P15    | P123  | H1    | P30   | 173   | I/O                   | 5    | -     | P93   | M6    |   |

| I/O, V <sub>REF</sub>    | 6    | P16    | P122  | H2    | P31   | 176   | V <sub>CCINT</sub>    | -    | P35   | P92   | N6    |   |

| GND                      | -    | -      | -     | -     | P32   | -     | I, GCK1               | 5    | P36   | P91   | M7    |   |

| I/O                      | 6    | -      | -     | -     | P33   | 179   | V <sub>CCO</sub>      | 5    | P37   | P90   | N7    |   |

| I/O                      | 6    | -      | -     | -     | P34   | 182   | V <sub>CCO</sub>      | 4    | P37   | P90   | N7    |   |

| I/O                      | 6    | -      | -     | -     | P35   | 185   | GND                   | -    | P38   | P89   | L7    |   |

| I/O                      | 6    | -      | P121  | H3    | P36   | 188   | I, GCK0               | 4    | P39   | P88   | K7    |   |

| I/O                      | 6    | P17    | P120  | H4    | P37   | 191   | I/O                   | 4    | P40   | P87   | N8    |   |

| V <sub>CCO</sub>         | 6    | -      | -     | -     | P39   | -     | I/O                   | 4    | -     | P86   | M8    |   |

| GND                      | -    | -      | P119  | J1    | P40   | -     | I/O                   | 4    | -     | -     | -     |   |

| I/O                      | 6    | P18    | P118  | J2    | P41   | 194   | I/O, V <sub>REF</sub> | 4    | P41   | P85   | L8    |   |

| I/O                      | 6    | P19    | P117  | J3    | P42   | 197   | GND                   | -    | -     | -     | -     |   |

| I/O                      | 6    | -      | P116  | J4    | P43   | 200   | I/O                   | 4    | -     | -     | -     |   |

## XC2S30 Device Pinouts (Continued)

| XC2S30 Pad Name       |      |       |       |       |       | Bndry |

|-----------------------|------|-------|-------|-------|-------|-------|

| Function              | Bank | VQ100 | TQ144 | CS144 | PQ208 | Scan  |

| V <sub>CCINT</sub>    | -    | P85   | P24   | A9    | P171  | -     |

| I/O                   | 1    | -     | P23   | D8    | P172  | 24    |

| I/O                   | 1    | -     | P22   | C8    | P173  | 27    |

| I/O                   | 1    | -     | -     | -     | P174  | 30    |

| I/O                   | 1    | -     | -     | -     | P175  | 33    |

| I/O                   | 1    | -     | -     | -     | P176  | 36    |

| GND                   | -    | -     | -     | -     | P177  | -     |

| I/O, V <sub>REF</sub> | 1    | P86   | P21   | B8    | P178  | 39    |

| I/O                   | 1    | -     | -     | -     | P179  | 42    |

| I/O                   | 1    | -     | P20   | A8    | P180  | 45    |

| I/O                   | 1    | P87   | P19   | B7    | P181  | 48    |

| I, GCK2               | 1    | P88   | P18   | A7    | P182  | 54    |

| GND                   | -    | P89   | P17   | C7    | P183  | -     |

| V <sub>CCO</sub>      | 1    | P90   | P16   | D7    | P184  | -     |

| V <sub>CCO</sub>      | 0    | P90   | P16   | D7    | P184  | -     |

| I, GCK3               | 0    | P91   | P15   | A6    | P185  | 55    |

| V <sub>CCINT</sub>    | -    | P92   | P14   | B6    | P186  | -     |

| I/O                   | 0    | -     | P13   | C6    | P187  | 62    |

| I/O                   | 0    | -     | -     | -     | P188  | 65    |

| I/O, V <sub>REF</sub> | 0    | P93   | P12   | D6    | P189  | 68    |

| GND                   | -    | -     | -     | -     | P190  | -     |

| I/O                   | 0    | -     | -     | -     | P191  | 71    |

| I/O                   | 0    | -     | -     | -     | P192  | 74    |

| I/O                   | 0    | -     | -     | -     | P193  | 77    |

| I/O                   | 0    | -     | P11   | A5    | P194  | 80    |

| I/O                   | 0    | -     | P10   | B5    | P195  | 83    |

| V <sub>CCINT</sub>    | -    | P94   | P9    | C5    | P196  | -     |

| V <sub>CCO</sub>      | 0    | -     | -     | -     | P197  | -     |

| GND                   | -    | -     | P8    | D5    | P198  | -     |

| I/O                   | 0    | P95   | P7    | A4    | P199  | 86    |

| I/O                   | 0    | P96   | P6    | B4    | P200  | 89    |

| I/O                   | 0    | -     | -     | -     | P201  | 92    |

#### XC2S30 Device Pinouts (Continued)

| XC2S30 Pad Name       |      |       |       |       |       | Bndry |

|-----------------------|------|-------|-------|-------|-------|-------|

| Function              | Bank | VQ100 | TQ144 | CS144 | PQ208 | Scan  |

| I/O, V <sub>REF</sub> | 0    | P97   | P5    | C4    | P203  | 95    |

| I/O                   | 0    | -     | -     | -     | P204  | 98    |

| I/O                   | 0    | -     | P4    | A3    | P205  | 101   |

| I/O                   | 0    | P98   | P3    | B3    | P206  | 104   |

| тск                   | -    | P99   | P2    | C3    | P207  | -     |

| V <sub>CCO</sub>      | 0    | P100  | P1    | A2    | P208  | -     |

| V <sub>CCO</sub>      | 7    | P100  | P144  | B2    | P208  | -     |

04/18/01

#### Notes:

- 1. IRDY and TRDY can only be accessed when using Xilinx PCI cores.

- 2. See "VCCO Banks" for details on  $V_{CCO}$  banking.

## Additional XC2S30 Package Pins

#### VQ100

| Not Connected Pins |     |   |   |   |   |  |  |  |

|--------------------|-----|---|---|---|---|--|--|--|

| P28                | P29 | - | - | - | - |  |  |  |

| 11/02/00           |     |   |   |   |   |  |  |  |

#### TQ144

| Not Connected Pins |      |   |   |   |   |  |  |  |

|--------------------|------|---|---|---|---|--|--|--|

| P104               | P105 | - | - | - | - |  |  |  |

| 11/02/00           |      |   |   |   |   |  |  |  |

#### CS144

| Not Connected Pins |    |   |   |   |   |  |  |  |

|--------------------|----|---|---|---|---|--|--|--|

| M3                 | N3 | - | - | - | - |  |  |  |

| 11/02/00           |    |   |   |   |   |  |  |  |

#### PQ208

| Not Connected Pins |      |      |      |      |      |  |  |  |

|--------------------|------|------|------|------|------|--|--|--|

| P7                 | P13  | P38  | P44  | P55  | P56  |  |  |  |

| P60                | P97  | P112 | P118 | P143 | P149 |  |  |  |

| P165               | P202 | -    | -    | -    | -    |  |  |  |

| 11/02/00           |      |      |      |      |      |  |  |  |

#### Notes:

1. For the PQ208 package, P13, P38, P118, and P143, which are Not Connected Pins on the XC2S30, are assigned to  $V_{\rm CCINT}$  on larger devices.

## XC2S50 Device Pinouts (Continued)

| XC2S50 Pad Name       |      |       |       |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | Scan  |

| I/O                   | 0    | -     | -     | D8                          | 83    |

| I/O                   | 0    | -     | P188  | A6                          | 86    |

| I/O, V <sub>REF</sub> | 0    | P12   | P189  | B7                          | 89    |

| GND                   | -    | -     | P190  | GND*                        | -     |

| I/O                   | 0    | -     | P191  | C8                          | 92    |

| I/O                   | 0    | -     | P192  | D7                          | 95    |

| I/O                   | 0    | -     | P193  | E7                          | 98    |

| I/O                   | 0    | P11   | P194  | C7                          | 104   |

| I/O                   | 0    | P10   | P195  | B6                          | 107   |

| V <sub>CCINT</sub>    | -    | P9    | P196  | V <sub>CCINT</sub> *        | -     |

| V <sub>CCO</sub>      | 0    | -     | P197  | V <sub>CCO</sub><br>Bank 0* | -     |

| GND                   | -    | P8    | P198  | GND*                        | -     |

| I/O                   | 0    | P7    | P199  | A5                          | 110   |

| I/O                   | 0    | P6    | P200  | C6                          | 113   |

| I/O                   | 0    | -     | P201  | B5                          | 116   |

| I/O                   | 0    | -     | -     | D6                          | 119   |

| I/O                   | 0    | -     | P202  | A4                          | 122   |

| I/O, V <sub>REF</sub> | 0    | P5    | P203  | B4                          | 125   |

| GND                   | -    | -     | -     | GND*                        | -     |

| I/O                   | 0    | -     | P204  | E6                          | 128   |

| I/O                   | 0    | -     | -     | D5                          | 131   |

| I/O                   | 0    | P4    | P205  | A3                          | 134   |

| I/O                   | 0    | -     | -     | C5                          | 137   |

| I/O                   | 0    | P3    | P206  | B3                          | 140   |

| TCK                   | -    | P2    | P207  | C4                          | -     |

| V <sub>CCO</sub>      | 0    | P1    | P208  | V <sub>CCO</sub><br>Bank 0* | -     |

| V <sub>CCO</sub>      | 7    | P144  | P208  | V <sub>CCO</sub><br>Bank 7* | -     |

04/18/01

#### Notes:

- 1. IRDY and TRDY can only be accessed when using Xilinx PCI cores.

- Pads labelled GND\*, V<sub>CCINT</sub>\*, V<sub>CCO</sub> Bank 0\*, V<sub>CCO</sub> Bank 1\*, V<sub>CCO</sub> Bank 2\*, V<sub>CCO</sub> Bank 3\*, V<sub>CCO</sub> Bank 4\*, V<sub>CCO</sub> Bank 5\*, V<sub>CCO</sub> Bank 6\*, V<sub>CCO</sub> Bank 7\* are internally bonded to independent ground or power planes within the package.

- 3. See "VCCO Banks" for details on  $V_{CCO}$  banking.

## Additional XC2S50 Package Pins

| TQ144 |  |

|-------|--|

|-------|--|

| Not Connected Pins |      |   |   |   |   |  |  |  |

|--------------------|------|---|---|---|---|--|--|--|

| P104               | P105 | - | - | - | - |  |  |  |

| 11/02/00           |      |   |   |   |   |  |  |  |

## XC2S100 Device Pinouts (Continued)

| XC2S100 Pad<br>Name   |      |       |       |                             |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | FG456                       | Scan  |

| V <sub>CCINT</sub>    | -    | -     | P38   | $V_{CCINT}^{*}$             | V <sub>CCINT</sub> *        | -     |

| V <sub>CCO</sub>      | 6    | -     | P39   | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -     |

| GND                   | -    | P119  | P40   | GND*                        | GND*                        | -     |

| I/O                   | 6    | P118  | P41   | K4                          | T1                          | 314   |

| I/O, V <sub>REF</sub> | 6    | P117  | P42   | M1                          | R4                          | 317   |

| I/O                   | 6    | -     | -     | -                           | T2                          | 320   |

| I/O                   | 6    | P116  | P43   | L4                          | U1                          | 323   |

| I/O                   | 6    | -     | -     | M2                          | R5                          | 326   |

| I/O                   | 6    | -     | P44   | L3                          | U2                          | 332   |

| I/O, V <sub>REF</sub> | 6    | P115  | P45   | N1                          | Т3                          | 335   |

| V <sub>CCO</sub>      | 6    | -     | -     | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -     |

| GND                   | -    | -     | -     | GND*                        | GND*                        | -     |

| I/O                   | 6    | -     | P46   | P1                          | T4                          | 338   |

| I/O                   | 6    | -     | -     | L5                          | W1                          | 341   |

| I/O                   | 6    | -     | -     | -                           | U4                          | 344   |

| I/O                   | 6    | P114  | P47   | N2                          | Y1                          | 347   |

| I/O                   | 6    | -     | -     | M4                          | W2                          | 350   |

| I/O                   | 6    | P113  | P48   | R1                          | Y2                          | 356   |

| I/O                   | 6    | P112  | P49   | М3                          | W3                          | 359   |

| M1                    | -    | P111  | P50   | P2                          | U5                          | 362   |

| GND                   | -    | P110  | P51   | GND*                        | GND*                        | -     |

| MO                    | -    | P109  | P52   | N3                          | AB2                         | 363   |

| V <sub>CCO</sub>      | 6    | P108  | P53   | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -     |

| V <sub>CCO</sub>      | 5    | P107  | P53   | V <sub>CCO</sub><br>Bank 5* | V <sub>CCO</sub><br>Bank 5* | -     |

| M2                    | -    | P106  | P54   | R3                          | Y4                          | 364   |

| I/O                   | 5    | -     | -     | N5                          | V7                          | 374   |

| I/O                   | 5    | P103  | P57   | T2                          | Y6                          | 377   |

| I/O                   | 5    | -     | -     | -                           | AA4                         | 380   |

| I/O                   | 5    | -     | -     | P5                          | W6                          | 383   |

| I/O                   | 5    | -     | P58   | Т3                          | Y7                          | 386   |

| GND                   | -    | -     | -     | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 5    | -     | -     | V <sub>CCO</sub><br>Bank 5* | V <sub>CCO</sub><br>Bank 5* | -     |

| I/O, V <sub>REF</sub> | 5    | P102  | P59   | T4                          | AA5                         | 389   |

| I/O                   | 5    | -     | P60   | M6                          | AB5                         | 392   |

| I/O                   | 5    | -     | -     | T5                          | AB6                         | 398   |

| I/O                   | 5    | P101  | P61   | N6                          | AA7                         | 401   |

| I/O                   | 5    | -     | -     | -                           | W7                          | 404   |

## XC2S100 Device Pinouts (Continued)

| XC2S100<br>Name       |      |       |       |                             |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | FG456                       | Scan  |

| I/O, V <sub>REF</sub> | 5    | P100  | P62   | R5                          | W8                          | 407   |

| I/O                   | 5    | P99   | P63   | P6                          | Y8                          | 410   |

| GND                   | -    | P98   | P64   | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 5    | -     | P65   | V <sub>CCO</sub><br>Bank 5* | V <sub>CCO</sub><br>Bank 5* | -     |

| V <sub>CCINT</sub>    | -    | P97   | P66   | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| I/O                   | 5    | P96   | P67   | R6                          | AA8                         | 413   |

| I/O                   | 5    | P95   | P68   | M7                          | V9                          | 416   |

| I/O                   | 5    | -     | -     | -                           | AB9                         | 419   |

| I/O                   | 5    | -     | P69   | N7                          | Y9                          | 422   |

| I/O                   | 5    | -     | P70   | T6                          | W10                         | 428   |

| I/O                   | 5    | -     | P71   | P7                          | AB10                        | 431   |

| GND                   | -    | -     | P72   | GND*                        | GND*                        | -     |

| I/O, V <sub>REF</sub> | 5    | P94   | P73   | P8                          | Y10                         | 434   |

| I/O                   | 5    | -     | P74   | R7                          | V11                         | 437   |

| I/O                   | 5    | -     | -     | T7                          | W11                         | 440   |

| I/O                   | 5    | P93   | P75   | Т8                          | AB11                        | 443   |

| V <sub>CCINT</sub>    | -    | P92   | P76   | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| I, GCK1               | 5    | P91   | P77   | R8                          | Y11                         | 455   |

| V <sub>CCO</sub>      | 5    | P90   | P78   | V <sub>CCO</sub><br>Bank 5* | V <sub>CCO</sub><br>Bank 5* | -     |

| V <sub>CCO</sub>      | 4    | P90   | P78   | V <sub>CCO</sub><br>Bank 4* | V <sub>CCO</sub><br>Bank 4* | -     |

| GND                   | -    | P89   | P79   | GND*                        | GND*                        | -     |

| I, GCK0               | 4    | P88   | P80   | N8                          | W12                         | 456   |

| I/O                   | 4    | P87   | P81   | N9                          | U12                         | 460   |

| I/O                   | 4    | P86   | P82   | R9                          | Y12                         | 466   |

| I/O                   | 4    | -     | -     | N10                         | AA12                        | 469   |

| I/O                   | 4    | -     | P83   | Т9                          | AB13                        | 472   |

| I/O, V <sub>REF</sub> | 4    | P85   | P84   | P9                          | AA13                        | 475   |

| GND                   | -    | -     | P85   | GND*                        | GND*                        | -     |

| I/O                   | 4    | -     | P86   | M10                         | Y13                         | 478   |

| I/O                   | 4    | -     | P87   | R10                         | V13                         | 481   |

| I/O                   | 4    | -     | P88   | P10                         | AA14                        | 487   |

| I/O                   | 4    | -     | -     | -                           | V14                         | 490   |

| I/O                   | 4    | P84   | P89   | T10                         | AB15                        | 493   |

| I/O                   | 4    | P83   | P90   | R11                         | AA15                        | 496   |

| V <sub>CCINT</sub>    | -    | P82   | P91   | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| V <sub>CCO</sub>      | 4    | -     | P92   | V <sub>CCO</sub><br>Bank 4* | V <sub>CCO</sub><br>Bank 4* | -     |

| GND                   | -    | P81   | P93   | GND*                        | GND*                        | -     |

| I/O                   | 4    | P80   | P94   | M11                         | Y15                         | 499   |

## XC2S200 Device Pinouts (Continued)

| XC2S200 Pac              |      |       |                             | Bndry                       |      |

|--------------------------|------|-------|-----------------------------|-----------------------------|------|

| Function                 | Bank | PQ208 | FG256                       | FG456                       | Scan |

| V <sub>CCO</sub>         | 3    | P117  | V <sub>CCO</sub><br>Bank 3* | V <sub>CCO</sub><br>Bank 3* | -    |

| V <sub>CCINT</sub>       | -    | P118  | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -    |

| I/O (D5)                 | 3    | P119  | M16                         | R21                         | 833  |

| I/O                      | 3    | P120  | K14                         | P18                         | 836  |

| I/O                      | 3    | -     | -                           | R22                         | 839  |

| I/O                      | 3    | -     | -                           | P19                         | 842  |

| I/O                      | 3    | -     | L16                         | P20                         | 845  |

| GND                      | -    | -     | GND*                        | GND*                        | -    |

| I/O                      | 3    | P121  | K13                         | P21                         | 848  |

| I/O                      | 3    | -     | -                           | N19                         | 851  |

| I/O                      | 3    | -     | -                           | P22                         | 854  |

| I/O                      | 3    | P122  | L15                         | N18                         | 857  |

| I/O                      | 3    | P123  | K12                         | N20                         | 860  |

| GND                      | -    | P124  | GND*                        | GND*                        | -    |

| V <sub>CCO</sub>         | 3    | -     | V <sub>CCO</sub><br>Bank 3* | V <sub>CCO</sub><br>Bank 3* | -    |

| I/O, V <sub>REF</sub>    | 3    | P125  | K16                         | N21                         | 863  |

| I/O (D4)                 | 3    | P126  | J16                         | N22                         | 866  |

| I/O                      | 3    | -     | -                           | M17                         | 872  |

| I/O                      | 3    | -     | J14                         | M19                         | 875  |

| I/O                      | 3    | P127  | K15                         | M20                         | 878  |

| I/O                      | 3    | -     | -                           | M18                         | 881  |

| V <sub>CCINT</sub>       | -    | P128  | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -    |

| I/O, TRDY <sup>(1)</sup> | 3    | P129  | J15                         | M22                         | 890  |

| V <sub>CCO</sub>         | 3    | P130  | V <sub>CCO</sub><br>Bank 3* | V <sub>CCO</sub><br>Bank 3* | -    |

| V <sub>CCO</sub>         | 2    | P130  | V <sub>CCO</sub><br>Bank 2* | V <sub>CCO</sub><br>Bank 2* | -    |

| GND                      | -    | P131  | GND*                        | GND*                        | -    |

| I/O, IRDY <sup>(1)</sup> | 2    | P132  | H16                         | L20                         | 893  |

| I/O                      | 2    | P133  | H14                         | L17                         | 896  |

| I/O                      | 2    | -     | -                           | L18                         | 902  |

| I/O                      | 2    | P134  | H15                         | L21                         | 905  |

| I/O                      | 2    | -     | J13                         | L22                         | 908  |

| I/O                      | 2    | -     | -                           | K19                         | 911  |

| I/O (D3)                 | 2    | P135  | G16                         | K20                         | 917  |

| I/O, V <sub>REF</sub>    | 2    | P136  | H13                         | K21                         | 920  |

| V <sub>CCO</sub>         | 2    | -     | V <sub>CCO</sub><br>Bank 2* | V <sub>CCO</sub><br>Bank 2* | -    |

| GND                      | -    | P137  | GND*                        | GND*                        | -    |

| I/O                      | 2    | P138  | G14                         | K22                         | 923  |

| I/O                      | 2    | P139  | G15                         | J21                         | 926  |

## XC2S200 Device Pinouts (Continued)

| XC2S200 Pad           | l Name |       |                             |                             | Bndry |

|-----------------------|--------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank   | PQ208 | FG256                       | FG456                       | Scan  |

| I/O                   | 2      | -     | -                           | K18                         | 929   |

| I/O                   | 2      | -     | -                           | J20                         | 932   |

| I/O                   | 2      | P140  | G12                         | J18                         | 935   |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O                   | 2      | -     | F16                         | J22                         | 938   |

| I/O                   | 2      | -     | -                           | J19                         | 941   |

| I/O                   | 2      | -     | -                           | H21                         | 944   |

| I/O                   | 2      | P141  | G13                         | H19                         | 947   |

| I/O (D2)              | 2      | P142  | F15                         | H20                         | 950   |

| V <sub>CCINT</sub>    | -      | P143  | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| V <sub>CCO</sub>      | 2      | P144  | V <sub>CCO</sub><br>Bank 2* | V <sub>CCO</sub><br>Bank 2* | -     |

| GND                   | -      | P145  | GND*                        | GND*                        | -     |

| I/O (D1)              | 2      | P146  | E16                         | H22                         | 953   |

| I/O, V <sub>REF</sub> | 2      | P147  | F14                         | H18                         | 956   |

| I/O                   | 2      | -     | -                           | G21                         | 962   |

| I/O                   | 2      | P148  | D16                         | G18                         | 965   |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O                   | 2      | -     | F12                         | G20                         | 968   |

| I/O                   | 2      | -     | -                           | G19                         | 971   |

| I/O                   | 2      | -     | -                           | F22                         | 974   |

| I/O                   | 2      | P149  | E15                         | F19                         | 977   |

| I/O, V <sub>REF</sub> | 2      | P150  | F13                         | F21                         | 980   |

| V <sub>CCO</sub>      | 2      | -     | V <sub>CCO</sub><br>Bank 2* | V <sub>CCO</sub><br>Bank 2* | -     |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O                   | 2      | P151  | E14                         | F20                         | 983   |

| I/O                   | 2      | -     | C16                         | F18                         | 986   |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O                   | 2      | -     | -                           | E22                         | 989   |

| I/O                   | 2      | -     | -                           | E21                         | 995   |

| I/O, V <sub>REF</sub> | 2      | P152  | E13                         | D22                         | 998   |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O                   | 2      | -     | B16                         | E20                         | 1001  |

| I/O                   | 2      | -     | -                           | D21                         | 1004  |

| I/O                   | 2      | -     | -                           | C22                         | 1007  |

| I/O (DIN, D0)         | 2      | P153  | D14                         | D20                         | 1013  |

| I/O (DOUT,<br>BUSY)   | 2      | P154  | C15                         | C21                         | 1016  |

| CCLK                  | 2      | P155  | D15                         | B22                         | 1019  |

| V <sub>CCO</sub>      | 2      | P156  | V <sub>CCO</sub><br>Bank 2* | V <sub>CCO</sub><br>Bank 2* | -     |

## XC2S200 Device Pinouts (Continued)

| XC2S200 Pad           | l Name |       |                             |                             | Bndry |

|-----------------------|--------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank   | PQ208 | FG256                       | FG456                       | Scan  |

| V <sub>CCO</sub>      | 1      | P156  | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| TDO                   | 2      | P157  | B14                         | A21                         | -     |

| GND                   | -      | P158  | GND*                        | GND*                        | -     |

| TDI                   | -      | P159  | A15                         | B20                         | -     |

| I/O ( <u>CS</u> )     | 1      | P160  | B13                         | C19                         | 0     |

| I/O (WRITE)           | 1      | P161  | C13                         | A20                         | 3     |

| I/O                   | 1      | -     | -                           | B19                         | 9     |

| I/O                   | 1      | -     | -                           | C18                         | 12    |

| I/O                   | 1      | -     | C12                         | D17                         | 15    |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O, V <sub>REF</sub> | 1      | P162  | A14                         | A19                         | 18    |

| I/O                   | 1      | -     | -                           | B18                         | 21    |

| I/O                   | 1      | -     | -                           | E16                         | 27    |

| I/O                   | 1      | -     | D12                         | C17                         | 30    |

| I/O                   | 1      | P163  | B12                         | D16                         | 33    |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 1      | -     | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| I/O, V <sub>REF</sub> | 1      | P164  | C11                         | A18                         | 36    |

| I/O                   | 1      | P165  | A13                         | B17                         | 39    |

| I/O                   | 1      | -     | -                           | E15                         | 42    |

| I/O                   | 1      | -     | -                           | A17                         | 45    |

| I/O                   | 1      | -     | D11                         | D15                         | 48    |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O                   | 1      | P166  | A12                         | C16                         | 51    |

| I/O                   | 1      | -     | -                           | D14                         | 54    |

| I/O, V <sub>REF</sub> | 1      | P167  | E11                         | E14                         | 60    |

| I/O                   | 1      | P168  | B11                         | A16                         | 63    |

| GND                   | -      | P169  | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 1      | P170  | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| V <sub>CCINT</sub>    | -      | P171  | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| I/O                   | 1      | P172  | A11                         | C15                         | 66    |

| I/O                   | 1      | P173  | C10                         | B15                         | 69    |

| I/O                   | 1      | -     | -                           | E13                         | 72    |

| I/O                   | 1      | -     | -                           | A15                         | 75    |

| I/O                   | 1      | -     | -                           | F12                         | 78    |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O                   | 1      | P174  | B10                         | C14                         | 81    |

| I/O                   | 1      | -     | -                           | B14                         | 84    |