# E·XFL

#### AMD Xilinx - XC2S15-5TQG144I Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | 96                                                          |

| Number of Logic Elements/Cells | 432                                                         |

| Total RAM Bits                 | 16384                                                       |

| Number of I/O                  | 86                                                          |

| Number of Gates                | 15000                                                       |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                          |

| Package / Case                 | 144-LQFP                                                    |

| Supplier Device Package        | 144-TQFP (20x20)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s15-5tqg144i |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **General Overview**

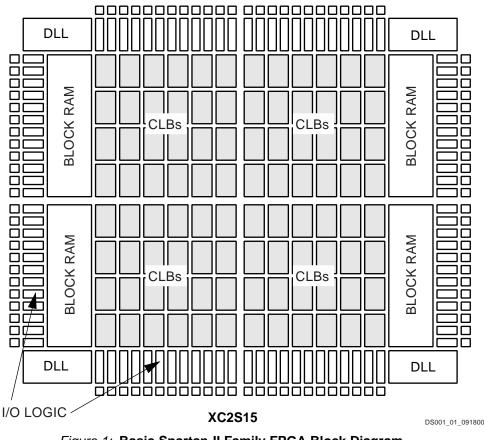

The Spartan-II family of FPGAs have a regular, flexible, programmable architecture of Configurable Logic Blocks (CLBs), surrounded by a perimeter of programmable Input/Output Blocks (IOBs). There are four Delay-Locked Loops (DLLs), one at each corner of the die. Two columns of block RAM lie on opposite sides of the die, between the CLBs and the IOB columns. These functional elements are interconnected by a powerful hierarchy of versatile routing channels (see Figure 1).

Spartan-II FPGAs are customized by loading configuration data into internal static memory cells. Unlimited reprogramming cycles are possible with this approach. Stored values in these cells determine logic functions and interconnections implemented in the FPGA. Configuration data can be read from an external serial PROM (master serial mode), or written into the FPGA in slave serial, slave parallel, or Boundary Scan modes.

Spartan-II FPGAs are typically used in high-volume applications where the versatility of a fast programmable solution adds benefits. Spartan-II FPGAs are ideal for shortening product development cycles while offering a cost-effective solution for high volume production.

Spartan-II FPGAs achieve high-performance, low-cost operation through advanced architecture and semiconductor technology. Spartan-II devices provide system clock rates up to 200 MHz. In addition to the conventional benefits of high-volume programmable logic solutions, Spartan-II FPGAs also offer on-chip synchronous single-port and dual-port RAM (block and distributed form), DLL clock drivers, programmable set and reset on all flip-flops, fast carry logic, and many other features.

Figure 1: Basic Spartan-II Family FPGA Block Diagram

Boundary-scan operation is independent of individual IOB configurations, and unaffected by package type. All IOBs, including unbonded ones, are treated as independent 3-state bidirectional pins in a single scan chain. Retention of the bidirectional test capability after configuration facilitates the testing of external interconnections.

Table 7 lists the boundary-scan instructions supported in Spartan-II FPGAs. Internal signals can be captured during EXTEST by connecting them to unbonded or unused IOBs. They may also be connected to the unused outputs of IOBs defined as unidirectional input pins.

| Boundary-Scan<br>Command | Binary<br>Code[4:0] | Description                                                   |

|--------------------------|---------------------|---------------------------------------------------------------|

| EXTEST                   | 00000               | Enables boundary-scan<br>EXTEST operation                     |

| SAMPLE                   | 00001               | Enables boundary-scan<br>SAMPLE operation                     |

| USR1                     | 00010               | Access user-defined<br>register 1                             |

| USR2                     | 00011               | Access user-defined<br>register 2                             |

| CFG_OUT                  | 00100               | Access the<br>configuration bus for<br>Readback               |

| CFG_IN                   | 00101               | Access the<br>configuration bus for<br>Configuration          |

| INTEST                   | 00111               | Enables boundary-scan<br>INTEST operation                     |

| USRCODE                  | 01000               | Enables shifting out<br>USER code                             |

| IDCODE                   | 01001               | Enables shifting out of<br>ID Code                            |

| HIZ                      | 01010               | Disables output pins<br>while enabling the<br>Bypass Register |

| JSTART                   | 01100               | Clock the start-up<br>sequence when<br>StartupClk is TCK      |

| BYPASS                   | 11111               | Enables BYPASS                                                |

| RESERVED                 | All other codes     | Xilinx <sup>®</sup> reserved<br>instructions                  |

### Table 7: Boundary-Scan Instructions

The public boundary-scan instructions are available prior to configuration. After configuration, the public instructions remain available together with any USERCODE instructions installed during the configuration. While the SAMPLE and BYPASS instructions are available during configuration, it is recommended that boundary-scan operations not be performed during this transitional period.

In addition to the test instructions outlined above, the boundary-scan circuitry can be used to configure the FPGA, and also to read back the configuration data.

To facilitate internal scan chains, the User Register provides three outputs (Reset, Update, and Shift) that represent the corresponding states in the boundary-scan internal state machine.

# Configuration

Configuration is the process by which the bitstream of a design, as generated by the Xilinx software, is loaded into the internal configuration memory of the FPGA. Spartan-II devices support both serial configuration, using the master/slave serial and JTAG modes, as well as byte-wide configuration employing the Slave Parallel mode.

## **Configuration File**

Spartan-II devices are configured by sequentially loading frames of data that have been concatenated into a configuration file. Table 8 shows how much nonvolatile storage space is needed for Spartan-II devices.

It is important to note that, while a PROM is commonly used to store configuration data before loading them into the FPGA, it is by no means required. Any of a number of different kinds of under populated nonvolatile storage already available either on or off the board (i.e., hard drives, FLASH cards, etc.) can be used. For more information on configuration without a PROM, refer to <u>XAPP098</u>, *The Low-Cost, Efficient Serial Configuration of Spartan FPGAs*.

| Device  | Configuration File Size (Bits) |

|---------|--------------------------------|

| XC2S15  | 197,696                        |

| XC2S30  | 336,768                        |

| XC2S50  | 559,200                        |

| XC2S100 | 781,216                        |

| XC2S150 | 1,040,096                      |

| XC2S200 | 1,335,840                      |

#### Table 8: Spartan-II Configuration File Size

#### Modes

Spartan-II devices support the following four configuration modes:

- Slave Serial mode

- Master Serial mode

- Slave Parallel mode

- Boundary-scan mode

The Configuration mode pins (M2, M1, M0) select among these configuration modes with the option in each case of having the IOB pins either pulled up or left floating prior to the end of configuration. The selection codes are listed in Table 9.

Configuration through the boundary-scan port is always available, independent of the mode selection. Selecting the boundary-scan mode simply turns off the other modes. The three mode pins have internal pull-up resistors, and default to a logic High if left unconnected.

| Configuration Mode  | Preconfiguration<br>Pull-ups | МО | M1 | M2 | CCLK<br>Direction | Data Width | Serial D <sub>OUT</sub> |

|---------------------|------------------------------|----|----|----|-------------------|------------|-------------------------|

| Master Serial mode  | No                           | 0  | 0  | 0  | Out               | 1          | Yes                     |

|                     | Yes                          | 0  | 0  | 1  |                   |            |                         |

| Slave Parallel mode | Yes                          | 0  | 1  | 0  | In                | 8          | No                      |

|                     | No                           | 0  | 1  | 1  |                   |            |                         |

| Boundary-Scan mode  | Yes                          | 1  | 0  | 0  | N/A               | 1          | No                      |

|                     | No                           | 1  | 0  | 1  |                   |            |                         |

| Slave Serial mode   | Yes                          | 1  | 1  | 0  | In                | 1          | Yes                     |

|                     | No                           | 1  | 1  | 1  |                   |            |                         |

#### Table 9: Configuration Modes

#### Notes:

During power-on and throughout configuration, the I/O drivers will be in a high-impedance state. After configuration, all unused I/Os (those not assigned signals) will remain in a high-impedance state. Pins used as outputs may pulse High at the end of configuration (see <u>Answer 10504</u>).

2. If the Mode pins are set for preconfiguration pull-ups, those resistors go into effect once the rising edge of INIT samples the Mode pins. They will stay in effect until GTS is released during startup, after which the UnusedPin bitstream generator option will determine whether the unused I/Os have a pull-up, pull-down, or no resistor.

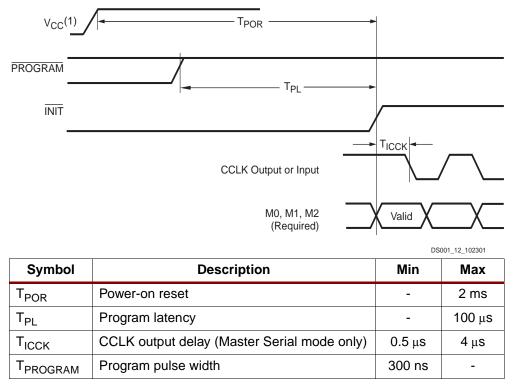

#### Notes: (referring to waveform above:)

1. Before configuration can begin,  $V_{CCINT}$  must be greater than 1.6V and  $V_{CCO}$  Bank 2 must be greater than 1.0V.

Figure 12: Configuration Timing on Power-Up

#### **Clearing Configuration Memory**

The device indicates that clearing the configuration memory is in progress by driving INIT Low. At this time, the user can delay configuration by holding either PROGRAM or INIT Low, which causes the device to remain in the memory clearing phase. Note that the bidirectional INIT line is driving a Low logic level during memory clearing. To avoid contention, use an open-drain driver to keep INIT Low.

With no delay in force, the device indicates that the memory is completely clear by driving INIT High. The FPGA samples its mode pins on this Low-to-High transition.

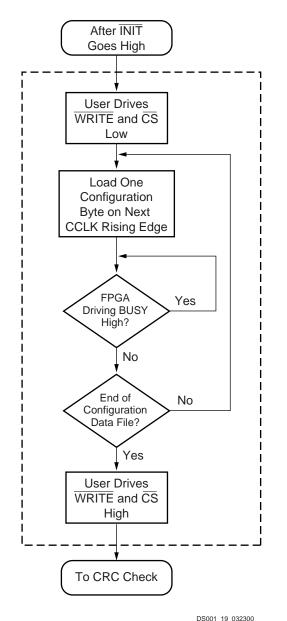

### Loading Configuration Data

Once INIT is High, the user can begin loading configuration data frames into the device. The details of loading the configuration data are discussed in the sections treating the configuration modes individually. The sequence of operations necessary to load configuration data using the serial modes is shown in Figure 14. Loading data using the Slave Parallel mode is shown in Figure 19, page 25.

#### **CRC Error Checking**

During the loading of configuration data, a CRC value embedded in the configuration file is checked against a CRC value calculated within the FPGA. If the CRC values do not match, the FPGA drives INIT Low to indicate that a frame error has occurred and configuration is aborted.

To reconfigure the device, the PROGRAM pin should be asserted to reset the configuration logic. Recycling power also resets the FPGA for configuration. See "Clearing Configuration Memory".

#### Start-up

The start-up sequence oversees the transition of the FPGA from the configuration state to full user operation. A match of CRC values, indicating a successful loading of the configuration data, initiates the sequence.

During start-up, the device performs four operations:

- 1. The assertion of DONE. The failure of DONE to go High may indicate the unsuccessful loading of configuration data.

- 2. The release of the Global Three State net. This activates I/Os to which signals are assigned. The remaining I/Os stay in a high-impedance state with internal weak pull-down resistors present.

- 3. Negates Global Set Reset (GSR). This allows all flip-flops to change state.

- 4. The assertion of Global Write Enable (GWE). This allows all RAMs and flip-flops to change state.

## Master Serial Mode

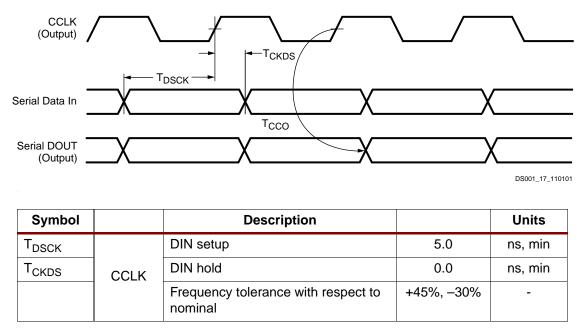

In Master Serial mode, the CCLK output of the FPGA drives a Xilinx PROM which feeds a serial stream of configuration data to the FPGA's DIN input. Figure 15 shows a Master Serial FPGA configuring a Slave Serial FPGA from a PROM. A Spartan-II device in Master Serial mode should be connected as shown for the device on the left side. Master Serial mode is selected by a <00x> on the mode pins (M0, M1, M2). The PROM RESET pin is driven by INIT, and CE input is driven by DONE. The interface is identical to the slave serial mode except that an oscillator internal to the FPGA is used to generate the configuration clock (CCLK). Any of a number of different frequencies ranging from 4 to 60 MHz can be set using the ConfigRate option in the Xilinx software. On power-up, while the first 60 bytes of the configuration data are being loaded, the CCLK frequency is always 2.5 MHz. This frequency is used until the ConfigRate bits, part of the configuration file, have been loaded into the FPGA, at which point, the frequency changes to the selected ConfigRate. Unless a different frequency is specified in the design, the default ConfigRate is 4 MHz. The frequency of the CCLK signal created by the internal oscillator has a variance of +45%, -30% from the specified value.

Figure 17 shows the timing for Master Serial configuration. The FPGA accepts one bit of configuration data on each rising CCLK edge. After the FPGA has been loaded, the data for the next device in a daisy-chain is presented on the DOUT pin after the rising CCLK edge.

Figure 17: Master Serial Mode Timing

## **Slave Parallel Mode**

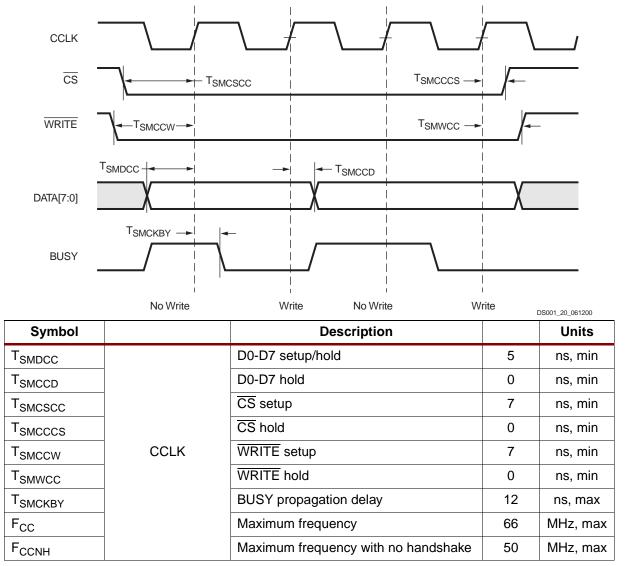

The Slave Parallel mode is the fastest configuration option. Byte-wide data is written into the FPGA. A BUSY flag is provided for controlling the flow of data at a clock frequency  $F_{CCNH}$  above 50 MHz.

Figure 18, page 24 shows the connections for two Spartan-II devices using the Slave Parallel mode. Slave Parallel mode is selected by a <011> on the mode pins (M0, M1, M2).

If a configuration file of the format .bit, .rbt, or non-swapped HEX is used for parallel programming, then the most significant bit (i.e. the left-most bit of each configuration byte, as displayed in a text editor) must be routed to the D0 input on the FPGA. The agent controlling configuration is not shown. Typically, a processor, a microcontroller, or CPLD controls the Slave Parallel interface. The controlling agent provides byte-wide configuration data, CCLK, a Chip Select ( $\overline{CS}$ ) signal and a Write signal (WRITE). If BUSY is asserted (High) by the FPGA, the data must be held until BUSY goes Low.

After configuration, the pins of the Slave Parallel port (D0-D7) can be used as additional user I/O. Alternatively, the port may be retained to permit high-speed 8-bit readback. Then data can be read by de-asserting WRITE. See "Readback," page 25.

www.xilinx.com

If CCLK is slower than  $\rm F_{CCNH},$  the FPGA will never assert BUSY. In this case, the above handshake is unnecessary, and data can simply be entered into the FPGA every CCLK cycle.

#### Figure 19: Loading Configuration Data for the Slave Parallel Mode

A configuration packet does not have to be written in one continuous stretch, rather it can be split into many write sequences. Each sequence would involve assertion of  $\overline{CS}$ .

In applications where multiple clock cycles may be required to access the configuration data before each byte can be loaded into the Slave Parallel interface, a new byte of data may not be ready for each consecutive CCLK edge. In such a case the  $\overline{CS}$  signal may be de-asserted until the next byte is valid on D0-D7. While  $\overline{CS}$  is High, the Slave Parallel interface does not expect any data and ignores all CCLK transitions. However, to avoid aborting configuration, WRITE must continue to be asserted while CS is asserted.

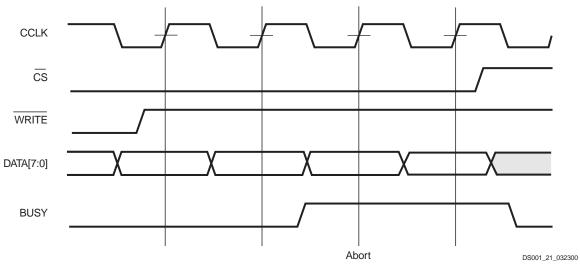

#### Abort

To abort configuration during a write sequence, de-assert  $\overline{\text{WRITE}}$  while holding  $\overline{\text{CS}}$  Low. The abort operation is initiated at the rising edge of CCLK, as shown in Figure 21, page 26. The device will remain BUSY until the aborted operation is complete. After aborting configuration, data is assumed to be unaligned to word boundaries and the FPGA requires a new synchronization word prior to accepting any new packets.

## **Boundary-Scan Mode**

In the boundary-scan mode, no nondedicated pins are required, configuration being done entirely through the IEEE 1149.1 Test Access Port.

Configuration through the TAP uses the special CFG\_IN instruction. This instruction allows data input on TDI to be converted into data packets for the internal configuration bus.

The following steps are required to configure the FPGA through the boundary-scan port.

- 1. Load the CFG\_IN instruction into the boundary-scan instruction register (IR)

- 2. Enter the Shift-DR (SDR) state

- 3. Shift a standard configuration bitstream into TDI

- 4. Return to Run-Test-Idle (RTI)

- 5. Load the JSTART instruction into IR

- 6. Enter the SDR state

- 7. Clock TCK through the sequence (the length is programmable)

- 8. Return to RTI

Configuration and readback via the TAP is always available. The boundary-scan mode simply locks out the other modes. The boundary-scan mode is selected by a <10x> on the mode pins (M0, M1, M2).

## Readback

The configuration data stored in the Spartan-II FPGA configuration memory can be readback for verification. Along with the configuration data it is possible to readback the contents of all flip-flops/latches, LUT RAMs, and block RAMs. This capability is used for real-time debugging.

For more detailed information see <u>XAPP176</u>, Spartan-II FPGA Family Configuration and Readback.

Figure 20: Slave Parallel Write Timing

Figure 21: Slave Parallel Write Abort Waveforms

# **Using Block RAM Features**

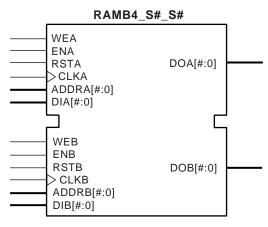

The Spartan-II FPGA family provides dedicated blocks of on-chip, true dual-read/write port synchronous RAM, with 4096 memory cells. Each port of the block RAM memory can be independently configured as a read/write port, a read port, a write port, and can be configured to a specific data width. The block RAM memory offers new capabilities allowing the FPGA designer to simplify designs.

## **Operating Modes**

Block RAM memory supports two operating modes.

- Read Through

- Write Back

### Read Through (One Clock Edge)

The read address is registered on the read port clock edge and data appears on the output after the RAM access time. Some memories may place the latch/register at the outputs depending on the desire to have a faster clock-to-out versus setup time. This is generally considered to be an inferior solution since it changes the read operation to an asynchronous function with the possibility of missing an address/control line transition during the generation of the read pulse clock.

## Write Back (One Clock Edge)

The write address is registered on the write port clock edge and the data input is written to the memory and mirrored on the write port input.

## **Block RAM Characteristics**

- 1. All inputs are registered with the port clock and have a setup to clock timing specification.

- 2. All outputs have a read through or write back function depending on the state of the port WE pin. The outputs relative to the port clock are available after the clock-to-out timing specification.

- 3. The block RAM are true SRAM memories and do not have a combinatorial path from the address to the output. The LUT cells in the CLBs are still available with this function.

- 4. The ports are completely independent from each other (*i.e.*, clocking, control, address, read/write function, and data width) without arbitration.

- 5. A write operation requires only one clock edge.

- 6. A read operation requires only one clock edge.

The output ports are latched with a self timed circuit to guarantee a glitch free read. The state of the output port will not change until the port executes another read or write operation.

## **Library Primitives**

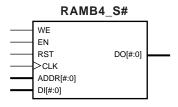

Figure 31 and Figure 32 show the two generic library block RAM primitives. Table 11 describes all of the available primitives for synthesis and simulation.

DS001\_31\_061200

DS001\_32\_061200

Figure 32: Single-Port Block RAM Memory

#### Table 11: Available Library Primitives

| Primitive    | Port A Width | Port B Width |

|--------------|--------------|--------------|

| RAMB4_S1     | 1            | N/A          |

| RAMB4_S1_S1  |              | 1            |

| RAMB4_S1_S2  |              | 2            |

| RAMB4_S1_S4  |              | 4            |

| RAMB4_S1_S8  |              | 8            |

| RAMB4_S1_S16 |              | 16           |

| RAMB4_S2     | 2            | N/A          |

| RAMB4_S2_S2  |              | 2            |

| RAMB4_S2_S4  |              | 4            |

| RAMB4_S2_S8  |              | 8            |

| RAMB4_S2_S16 |              | 16           |

property. This property could have one of the following seven values.

DRIVE=2 DRIVE=4 DRIVE=6 DRIVE=8 DRIVE=12 (Default) DRIVE=16 DRIVE=24

## **Design Considerations**

## Reference Voltage (V<sub>RFF</sub>) Pins

Low-voltage I/O standards with a differential amplifier input buffer require an input reference voltage (V<sub>RFF</sub>). Provide the V<sub>RFF</sub> as an external signal to the device.

The voltage reference signal is "banked" within the device on a half-edge basis such that for all packages there are eight independent V<sub>RFF</sub> banks internally. See Figure 36, page 39 for a representation of the I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a V<sub>RFF</sub> input.

Within each V<sub>REF</sub> bank, any input buffers that require a V<sub>RFF</sub> signal must be of the same type. Output buffers of any type and input buffers can be placed without requiring a reference voltage within the same V<sub>REF</sub> bank.

## Output Drive Source Voltage (V<sub>CCO</sub>) Pins

Many of the low voltage I/O standards supported by Versatile I/Os require a different output drive source voltage  $(V_{CCO})$ . As a result each device can often have to support multiple output drive source voltages.

The V<sub>CCO</sub> supplies are internally tied together for some packages. The VQ100 and the PQ208 provide one combined  $V_{\mbox{\scriptsize CCO}}$  supply. The TQ144 and the CS144 packages provide four independent V<sub>CCO</sub> supplies. The FG256 and the FG456 provide eight independent V<sub>CCO</sub> supplies.

Output buffers within a given  $V_{CCO}$  bank must share the same output drive source voltage. Input buffers for LVTTL, LVCMOS2, PCI33\_3, and PCI 66\_3 use the V<sub>CCO</sub> voltage for Input V<sub>CCO</sub> voltage.

## Transmission Line Effects

The delay of an electrical signal along a wire is dominated by the rise and fall times when the signal travels a short distance. Transmission line delays vary with inductance and capacitance, but a well-designed board can experience delays of approximately 180 ps per inch.

Transmission line effects, or reflections, typically start at 1.5" for fast (1.5 ns) rise and fall times. Poor (or non-existent) termination or changes in the transmission line impedance cause these reflections and can cause additional delay in longer traces. As system speeds continue to increase, the effect of I/O delays can become a limiting factor and therefore transmission line termination becomes increasingly more important.

## **Termination Techniques**

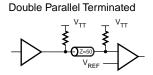

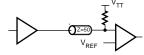

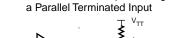

A variety of termination techniques reduce the impact of transmission line effects.

The following lists output termination techniques:

None Series Parallel (Shunt) Series and Parallel (Series-Shunt)

Input termination techniques include the following:

None Parallel (Shunt)

These termination techniques can be applied in any combination. A generic example of each combination of termination methods appears in Figure 41.

Unterminated Output Driving a Parallel Terminated Input

Series Terminated Output Driving

Series-Parallel Terminated Output

Series Terminated Output

Driving a Parallel Terminated Input VTT

DS001 41 032300

Figure 41: Overview of Standard Input and Output **Termination Methods**

## Simultaneous Switching Guidelines

Ground bounce can occur with high-speed digital ICs when multiple outputs change states simultaneously, causing undesired transient behavior on an output, or in the internal logic. This problem is also referred to as the Simultaneous Switching Output (SSO) problem.

Ground bounce is primarily due to current changes in the combined inductance of ground pins, bond wires, and

# XILINX<sup>®</sup>

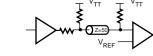

### GTL

A sample circuit illustrating a valid termination technique for GTL is shown in Figure 42. Table 20 lists DC voltage specifications for the GTL standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 42: Terminated GTL

#### Table 20: GTL Voltage Specifications

| Parameter                                       | Min  | Тур  | Max  |

|-------------------------------------------------|------|------|------|

| V <sub>CCO</sub>                                | -    | N/A  | -    |

| $V_{REF} = N \times V_{TT}^{(1)}$               | 0.74 | 0.8  | 0.86 |

| V <sub>TT</sub>                                 | 1.14 | 1.2  | 1.26 |

| $V_{IH} \ge V_{REF} + 0.05$                     | 0.79 | 0.85 | -    |

| $V_{IL} \leq V_{REF} - 0.05$                    | -    | 0.75 | 0.81 |

| V <sub>OH</sub>                                 | -    | -    | -    |

| V <sub>OL</sub>                                 | -    | 0.2  | 0.4  |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)         | -    | -    | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.4V | 32   | -    | -    |

| $I_{OL}$ at $V_{OL}$ (mA) at 0.2V               | -    | -    | 40   |

#### Notes:

1. N must be greater than or equal to 0.653 and less than or equal to 0.68.

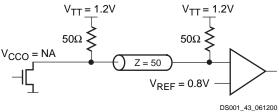

### GTL+

A sample circuit illustrating a valid termination technique for GTL+ appears in Figure 43. DC voltage specifications appear in Table 21 for the GTL+ standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 43: Terminated GTL+

#### Table 21: GTL+ Voltage Specifications

| Parameter                                       | Min  | Тур  | Max  |

|-------------------------------------------------|------|------|------|

| V <sub>CCO</sub>                                | -    | -    | -    |

| $V_{REF} = N \times V_{TT}^{(1)}$               | 0.88 | 1.0  | 1.12 |

| V <sub>TT</sub>                                 | 1.35 | 1.5  | 1.65 |

| $V_{IH} \ge V_{REF} + 0.1$                      | 0.98 | 1.1  | -    |

| $V_{IL} \le V_{REF} - 0.1$                      | -    | 0.9  | 1.02 |

| V <sub>OH</sub>                                 | -    | -    | -    |

| V <sub>OL</sub>                                 | 0.3  | 0.45 | 0.6  |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)         | -    | -    | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.6V | 36   | -    | -    |

| $I_{OL}$ at $V_{OL}$ (mA) at 0.3V               | -    | -    | 48   |

#### Notes:

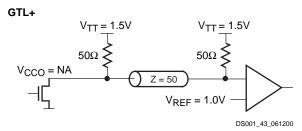

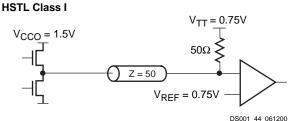

#### HSTL Class I

A sample circuit illustrating a valid termination technique for HSTL\_I appears in Figure 44. DC voltage specifications appear in Table 22 for the HSTL\_1 standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

DS001\_44\_061.

Figure 44: Terminated HSTL Class I

#### Table 22: HSTL Class I Voltage Specification

| Parameter                               | Min                    | Тур                 | Max             |

|-----------------------------------------|------------------------|---------------------|-----------------|

| V <sub>CCO</sub>                        | 1.40                   | 1.50                | 1.60            |

| V <sub>REF</sub>                        | 0.68                   | 0.75                | 0.90            |

| V <sub>TT</sub>                         | -                      | $V_{CCO} 	imes 0.5$ | -               |

| V <sub>IH</sub>                         | V <sub>REF</sub> + 0.1 | -                   | -               |

| V <sub>IL</sub>                         | -                      | -                   | $V_{REF} - 0.1$ |

| V <sub>OH</sub>                         | $V_{CCO} - 0.4$        | -                   | -               |

| V <sub>OL</sub>                         |                        |                     | 0.4             |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -8                     | -                   | -               |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 8                      | -                   | -               |

<sup>1.</sup> N must be greater than or equal to 0.653 and less than or equal to 0.68.

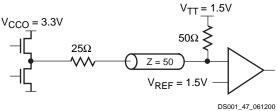

## SSTL3 Class I

A sample circuit illustrating a valid termination technique for SSTL3\_I appears in Figure 47. DC voltage specifications appear in Table 25 for the SSTL3\_I standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

#### SSTL3 Class I

Figure 47: Terminated SSTL3 Class I

| Table 2 | 25: | SSTL3_ | I Voltage | Specifications |

|---------|-----|--------|-----------|----------------|

|---------|-----|--------|-----------|----------------|

| Parameter                               | Min     | Тур | Max                |

|-----------------------------------------|---------|-----|--------------------|

| V <sub>CCO</sub>                        | 3.0     | 3.3 | 3.6                |

| $V_{REF} = 0.45 \times V_{CCO}$         | 1.3     | 1.5 | 1.7                |

| V <sub>TT</sub> = V <sub>REF</sub>      | 1.3     | 1.5 | 1.7                |

| $V_{IH} \ge V_{REF} + 0.2$              | 1.5     | 1.7 | 3.9 <sup>(1)</sup> |

| $V_{IL} \leq V_{REF} - 0.2$             | -0.3(2) | 1.3 | 1.5                |

| $V_{OH} \ge V_{REF} + 0.6$              | 1.9     | -   | -                  |

| $V_{OL} \leq V_{REF} - 0.6$             | -       | -   | 1.1                |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -8      | -   | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 8       | -   | -                  |

#### Notes:

1.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3.

2. V<sub>IL</sub> minimum does not conform to the formula.

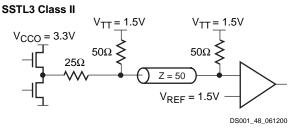

#### SSTL3 Class II

A sample circuit illustrating a valid termination technique for SSTL3\_II appears in Figure 48. DC voltage specifications appear in Table 26 for the SSTL3\_II standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 48: Terminated SSTL3 Class II

#### Table 26: SSTL3\_II Voltage Specifications

| Parameter                                | Min     | Тур | Max                |

|------------------------------------------|---------|-----|--------------------|

| V <sub>CCO</sub>                         | 3.0     | 3.3 | 3.6                |

| $V_{REF} = 0.45 \times V_{CCO}$          | 1.3     | 1.5 | 1.7                |

| V <sub>TT</sub> = V <sub>REF</sub>       | 1.3     | 1.5 | 1.7                |

| V <sub>IH</sub> ≥ V <sub>REF</sub> + 0.2 | 1.5     | 1.7 | 3.9 <sup>(1)</sup> |

| $V_{IL} \leq V_{REF} - 0.2$              | -0.3(2) | 1.3 | 1.5                |

| $V_{OH} \ge V_{REF} + 0.8$               | 2.1     | -   | -                  |

| $V_{OL} \leq V_{REF} - 0.8$              | -       | -   | 0.9                |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)  | -16     | -   | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA)  | 16      | -   | -                  |

Notes:

1.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3

2. V<sub>IL</sub> minimum does not conform to the formula

# **Revision History**

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09/18/00 | 2.0     | Sectioned the Spartan-II Family data sheet into four modules. Corrected banking description.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 03/05/01 | 2.1     | Clarified guidelines for applying power to $V_{\mbox{CCINT}}$ and $V_{\mbox{CCO}}$                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 09/03/03 | 2.2     | <ul> <li>The following changes were made:</li> <li>"Serial Modes," page 20 cautions about toggling WRITE during serial configuration.</li> <li>Maximum V<sub>IH</sub> values in Table 32 and Table 33 changed to 5.5V.</li> <li>In "Boundary Scan," page 13, removed sentence about lack of INTEST support.</li> <li>In Table 9, page 17, added note about the state of I/Os after power-on.</li> <li>In "Slave Parallel Mode," page 23, explained configuration bit alignment to SelectMap port.</li> </ul> |

| 06/13/08 | 2.8     | Added note that TDI, TMS, and TCK have a default pull-up resistor. Added note on maximum daisy chain limit. Updated Figure 15 and Figure 18 since Mode pins can be pulled up to either 2.5V or 3.3V. Updated DLL section. Recommended using property or attribute instead of primitive to define I/O properties. Updated description and links. Updated all modules for continuous page, figure, and table numbering. Synchronized all modules to v2.8.                                                      |

## Global Clock Setup and Hold for LVTTL Standard, with DLL (Pin-to-Pin)

|                                         |                                                                                                                                     |        | Speed Grade |         |       |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|---------|-------|

|                                         |                                                                                                                                     |        | -6          | -5      |       |

| Symbol                                  | Description                                                                                                                         | Device | Min         | Min     | Units |

| T <sub>PSDLL</sub> / T <sub>PHDLL</sub> | Input setup and hold time relative<br>to global clock input signal for<br>LVTTL standard, no delay, IFF, <sup>(1)</sup><br>with DLL | All    | 1.7 / 0     | 1.9 / 0 | ns    |

Notes:

1. IFF = Input Flip-Flop or Latch

2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

3. DLL output jitter is already included in the timing calculation.

4. A zero hold time listing indicates no hold time or a negative hold time.

For data input with different standards, adjust the setup time delay by the values shown in "IOB Input Delay Adjustments for Different Standards," page 57. For a global clock input with standards other than LVTTL, adjust delays with values from the "I/O Standard Global Clock Input Adjustments," page 61.

## Global Clock Setup and Hold for LVTTL Standard, without DLL (Pin-to-Pin)

|                                       |                                                                                                                                        |                                  | Speed   |         |         |    |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------|---------|---------|----|

|                                       |                                                                                                                                        |                                  | -6      | -5      |         |    |

| Symbol                                | Description                                                                                                                            | Device                           | Min     | Min     | Units   |    |

| T <sub>PSFD</sub> / T <sub>PHFD</sub> | Input setup and hold time relative<br>to global clock input signal for<br>LVTTL standard, no delay, IFF, <sup>(1)</sup><br>without DLL | XC2S15                           | 2.2 / 0 | 2.7 / 0 | ns      |    |

|                                       |                                                                                                                                        | to global clock input signal for | XC2S30  | 2.2 / 0 | 2.7 / 0 | ns |

|                                       |                                                                                                                                        | XC2S50                           | 2.2 / 0 | 2.7 / 0 | ns      |    |

|                                       |                                                                                                                                        | XC2S100                          | 2.3 / 0 | 2.8 / 0 | ns      |    |

|                                       |                                                                                                                                        | XC2S150                          | 2.4 / 0 | 2.9 / 0 | ns      |    |

|                                       |                                                                                                                                        | XC2S200                          | 2.4 / 0 | 3.0 / 0 | ns      |    |

Notes:

1. IFF = Input Flip-Flop or Latch

2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

- 3. A zero hold time listing indicates no hold time or a negative hold time.

- 4. For data input with different standards, adjust the setup time delay by the values shown in "IOB Input Delay Adjustments for Different Standards," page 57. For a global clock input with standards other than LVTTL, adjust delays with values from the "I/O Standard Global Clock Input Adjustments," page 61.

## IOB Input Switching Characteristics<sup>(1)</sup>

Input delays associated with the pad are specified for LVTTL levels. For other standards, adjust the delays with the values shown in "IOB Input Delay Adjustments for Different Standards," page 57.

|                                           |                                                  |          |            | Speed | d Grade    |      |       |

|-------------------------------------------|--------------------------------------------------|----------|------------|-------|------------|------|-------|

|                                           |                                                  |          | -6         |       | -5         |      |       |

| Symbol                                    | Description                                      | Device   | Min        | Max   | Min        | Max  | Units |

| Propagation Delays                        |                                                  | ·        |            |       |            |      |       |

| T <sub>IOPI</sub>                         | Pad to I output, no delay                        | All      | -          | 0.8   | -          | 1.0  | ns    |

| T <sub>IOPID</sub>                        | Pad to I output, with delay                      | All      | -          | 1.5   | -          | 1.8  | ns    |

| T <sub>IOPLI</sub>                        | Pad to output IQ via transparent latch, no delay | All      | -          | 1.7   | -          | 2.0  | ns    |

| T <sub>IOPLID</sub>                       | Pad to output IQ via transparent latch,          | XC2S15   | -          | 3.8   | -          | 4.5  | ns    |

|                                           | with delay                                       | XC2S30   | -          | 3.8   | -          | 4.5  | ns    |

|                                           |                                                  | XC2S50   | -          | 3.8   | -          | 4.5  | ns    |

|                                           |                                                  | XC2S100  | -          | 3.8   | -          | 4.5  | ns    |

|                                           |                                                  | XC2S150  | -          | 4.0   | -          | 4.7  | ns    |

|                                           |                                                  | XC2S200  | -          | 4.0   | -          | 4.7  | ns    |

| Sequential Delays                         | 1                                                | 1        |            |       | 1          |      |       |

| TIOCKIQ                                   | Clock CLK to output IQ                           | All      | -          | 0.7   | -          | 0.8  | ns    |

| Setup/Hold Times w                        | ith Respect to Clock CLK <sup>(2)</sup>          | <b>I</b> | 1          |       |            |      |       |

| T <sub>IOPICK</sub> / T <sub>IOICKP</sub> | Pad, no delay                                    | All      | 1.7 / 0    | -     | 1.9/0      | -    | ns    |

| TIOPICKD / TIOICKPD                       | Pad, with delay <sup>(1)</sup>                   | XC2S15   | 3.8 / 0    | -     | 4.4 / 0    | -    | ns    |

|                                           |                                                  | XC2S30   | 3.8 / 0    | -     | 4.4 / 0    | -    | ns    |

|                                           |                                                  | XC2S50   | 3.8 / 0    | -     | 4.4 / 0    | -    | ns    |

|                                           |                                                  | XC2S100  | 3.8 / 0    | -     | 4.4 / 0    | -    | ns    |

|                                           |                                                  | XC2S150  | 3.9 / 0    | -     | 4.6 / 0    | -    | ns    |

|                                           |                                                  | XC2S200  | 3.9 / 0    | -     | 4.6 / 0    | -    | ns    |

| TIOICECK / TIOCKICE                       | ICE input                                        | All      | 0.9 / 0.01 | -     | 0.9 / 0.01 | -    | ns    |

| Set/Reset Delays                          |                                                  |          |            |       | 1          | 1    |       |

| T <sub>IOSRCKI</sub>                      | SR input (IFF, synchronous)                      | All      | -          | 1.1   | -          | 1.2  | ns    |

| T <sub>IOSRIQ</sub>                       | SR input to IQ (asynchronous)                    | All      | -          | 1.5   | -          | 1.7  | ns    |

| T <sub>GSRQ</sub>                         | GSR to output IQ                                 | All      | -          | 9.9   | -          | 11.7 | ns    |

Notes:

1. Input timing for LVTTL is measured at 1.4V. For other I/O standards, see the table "Delay Measurement Methodology," page 60.

2. A zero hold time listing indicates no hold time or a negative hold time.

# Calculation of T<sub>IOOP</sub> as a Function of Capacitance

$T_{\rm IOOP}$  is the propagation delay from the O Input of the IOB to the pad. The values for  $T_{\rm IOOP}$  are based on the standard capacitive load (C<sub>SL</sub>) for each I/O standard as listed in the table "Constants for Calculating TIOOP", below.

For other capacitive loads, use the formulas below to calculate an adjusted propagation delay,  $T_{IOOP1}$ .

$$T_{IOOP1} = T_{IOOP} + Adj + (C_{LOAD} - C_{SL}) * F_{L}$$

Where:

Adj is selected from "IOB Output Delay Adjustments for Different Standards", page 59, according to the I/O standard used

$C_{\text{LOAD}}\,$  is the capacitive load for the design

F<sub>L</sub> is the capacitance scaling factor

#### **Delay Measurement Methodology**

| Standard       | V <sub>L</sub> (1)                            | V <sub>H</sub> (1)                            | Meas.<br>Point   | V <sub>REF</sub><br>Typ <sup>(2)</sup> |

|----------------|-----------------------------------------------|-----------------------------------------------|------------------|----------------------------------------|

| LVTTL          | 0                                             | 3                                             | 1.4              | -                                      |

| LVCMOS2        | 0                                             | 2.5                                           | 1.125            | -                                      |

| PCI33_5        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| PCI33_3        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| PCI66_3        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| GTL            | V <sub>REF</sub> - 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 0.80                                   |

| GTL+           | V <sub>REF</sub> - 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 1.0                                    |

| HSTL Class I   | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.75                                   |

| HSTL Class III | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.90                                   |

| HSTL Class IV  | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.90                                   |

| SSTL3 I and II | V <sub>REF</sub> – 1.0                        | V <sub>REF</sub> + 1.0                        | $V_{REF}$        | 1.5                                    |

| SSTL2 I and II | V <sub>REF</sub> -0.75                        | V <sub>REF</sub> + 0.75                       | $V_{REF}$        | 1.25                                   |

| СТТ            | V <sub>REF</sub> – 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 1.5                                    |

| AGP            | V <sub>REF</sub> –<br>(0.2xV <sub>CCO</sub> ) | V <sub>REF</sub> +<br>(0.2xV <sub>CCO</sub> ) | V <sub>REF</sub> | Per AGP<br>Spec                        |

#### Notes:

- 1. Input waveform switches between V<sub>L</sub> and V<sub>H</sub>.

- 2. Measurements are made at V<sub>REF</sub> Typ, Maximum, and Minimum. Worst-case values are reported.

- I/O parameter measurements are made with the capacitance values shown in the table, "Constants for Calculating TIOOP". See Xilinx application note <u>XAPP179</u> for the appropriate terminations.

- 4. I/O standard measurements are reflected in the IBIS model information except where the IBIS format precludes it.

## Constants for Calculating T<sub>IOOP</sub>

| Standard                          | C <sub>SL</sub> <sup>(1)</sup><br>(pF) | F <sub>L</sub><br>(ns/pF) |

|-----------------------------------|----------------------------------------|---------------------------|

| LVTTL Fast Slew Rate, 2 mA drive  | 35                                     | 0.41                      |

| LVTTL Fast Slew Rate, 4 mA drive  | 35                                     | 0.20                      |

| LVTTL Fast Slew Rate, 6 mA drive  | 35                                     | 0.13                      |

| LVTTL Fast Slew Rate, 8 mA drive  | 35                                     | 0.079                     |

| LVTTL Fast Slew Rate, 12 mA drive | 35                                     | 0.044                     |

| LVTTL Fast Slew Rate, 16 mA drive | 35                                     | 0.043                     |

| LVTTL Fast Slew Rate, 24 mA drive | 35                                     | 0.033                     |

| LVTTL Slow Slew Rate, 2 mA drive  | 35                                     | 0.41                      |

| LVTTL Slow Slew Rate, 4 mA drive  | 35                                     | 0.20                      |

| LVTTL Slow Slew Rate, 6 mA drive  | 35                                     | 0.100                     |

| LVTTL Slow Slew Rate, 8 mA drive  | 35                                     | 0.086                     |

| LVTTL Slow Slew Rate, 12 mA drive | 35                                     | 0.058                     |

| LVTTL Slow Slew Rate, 16 mA drive | 35                                     | 0.050                     |

| LVTTL Slow Slew Rate, 24 mA drive | 35                                     | 0.048                     |

| LVCMOS2                           | 35                                     | 0.041                     |

| PCI 33 MHz 5V                     | 50                                     | 0.050                     |

| PCI 33 MHZ 3.3V                   | 10                                     | 0.050                     |

| PCI 66 MHz 3.3V                   | 10                                     | 0.033                     |

| GTL                               | 0                                      | 0.014                     |

| GTL+                              | 0                                      | 0.017                     |

| HSTL Class I                      | 20                                     | 0.022                     |

| HSTL Class III                    | 20                                     | 0.016                     |

| HSTL Class IV                     | 20                                     | 0.014                     |

| SSTL2 Class I                     | 30                                     | 0.028                     |

| SSTL2 Class II                    | 30                                     | 0.016                     |

| SSTL3 Class I                     | 30                                     | 0.029                     |

| SSTL3 Class II                    | 30                                     | 0.016                     |

| СТТ                               | 20                                     | 0.035                     |

| AGP                               | 10                                     | 0.037                     |

#### Notes:

- 1. I/O parameter measurements are made with the capacitance values shown above. See Xilinx application note <u>XAPP179</u> for the appropriate terminations.

- 2. I/O standard measurements are reflected in the IBIS model information except where the IBIS format precludes it.

## **DLL Timing Parameters**

All devices are 100 percent functionally tested. Because of the difficulty in directly measuring many internal timing parameters, those parameters are derived from benchmark timing patterns. The following guidelines reflect worst-case values across the recommended operating conditions.

|                      |                                    |     | Speed Grade |     |     |       |

|----------------------|------------------------------------|-----|-------------|-----|-----|-------|

|                      |                                    |     | -6 -5       |     | ·5  |       |

| Symbol               | Description                        | Min | Max         | Min | Max | Units |

| F <sub>CLKINHF</sub> | Input clock frequency (CLKDLLHF)   | 60  | 200         | 60  | 180 | MHz   |

| F <sub>CLKINLF</sub> | Input clock frequency (CLKDLL)     | 25  | 100         | 25  | 90  | MHz   |

| T <sub>DLLPWHF</sub> | Input clock pulse width (CLKDLLHF) | 2.0 | -           | 2.4 | -   | ns    |

| T <sub>DLLPWLF</sub> | Input clock pulse width (CLKDLL)   | 2.5 | -           | 3.0 | -   | ns    |

### **DLL Clock Tolerance, Jitter, and Phase Information**

All DLL output jitter and phase specifications were determined through statistical measurement at the package pins using a clock mirror configuration and matched drivers.

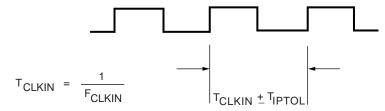

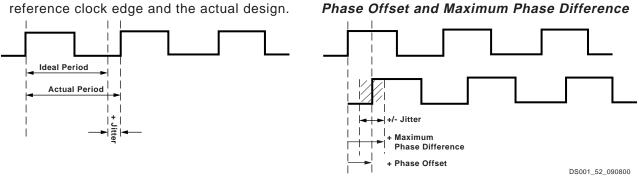

Figure 52, page 63, provides definitions for various parameters in the table below.

|                     |                                                                |                               |     | CLKDLLHF |     | DLL  |       |

|---------------------|----------------------------------------------------------------|-------------------------------|-----|----------|-----|------|-------|

| Symbol              | Description                                                    | F <sub>CLKIN</sub>            | Min | Max      | Min | Max  | Units |

| T <sub>IPTOL</sub>  | Input clock period tolerance                                   |                               | -   | 1.0      | -   | 1.0  | ns    |

| T <sub>IJITCC</sub> | Input clock jitter tolerance (cycle-to-cycle)                  |                               | -   | ±150     | -   | ±300 | ps    |

| T <sub>LOCK</sub>   | Time required for DLL to acquire lock                          | > 60 MHz                      | -   | 20       | -   | 20   | μs    |

|                     |                                                                | 50-60 MHz                     | -   | -        | -   | 25   | μs    |

|                     |                                                                | 40-50 MHz                     | -   | -        | -   | 50   | μs    |

|                     |                                                                | 30-40 MHz                     | -   | -        | -   | 90   | μs    |

|                     |                                                                | 25-30 MHz                     | -   | -        | -   | 120  | μs    |

| T <sub>OJITCC</sub> | Output jitter (cycle-to-cycle) for any DLL clock c             | output <sup>(1)</sup>         | -   | ±60      | -   | ±60  | ps    |

| T <sub>PHIO</sub>   | Phase offset between CLKIN and CLKO <sup>(2)</sup>             |                               | -   | ±100     | -   | ±100 | ps    |

| T <sub>PHOO</sub>   | Phase offset between clock outputs on the DLL <sup>(3)</sup>   |                               | -   | ±140     | -   | ±140 | ps    |

| T <sub>PHIOM</sub>  | Maximum phase difference between CLKIN and CLKO <sup>(4)</sup> |                               | -   | ±160     | -   | ±160 | ps    |

| T <sub>PHOOM</sub>  | Maximum phase difference between clock outp                    | uts on the DLL <sup>(5)</sup> | -   | ±200     | -   | ±200 | ps    |

Notes:

1. **Output Jitter** is cycle-to-cycle jitter measured on the DLL output clock, *excluding* input clock jitter.

2. Phase Offset between CLKIN and CLKO is the worst-case fixed time difference between rising edges of CLKIN and CLKO, *excluding* output jitter and input clock jitter.

3. Phase Offset between Clock Outputs on the DLL is the worst-case fixed time difference between rising edges of any two DLL outputs, *excluding* Output Jitter and input clock jitter.

4. Maximum Phase Difference between CLKIN an CLKO is the sum of Output Jitter and Phase Offset between CLKIN and CLKO, or the greatest difference between CLKIN and CLKO rising edges due to DLL alone (*excluding* input clock jitter).

5. **Maximum Phase Difference between Clock Outputs on the DLL** is the sum of Output JItter and Phase Offset between any DLL clock outputs, or the greatest difference between any two DLL output rising edges due to DLL alone (*excluding* input clock jitter).

**Period Tolerance:** the allowed input clock period change in nanoseconds.

**Output Jitter:** the difference between an ideal reference clock edge and the actual design.

Figure 52: Period Tolerance and Clock Jitter

| Package        | Leads | Туре                               | Maximum<br>I/O | Lead Pitch<br>(mm) | Footprint<br>Area (mm) | Height<br>(mm) | Mass <sup>(1)</sup><br>(g) |

|----------------|-------|------------------------------------|----------------|--------------------|------------------------|----------------|----------------------------|

| VQ100 / VQG100 | 100   | Very Thin Quad Flat Pack (VQFP)    | 60             | 0.5                | 16 x 16                | 1.20           | 0.6                        |

| TQ144 / TQG144 | 144   | Thin Quad Flat Pack (TQFP)         | 92             | 0.5                | 22 x 22                | 1.60           | 1.4                        |

| CS144 / CSG144 | 144   | Chip Scale Ball Grid Array (CSBGA) | 92             | 0.8                | 12 x 12                | 1.20           | 0.3                        |

| PQ208 / PQG208 | 208   | Plastic Quad Flat Pack (PQFP)      | 140            | 0.5                | 30.6 x 30.6            | 3.70           | 5.3                        |

| FG256 / FGG256 | 256   | Fine-pitch Ball Grid Array (FBGA)  | 176            | 1.0                | 17 x 17                | 2.00           | 0.9                        |

| FG456 / FGG456 | 456   | Fine-pitch Ball Grid Array (FBGA)  | 284            | 1.0                | 23 x 23                | 2.60           | 2.2                        |

#### Table 36: Spartan-II Family Package Options

#### Notes:

1. Package mass is  $\pm 10\%$ .

Note: Some early versions of Spartan-II devices, including the XC2S15 and XC2S30 ES devices and the XC2S150 with date code 0045 or earlier, included a power-down pin. For more information, see <u>Answer Record 10500</u>.

# VCCO Banks

Some of the I/O standards require specific V<sub>CCO</sub> voltages. These voltages are externally connected to device pins that serve groups of IOBs, called banks. Eight I/O banks result from separating each edge of the FPGA into two banks (see Figure 3 in Module 2). Each bank has multiple V<sub>CCO</sub> pins which must be connected to the same voltage. In the smaller packages, the V<sub>CCO</sub> pins are connected between banks, effectively reducing the number of independent banks available (see Table 37). These interconnected banks are shown in the Pinout Tables with V<sub>CCO</sub> pads for multiple banks connected to the same pin.

#### Table 37: Independent VCCO Banks Available

| Package           | VQ100 | CS144 | FG256 |  |

|-------------------|-------|-------|-------|--|

|                   | PQ208 | TQ144 | FG456 |  |

| Independent Banks | 1     | 4     | 8     |  |

## Package Overview

Table 36 shows the six low-cost, space-saving productionpackage styles for the Spartan-II family.

Each package style is available in an environmentally friendly lead-free (Pb-free) option. The Pb-free packages include an extra 'G' in the package style name. For example, the standard "CS144" package becomes "CSG144" when ordered as the Pb-free option. Leaded (non-Pb-free) packages may be available for selected devices, with the same pin-out and without the "G" in the ordering code; contact Xilinx sales for more information. The mechanical dimensions of the standard and Pb-free packages are similar, as shown in the mechanical drawings provided in Table 38. For additional package information, see <u>UG112</u>: *Device Package User Guide*.

## **Mechanical Drawings**

Detailed mechanical drawings for each package type are available from the Xilinx web site at the specified location in Table 38.

Material Declaration Data Sheets (MDDS) are also available on the <u>Xilinx web site</u> for each package.

#### Table 38: Xilinx Package Documentation

| Package | Drawing         | MDDS         |

|---------|-----------------|--------------|

| VQ100   | Package Drawing | PK173_VQ100  |

| VQG100  |                 | PK130_VQG100 |

| TQ144   | Package Drawing | PK169_TQ144  |

| TQG144  |                 | PK126_TQG144 |

| CS144   | Package Drawing | PK149_CS144  |

| CSG144  | _               | PK103_CSG144 |

| PQ208   | Package Drawing | PK166_PQ208  |

| PQG208  | _               | PK123_PQG208 |

| FG256   | Package Drawing | PK151_FG256  |

| FGG256  |                 | PK105_FGG256 |

| FG456   | Package Drawing | PK154_FG456  |

| FGG456  |                 | PK109_FGG456 |

## XC2S200 Device Pinouts (Continued)

| XC2S200 Pad           | l Name |       |                             |                             | Bndry |

|-----------------------|--------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank   | PQ208 | FG256                       | FG456                       | Scan  |

| V <sub>CCO</sub>      | 1      | P156  | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| TDO                   | 2      | P157  | B14                         | A21                         | -     |

| GND                   | -      | P158  | GND*                        | GND*                        | -     |

| TDI                   | -      | P159  | A15                         | B20                         | -     |

| I/O ( <u>CS</u> )     | 1      | P160  | B13                         | C19                         | 0     |

| I/O (WRITE)           | 1      | P161  | C13                         | A20                         | 3     |

| I/O                   | 1      | -     | -                           | B19                         | 9     |

| I/O                   | 1      | -     | -                           | C18                         | 12    |

| I/O                   | 1      | -     | C12                         | D17                         | 15    |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O, V <sub>REF</sub> | 1      | P162  | A14                         | A19                         | 18    |

| I/O                   | 1      | -     | -                           | B18                         | 21    |

| I/O                   | 1      | -     | -                           | E16                         | 27    |

| I/O                   | 1      | -     | D12                         | C17                         | 30    |

| I/O                   | 1      | P163  | B12                         | D16                         | 33    |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 1      | -     | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| I/O, V <sub>REF</sub> | 1      | P164  | C11                         | A18                         | 36    |

| I/O                   | 1      | P165  | A13                         | B17                         | 39    |

| I/O                   | 1      | -     | -                           | E15                         | 42    |

| I/O                   | 1      | -     | -                           | A17                         | 45    |

| I/O                   | 1      | -     | D11                         | D15                         | 48    |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O                   | 1      | P166  | A12                         | C16                         | 51    |

| I/O                   | 1      | -     | -                           | D14                         | 54    |

| I/O, V <sub>REF</sub> | 1      | P167  | E11                         | E14                         | 60    |

| I/O                   | 1      | P168  | B11                         | A16                         | 63    |

| GND                   | -      | P169  | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 1      | P170  | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| V <sub>CCINT</sub>    | -      | P171  | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| I/O                   | 1      | P172  | A11                         | C15                         | 66    |

| I/O                   | 1      | P173  | C10                         | B15                         | 69    |

| I/O                   | 1      | -     | -                           | E13                         | 72    |

| I/O                   | 1      | -     | -                           | A15                         | 75    |

| I/O                   | 1      | -     | -                           | F12                         | 78    |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O                   | 1      | P174  | B10                         | C14                         | 81    |

| I/O                   | 1      | -     | -                           | B14                         | 84    |

| I/O                   | 1      | -     | -                           | A14                         | 87    |

## XC2S200 Device Pinouts (Continued)

| XC2S200 Pad Name      |      |       |                             |                             | Bndry |

|-----------------------|------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank | PQ208 | FG256                       | FG456                       | Scan  |

| I/O                   | 1    | P175  | D10                         | D13                         | 90    |

| I/O                   | 1    | P176  | A10                         | C13                         | 93    |

| GND                   | -    | P177  | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 1    | -     | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| I/O, V <sub>REF</sub> | 1    | P178  | B9                          | B13                         | 96    |

| I/O                   | 1    | P179  | E10                         | E12                         | 99    |

| I/O                   | 1    | -     | -                           | A13                         | 105   |

| I/O                   | 1    | -     | A9                          | B12                         | 108   |

| I/O                   | 1    | P180  | D9                          | D12                         | 111   |

| I/O                   | 1    | -     | -                           | C12                         | 114   |

| I/O                   | 1    | P181  | A8                          | D11                         | 120   |

| I, GCK2               | 1    | P182  | C9                          | A11                         | 126   |

| GND                   | -    | P183  | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 1    | P184  | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| V <sub>CCO</sub>      | 0    | P184  | V <sub>CCO</sub><br>Bank 0* | V <sub>CCO</sub><br>Bank 0* | -     |

| I, GCK3               | 0    | P185  | B8                          | C11                         | 127   |

| V <sub>CCINT</sub>    | -    | P186  | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| I/O                   | 0    | -     | -                           | E11                         | 137   |

| I/O                   | 0    | P187  | A7                          | A10                         | 140   |

| I/O                   | 0    | -     | D8                          | B10                         | 143   |

| I/O                   | 0    | -     | -                           | F11                         | 146   |

| I/O                   | 0    | P188  | A6                          | C10                         | 152   |

| I/O, V <sub>REF</sub> | 0    | P189  | B7                          | A9                          | 155   |

| V <sub>CCO</sub>      | 0    | -     | V <sub>CCO</sub><br>Bank 0* | V <sub>CCO</sub><br>Bank 0* | -     |

| GND                   | -    | P190  | GND*                        | GND*                        | -     |

| I/O                   | 0    | P191  | C8                          | B9                          | 158   |

| I/O                   | 0    | P192  | D7                          | E10                         | 161   |

| I/O                   | 0    | -     | -                           | C9                          | 164   |

| I/O                   | 0    | -     | -                           | D10                         | 167   |

| I/O                   | 0    | P193  | E7                          | A8                          | 170   |

| GND                   | -    | -     | GND*                        | GND*                        | -     |

| I/O                   | 0    | -     | -                           | D9                          | 173   |

| I/O                   | 0    | -     | -                           | B8                          | 176   |

| I/O                   | 0    | -     | -                           | C8                          | 179   |

| I/O                   | 0    | P194  | C7                          | E9                          | 182   |

| I/O                   | 0    | P195  | B6                          | A7                          | 185   |

| V <sub>CCINT</sub>    | -    | P196  | V <sub>CCINT</sub> *        | $V_{CCINT}^{*}$             | -     |

| V <sub>CCO</sub>      | 0    | P197  | V <sub>CCO</sub><br>Bank 0* | V <sub>CCO</sub><br>Bank 0* | -     |

### Additional XC2S200 Package Pins (Continued)

#### 11/02/00

| FG456                        |                              |                     |                   |     |     |  |  |

|------------------------------|------------------------------|---------------------|-------------------|-----|-----|--|--|

|                              |                              | V <sub>CCIN</sub>   | <sub>T</sub> Pins |     |     |  |  |

| E5                           | E18                          | F6                  | F17               | G7  | G8  |  |  |

| G9                           | G14                          | G15                 | G16               | H7  | H16 |  |  |

| J7                           | J16                          | P7                  | P16               | R7  | R16 |  |  |

| T7                           | Т8                           | Т9                  | T14               | T15 | T16 |  |  |

| U6                           | U17                          | V5                  | V18               | -   | -   |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 0 Pins         |     |     |  |  |

| F7                           | F8                           | F9                  | F10               | G10 | G11 |  |  |

| V <sub>CCO</sub> Bank 1 Pins |                              |                     |                   |     |     |  |  |

| F13                          | F14                          | F15                 | F16               | G12 | G13 |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 2 Pins         |     |     |  |  |

| G17                          | H17                          | J17                 | K16               | K17 | L16 |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 3 Pins         |     |     |  |  |

| M16                          | N16                          | N17                 | P17               | R17 | T17 |  |  |

|                              | V <sub>CCO</sub> Bank 4 Pins |                     |                   |     |     |  |  |

| T12                          | T13                          | U13                 | U14               | U15 | U16 |  |  |

|                              | V <sub>CCO</sub> Bank 5 Pins |                     |                   |     |     |  |  |

| T10                          | T11                          | U7                  | U8                | U9  | U10 |  |  |

|                              | V <sub>CCO</sub> Bank 6 Pins |                     |                   |     |     |  |  |

| M7                           | N6                           | N7                  | P6                | R6  | T6  |  |  |

| V <sub>CCO</sub> Bank 7 Pins |                              |                     |                   |     |     |  |  |

## Additional XC2S200 Package Pins (Continued)

|                    |     |      |      | •   |      |  |  |

|--------------------|-----|------|------|-----|------|--|--|

| G6                 | H6  | J6   | K6   | K7  | L7   |  |  |

| GND Pins           |     |      |      |     |      |  |  |

| A1                 | A22 | B2   | B21  | C3  | C20  |  |  |

| J9                 | J10 | J11  | J12  | J13 | J14  |  |  |

| K9                 | K10 | K11  | K12  | K13 | K14  |  |  |