# E·XFL

#### AMD Xilinx - XC2S150-5PQ208C Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 864                                                         |

| Number of Logic Elements/Cells | 3888                                                        |

| Total RAM Bits                 | 49152                                                       |

| Number of I/O                  | 140                                                         |

| Number of Gates                | 150000                                                      |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 208-BFQFP                                                   |

| Supplier Device Package        | 208-PQFP (28x28)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s150-5pq208c |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#

DS001-1 (v2.8) June 13, 2008

# Spartan-II FPGA Family: Introduction and Ordering Information

#### **Product Specification**

# Introduction

The Spartan<sup>®</sup>-II Field-Programmable Gate Array family gives users high performance, abundant logic resources, and a rich feature set, all at an exceptionally low price. The six-member family offers densities ranging from 15,000 to 200,000 system gates, as shown in Table 1. System performance is supported up to 200 MHz. Features include block RAM (to 56K bits), distributed RAM (to 75,264 bits), 16 selectable I/O standards, and four DLLs. Fast, predictable interconnect means that successive design iterations continue to meet timing requirements.

The Spartan-II family is a superior alternative to mask-programmed ASICs. The FPGA avoids the initial cost, lengthy development cycles, and inherent risk of conventional ASICs. Also, FPGA programmability permits design upgrades in the field with no hardware replacement necessary (impossible with ASICs).

# **Features**

- Second generation ASIC replacement technology

- Densities as high as 5,292 logic cells with up to 200,000 system gates

- Streamlined features based on Virtex<sup>®</sup> FPGA architecture

- Unlimited reprogrammability

- Very low cost

- Cost-effective 0.18 micron process

- System level features

- SelectRAM<sup>™</sup> hierarchical memory:

- · 16 bits/LUT distributed RAM

- Configurable 4K bit block RAM

- Fast interfaces to external RAM

- Fully PCI compliant

- Low-power segmented routing architecture

- Full readback ability for verification/observability

- Dedicated carry logic for high-speed arithmetic

- Efficient multiplier support

- Cascade chain for wide-input functions

- Abundant registers/latches with enable, set, reset

- Four dedicated DLLs for advanced clock control

- Four primary low-skew global clock distribution nets

- IEEE 1149.1 compatible boundary scan logic

- Versatile I/O and packaging

- Pb-free package options

- Low-cost packages available in all densities

- Family footprint compatibility in common packages

- 16 high-performance interface standards

- Hot swap Compact PCI friendly

- Zero hold time simplifies system timing

- Core logic powered at 2.5V and I/Os powered at 1.5V, 2.5V, or 3.3V

- Fully supported by powerful Xilinx<sup>®</sup> ISE<sup>®</sup> development system

- Fully automatic mapping, placement, and routing

| Table 1: Spartan-II FPGA Family Members |                |                                 |                         |               |                                                 |                                  |                            |

|-----------------------------------------|----------------|---------------------------------|-------------------------|---------------|-------------------------------------------------|----------------------------------|----------------------------|

| Device                                  | Logic<br>Cells | System Gates<br>(Logic and RAM) | CLB<br>Array<br>(R x C) | Total<br>CLBs | Maximum<br>Available<br>User I/O <sup>(1)</sup> | Total<br>Distributed RAM<br>Bits | Total<br>Block RAM<br>Bits |

| XC2S15                                  | 432            | 15,000                          | 8 x 12                  | 96            | 86                                              | 6,144                            | 16K                        |

| XC2S30                                  | 972            | 30,000                          | 12 x 18                 | 216           | 92                                              | 13,824                           | 24K                        |

| XC2S50                                  | 1,728          | 50,000                          | 16 x 24                 | 384           | 176                                             | 24,576                           | 32K                        |

| XC2S100                                 | 2,700          | 100,000                         | 20 x 30                 | 600           | 176                                             | 38,400                           | 40K                        |

| XC2S150                                 | 3,888          | 150,000                         | 24 x 36                 | 864           | 260                                             | 55,296                           | 48K                        |

| XC2S200                                 | 5,292          | 200,000                         | 28 x 42                 | 1,176         | 284                                             | 75,264                           | 56K                        |

#### Notes:

1. All user I/O counts do not include the four global clock/user input pins. See details in Table 2, page 4.

© 2000-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

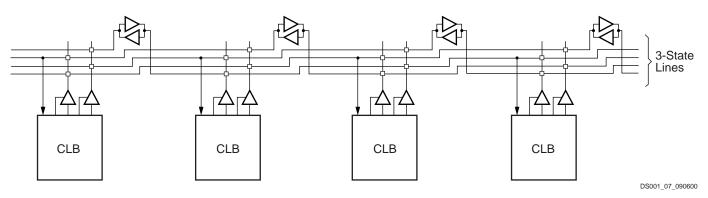

Figure 7: BUFT Connections to Dedicated Horizontal Bus Lines

# **Clock Distribution**

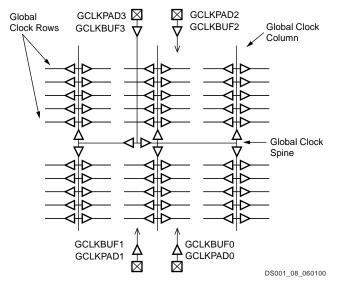

The Spartan-II family provides high-speed, low-skew clock distribution through the primary global routing resources described above. A typical clock distribution net is shown in Figure 8.

Four global buffers are provided, two at the top center of the device and two at the bottom center. These drive the four primary global nets that in turn drive any clock pin.

Four dedicated clock pads are provided, one adjacent to each of the global buffers. The input to the global buffer is selected either from these pads or from signals in the general purpose routing. Global clock pins do not have the option for internal, weak pull-up resistors.

Figure 8: Global Clock Distribution Network

# Delay-Locked Loop (DLL)

Associated with each global clock input buffer is a fully digital Delay-Locked Loop (DLL) that can eliminate skew between the clock input pad and internal clock-input pins throughout the device. Each DLL can drive two global clock networks. The DLL monitors the input clock and the distributed clock, and automatically adjusts a clock delay element. Additional delay is introduced such that clock edges reach internal flip-flops exactly one clock period after they arrive at the input. This closed-loop system effectively eliminates clock-distribution delay by ensuring that clock edges arrive at internal flip-flops in synchronism with clock edges arriving at the input.

In addition to eliminating clock-distribution delay, the DLL provides advanced control of multiple clock domains. The DLL provides four quadrature phases of the source clock, can double the clock, or divide the clock by 1.5, 2, 2.5, 3, 4, 5, 8, or 16. It has six outputs.

The DLL also operates as a clock mirror. By driving the output from a DLL off-chip and then back on again, the DLL can be used to deskew a board level clock among multiple Spartan-II devices.

In order to guarantee that the system clock is operating correctly prior to the FPGA starting up after configuration, the DLL can delay the completion of the configuration process until after it has achieved lock.

# **Boundary Scan**

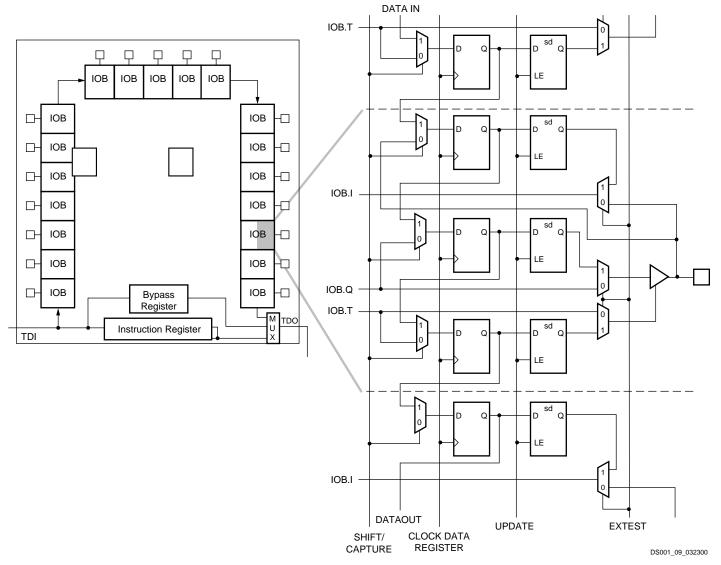

Spartan-II devices support all the mandatory boundaryscan instructions specified in the IEEE standard 1149.1. A Test Access Port (TAP) and registers are provided that implement the EXTEST, SAMPLE/PRELOAD, and BYPASS instructions. The TAP also supports two USERCODE instructions and internal scan chains.

The TAP uses dedicated package pins that always operate using LVTTL. For TDO to operate using LVTTL, the V<sub>CCO</sub> for Bank 2 must be 3.3V. Otherwise, TDO switches rail-to-rail between ground and V<sub>CCO</sub>. TDI, TMS, and TCK have a default internal weak pull-up resistor, and TDO has no default resistor. Bitstream options allow setting any of the four TAP pins to have an internal pull-up, pull-down, or neither.

# **∑**XILINX<sup>®</sup>

Figure 9 is a diagram of the Spartan-II family boundary scan logic. It includes three bits of Data Register per IOB, the IEEE 1149.1 Test Access Port controller, and the Instruction Register with decodes.

## **Bit Sequence**

The bit sequence within each IOB is: In, Out, 3-State. The input-only pins contribute only the In bit to the boundary scan I/O data register, while the output-only pins contributes all three bits.

From a cavity-up view of the chip (as shown in the FPGA Editor), starting in the upper right chip corner, the boundary scan data-register bits are ordered as shown in Figure 10.

BSDL (Boundary Scan Description Language) files for Spartan-II family devices are available on the Xilinx website, in the <u>Downloads</u> area.

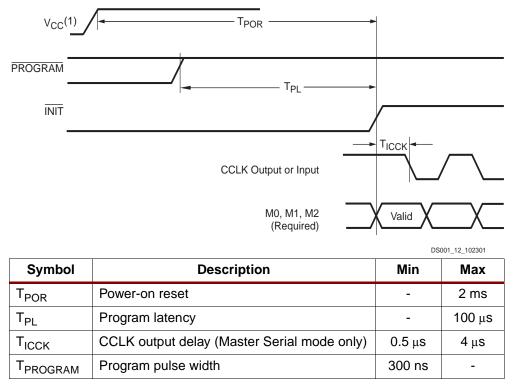

#### Notes: (referring to waveform above:)

1. Before configuration can begin,  $V_{CCINT}$  must be greater than 1.6V and  $V_{CCO}$  Bank 2 must be greater than 1.0V.

Figure 12: Configuration Timing on Power-Up

## **Clearing Configuration Memory**

The device indicates that clearing the configuration memory is in progress by driving INIT Low. At this time, the user can delay configuration by holding either PROGRAM or INIT Low, which causes the device to remain in the memory clearing phase. Note that the bidirectional INIT line is driving a Low logic level during memory clearing. To avoid contention, use an open-drain driver to keep INIT Low.

With no delay in force, the device indicates that the memory is completely clear by driving INIT High. The FPGA samples its mode pins on this Low-to-High transition.

# Loading Configuration Data

Once INIT is High, the user can begin loading configuration data frames into the device. The details of loading the configuration data are discussed in the sections treating the configuration modes individually. The sequence of operations necessary to load configuration data using the serial modes is shown in Figure 14. Loading data using the Slave Parallel mode is shown in Figure 19, page 25.

## **CRC Error Checking**

During the loading of configuration data, a CRC value embedded in the configuration file is checked against a CRC value calculated within the FPGA. If the CRC values do not match, the FPGA drives INIT Low to indicate that a frame error has occurred and configuration is aborted.

To reconfigure the device, the PROGRAM pin should be asserted to reset the configuration logic. Recycling power also resets the FPGA for configuration. See "Clearing Configuration Memory".

#### Start-up

The start-up sequence oversees the transition of the FPGA from the configuration state to full user operation. A match of CRC values, indicating a successful loading of the configuration data, initiates the sequence.

During start-up, the device performs four operations:

- 1. The assertion of DONE. The failure of DONE to go High may indicate the unsuccessful loading of configuration data.

- 2. The release of the Global Three State net. This activates I/Os to which signals are assigned. The remaining I/Os stay in a high-impedance state with internal weak pull-down resistors present.

- 3. Negates Global Set Reset (GSR). This allows all flip-flops to change state.

- 4. The assertion of Global Write Enable (GWE). This allows all RAMs and flip-flops to change state.

# **Design Considerations**

This section contains more detailed design information on the following features:

- Delay-Locked Loop . . . see page 27

- Block RAM . . . see page 32

- Versatile I/O . . . see page 36

# Using Delay-Locked Loops

The Spartan-II FPGA family provides up to four fully digital dedicated on-chip Delay-Locked Loop (DLL) circuits which provide zero propagation delay, low clock skew between output clock signals distributed throughout the device, and advanced clock domain control. These dedicated DLLs can be used to implement several circuits that improve and simplify system level design.

# Introduction

Quality on-chip clock distribution is important. Clock skew and clock delay impact device performance and the task of managing clock skew and clock delay with conventional clock trees becomes more difficult in large devices. The Spartan-II family of devices resolve this potential problem by providing up to four fully digital dedicated on-chip Delay-Locked Loop (DLL) circuits which provide zero propagation delay and low clock skew between output clock signals distributed throughout the device.

Each DLL can drive up to two global clock routing networks within the device. The global clock distribution network minimizes clock skews due to loading differences. By monitoring a sample of the DLL output clock, the DLL can compensate for the delay on the routing network, effectively eliminating the delay from the external input port to the individual clock loads within the device.

In addition to providing zero delay with respect to a user source clock, the DLL can provide multiple phases of the source clock. The DLL can also act as a clock doubler or it can divide the user source clock by up to 16.

Clock multiplication gives the designer a number of design alternatives. For instance, a 50 MHz source clock doubled by the DLL can drive an FPGA design operating at 100 MHz. This technique can simplify board design because the clock path on the board no longer distributes such a high-speed signal. A multiplied clock also provides designers the option of time-domain-multiplexing, using one circuit twice per clock cycle, consuming less area than two copies of the same circuit.

The DLL can also act as a clock mirror. By driving the DLL output off-chip and then back in again, the DLL can be used to de-skew a board level clock between multiple devices.

In order to guarantee the system clock establishes prior to the device "waking up," the DLL can delay the completion of the device configuration process until after the DLL achieves lock.

By taking advantage of the DLL to remove on-chip clock delay, the designer can greatly simplify and improve system level design involving high-fanout, high-performance clocks.

# **Library DLL Primitives**

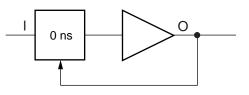

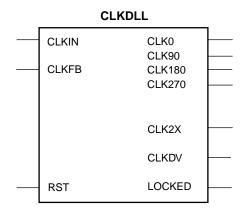

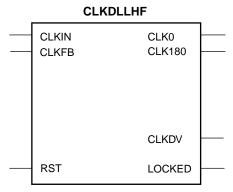

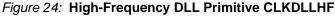

Figure 22 shows the simplified Xilinx library DLL macro, BUFGDLL. This macro delivers a quick and efficient way to provide a system clock with zero propagation delay throughout the device. Figure 23 and Figure 24 show the two library DLL primitives. These primitives provide access to the complete set of DLL features when implementing more complex applications.

Figure 22: Simplified DLL Macro BUFGDLL

DS001\_23\_032300

DS001\_24\_032300

division factor N except for non-integer division in High Frequency (HF) mode. For division factor 1.5 the duty cycle in the HF mode is 33.3% High and 66.7% Low. For division factor 2.5, the duty cycle in the HF mode is 40.0% High and 60.0% Low.

# 1x Clock Outputs — CLK[0/90/180/270]

The 1x clock output pin CLK0 represents a delay-compensated version of the source clock (CLKIN) signal. The CLKDLL primitive provides three phase-shifted versions of the CLK0 signal while CLKDLLHF provides only the 180 degree phase-shifted version. The relationship between phase shift and the corresponding period shift appears in Table 10.

The timing diagrams in Figure 26 illustrate the DLL clock output characteristics.

# Table 10: Relationship of Phase-Shifted Output Clock to Period Shift

| Phase (degrees) | Period Shift (percent) |

|-----------------|------------------------|

| 0               | 0%                     |

| 90              | 25%                    |

| 180             | 50%                    |

| 270             | 75%                    |

The DLL provides duty cycle correction on all 1x clock outputs such that all 1x clock outputs by default have a 50/50 duty cycle. The DUTY\_CYCLE\_CORRECTION property (TRUE by default), controls this feature. In order to deactivate the DLL duty cycle correction, attach the DUTY\_CYCLE\_CORRECTION=FALSE property to the DLL primitive. When duty cycle correction deactivates, the output clock has the same duty cycle as the source clock.

The DLL clock outputs can drive an OBUF, a BUFG, or they can route directly to destination clock pins. The DLL clock outputs can only drive the BUFGs that reside on the same edge (top or bottom).

# Locked Output — LOCKED

In order to achieve lock, the DLL may need to sample several thousand clock cycles. After the DLL achieves lock the LOCKED signal activates. The "DLL Timing Parameters" section of Module 3 provides estimates for locking times.

In order to guarantee that the system clock is established prior to the device "waking up," the DLL can delay the completion of the device configuration process until after the DLL locks. The STARTUP\_WAIT property activates this feature.

Until the LOCKED signal activates, the DLL output clocks are not valid and can exhibit glitches, spikes, or other

spurious movement. In particular the CLK2X output will appear as a 1x clock with a 25/75 duty cycle.

## **DLL Properties**

Properties provide access to some of the Spartan-II family DLL features, (for example, clock division and duty cycle correction).

# **Duty Cycle Correction Property**

The 1x clock outputs, CLK0, CLK90, CLK180, and CLK270, use the duty-cycle corrected default, such that they exhibit a 50/50 duty cycle. The DUTY\_CYCLE\_CORRECTION property (by default TRUE) controls this feature. To deactivate the DLL duty-cycle correction for the 1x clock outputs, attach the DUTY\_CYCLE\_CORRECTION=FALSE property to the DLL primitive.

Figure 26: DLL Output Characteristics

# Clock Divide Property

The CLKDV\_DIVIDE property specifies how the signal on the CLKDV pin is frequency divided with respect to the CLK0 pin. The values allowed for this property are 1.5, 2, 2.5, 3, 4, 5, 8, or 16; the default value is 2.

# Startup Delay Property

This property, STARTUP\_WAIT, takes on a value of TRUE or FALSE (the default value). When TRUE the Startup Sequence following device configuration is paused at a user-specified point until the DLL locks. <u>XAPP176</u>: *Configuration and Readback of the Spartan-II and Spartan-IIE Families* explains how this can result in delaying the assertion of the DONE pin until the DLL locks.

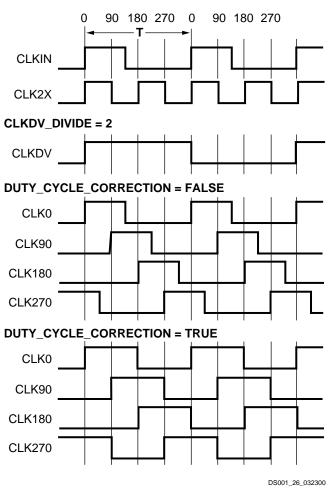

## **DLL Location Constraints**

The DLLs are distributed such that there is one DLL in each corner of the device. The location constraint LOC, attached to the DLL primitive with the numeric identifier 0, 1, 2, or 3, controls DLL location. The orientation of the four DLLs and their corresponding clock resources appears in Figure 27.

The LOC property uses the following form.

LOC = DLL2

Figure 27: Orientation of DLLs

# **Design Considerations**

Use the following design considerations to avoid pitfalls and improve success designing with Xilinx devices.

# Input Clock

The output clock signal of a DLL, essentially a delayed version of the input clock signal, reflects any instability on the input clock in the output waveform. For this reason the quality of the DLL input clock relates directly to the quality of the output clock waveforms generated by the DLL. The DLL input clock requirements are specified in the "DLL Timing Parameters" section of the data sheet.

In most systems a crystal oscillator generates the system clock. The DLL can be used with any commercially available quartz crystal oscillator. For example, most crystal oscillators produce an output waveform with a frequency tolerance of 100 PPM, meaning 0.01 percent change in the clock period. The DLL operates reliably on an input waveform with a frequency drift of up to 1 ns — orders of magnitude in excess of that needed to support any crystal oscillator in the industry. However, the cycle-to-cycle jitter must be kept to less than 300 ps in the low frequencies and 150 ps for the high frequencies.

# Input Clock Changes

Changing the period of the input clock beyond the maximum drift amount requires a manual reset of the CLKDLL. Failure to reset the DLL will produce an unreliable lock signal and output clock.

It is possible to stop the input clock in a way that has little impact to the DLL. Stopping the clock should be limited to less than approximately 100  $\mu$ s to keep device cooling to a minimum and maintain the validity of the current tap setting. The clock should be stopped during a Low phase, and when restored the full High period should be seen. During this time LOCKED will stay High and remain High when the clock is restored. If these conditions may not be met in the design, apply a manual reset to the DLL after re-starting the input clock, even if the LOCKED signal has not changed.

When the clock is stopped, one to four more clocks will still be observed as the delay line is flushed. When the clock is restarted, the output clocks will not be observed for one to four clocks as the delay line is filled. The most common case will be two or three clocks.

In a similar manner, a phase shift of the input clock is also possible. The phase shift will propagate to the output one to four clocks after the original shift, with no disruption to the CLKDLL control.

# **Output Clocks**

As mentioned earlier in the DLL pin descriptions, some restrictions apply regarding the connectivity of the output pins. The DLL clock outputs can drive an OBUF, a global clock buffer BUFG, or route directly to destination clock pins. The only BUFGs that the DLL clock outputs can drive are the two on the same edge of the device (top or bottom). One DLL output can drive more than one OBUF; however, this adds skew.

Do not use the DLL output clock signals until after activation of the LOCKED signal. Prior to the activation of the LOCKED signal, the DLL output clocks are not valid and can exhibit glitches, spikes, or other spurious movement.

# **Creating Larger RAM Structures**

The block RAM columns have specialized routing to allow cascading blocks together with minimal routing delays. This achieves wider or deeper RAM structures with a smaller timing penalty than when using normal routing channels.

# **Location Constraints**

Block RAM instances can have LOC properties attached to them to constrain the placement. The block RAM placement locations are separate from the CLB location naming convention, allowing the LOC properties to transfer easily from array to array.

The LOC properties use the following form:

LOC = RAMB4\_R#C#

RAMB4\_R0C0 is the upper left RAMB4 location on the device.

# **Conflict Resolution**

The block RAM memory is a true dual-read/write port RAM that allows simultaneous access of the same memory cell from both ports. When one port writes to a given memory cell, the other port must not address that memory cell (for a write or a read) within the clock-to-clock setup window. The following lists specifics of port and memory cell write conflict resolution.

- If both ports write to the same memory cell simultaneously, violating the clock-to-clock setup requirement, consider the data stored as invalid.

- If one port attempts a read of the same memory cell the other simultaneously writes, violating the clock-to-clock setup requirement, the following occurs.

- The write succeeds

- The data out on the writing port accurately reflects the data written.

- The data out on the reading port is invalid.

Conflicts do not cause any physical damage.

# Single Port Timing

Figure 33 shows a timing diagram for a single port of a block RAM memory. The block RAM AC switching characteristics are specified in the data sheet. The block RAM memory is initially disabled.

At the first rising edge of the CLK pin, the ADDR, DI, EN, WE, and RST pins are sampled. The EN pin is High and the WE pin is Low indicating a read operation. The DO bus contains the contents of the memory location, 0x00, as indicated by the ADDR bus.

At the second rising edge of the CLK pin, the ADDR, DI, EN, WR, and RST pins are sampled again. The EN and WE pins are High indicating a write operation. The DO bus mirrors

the DI bus. The DI bus is written to the memory location 0x0F.

At the third rising edge of the CLK pin, the ADDR, DI, EN, WR, and RST pins are sampled again. The EN pin is High and the WE pin is Low indicating a read operation. The DO bus contains the contents of the memory location 0x7E as indicated by the ADDR bus.

At the fourth rising edge of the CLK pin, the ADDR, DI, EN, WR, and RST pins are sampled again. The EN pin is Low indicating that the block RAM memory is now disabled. The DO bus retains the last value.

# **Dual Port Timing**

Figure 34 shows a timing diagram for a true dual-port read/write block RAM memory. The clock on port A has a longer period than the clock on Port B. The timing parameter  $T_{BCCS}$ , (clock-to-clock setup) is shown on this diagram. The parameter,  $T_{BCCS}$  is violated once in the diagram. All other timing parameters are identical to the single port version shown in Figure 33.

T<sub>BCCS</sub> is only of importance when the address of both ports are the same and at least one port is performing a write operation. When the clock-to-clock set-up parameter is violated for a WRITE-WRITE condition, the contents of the memory at that location will be invalid. When the clock-to-clock set-up parameter is violated for a WRITE-READ condition, the contents of the memory will be correct, but the read port will have invalid data. At the first rising edge of the CLKA, memory location 0x00 is to be written with the value 0xAAAA and is mirrored on the DOA bus. The last operation of Port B was a read to the same memory location 0x00. The DOB bus of Port B does not change with the new value on Port A, and retains the last read value. A short time later, Port B executes another read to memory location 0x00, and the DOB bus now reflects the new memory value written by Port A.

At the second rising edge of CLKA, memory location 0x7E is written with the value 0x9999 and is mirrored on the DOA bus. Port B then executes a read operation to the same memory location without violating the T<sub>BCCS</sub> parameter and the DOB reflects the new memory values written by Port A.

# PCI — Peripheral Component Interface

The Peripheral Component Interface (PCI) standard specifies support for both 33 MHz and 66 MHz PCI bus applications. It uses a LVTTL input buffer and a push-pull output buffer. This standard does not require the use of a reference voltage ( $V_{REF}$ ) or a board termination voltage ( $V_{TT}$ ), however, it does require a 3.3V output source voltage ( $V_{CCO}$ ). I/Os configured for the PCI, 33 MHz, 5V standard are also 5V-tolerant.

# GTL — Gunning Transceiver Logic Terminated

The Gunning Transceiver Logic (GTL) standard is a high-speed bus standard (JESD8.3). Xilinx has implemented the terminated variation of this standard. This standard requires a differential amplifier input buffer and an open-drain output buffer.

# GTL+ — Gunning Transceiver Logic Plus

The Gunning Transceiver Logic Plus (GTL+) standard is a high-speed bus standard (JESD8.3).

# HSTL — High-Speed Transceiver Logic

The High-Speed Transceiver Logic (HSTL) standard is a general purpose high-speed, 1.5V bus standard (EIA/JESD 8-6). This standard has four variations or classes. Versatile I/O devices support Class I, III, and IV. This standard requires a Differential Amplifier input buffer and a Push-Pull output buffer.

## SSTL3 — Stub Series Terminated Logic for 3.3V

The Stub Series Terminated Logic for 3.3V (SSTL3) standard is a general purpose 3.3V memory bus standard (JESD8-8). This standard has two classes, I and II. Versatile I/O devices support both classes for the SSTL3 standard. This standard requires a Differential Amplifier input buffer and an Push-Pull output buffer.

# SSTL2 — Stub Series Terminated Logic for 2.5V

The Stub Series Terminated Logic for 2.5V (SSTL2) standard is a general purpose 2.5V memory bus standard (JESD8-9). This standard has two classes, I and II. Versatile I/O devices support both classes for the SSTL2 standard. This standard requires a Differential Amplifier input buffer and an Push-Pull output buffer.

# CTT — Center Tap Terminated

The Center Tap Terminated (CTT) standard is a 3.3V memory bus standard (JESD8-4). This standard requires a Differential Amplifier input buffer and a Push-Pull output buffer.

#### AGP-2X — Advanced Graphics Port

The AGP standard is a 3.3V Advanced Graphics Port-2X bus standard used with processors for graphics applications. This standard requires a Push-Pull output buffer and a Differential Amplifier input buffer.

# **Library Primitives**

The Xilinx library includes an extensive list of primitives designed to provide support for the variety of Versatile I/O features. Most of these primitives represent variations of the five generic Versatile I/O primitives:

- IBUF (input buffer)

- IBUFG (global clock input buffer)

- OBUF (output buffer)

- OBUFT (3-state output buffer)

- IOBUF (input/output buffer)

These primitives are available with various extensions to define the desired I/O standard. However, it is recommended that customers use a a property or attribute on the generic primitive to specify the I/O standard. See "Versatile I/O Properties".

#### **IBUF**

Signals used as inputs to the Spartan-II device must source an input buffer (IBUF) via an external input port. The generic IBUF primitive appears in Figure 35. The assumed standard is LVTTL when the generic IBUF has no specified extension or property.

DS001\_35\_061200

Figure 35: Input Buffer (IBUF) Primitive

When the IBUF primitive supports an I/O standard such as LVTTL, LVCMOS, or PCI33\_5, the IBUF automatically configures as a 5V tolerant input buffer unless the V<sub>CCO</sub> for the bank is less than 2V. If the single-ended IBUF is placed in a bank with an HSTL standard (V<sub>CCO</sub> < 2V), the input buffer is not 5V tolerant.

The voltage reference signal is "banked" within the Spartan-II device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 36 for a representation of the I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input.

IBUF placement restrictions require that any differential amplifier input signals within a bank be of the same standard. How to specify a specific location for the IBUF via property. This property could have one of the following seven values.

DRIVE=2 DRIVE=4 DRIVE=6 DRIVE=8 DRIVE=12 (Default) DRIVE=16 DRIVE=24

# **Design Considerations**

# Reference Voltage (V<sub>RFF</sub>) Pins

Low-voltage I/O standards with a differential amplifier input buffer require an input reference voltage (V<sub>RFF</sub>). Provide the V<sub>RFF</sub> as an external signal to the device.

The voltage reference signal is "banked" within the device on a half-edge basis such that for all packages there are eight independent V<sub>RFF</sub> banks internally. See Figure 36, page 39 for a representation of the I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a V<sub>RFF</sub> input.

Within each V<sub>REF</sub> bank, any input buffers that require a V<sub>RFF</sub> signal must be of the same type. Output buffers of any type and input buffers can be placed without requiring a reference voltage within the same V<sub>REF</sub> bank.

# Output Drive Source Voltage (V<sub>CCO</sub>) Pins

Many of the low voltage I/O standards supported by Versatile I/Os require a different output drive source voltage  $(V_{CCO})$ . As a result each device can often have to support multiple output drive source voltages.

The V<sub>CCO</sub> supplies are internally tied together for some packages. The VQ100 and the PQ208 provide one combined  $V_{\mbox{\scriptsize CCO}}$  supply. The TQ144 and the CS144 packages provide four independent V<sub>CCO</sub> supplies. The FG256 and the FG456 provide eight independent V<sub>CCO</sub> supplies.

Output buffers within a given  $V_{CCO}$  bank must share the same output drive source voltage. Input buffers for LVTTL, LVCMOS2, PCI33\_3, and PCI 66\_3 use the V<sub>CCO</sub> voltage for Input V<sub>CCO</sub> voltage.

# Transmission Line Effects

The delay of an electrical signal along a wire is dominated by the rise and fall times when the signal travels a short distance. Transmission line delays vary with inductance and capacitance, but a well-designed board can experience delays of approximately 180 ps per inch.

Transmission line effects, or reflections, typically start at 1.5" for fast (1.5 ns) rise and fall times. Poor (or non-existent) termination or changes in the transmission line impedance cause these reflections and can cause additional delay in longer traces. As system speeds continue to increase, the effect of I/O delays can become a limiting factor and therefore transmission line termination becomes increasingly more important.

# **Termination Techniques**

A variety of termination techniques reduce the impact of transmission line effects.

The following lists output termination techniques:

None Series Parallel (Shunt) Series and Parallel (Series-Shunt)

Input termination techniques include the following:

None Parallel (Shunt)

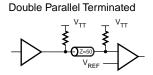

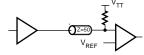

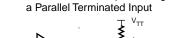

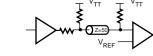

These termination techniques can be applied in any combination. A generic example of each combination of termination methods appears in Figure 41.

Unterminated Output Driving a Parallel Terminated Input

Series Terminated Output Driving

Series-Parallel Terminated Output

Series Terminated Output

Driving a Parallel Terminated Input VTT

DS001 41 032300

Figure 41: Overview of Standard Input and Output **Termination Methods**

# Simultaneous Switching Guidelines

Ground bounce can occur with high-speed digital ICs when multiple outputs change states simultaneously, causing undesired transient behavior on an output, or in the internal logic. This problem is also referred to as the Simultaneous Switching Output (SSO) problem.

Ground bounce is primarily due to current changes in the combined inductance of ground pins, bond wires, and

ground metallization. The IC internal ground level deviates from the external system ground level for a short duration (a few nanoseconds) after multiple outputs change state simultaneously.

Ground bounce affects stable Low outputs and all inputs because they interpret the incoming signal by comparing it to the internal ground. If the ground bounce amplitude exceeds the actual instantaneous noise margin, then a non-changing input can be interpreted as a short pulse with a polarity opposite to the ground bounce.

Table 18 provides the guidelines for the maximum numberof simultaneously switching outputs allowed per outputpower/ground pair to avoid the effects of ground bounce.Refer to Table 19 for the number of effective outputpower/ground pairs for each Spartan-II device and packagecombination.

# Table 18: Maximum Number of Simultaneously Switching Outputs per Power/Ground Pair

|                                   | Package |               |

|-----------------------------------|---------|---------------|

| Standard                          | CS, FG  | PQ,<br>TQ, VQ |

| LVTTL Slow Slew Rate, 2 mA drive  | 68      | 36            |

| LVTTL Slow Slew Rate, 4 mA drive  | 41      | 20            |

| LVTTL Slow Slew Rate, 6 mA drive  | 29      | 15            |

| LVTTL Slow Slew Rate, 8 mA drive  | 22      | 12            |

| LVTTL Slow Slew Rate, 12 mA drive | 17      | 9             |

| LVTTL Slow Slew Rate, 16 mA drive | 14      | 7             |

| LVTTL Slow Slew Rate, 24 mA drive | 9       | 5             |

| LVTTL Fast Slew Rate, 2 mA drive  | 40      | 21            |

| LVTTL Fast Slew Rate, 4 mA drive  | 24      | 12            |

| LVTTL Fast Slew Rate, 6 mA drive  | 17      | 9             |

| LVTTL Fast Slew Rate, 8 mA drive  | 13      | 7             |

| LVTTL Fast Slew Rate, 12 mA drive | 10      | 5             |

| LVTTL Fast Slew Rate, 16 mA drive | 8       | 4             |

| LVTTL Fast Slew Rate, 24 mA drive | 5       | 3             |

| LVCMOS2                           | 10      | 5             |

| PCI                               | 8       | 4             |

| GTL                               | 4       | 4             |

| GTL+                              | 4       | 4             |

| HSTL Class I                      | 18      | 9             |

| HSTL Class III                    | 9       | 5             |

| HSTL Class IV                     | 5       | 3             |

| SSTL2 Class I                     | 15      | 8             |

# Table 18: Maximum Number of SimultaneouslySwitching Outputs per Power/Ground Pair

|                | Package |               |  |

|----------------|---------|---------------|--|

| Standard       | CS, FG  | PQ,<br>TQ, VQ |  |

| SSTL2 Class II | 10      | 5             |  |

| SSTL3 Class I  | 11      | 6             |  |

| SSTL3 Class II | 7       | 4             |  |

| СТТ            | 14      | 7             |  |

| AGP            | 9       | 5             |  |

Notes:

1. This analysis assumes a 35 pF load for each output.

# Table 19: Effective Output Power/Ground Pairs for Spartan-II Devices

|       | Spartan-II Devices |            |            |             |             |             |

|-------|--------------------|------------|------------|-------------|-------------|-------------|

| Pkg.  | XC2S<br>15         | XC2S<br>30 | XC2S<br>50 | XC2S<br>100 | XC2S<br>150 | XC2S<br>200 |

| VQ100 | 8                  | 8          | -          | -           | -           | -           |

| CS144 | 12                 | 12         | -          | -           | -           | -           |

| TQ144 | 12                 | 12         | 12         | 12          | -           | -           |

| PQ208 | -                  | 16         | 16         | 16          | 16          | 16          |

| FG256 | -                  | -          | 16         | 16          | 16          | 16          |

| FG456 | -                  | -          | -          | 48          | 48          | 48          |

# **Termination Examples**

Creating a design with the Versatile I/O features requires the instantiation of the desired library primitive within the design code. At the board level, designers need to know the termination techniques required for each I/O standard.

This section describes some common application examples illustrating the termination techniques recommended by each of the standards supported by the Versatile I/O features. For a full range of accepted values for the DC voltage specifications for each standard, refer to the table associated with each figure.

The resistors used in each termination technique example and the transmission lines depicted represent board level components and are not meant to represent components on the device.

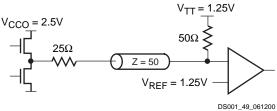

# SSTL2\_I

A sample circuit illustrating a valid termination technique for SSTL2\_I appears in Figure 49. DC voltage specifications appear in Table 27 for the SSTL2\_I standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics

#### SSTL2 Class I

Figure 49: Terminated SSTL2 Class I

| Table 2 | 7: SSTL2 | I Voltage | Specifications |

|---------|----------|-----------|----------------|

|---------|----------|-----------|----------------|

| Parameter                                 | Min                 | Тур  | Max                |

|-------------------------------------------|---------------------|------|--------------------|

| V <sub>CCO</sub>                          | 2.3                 | 2.5  | 2.7                |

| $V_{REF} = 0.5 \times V_{CCO}$            | 1.15                | 1.25 | 1.35               |

| $V_{TT} = V_{REF} + N^{(1)}$              | 1.11                | 1.25 | 1.39               |

| $V_{IH} \ge V_{REF} + 0.18$               | 1.33                | 1.43 | 3.0 <sup>(2)</sup> |

| $V_{IL} \leq V_{REF} - 0.18$              | -0.3 <sup>(3)</sup> | 1.07 | 1.17               |

| V <sub>OH</sub> ≥ V <sub>REF</sub> + 0.61 | 1.76                | -    | -                  |

| $V_{OL} \le V_{REF} - 0.61$               | -                   | -    | 0.74               |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)   | -7.6                | -    | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA)   | 7.6                 | -    | -                  |

#### Notes:

- 1. N must be greater than or equal to -0.04 and less than or equal to 0.04.

- 2.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3.

- 3. V<sub>IL</sub> minimum does not conform to the formula.

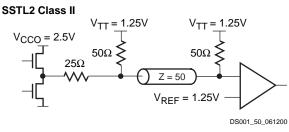

## SSTL2 Class II

A sample circuit illustrating a valid termination technique for SSTL2\_II appears in Figure 50. DC voltage specifications appear in Table 28 for the SSTL2\_II standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 50: Terminated SSTL2 Class II

#### Table 28: SSTL2\_II Voltage Specifications

| Parameter                               | Min                 | Тур  | Max                |

|-----------------------------------------|---------------------|------|--------------------|

| V <sub>CCO</sub>                        | 2.3                 | 2.5  | 2.7                |

| $V_{REF} = 0.5 \times V_{CCO}$          | 1.15                | 1.25 | 1.35               |

| $V_{TT} = V_{REF} + N^{(1)}$            | 1.11                | 1.25 | 1.39               |

| $V_{IH} \ge V_{REF} + 0.18$             | 1.33                | 1.43 | 3.0 <sup>(2)</sup> |

| $V_{IL} \leq V_{REF} - 0.18$            | -0.3 <sup>(3)</sup> | 1.07 | 1.17               |

| $V_{OH} \ge V_{REF} + 0.8$              | 1.95                | -    | -                  |

| $V_{OL} \leq V_{REF} - 0.8$             | -                   | -    | 0.55               |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -15.2               | -    | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 15.2                | -    | -                  |

#### Notes:

- 1. N must be greater than or equal to -0.04 and less than or equal to 0.04.

- 2.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3.

- 3. V<sub>IL</sub> minimum does not conform to the formula.

# XILINX<sup>®</sup>

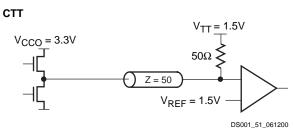

# СТТ

A sample circuit illustrating a valid termination technique for CTT appear in Figure 51. DC voltage specifications appear in Table 29 for the CTT standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics .

Figure 51: Terminated CTT

#### Table 29: CTT Voltage Specifications

| Parameter                               | Min                 | Тур | Max  |

|-----------------------------------------|---------------------|-----|------|

| V <sub>CCO</sub>                        | 2.05 <sup>(1)</sup> | 3.3 | 3.6  |

| V <sub>REF</sub>                        | 1.35                | 1.5 | 1.65 |

| V <sub>TT</sub>                         | 1.35                | 1.5 | 1.65 |

| $V_{IH} \ge V_{REF} + 0.2$              | 1.55                | 1.7 | -    |

| $V_{IL} \leq V_{REF} - 0.2$             | -                   | 1.3 | 1.45 |

| $V_{OH} \ge V_{REF} + 0.4$              | 1.75                | 1.9 | -    |

| $V_{OL} \leq V_{REF} - 0.4$             | -                   | 1.1 | 1.25 |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -8                  | -   | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 8                   | -   | -    |

#### Notes:

1. Timing delays are calculated based on  $V_{CCO}$  min of 3.0V.

## PCI33\_3 and PCI66\_3

PCI33\_3 or PCI66\_3 require no termination. DC voltage specifications appear in Table 30 for the PCI33\_3 and PCI66\_3 standards. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

#### Table 30: PCI33\_3 and PCI66\_3 Voltage Specifications

| Parameter                               | Min    | Тур  | Max                    |

|-----------------------------------------|--------|------|------------------------|

| V <sub>CCO</sub>                        | 3.0    | 3.3  | 3.6                    |

| V <sub>REF</sub>                        | -      | -    | -                      |

| V <sub>TT</sub>                         | -      | -    | -                      |

| $V_{IH} = 0.5 \times V_{CCO}$           | 1.5    | 1.65 | V <sub>CCO</sub> + 0.5 |

| $V_{IL} = 0.3 \times V_{CCO}$           | -0.5   | 0.99 | 1.08                   |

| $V_{OH} = 0.9 \times V_{CCO}$           | 2.7    | -    | -                      |

| $V_{OL} = 0.1 \times V_{CCO}$           | -      | -    | 0.36                   |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | Note 1 | -    | -                      |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | Note 1 | -    | -                      |

#### Notes:

1. Tested according to the relevant specification.

# PCI33\_5

PCI33\_5 requires no termination. DC voltage specifications appear in Table 31 for the PCI33\_5 standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

#### Table 31: PCI33\_5 Voltage Specifications

| Parameter                               | Min    | Тур | Max  |

|-----------------------------------------|--------|-----|------|

| V <sub>CCO</sub>                        | 3.0    | 3.3 | 3.6  |

| V <sub>REF</sub>                        | -      | -   | -    |

| V <sub>TT</sub>                         | -      | -   | -    |

| V <sub>IH</sub>                         | 1.425  | 1.5 | 5.5  |

| V <sub>IL</sub>                         | -0.5   | 1.0 | 1.05 |

| V <sub>OH</sub>                         | 2.4    | -   | -    |

| V <sub>OL</sub>                         | -      | -   | 0.55 |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | Note 1 | -   | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | Note 1 | -   | -    |

#### Notes:

1. Tested according to the relevant specification.

# **Power-On Requirements**

Spartan-II FPGAs require that a minimum supply current  $I_{CCPO}$  be provided to the  $V_{CCINT}$  lines for a successful power-on. If more current is available, the FPGA can consume more than  $I_{CCPO}$  minimum, though this cannot adversely affect reliability.

A maximum limit for  $I_{CCPO}$  is not specified. Therefore the use of foldback/crowbar supplies and fuses deserves special attention. In these cases, limit the  $I_{CCPO}$  current to a level below the trip point for over-current protection in order to avoid inadvertently shutting down the supply.

|                                    |                                 | Conditions                               |                                | New<br>Requirements <sup>(1)</sup><br>For Devices with<br>Date Code 0321<br>or Later |     | Old<br>Requirements <sup>(1)</sup><br>For Devices with<br>Date Code<br>before 0321 |     |       |

|------------------------------------|---------------------------------|------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------|-----|-------|

| Symbol                             | Description                     | Junction<br>Temperature <sup>(2)</sup>   | Device<br>Temperature<br>Grade | Min                                                                                  | Max | Min                                                                                | Max | Units |

| I <sub>CCPO</sub> <sup>(3)</sup>   | Total V <sub>CCINT</sub> supply | $-40^{\circ}C \le T_{J} < -20^{\circ}C$  | Industrial                     | 1.50                                                                                 | -   | 2.00                                                                               | -   | Α     |

|                                    | current required                | $-20^{\circ}C \le T_{J} < 0^{\circ}C$    | Industrial                     | 1.00                                                                                 | -   | 2.00                                                                               | -   | Α     |

|                                    | during power-on                 | $0^{\circ}C \leq T_{J} \leq 85^{\circ}C$ | Commercial                     | 0.25                                                                                 | -   | 0.50                                                                               | -   | Α     |

|                                    |                                 | $85^{\circ}C < T_{J} \le 100^{\circ}C$   | Industrial                     | 0.50                                                                                 | -   | 0.50                                                                               | -   | Α     |

| T <sub>CCPO</sub> <sup>(4,5)</sup> | V <sub>CCINT</sub> ramp time    | –40°C≤ Tj≤ 100°C                         | All                            | -                                                                                    | 50  | -                                                                                  | 50  | ms    |

#### Notes:

1. The date code is printed on the top of the device's package. See the "Device Part Marking" section in Module 1.

2. The expected T<sub>J</sub> range for the design determines the I<sub>CCPO</sub> minimum requirement. Use the applicable ranges in the junction temperature column to find the associated current values in the appropriate new or old requirements column according to the date code. Then choose the highest of these current values to serve as the minimum I<sub>CCPO</sub> requirement that must be met. For example, if the junction temperature for a given design is -25°C ≤ T<sub>J</sub> ≤ 75°C, then the new minimum I<sub>CCPO</sub> requirement is 1.5A. If 5°C ≤ T<sub>J</sub> ≤ 90°C, then the new minimum I<sub>CCPO</sub> requirement is 0.5A.

3. The I<sub>CCPO</sub> requirement applies for a brief time (commonly only a few milliseconds) when V<sub>CCINT</sub> ramps from 0 to 2.5V.

4. The ramp time is measured from GND to V<sub>CCINT</sub> max on a fully loaded board.

5. During power-on, the V<sub>CCINT</sub> ramp must increase steadily in voltage with no dips.

6. For more information on designing to meet the power-on specifications, refer to the application note <u>XAPP450 "Power-On Current</u> <u>Requirements for the Spartan-II and Spartan-IIE Families"</u>

# **DC Input and Output Levels**

Values for  $V_{IL}$  and  $V_{IH}$  are recommended input voltages. Values for  $V_{OL}$  and  $V_{OH}$  are guaranteed output voltages over the recommended operating conditions. Only selected standards are tested. These are chosen to ensure that all standards meet their specifications. The selected standards are tested at minimum V<sub>CCO</sub> with the respective I<sub>OL</sub> and I<sub>OH</sub> currents shown. Other standards are sample tested.

| Input/Output         |        | V <sub>IL</sub>         | V                       | н                      | V <sub>OL</sub>        | V <sub>OH</sub>        | I <sub>OL</sub> | I <sub>ОН</sub> |

|----------------------|--------|-------------------------|-------------------------|------------------------|------------------------|------------------------|-----------------|-----------------|

| Standard             | V, Min | V, Max                  | V, Min                  | V, Max                 | V, Max                 | V, Min                 | mA              | mA              |

| LVTTL <sup>(1)</sup> | -0.5   | 0.8                     | 2.0                     | 5.5                    | 0.4                    | 2.4                    | 24              | -24             |

| LVCMOS2              | -0.5   | 0.7                     | 1.7                     | 5.5                    | 0.4                    | 1.9                    | 12              | -12             |

| PCI, 3.3V            | -0.5   | 44% V <sub>CCINT</sub>  | 60% V <sub>CCINT</sub>  | V <sub>CCO</sub> + 0.5 | 10% V <sub>CCO</sub>   | 90% V <sub>CCO</sub>   | Note (2)        | Note (2)        |

| PCI, 5.0V            | -0.5   | 0.8                     | 2.0                     | 5.5                    | 0.55                   | 2.4                    | Note (2)        | Note (2)        |

| GTL                  | -0.5   | V <sub>REF</sub> – 0.05 | V <sub>REF</sub> + 0.05 | 3.6                    | 0.4                    | N/A                    | 40              | N/A             |

| GTL+                 | -0.5   | V <sub>REF</sub> – 0.1  | V <sub>REF</sub> + 0.1  | 3.6                    | 0.6                    | N/A                    | 36              | N/A             |

| HSTL I               | -0.5   | V <sub>REF</sub> – 0.1  | V <sub>REF</sub> + 0.1  | 3.6                    | 0.4                    | V <sub>CCO</sub> – 0.4 | 8               | -8              |

| HSTL III             | -0.5   | V <sub>REF</sub> – 0.1  | V <sub>REF</sub> + 0.1  | 3.6                    | 0.4                    | V <sub>CCO</sub> – 0.4 | 24              | -8              |

| HSTL IV              | -0.5   | V <sub>REF</sub> – 0.1  | V <sub>REF</sub> + 0.1  | 3.6                    | 0.4                    | V <sub>CCO</sub> – 0.4 | 48              | -8              |

| SSTL3 I              | -0.5   | V <sub>REF</sub> – 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | V <sub>REF</sub> – 0.6 | V <sub>REF</sub> + 0.6 | 8               | -8              |

| SSTL3 II             | -0.5   | V <sub>REF</sub> – 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | V <sub>REF</sub> – 0.8 | V <sub>REF</sub> + 0.8 | 16              | -16             |

| SSTL2 I              | -0.5   | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | V <sub>REF</sub> - 0.6 | V <sub>REF</sub> + 0.6 | 7.6             | -7.6            |

| SSTL2 II             | -0.5   | V <sub>REF</sub> – 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | V <sub>REF</sub> – 0.8 | V <sub>REF</sub> + 0.8 | 15.2            | -15.2           |

# IOB Input Switching Characteristics<sup>(1)</sup>

Input delays associated with the pad are specified for LVTTL levels. For other standards, adjust the delays with the values shown in "IOB Input Delay Adjustments for Different Standards," page 57.

|                                           |                                                  | Speed    |            |     |            |      |       |

|-------------------------------------------|--------------------------------------------------|----------|------------|-----|------------|------|-------|

|                                           |                                                  |          | -6         |     | -5         |      |       |

| Symbol                                    | Description                                      | Device   | Min        | Max | Min        | Max  | Units |

| Propagation Delays                        |                                                  | ·        |            |     |            |      |       |

| T <sub>IOPI</sub>                         | Pad to I output, no delay                        | All      | -          | 0.8 | -          | 1.0  | ns    |

| T <sub>IOPID</sub>                        | Pad to I output, with delay                      | All      | -          | 1.5 | -          | 1.8  | ns    |

| T <sub>IOPLI</sub>                        | Pad to output IQ via transparent latch, no delay | All      | -          | 1.7 | -          | 2.0  | ns    |

| T <sub>IOPLID</sub>                       | Pad to output IQ via transparent latch,          | XC2S15   | -          | 3.8 | -          | 4.5  | ns    |

|                                           | with delay                                       | XC2S30   | -          | 3.8 | -          | 4.5  | ns    |

|                                           |                                                  | XC2S50   | -          | 3.8 | -          | 4.5  | ns    |

|                                           |                                                  | XC2S100  | -          | 3.8 | -          | 4.5  | ns    |

|                                           |                                                  | XC2S150  | -          | 4.0 | -          | 4.7  | ns    |

|                                           |                                                  | XC2S200  | -          | 4.0 | -          | 4.7  | ns    |

| Sequential Delays                         | 1                                                | 1        |            |     | 1          |      |       |

| TIOCKIQ                                   | Clock CLK to output IQ                           | All      | -          | 0.7 | -          | 0.8  | ns    |

| Setup/Hold Times w                        | ith Respect to Clock CLK <sup>(2)</sup>          | <b>I</b> | 1          |     |            |      |       |

| T <sub>IOPICK</sub> / T <sub>IOICKP</sub> | Pad, no delay                                    | All      | 1.7 / 0    | -   | 1.9/0      | -    | ns    |

| TIOPICKD / TIOICKPD                       | Pad, with delay <sup>(1)</sup>                   | XC2S15   | 3.8 / 0    | -   | 4.4 / 0    | -    | ns    |

|                                           |                                                  | XC2S30   | 3.8 / 0    | -   | 4.4 / 0    | -    | ns    |

|                                           |                                                  | XC2S50   | 3.8 / 0    | -   | 4.4 / 0    | -    | ns    |

|                                           |                                                  | XC2S100  | 3.8 / 0    | -   | 4.4 / 0    | -    | ns    |

|                                           |                                                  | XC2S150  | 3.9 / 0    | -   | 4.6 / 0    | -    | ns    |

|                                           |                                                  | XC2S200  | 3.9 / 0    | -   | 4.6 / 0    | -    | ns    |

| TIOICECK / TIOCKICE                       | ICE input                                        | All      | 0.9 / 0.01 | -   | 0.9 / 0.01 | -    | ns    |

| Set/Reset Delays                          |                                                  |          |            |     | 1          | 1    |       |

| T <sub>IOSRCKI</sub>                      | SR input (IFF, synchronous)                      | All      | -          | 1.1 | -          | 1.2  | ns    |

| T <sub>IOSRIQ</sub>                       | SR input to IQ (asynchronous)                    | All      | -          | 1.5 | -          | 1.7  | ns    |

| T <sub>GSRQ</sub>                         | GSR to output IQ                                 | All      | -          | 9.9 | -          | 11.7 | ns    |

Notes:

1. Input timing for LVTTL is measured at 1.4V. For other I/O standards, see the table "Delay Measurement Methodology," page 60.

2. A zero hold time listing indicates no hold time or a negative hold time.

| Package        | Leads | Туре                               | Maximum<br>I/O | Lead Pitch<br>(mm) | Footprint<br>Area (mm) | Height<br>(mm) | Mass <sup>(1)</sup><br>(g) |

|----------------|-------|------------------------------------|----------------|--------------------|------------------------|----------------|----------------------------|

| VQ100 / VQG100 | 100   | Very Thin Quad Flat Pack (VQFP)    | 60             | 0.5                | 16 x 16                | 1.20           | 0.6                        |

| TQ144 / TQG144 | 144   | Thin Quad Flat Pack (TQFP)         | 92             | 0.5                | 22 x 22                | 1.60           | 1.4                        |

| CS144 / CSG144 | 144   | Chip Scale Ball Grid Array (CSBGA) | 92             | 0.8                | 12 x 12                | 1.20           | 0.3                        |

| PQ208 / PQG208 | 208   | Plastic Quad Flat Pack (PQFP)      | 140            | 0.5                | 30.6 x 30.6            | 3.70           | 5.3                        |

| FG256 / FGG256 | 256   | Fine-pitch Ball Grid Array (FBGA)  | 176            | 1.0                | 17 x 17                | 2.00           | 0.9                        |

| FG456 / FGG456 | 456   | Fine-pitch Ball Grid Array (FBGA)  | 284            | 1.0                | 23 x 23                | 2.60           | 2.2                        |

#### Table 36: Spartan-II Family Package Options

#### Notes:

1. Package mass is  $\pm 10\%$ .

Note: Some early versions of Spartan-II devices, including the XC2S15 and XC2S30 ES devices and the XC2S150 with date code 0045 or earlier, included a power-down pin. For more information, see <u>Answer Record 10500</u>.

# VCCO Banks

Some of the I/O standards require specific V<sub>CCO</sub> voltages. These voltages are externally connected to device pins that serve groups of IOBs, called banks. Eight I/O banks result from separating each edge of the FPGA into two banks (see Figure 3 in Module 2). Each bank has multiple V<sub>CCO</sub> pins which must be connected to the same voltage. In the smaller packages, the V<sub>CCO</sub> pins are connected between banks, effectively reducing the number of independent banks available (see Table 37). These interconnected banks are shown in the Pinout Tables with V<sub>CCO</sub> pads for multiple banks connected to the same pin.

#### Table 37: Independent VCCO Banks Available

| Package           | VQ100 | CS144 | FG256 |

|-------------------|-------|-------|-------|

|                   | PQ208 | TQ144 | FG456 |

| Independent Banks | 1     | 4     | 8     |

# **Package Overview**

Table 36 shows the six low-cost, space-saving productionpackage styles for the Spartan-II family.

Each package style is available in an environmentally friendly lead-free (Pb-free) option. The Pb-free packages include an extra 'G' in the package style name. For example, the standard "CS144" package becomes "CSG144" when ordered as the Pb-free option. Leaded (non-Pb-free) packages may be available for selected devices, with the same pin-out and without the "G" in the ordering code; contact Xilinx sales for more information. The mechanical dimensions of the standard and Pb-free packages are similar, as shown in the mechanical drawings provided in Table 38. For additional package information, see <u>UG112</u>: *Device Package User Guide*.

# **Mechanical Drawings**

Detailed mechanical drawings for each package type are available from the Xilinx web site at the specified location in Table 38.

Material Declaration Data Sheets (MDDS) are also available on the <u>Xilinx web site</u> for each package.

#### Table 38: Xilinx Package Documentation

| Package | Drawing         | MDDS         |

|---------|-----------------|--------------|

| VQ100   | Package Drawing | PK173_VQ100  |

| VQG100  |                 | PK130_VQG100 |

| TQ144   | Package Drawing | PK169_TQ144  |

| TQG144  |                 | PK126_TQG144 |

| CS144   | Package Drawing | PK149_CS144  |

| CSG144  | _               | PK103_CSG144 |

| PQ208   | Package Drawing | PK166_PQ208  |

| PQG208  | _               | PK123_PQG208 |

| FG256   | Package Drawing | PK151_FG256  |

| FGG256  |                 | PK105_FGG256 |

| FG456   | Package Drawing | PK154_FG456  |

| FGG456  |                 | PK109_FGG456 |

# Additional XC2S100 Package Pins

#### TQ144

| Not Connected Pins |          |   |   |   |   |  |  |

|--------------------|----------|---|---|---|---|--|--|

| P104               | P105     | - | - | - | - |  |  |

| 11/02/00           | 11/02/00 |   |   |   |   |  |  |

# PQ208

| Not Connected Pins |     |    |    |    |    |  |  |  |

|--------------------|-----|----|----|----|----|--|--|--|

| P55                | P56 | -  | -  | -  | -  |  |  |  |

| 11/02/00           |     | I. | I. | I. | I. |  |  |  |

#### FG256

| V <sub>CCINT</sub> Pins |                              |                     |            |    |     |  |  |  |

|-------------------------|------------------------------|---------------------|------------|----|-----|--|--|--|

| C3                      | C14                          | D4                  | D13        | E5 | E12 |  |  |  |

| M5                      | M12                          | N4                  | N13        | P3 | P14 |  |  |  |

|                         |                              | V <sub>CCO</sub> Ba | nk 0 Pins  |    |     |  |  |  |

| E8                      | F8                           | -                   | -          | -  | -   |  |  |  |

|                         |                              | V <sub>CCO</sub> Ba | nk 1 Pins  |    |     |  |  |  |

| E9                      | F9                           | -                   | -          | -  | -   |  |  |  |

|                         |                              | V <sub>CCO</sub> Ba | nk 2 Pins  |    |     |  |  |  |

| H11                     | H12                          | -                   | -          | -  | -   |  |  |  |

|                         |                              | V <sub>CCO</sub> Ba | nk 3 Pins  |    |     |  |  |  |

| J11                     | J12                          | -                   | -          | -  | -   |  |  |  |

|                         |                              | V <sub>CCO</sub> Ba | nk 4 Pins  |    |     |  |  |  |

| L9                      | M9                           | -                   | -          | -  | -   |  |  |  |

|                         | V <sub>CCO</sub> Bank 5 Pins |                     |            |    |     |  |  |  |

| L8                      | M8                           | -                   | -          | -  | -   |  |  |  |

|                         |                              | V <sub>CCO</sub> Ba | nk 6 Pins  |    |     |  |  |  |

| J5                      | J6                           | -                   | -          | -  | -   |  |  |  |

|                         |                              | V <sub>CCO</sub> Ba | nk 7 Pins  |    |     |  |  |  |

| H5                      | H6                           | -                   | -          | -  | -   |  |  |  |

|                         |                              | GND                 | Pins       |    |     |  |  |  |

| A1                      | A16                          | B2                  | B15        | F6 | F7  |  |  |  |

| F10                     | F11                          | G6                  | G7         | G8 | G9  |  |  |  |

| G10                     | G11                          | H7                  | H8         | H9 | H10 |  |  |  |

| J7                      | J8                           | J9                  | J10        | K6 | K7  |  |  |  |

| K8                      | K9                           | K10                 | K11        | L6 | L7  |  |  |  |

| L10                     | L11                          | R2                  | R15        | T1 | T16 |  |  |  |

|                         |                              | Not Conn            | ected Pins |    |     |  |  |  |

| P4                      | R4                           | -                   | -          | -  | -   |  |  |  |

| 11/02/00                |                              |                     |            |    |     |  |  |  |

# 11/02/00

#### FG456

|    | V <sub>CCINT</sub> Pins      |     |     |     |     |  |  |  |

|----|------------------------------|-----|-----|-----|-----|--|--|--|

| E5 | E18                          | F6  | F17 | G7  | G8  |  |  |  |

| G9 | G14                          | G15 | G16 | H7  | H16 |  |  |  |

| J7 | J16                          | P7  | P16 | R7  | R16 |  |  |  |

| T7 | T8                           | Т9  | T14 | T15 | T16 |  |  |  |

| U6 | U6 U17 V5 V18                |     |     |     |     |  |  |  |

|    | V <sub>CCO</sub> Bank 0 Pins |     |     |     |     |  |  |  |

# Additional XC2S100 Package Pins (Continued)

|          |      | IUU Fach             | ago i int  |      | uou) |

|----------|------|----------------------|------------|------|------|

| F10      | F7   | F8                   | F9         | G10  | G11  |

|          |      | V <sub>CCO</sub> Bar | nk 1 Pins  |      |      |

| F13      | F14  | F15                  | F16        | G12  | G13  |

|          |      | V <sub>CCO</sub> Bai | nk 2 Pins  |      |      |

| G17      | H17  | J17                  | K16        | K17  | L16  |

|          |      | V <sub>CCO</sub> Bai | nk 3 Pins  |      |      |

| M16      | N16  | N17                  | P17        | R17  | T17  |

|          |      | V <sub>CCO</sub> Bar | nk 4 Pins  |      |      |

| T12      | T13  | U13                  | U14        | U15  | U16  |

|          |      | V <sub>CCO</sub> Bai | nk 5 Pins  |      |      |

| T10      | T11  | U10                  | U7         | U8   | U9   |

|          |      | V <sub>CCO</sub> Bai | nk 6 Pins  |      |      |

| M7       | N6   | N7                   | P6         | R6   | T6   |

|          |      | V <sub>CCO</sub> Bar | nk 7 Pins  |      |      |

| G6       | H6   | J6                   | K6         | K7   | L7   |

|          |      | GND                  | Pins       |      |      |

| A1       | A22  | B2                   | B21        | C3   | C20  |

| J9       | J10  | J11                  | J12        | J13  | J14  |

| K9       | K10  | K11                  | K12        | K13  | K14  |

| L9       | L10  | L11                  | L12        | L13  | L14  |

| M9       | M10  | M11                  | M12        | M13  | M14  |

| N9       | N10  | N11                  | N12        | N13  | N14  |

| P9       | P10  | P11                  | P12        | P13  | P14  |

| Y3       | Y20  | AA2                  | AA21       | AB1  | AB22 |

| L        |      | Not Conne            | ected Pins |      |      |

| A2       | A4   | A5                   | A6         | A12  | A13  |

| A14      | A15  | A17                  | B3         | B6   | B8   |

| B11      | B14  | B16                  | B19        | C1   | C2   |

| C8       | C9   | C12                  | C18        | C22  | D1   |

| D4       | D5   | D10                  | D18        | D19  | D21  |

| E4       | E11  | E13                  | E15        | E16  | E17  |

| E19      | E22  | F4                   | F11        | F22  | G2   |

| G3       | G4   | G19                  | G22        | H1   | H21  |

| J1       | J3   | J4                   | J19        | J20  | K2   |

| K18      | K19  | L2                   | L5         | L18  | L19  |

| M2       | M6   | M17                  | M18        | M21  | N1   |

| N5       | N19  | P1                   | P5         | P19  | P22  |

| R1       | R3   | R20                  | R22        | T5   | T19  |

| U3       | U11  | U18                  | V1         | V2   | V10  |

| V12      | V17  | V3                   | V4         | V6   | V8   |

| V20      | V21  | V22                  | W4         | W5   | W9   |

| W13      | W14  | W15                  | W16        | W19  | Y5   |

| Y14      | Y18  | Y22                  | AA1        | AA3  | AA6  |

| AA9      | AA10 | AA11                 | AA16       | AA17 | AA18 |

| AA22     | AB3  | AB4                  | AB7        | AB8  | AB12 |

| AB14     | AB21 | -                    | -          | -    | -    |

| 11/02/00 |      |                      |            | 1    |      |

# **XC2S200 Device Pinouts**

| XC2S200 Pa            | d Name |       |                             |                             | Bndry |

|-----------------------|--------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank   | PQ208 | FG256                       | FG456                       | Scan  |

| GND                   | -      | P1    | GND*                        | GND*                        | -     |

| TMS                   | -      | P2    | D3                          | D3                          | -     |

| I/O                   | 7      | P3    | C2                          | B1                          | 257   |

| I/O                   | 7      | -     | -                           | E4                          | 263   |

| I/O                   | 7      | -     | -                           | C1                          | 266   |

| I/O                   | 7      | -     | A2                          | F5                          | 269   |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O, V <sub>REF</sub> | 7      | P4    | B1                          | D2                          | 272   |

| I/O                   | 7      | -     | -                           | E3                          | 275   |

| I/O                   | 7      | -     | -                           | F4                          | 281   |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O                   | 7      | -     | E3                          | G5                          | 284   |

| I/O                   | 7      | P5    | D2                          | F3                          | 287   |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 7      | -     | V <sub>CCO</sub><br>Bank 7* | V <sub>CCO</sub><br>Bank 7* | -     |

| I/O, V <sub>REF</sub> | 7      | P6    | C1                          | E2                          | 290   |

| I/O                   | 7      | P7    | F3                          | E1                          | 293   |

| I/O                   | 7      | -     | -                           | G4                          | 296   |

| I/O                   | 7      | -     | -                           | G3                          | 299   |

| I/O                   | 7      | -     | E2                          | H5                          | 302   |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O                   | 7      | P8    | E4                          | F2                          | 305   |

| I/O                   | 7      | -     | -                           | F1                          | 308   |