# E·XFL

#### AMD Xilinx - XC2S150-6FG256C Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | 864                                                         |

| Number of Logic Elements/Cells | 3888                                                        |

| Total RAM Bits                 | 49152                                                       |

| Number of I/O                  | 176                                                         |

| Number of Gates                | 150000                                                      |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 256-BGA                                                     |

| Supplier Device Package        | 256-FBGA (17x17)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s150-6fg256c |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **General Overview**

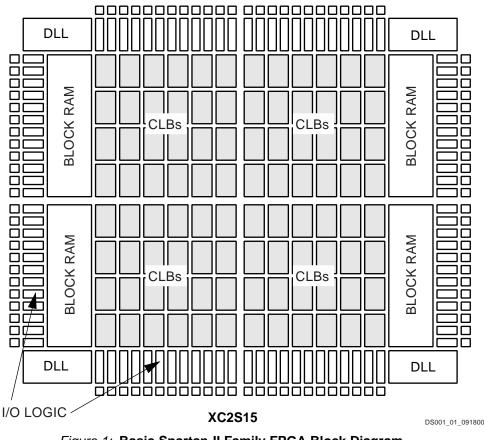

The Spartan-II family of FPGAs have a regular, flexible, programmable architecture of Configurable Logic Blocks (CLBs), surrounded by a perimeter of programmable Input/Output Blocks (IOBs). There are four Delay-Locked Loops (DLLs), one at each corner of the die. Two columns of block RAM lie on opposite sides of the die, between the CLBs and the IOB columns. These functional elements are interconnected by a powerful hierarchy of versatile routing channels (see Figure 1).

Spartan-II FPGAs are customized by loading configuration data into internal static memory cells. Unlimited reprogramming cycles are possible with this approach. Stored values in these cells determine logic functions and interconnections implemented in the FPGA. Configuration data can be read from an external serial PROM (master serial mode), or written into the FPGA in slave serial, slave parallel, or Boundary Scan modes.

Spartan-II FPGAs are typically used in high-volume applications where the versatility of a fast programmable solution adds benefits. Spartan-II FPGAs are ideal for shortening product development cycles while offering a cost-effective solution for high volume production.

Spartan-II FPGAs achieve high-performance, low-cost operation through advanced architecture and semiconductor technology. Spartan-II devices provide system clock rates up to 200 MHz. In addition to the conventional benefits of high-volume programmable logic solutions, Spartan-II FPGAs also offer on-chip synchronous single-port and dual-port RAM (block and distributed form), DLL clock drivers, programmable set and reset on all flip-flops, fast carry logic, and many other features.

Figure 1: Basic Spartan-II Family FPGA Block Diagram

## **Ordering Information**

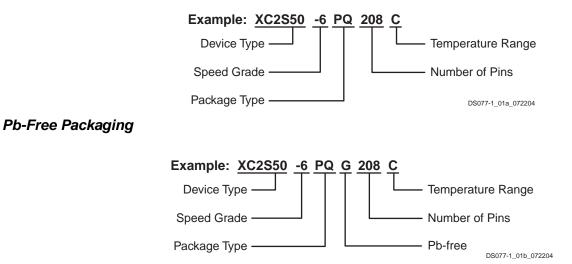

Spartan-II devices are available in both standard and Pb-free packaging options for all device/package combinations. The Pb-free packages include a special "G" character in the ordering code.

#### Standard Packaging

## **Device Ordering Options**

| Device  |    | Speed Grade                       | Numb     | per of Pins / Package Type    | Temperatur     | re Range (T <sub>J</sub> ) |

|---------|----|-----------------------------------|----------|-------------------------------|----------------|----------------------------|

| XC2S15  | -5 | Standard Performance              | VQ(G)100 | 100-pin Plastic Very Thin QFP | C = Commercial | 0°C to +85°C               |

| XC2S30  | -6 | Higher Performance <sup>(1)</sup> | CS(G)144 | 144-ball Chip-Scale BGA       | I = Industrial | -40°C to +100°C            |

| XC2S50  |    |                                   | TQ(G)144 | 144-pin Plastic Thin QFP      |                |                            |

| XC2S100 |    |                                   | PQ(G)208 | 208-pin Plastic QFP           |                |                            |

| XC2S150 |    |                                   | FG(G)256 | 256-ball Fine Pitch BGA       |                |                            |

| XC2S200 |    |                                   | FG(G)456 | 456-ball Fine Pitch BGA       |                |                            |

#### Notes:

1. The -6 speed grade is exclusively available in the Commercial temperature range.

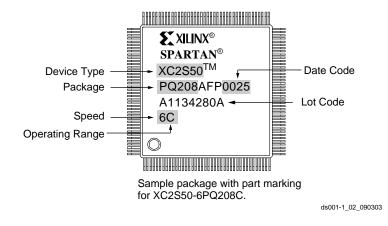

## **Device Part Marking**

www.xilinx.com

# **∑** XILINX<sup>®</sup>

## Local Routing

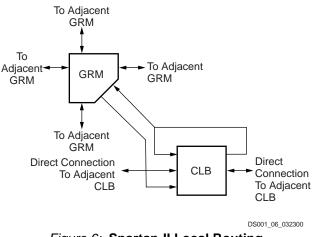

The local routing resources, as shown in Figure 6, provide the following three types of connections:

- Interconnections among the LUTs, flip-flops, and General Routing Matrix (GRM)

- Internal CLB feedback paths that provide high-speed connections to LUTs within the same CLB, chaining them together with minimal routing delay

- Direct paths that provide high-speed connections between horizontally adjacent CLBs, eliminating the delay of the GRM

Figure 6: Spartan-II Local Routing

## General Purpose Routing

Most Spartan-II FPGA signals are routed on the general purpose routing, and consequently, the majority of interconnect resources are associated with this level of the routing hierarchy. The general routing resources are located in horizontal and vertical routing channels associated with the rows and columns CLBs. The general-purpose routing resources are listed below.

- Adjacent to each CLB is a General Routing Matrix (GRM). The GRM is the switch matrix through which horizontal and vertical routing resources connect, and is also the means by which the CLB gains access to the general purpose routing.

- 24 single-length lines route GRM signals to adjacent GRMs in each of the four directions.

- 96 buffered Hex lines route GRM signals to other GRMs six blocks away in each one of the four directions. Organized in a staggered pattern, Hex lines may be driven only at their endpoints. Hex-line signals can be accessed either at the endpoints or at the midpoint (three blocks from the source). One third of the Hex lines are bidirectional, while the remaining ones are unidirectional.

- 12 Longlines are buffered, bidirectional wires that distribute signals across the device quickly and

efficiently. Vertical Longlines span the full height of the device, and horizontal ones span the full width of the device.

## I/O Routing

Spartan-II devices have additional routing resources around their periphery that form an interface between the CLB array and the IOBs. This additional routing, called the VersaRing, facilitates pin-swapping and pin-locking, such that logic redesigns can adapt to existing PCB layouts. Time-to-market is reduced, since PCBs and other system components can be manufactured while the logic design is still in progress.

## **Dedicated Routing**

Some classes of signal require dedicated routing resources to maximize performance. In the Spartan-II architecture, dedicated routing resources are provided for two classes of signal.

- Horizontal routing resources are provided for on-chip 3-state busses. Four partitionable bus lines are provided per CLB row, permitting multiple busses within a row, as shown in Figure 7.

- Two dedicated nets per CLB propagate carry signals vertically to the adjacent CLB.

## **Global Routing**

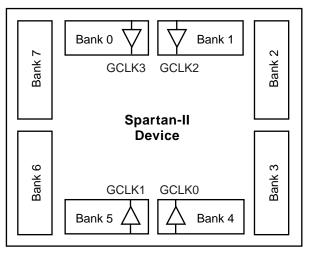

Global Routing resources distribute clocks and other signals with very high fanout throughout the device. Spartan-II devices include two tiers of global routing resources referred to as primary and secondary global routing resources.

- The primary global routing resources are four dedicated global nets with dedicated input pins that are designed to distribute high-fanout clock signals with minimal skew. Each global clock net can drive all CLB, IOB, and block RAM clock pins. The primary global nets may only be driven by global buffers. There are four global buffers, one for each global net.

- The secondary global routing resources consist of 24 backbone lines, 12 across the top of the chip and 12 across bottom. From these lines, up to 12 unique signals per column can be distributed via the 12 longlines in the column. These secondary resources are more flexible than the primary resources since they are not restricted to routing only to clock pins.

## Master Serial Mode

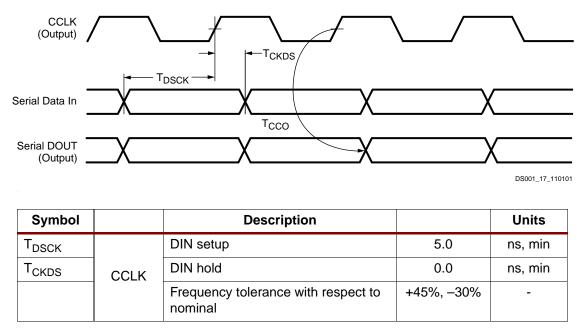

In Master Serial mode, the CCLK output of the FPGA drives a Xilinx PROM which feeds a serial stream of configuration data to the FPGA's DIN input. Figure 15 shows a Master Serial FPGA configuring a Slave Serial FPGA from a PROM. A Spartan-II device in Master Serial mode should be connected as shown for the device on the left side. Master Serial mode is selected by a <00x> on the mode pins (M0, M1, M2). The PROM RESET pin is driven by INIT, and CE input is driven by DONE. The interface is identical to the slave serial mode except that an oscillator internal to the FPGA is used to generate the configuration clock (CCLK). Any of a number of different frequencies ranging from 4 to 60 MHz can be set using the ConfigRate option in the Xilinx software. On power-up, while the first 60 bytes of the configuration data are being loaded, the CCLK frequency is always 2.5 MHz. This frequency is used until the ConfigRate bits, part of the configuration file, have been loaded into the FPGA, at which point, the frequency changes to the selected ConfigRate. Unless a different frequency is specified in the design, the default ConfigRate is 4 MHz. The frequency of the CCLK signal created by the internal oscillator has a variance of +45%, -30% from the specified value.

Figure 17 shows the timing for Master Serial configuration. The FPGA accepts one bit of configuration data on each rising CCLK edge. After the FPGA has been loaded, the data for the next device in a daisy-chain is presented on the DOUT pin after the rising CCLK edge.

Figure 17: Master Serial Mode Timing

## **Slave Parallel Mode**

The Slave Parallel mode is the fastest configuration option. Byte-wide data is written into the FPGA. A BUSY flag is provided for controlling the flow of data at a clock frequency  $F_{CCNH}$  above 50 MHz.

Figure 18, page 24 shows the connections for two Spartan-II devices using the Slave Parallel mode. Slave Parallel mode is selected by a <011> on the mode pins (M0, M1, M2).

If a configuration file of the format .bit, .rbt, or non-swapped HEX is used for parallel programming, then the most significant bit (i.e. the left-most bit of each configuration byte, as displayed in a text editor) must be routed to the D0 input on the FPGA. The agent controlling configuration is not shown. Typically, a processor, a microcontroller, or CPLD controls the Slave Parallel interface. The controlling agent provides byte-wide configuration data, CCLK, a Chip Select ( $\overline{CS}$ ) signal and a Write signal (WRITE). If BUSY is asserted (High) by the FPGA, the data must be held until BUSY goes Low.

After configuration, the pins of the Slave Parallel port (D0-D7) can be used as additional user I/O. Alternatively, the port may be retained to permit high-speed 8-bit readback. Then data can be read by de-asserting WRITE. See "Readback," page 25.

www.xilinx.com

## **BUFGDLL Pin Descriptions**

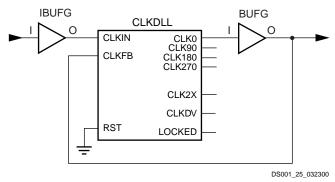

Use the BUFGDLL macro as the simplest way to provide zero propagation delay for a high-fanout on-chip clock from an external input. This macro uses the IBUFG, CLKDLL and BUFG primitives to implement the most basic DLL application as shown in Figure 25.

Figure 25: BUFGDLL Block Diagram

This macro does not provide access to the advanced clock domain controls or to the clock multiplication or clock division features of the DLL. This macro also does not provide access to the RST or LOCKED pins of the DLL. For access to these features, a designer must use the DLL primitives described in the following sections.

## Source Clock Input — I

The I pin provides the user source clock, the clock signal on which the DLL operates, to the BUFGDLL. For the BUFGDLL macro the source clock frequency must fall in the low frequency range as specified in the data sheet. The BUFGDLL requires an external signal source clock. Therefore, only an external input port can source the signal that drives the BUFGDLL I pin.

#### Clock Output — O

The clock output pin O represents a delay-compensated version of the source clock (I) signal. This signal, sourced by a global clock buffer BUFG primitive, takes advantage of the dedicated global clock routing resources of the device.

The output clock has a 50/50 duty cycle unless you deactivate the duty cycle correction property.

## **CLKDLL Primitive Pin Descriptions**

The library CLKDLL primitives provide access to the complete set of DLL features needed when implementing more complex applications with the DLL.

#### Source Clock Input — CLKIN

The CLKIN pin provides the user source clock (the clock signal on which the DLL operates) to the DLL. The CLKIN frequency must fall in the ranges specified in the data sheet. A global clock buffer (BUFG) driven from another CLKDLL

or one of the global clock input buffers (IBUFG) on the same edge of the device (top or bottom) must source this clock signal.

## Feedback Clock Input — CLKFB

The DLL requires a reference or feedback signal to provide the delay-compensated output. Connect only the CLK0 or CLK2X DLL outputs to the feedback clock input (CLKFB) pin to provide the necessary feedback to the DLL. Either a global clock buffer (BUFG) or one of the global clock input buffers (IBUFG) on the same edge of the device (top or bottom) must source this clock signal.

If an IBUFG sources the CLKFB pin, the following special rules apply.

- 1. An external input port must source the signal that drives the IBUFG I pin.

- The CLK2X output must feed back to the device if both the CLK0 and CLK2X outputs are driving off chip devices.

- 3. That signal must directly drive only OBUFs and nothing else.

These rules enable the software to determine which DLL clock output sources the CLKFB pin.

## Reset Input — RST

When the reset pin RST activates, the LOCKED signal deactivates within four source clock cycles. The RST pin, active High, must either connect to a dynamic signal or be tied to ground. As the DLL delay taps reset to zero, glitches can occur on the DLL clock output pins. Activation of the RST pin can also severely affect the duty cycle of the clock output pins. Furthermore, the DLL output clocks no longer deskew with respect to one another. The DLL must be reset when the input clock frequency changes, if the device is reconfigured in Boundary-Scan mode, if the device undergoes a hot swap, and after the device is configured if the input clock is not stable during the startup sequence.

## 2x Clock Output — CLK2X

The output pin CLK2X provides a frequency-doubled clock with an automatic 50/50 duty-cycle correction. Until the CLKDLL has achieved lock, the CLK2X output appears as a 1x version of the input clock with a 25/75 duty cycle. This behavior allows the DLL to lock on the correct edge with respect to source clock. This pin is not available on the CLKDLLHF primitive.

#### Clock Divide Output — CLKDV

The clock divide output pin CLKDV provides a lower frequency version of the source clock. The CLKDV\_DIVIDE property controls CLKDV such that the source clock is divided by N where N is either 1.5, 2, 2.5, 3, 4, 5, 8, or 16.

This feature provides automatic duty cycle correction. The CLKDV output pin has a 50/50 duty cycle for all values of the

#### Table 11: Available Library Primitives

| Primitive                                               | Port A Width | Port B Width         |

|---------------------------------------------------------|--------------|----------------------|

| RAMB4_S4<br>RAMB4_S4_S4<br>RAMB4_S4_S8<br>RAMB4_S4_S16  | 4            | N/A<br>4<br>8        |

| RAMB4_S4_S16<br>RAMB4_S8<br>RAMB4_S8_S8<br>RAMB4_S8_S16 | 8            | 16<br>N/A<br>8<br>16 |

| RAMB4_S16<br>RAMB4_S16_S16                              | 16           | N/A<br>16            |

## **Port Signals**

Each block RAM port operates independently of the others while accessing the same set of 4096 memory cells.

Table 12 describes the depth and width aspect ratios for the block RAM memory.

Table 12: Block RAM Port Aspect Ratios

| Width | Depth | ADDR Bus   | Data Bus   |

|-------|-------|------------|------------|

| 1     | 4096  | ADDR<11:0> | DATA<0>    |

| 2     | 2048  | ADDR<10:0> | DATA<1:0>  |

| 4     | 1024  | ADDR<9:0>  | DATA<3:0>  |

| 8     | 512   | ADDR<8:0>  | DATA<7:0>  |

| 16    | 256   | ADDR<7:0>  | DATA<15:0> |

## Clock—CLK[A/B]

Each port is fully synchronous with independent clock pins. All port input pins have setup time referenced to the port CLK pin. The data output bus has a clock-to-out time referenced to the CLK pin.

## Enable—EN[A/B]

The enable pin affects the read, write and reset functionality of the port. Ports with an inactive enable pin keep the output pins in the previous state and do not write data to the memory cells.

## Write Enable—WE[A/B]

Activating the write enable pin allows the port to write to the memory cells. When active, the contents of the data input bus are written to the RAM at the address pointed to by the address bus, and the new data also reflects on the data out bus. When inactive, a read operation occurs and the contents of the memory cells referenced by the address bus reflect on the data out bus.

#### Reset—RST[A|B]

The reset pin forces the data output bus latches to zero synchronously. This does not affect the memory cells of the RAM and does not disturb a write operation on the other port.

## Address Bus—ADDR[A/B]<#:0>

The address bus selects the memory cells for read or write. The width of the port determines the required width of this bus as shown in Table 12.

## Data In Bus-DI[A/B]<#:0>

The data in bus provides the new data value to be written into the RAM. This bus and the port have the same width, as shown in Table 12.

## Data Output Bus—DO[A/B]<#:0>

The data out bus reflects the contents of the memory cells referenced by the address bus at the last active clock edge. During a write operation, the data out bus reflects the data in bus. The width of this bus equals the width of the port. The allowed widths appear in Table 12.

## **Inverting Control Pins**

The four control pins (CLK, EN, WE and RST) for each port have independent inversion control as a configuration option.

## **Address Mapping**

Each port accesses the same set of 4096 memory cells using an addressing scheme dependent on the width of the port. The physical RAM location addressed for a particular width are described in the following formula (of interest only when the two ports use different aspect ratios).

Table 13 shows low order address mapping for each portwidth.

Table 13: Port Address Mapping

| Port<br>Widt<br>h |      | Port<br>Addresses |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

|-------------------|------|-------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 1                 | 4095 | 1<br>5            | 1<br>4 | 1<br>3 | 1<br>2 | 1<br>1 | 1<br>0 | 0<br>9 | 0<br>8 | 0<br>7 | 0<br>6 | 0<br>5 | 0<br>4 | 0<br>3 | 0<br>2 | 0<br>1 | 0<br>0 |

| 2                 | 2047 | 0                 | 7      | 0      | 6      | 05 04  |        | 03 02  |        | 2      | 01     |        | 0      | 0      |        |        |        |

| 4                 | 1023 |                   | 0      | 3      | 02 01  |        |        | 01 00  |        |        | 0      |        |        |        |        |        |        |

| 8                 | 511  | 01                |        |        |        |        |        |        |        | 0      | 0      |        |        |        |        |        |        |

| 16                | 255  |                   |        |        |        |        |        |        | 0      | 0      |        |        |        |        |        |        |        |

the LOC property is described below. Table 16 summarizes the input standards compatibility requirements.

An optional delay element is associated with each IBUF. When the IBUF drives a flip-flop within the IOB, the delay element by default activates to ensure a zero hold-time requirement. The NODELAY=TRUE property overrides this default.

When the IBUF does not drive a flip-flop within the IOB, the delay element de-activates by default to provide higher performance. To delay the input signal, activate the delay element with the DELAY=TRUE property.

DS001\_03\_060100

Figure 36: I/O Banks

# Table 16: Xilinx Input Standards CompatibilityRequirements

| Rule 1 | All differential amplifier input signals within a bank are required to be of the same standard.         |

|--------|---------------------------------------------------------------------------------------------------------|

| Rule 2 | There are no placement restrictions for inputs with standards that require a single-ended input buffer. |

#### IBUFG

Signals used as high fanout clock inputs to the Spartan-II device should drive a global clock input buffer (IBUFG) via an external input port in order to take advantage of one of the four dedicated global clock distribution networks. The output of the IBUFG primitive can only drive a CLKDLL, CLKDLLHF, or a BUFG primitive. The generic IBUFG primitive appears in Figure 37.

DS001\_37\_061200

Figure 37: Global Clock Input Buffer (IBUFG) Primitive

With no extension or property specified for the generic IBUFG primitive, the assumed standard is LVTTL.

The voltage reference signal is "banked" within the Spartan-II device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 36 for a representation of the I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input.

IBUFG placement restrictions require any differential amplifier input signals within a bank be of the same standard. The LOC property can specify a location for the IBUFG.

As an added convenience, the BUFGP can be used to instantiate a high fanout clock input. The BUFGP primitive represents a combination of the LVTTL IBUFG and BUFG primitives, such that the output of the BUFGP can connect directly to the clock pins throughout the design.

The Spartan-II FPGA BUFGP primitive can only be placed in a global clock pad location. The LOC property can specify a location for the BUFGP.

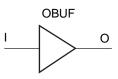

#### OBUF

An OBUF must drive outputs through an external output port. The generic output buffer (OBUF) primitive appears in Figure 38.

DS001\_38\_061200

#### Figure 38: Output Buffer (OBUF) Primitive

With no extension or property specified for the generic OBUF primitive, the assumed standard is slew rate limited LVTTL with 12 mA drive strength.

The LVTTL OBUF additionally can support one of two slew rate modes to minimize bus transients. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals.

# XILINX<sup>®</sup>

## LVTTL

LVTTL requires no termination. DC voltage specifications appears in Table 32 for the LVTTL standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

| Table | 32: | LVTTL | Voltage | Specifications |

|-------|-----|-------|---------|----------------|

|-------|-----|-------|---------|----------------|

| Parameter                               | Min  | Тур | Max |

|-----------------------------------------|------|-----|-----|

| V <sub>CCO</sub>                        | 3.0  | 3.3 | 3.6 |

| V <sub>REF</sub>                        | -    | -   | -   |

| V <sub>TT</sub>                         | -    | -   | -   |

| V <sub>IH</sub>                         | 2.0  | -   | 5.5 |

| V <sub>IL</sub>                         | -0.5 | -   | 0.8 |

| V <sub>OH</sub>                         | 2.4  | -   | -   |

| V <sub>OL</sub>                         | -    | -   | 0.4 |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -24  | -   | -   |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 24   | -   | -   |

#### Notes:

1.  $V_{OL}$  and  $V_{OH}$  for lower drive currents sample tested.

#### LVCMOS2

LVCMOS2 requires no termination. DC voltage specifications appear in Table 33 for the LVCMOS2 standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

#### Table 33: LVCMOS2 Voltage Specifications

| Parameter                               | Min  | Тур | Max |

|-----------------------------------------|------|-----|-----|

| V <sub>CCO</sub>                        | 2.3  | 2.5 | 2.7 |

| V <sub>REF</sub>                        | -    | -   | -   |

| V <sub>TT</sub>                         | -    | -   | -   |

| V <sub>IH</sub>                         | 1.7  | -   | 5.5 |

| V <sub>IL</sub>                         | -0.5 | -   | 0.7 |

| V <sub>OH</sub>                         | 1.9  | -   | -   |

| V <sub>OL</sub>                         | -    | -   | 0.4 |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -12  | -   | -   |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 12   | -   | -   |

#### AGP-2X

The specification for the AGP-2X standard does not document a recommended termination technique. DC voltage specifications appear in Table 34 for the AGP-2X standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

#### Table 34: AGP-2X Voltage Specifications

| Parameter                               | Min    | Тур  | Max  |

|-----------------------------------------|--------|------|------|

| V <sub>CCO</sub>                        | 3.0    | 3.3  | 3.6  |

| $V_{REF} = N \times V_{CCO}^{(1)}$      | 1.17   | 1.32 | 1.48 |

| V <sub>TT</sub>                         | -      | -    | -    |

| $V_{IH} \ge V_{REF} + 0.2$              | 1.37   | 1.52 | -    |

| $V_{IL} \le V_{REF} - 0.2$              | -      | 1.12 | 1.28 |

| $V_{OH} \ge 0.9 \times V_{CCO}$         | 2.7    | 3.0  | -    |

| $V_{OL} \le 0.1 \times V_{CCO}$         | -      | 0.33 | 0.36 |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | Note 2 | -    | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | Note 2 | -    | -    |

#### Notes:

For design examples and more information on using the I/O, see <u>XAPP179</u>, Using SelectIO Interfaces in Spartan-II and Spartan-IIE FPGAs.

<sup>1.</sup> N must be greater than or equal to 0.39 and less than or equal to 0.41.

<sup>2.</sup> Tested according to the relevant specification.

## **Recommended Operating Conditions**

| Symbol             | Description                                     |            | Min      | Мах      | Units |  |

|--------------------|-------------------------------------------------|------------|----------|----------|-------|--|

| ТJ                 | Junction temperature <sup>(1)</sup> Commercial  |            | 0        | 85       | °C    |  |

|                    |                                                 | Industrial | -40      | 100      | °C    |  |

| V <sub>CCINT</sub> | Supply voltage relative to GND <sup>(2,5)</sup> | Commercial | 2.5 – 5% | 2.5 + 5% | V     |  |

|                    |                                                 | Industrial | 2.5 – 5% | 2.5 + 5% | V     |  |

| V <sub>CCO</sub>   | Supply voltage relative to GND <sup>(3,5)</sup> | Commercial | 1.4      | 3.6      | V     |  |

|                    |                                                 | Industrial | 1.4      | 3.6      | V     |  |

| T <sub>IN</sub>    | Input signal transition time <sup>(4)</sup>     |            | -        | 250      | ns    |  |

#### Notes:

1. At junction temperatures above those listed as Operating Conditions, all delay parameters increase by 0.35% per °C.

2. Functional operation is guaranteed down to a minimum  $V_{CCINT}$  of 2.25V (Nominal  $V_{CCINT} - 10\%$ ). For every 50 mV reduction in  $V_{CCINT}$  below 2.375V (nominal  $V_{CCINT} - 5\%$ ), all delay parameters increase by 3%.

3. Minimum and maximum values for  $V_{CCO}$  vary according to the I/O standard selected.

4. Input and output measurement threshold is ~50% of V<sub>CCO</sub>. See "Delay Measurement Methodology," page 60 for specific levels.

5. Supply voltages may be applied in any order desired.

## **DC Characteristics Over Operating Conditions**

| Symbol             | Descripti                                                                      | Min                                                         | Тур                         | Max | Units |      |    |

|--------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------|-----|-------|------|----|

| V <sub>DRINT</sub> | Data Retention V <sub>CCINT</sub> voltage (below<br>may be lost)               | 2.0                                                         | -                           | -   | V     |      |    |

| V <sub>DRIO</sub>  | Data Retention V <sub>CCO</sub> voltage (below be lost)                        | ntion $V_{CCO}$ voltage (below which configuration data may |                             |     |       |      | V  |

| ICCINTQ            | Quiescent V <sub>CCINT</sub> supply current <sup>(1)</sup>                     | XC2S15                                                      | Commercial                  | -   | 10    | 30   | mA |

|                    |                                                                                |                                                             | Industrial                  | -   | 10    | 60   | mA |

|                    |                                                                                | XC2S30                                                      | Commercial                  | -   | 10    | 30   | mA |

|                    |                                                                                |                                                             | Industrial                  | -   | 10    | 60   | mA |

|                    |                                                                                | XC2S50                                                      | Commercial                  | -   | 12    | 50   | mA |

|                    |                                                                                |                                                             | Industrial                  | -   | 12    | 100  | mA |

|                    |                                                                                | XC2S100                                                     | Commercial                  | -   | 12    | 50   | mA |

|                    |                                                                                |                                                             | Industrial                  | -   | 12    | 100  | mA |

|                    |                                                                                | XC2S150                                                     | Commercial                  | -   | 15    | 50   | mA |

|                    |                                                                                |                                                             | Industrial                  | -   | 15    | 100  | mA |

|                    |                                                                                | XC2S200                                                     | Commercial                  | -   | 15    | 75   | mA |

|                    |                                                                                |                                                             | Industrial                  | -   | 15    | 150  | mA |

| ICCOQ              | Quiescent V <sub>CCO</sub> supply current <sup>(1)</sup>                       | 4                                                           |                             | -   | -     | 2    | mA |

| I <sub>REF</sub>   | V <sub>REF</sub> current per V <sub>REF</sub> pin                              |                                                             |                             | -   | -     | 20   | μA |

| ١L                 | Input or output leakage current <sup>(2)</sup>                                 |                                                             |                             | -10 | -     | +10  | μA |

| C <sub>IN</sub>    | Input capacitance (sample tested)                                              | VQ, CS, TQ, PQ, FG<br>packages                              |                             | -   | -     | 8    | pF |

| I <sub>RPU</sub>   | Pad pull-up (when selected) @ V <sub>IN</sub> = (sample tested) <sup>(3)</sup> | 3.3V                                                        | -                           | -   | 0.25  | mA   |    |

| I <sub>RPD</sub>   | Pad pull-down (when selected) @ V                                              | <sub>N</sub> = 3.6V (sar                                    | mple tested) <sup>(3)</sup> | -   | -     | 0.15 | mA |

#### Notes:

1. With no output current loads, no active input pull-up resistors, all I/O pins 3-stated and floating.

2. The I/O leakage current specification applies only when the V<sub>CCINT</sub> and V<sub>CCO</sub> supply voltages have reached their respective minimum Recommended Operating Conditions.

3. Internal pull-up and pull-down resistors guarantee valid logic levels at unconnected input pins. These pull-up and pull-down resistors do not provide valid logic levels when input pins are connected to other circuits.

# IOB Input Delay Adjustments for Different Standards<sup>(1)</sup>

Input delays associated with the pad are specified for LVTTL. For other standards, adjust the delays by the values shown. A delay adjusted in this way constitutes a worst-case limit.

|                       |                                    |                   | Speed | Speed Grade |       |

|-----------------------|------------------------------------|-------------------|-------|-------------|-------|

| Symbol                | Description                        | Standard          | -6    | -5          | Units |

| Data Input            | Delay Adjustments                  |                   |       | ·           |       |

| T <sub>ILVTTL</sub>   | Standard-specific data input delay | LVTTL             | 0     | 0           | ns    |

| T <sub>ILVCMOS2</sub> | adjustments                        | LVCMOS2           | -0.04 | -0.05       | ns    |

| T <sub>IPCI33_3</sub> | -                                  | PCI, 33 MHz, 3.3V | -0.11 | -0.13       | ns    |

| T <sub>IPCI33_5</sub> | -                                  | PCI, 33 MHz, 5.0V | 0.26  | 0.30        | ns    |

| T <sub>IPCI66_3</sub> | -                                  | PCI, 66 MHz, 3.3V | -0.11 | -0.13       | ns    |

| T <sub>IGTL</sub>     | -                                  | GTL               | 0.20  | 0.24        | ns    |

| T <sub>IGTLP</sub>    | -                                  | GTL+              | 0.11  | 0.13        | ns    |

| T <sub>IHSTL</sub>    | -                                  | HSTL              | 0.03  | 0.04        | ns    |

| T <sub>ISSTL2</sub>   | -                                  | SSTL2             | -0.08 | -0.09       | ns    |

| T <sub>ISSTL3</sub>   | -                                  | SSTL3             | -0.04 | -0.05       | ns    |

| T <sub>ICTT</sub>     |                                    | CTT               | 0.02  | 0.02        | ns    |

| T <sub>IAGP</sub>     | ]                                  | AGP               | -0.06 | -0.07       | ns    |

Notes:

1. Input timing for LVTTL is measured at 1.4V. For other I/O standards, see the table "Delay Measurement Methodology," page 60.

## IOB Output Delay Adjustments for Different Standards<sup>(1)</sup>

Output delays terminating at a pad are specified for LVTTL with 12 mA drive and fast slew rate. For other standards, adjust the delays by the values shown. A delay adjusted in this way constitutes a worst-case limit.

|                         |                                                                    |                   | Speed | d Grade |       |

|-------------------------|--------------------------------------------------------------------|-------------------|-------|---------|-------|

| Symbol                  | Description                                                        | Standard          | -6    | -5      | Units |

| Output Delay Adj        | ustments (Adj)                                                     |                   |       |         |       |

| T <sub>OLVTTL_S2</sub>  | Standard-specific adjustments for                                  | LVTTL, Slow, 2 mA | 14.2  | 16.9    | ns    |

| T <sub>OLVTTL_S4</sub>  | output delays terminating at pads<br>(based on standard capacitive | 4 mA              | 7.2   | 8.6     | ns    |

| T <sub>OLVTTL_S6</sub>  | load, C <sub>SI</sub> )                                            | 6 mA              | 4.7   | 5.5     | ns    |

| T <sub>OLVTTL_S8</sub>  |                                                                    | 8 mA              | 2.9   | 3.5     | ns    |

| T <sub>OLVTTL_S12</sub> |                                                                    | 12 mA             | 1.9   | 2.2     | ns    |

| T <sub>OLVTTL_S16</sub> |                                                                    | 16 mA             | 1.7   | 2.0     | ns    |

| T <sub>OLVTTL_S24</sub> |                                                                    | 24 mA             | 1.3   | 1.5     | ns    |

| T <sub>OLVTTL_F2</sub>  |                                                                    | LVTTL, Fast, 2 mA | 12.6  | 15.0    | ns    |

| T <sub>OLVTTL_F4</sub>  |                                                                    | 4 mA              | 5.1   | 6.1     | ns    |

| T <sub>OLVTTL_F6</sub>  |                                                                    | 6 mA              | 3.0   | 3.6     | ns    |

| T <sub>OLVTTL_F8</sub>  |                                                                    | 8 mA              | 1.0   | 1.2     | ns    |

| T <sub>OLVTTL_F12</sub> |                                                                    | 12 mA             | 0     | 0       | ns    |

| T <sub>OLVTTL_F16</sub> |                                                                    | 16 mA             | -0.1  | -0.1    | ns    |

| T <sub>OLVTTL_F24</sub> |                                                                    | 24 mA             | -0.1  | -0.2    | ns    |

| T <sub>OLVCMOS2</sub>   |                                                                    | LVCMOS2           | 0.2   | 0.2     | ns    |

| T <sub>OPCI33_3</sub>   |                                                                    | PCI, 33 MHz, 3.3V | 2.4   | 2.9     | ns    |

| T <sub>OPCI33_5</sub>   |                                                                    | PCI, 33 MHz, 5.0V | 2.9   | 3.5     | ns    |

| T <sub>OPCI66_3</sub>   |                                                                    | PCI, 66 MHz, 3.3V | -0.3  | -0.4    | ns    |

| T <sub>OGTL</sub>       |                                                                    | GTL               | 0.6   | 0.7     | ns    |

| T <sub>OGTLP</sub>      |                                                                    | GTL+              | 0.9   | 1.1     | ns    |

| T <sub>OHSTL_I</sub>    |                                                                    | HSTL I            | -0.4  | -0.5    | ns    |

| T <sub>OHSTL_III</sub>  |                                                                    | HSTL III          | -0.8  | -1.0    | ns    |

| T <sub>OHSTL_IV</sub>   |                                                                    | HSTL IV           | -0.9  | -1.1    | ns    |

| T <sub>OSSTL2_I</sub>   | —                                                                  | SSTL2 I           | -0.4  | -0.5    | ns    |

| T <sub>OSSLT2_II</sub>  |                                                                    | SSTL2 II          | -0.8  | -1.0    | ns    |

| T <sub>OSSTL3_I</sub>   | -                                                                  | SSTL3 I           | -0.4  | -0.5    | ns    |

| T <sub>OSSTL3_II</sub>  |                                                                    | SSTL3 II          | -0.9  | -1.1    | ns    |

| T <sub>OCTT</sub>       |                                                                    | CTT               | -0.5  | -0.6    | ns    |

| T <sub>OAGP</sub>       |                                                                    | AGP               | -0.8  | -1.0    | ns    |

Notes:

1. Output timing is measured at 1.4V with 35 pF external capacitive load for LVTTL. For other I/O standards and different loads, see the tables "Constants for Calculating TIOOP" and "Delay Measurement Methodology," page 60.

## **DLL Timing Parameters**

All devices are 100 percent functionally tested. Because of the difficulty in directly measuring many internal timing parameters, those parameters are derived from benchmark timing patterns. The following guidelines reflect worst-case values across the recommended operating conditions.

|                      |                                    |     | ·6  | -   | =   |       |

|----------------------|------------------------------------|-----|-----|-----|-----|-------|

| Symbol               | Description                        | Min | Max | Min | Max | Units |

| F <sub>CLKINHF</sub> | Input clock frequency (CLKDLLHF)   | 60  | 200 | 60  | 180 | MHz   |

| F <sub>CLKINLF</sub> | Input clock frequency (CLKDLL)     | 25  | 100 | 25  | 90  | MHz   |

| T <sub>DLLPWHF</sub> | Input clock pulse width (CLKDLLHF) | 2.0 | -   | 2.4 | -   | ns    |

| T <sub>DLLPWLF</sub> | Input clock pulse width (CLKDLL)   | 2.5 | -   | 3.0 | -   | ns    |

## **DLL Clock Tolerance, Jitter, and Phase Information**

All DLL output jitter and phase specifications were determined through statistical measurement at the package pins using a clock mirror configuration and matched drivers.

Figure 52, page 63, provides definitions for various parameters in the table below.

|                     |                                                                |                               | CLKE | DLLHF | CLKDLL |      |       |

|---------------------|----------------------------------------------------------------|-------------------------------|------|-------|--------|------|-------|

| Symbol              | Description                                                    | F <sub>CLKIN</sub>            | Min  | Max   | Min    | Max  | Units |

| T <sub>IPTOL</sub>  | Input clock period tolerance                                   |                               | -    | 1.0   | -      | 1.0  | ns    |

| T <sub>IJITCC</sub> | Input clock jitter tolerance (cycle-to-cycle)                  |                               | -    | ±150  | -      | ±300 | ps    |

| TLOCK               | Time required for DLL to acquire lock                          | > 60 MHz                      | -    | 20    | -      | 20   | μs    |

|                     |                                                                | 50-60 MHz                     | -    | -     | -      | 25   | μs    |

|                     |                                                                | 40-50 MHz                     | -    | -     | -      | 50   | μs    |

|                     |                                                                | 30-40 MHz                     | -    | -     | -      | 90   | μs    |

|                     |                                                                | 25-30 MHz                     | -    | -     | -      | 120  | μs    |

| T <sub>OJITCC</sub> | Output jitter (cycle-to-cycle) for any DLL clock c             | output <sup>(1)</sup>         | -    | ±60   | -      | ±60  | ps    |

| T <sub>PHIO</sub>   | Phase offset between CLKIN and CLKO <sup>(2)</sup>             |                               | -    | ±100  | -      | ±100 | ps    |

| T <sub>PHOO</sub>   | Phase offset between clock outputs on the DLL <sup>(3)</sup>   |                               | -    | ±140  | -      | ±140 | ps    |

| T <sub>PHIOM</sub>  | Maximum phase difference between CLKIN and CLKO <sup>(4)</sup> |                               | -    | ±160  | -      | ±160 | ps    |

| T <sub>PHOOM</sub>  | Maximum phase difference between clock outp                    | uts on the DLL <sup>(5)</sup> | -    | ±200  | -      | ±200 | ps    |

Notes:

1. **Output Jitter** is cycle-to-cycle jitter measured on the DLL output clock, *excluding* input clock jitter.

2. Phase Offset between CLKIN and CLKO is the worst-case fixed time difference between rising edges of CLKIN and CLKO, *excluding* output jitter and input clock jitter.

3. Phase Offset between Clock Outputs on the DLL is the worst-case fixed time difference between rising edges of any two DLL outputs, *excluding* Output Jitter and input clock jitter.

4. Maximum Phase Difference between CLKIN an CLKO is the sum of Output Jitter and Phase Offset between CLKIN and CLKO, or the greatest difference between CLKIN and CLKO rising edges due to DLL alone (*excluding* input clock jitter).

5. **Maximum Phase Difference between Clock Outputs on the DLL** is the sum of Output JItter and Phase Offset between any DLL clock outputs, or the greatest difference between any two DLL output rising edges due to DLL alone (*excluding* input clock jitter).

| XC2S100<br>Name       |      |       |       |                             |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | FG456                       | Scan  |

| V <sub>CCINT</sub>    | -    | -     | P38   | $V_{CCINT}^{*}$             | V <sub>CCINT</sub> *        | -     |

| V <sub>CCO</sub>      | 6    | -     | P39   | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -     |

| GND                   | -    | P119  | P40   | GND*                        | GND*                        | -     |

| I/O                   | 6    | P118  | P41   | K4                          | T1                          | 314   |

| I/O, V <sub>REF</sub> | 6    | P117  | P42   | M1                          | R4                          | 317   |

| I/O                   | 6    | -     | -     | -                           | T2                          | 320   |

| I/O                   | 6    | P116  | P43   | L4                          | U1                          | 323   |

| I/O                   | 6    | -     | -     | M2                          | R5                          | 326   |

| I/O                   | 6    | -     | P44   | L3                          | U2                          | 332   |

| I/O, V <sub>REF</sub> | 6    | P115  | P45   | N1                          | Т3                          | 335   |

| V <sub>CCO</sub>      | 6    | -     | -     | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -     |

| GND                   | -    | -     | -     | GND*                        | GND*                        | -     |

| I/O                   | 6    | -     | P46   | P1                          | T4                          | 338   |

| I/O                   | 6    | -     | -     | L5                          | W1                          | 341   |

| I/O                   | 6    | -     | -     | -                           | U4                          | 344   |

| I/O                   | 6    | P114  | P47   | N2                          | Y1                          | 347   |

| I/O                   | 6    | -     | -     | M4                          | W2                          | 350   |

| I/O                   | 6    | P113  | P48   | R1                          | Y2                          | 356   |

| I/O                   | 6    | P112  | P49   | М3                          | W3                          | 359   |

| M1                    | -    | P111  | P50   | P2                          | U5                          | 362   |

| GND                   | -    | P110  | P51   | GND*                        | GND*                        | -     |

| MO                    | -    | P109  | P52   | N3                          | AB2                         | 363   |

| V <sub>CCO</sub>      | 6    | P108  | P53   | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -     |

| V <sub>CCO</sub>      | 5    | P107  | P53   | V <sub>CCO</sub><br>Bank 5* | V <sub>CCO</sub><br>Bank 5* | -     |

| M2                    | -    | P106  | P54   | R3                          | Y4                          | 364   |

| I/O                   | 5    | -     | -     | N5                          | V7                          | 374   |

| I/O                   | 5    | P103  | P57   | T2                          | Y6                          | 377   |

| I/O                   | 5    | -     | -     | -                           | AA4                         | 380   |

| I/O                   | 5    | -     | -     | P5                          | W6                          | 383   |

| I/O                   | 5    | -     | P58   | Т3                          | Y7                          | 386   |

| GND                   | -    | -     | -     | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 5    | -     | -     | V <sub>CCO</sub><br>Bank 5* | V <sub>CCO</sub><br>Bank 5* | -     |

| I/O, V <sub>REF</sub> | 5    | P102  | P59   | T4                          | AA5                         | 389   |

| I/O                   | 5    | -     | P60   | M6                          | AB5                         | 392   |

| I/O                   | 5    | -     | -     | T5                          | AB6                         | 398   |

| I/O                   | 5    | P101  | P61   | N6                          | AA7                         | 401   |

| I/O                   | 5    | -     | -     | -                           | W7                          | 404   |

## XC2S100 Device Pinouts (Continued)

| XC2S100<br>Name       |      |       |       |                             |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | FG456                       | Scan  |

| I/O, V <sub>REF</sub> | 5    | P100  | P62   | R5                          | W8                          | 407   |

| I/O                   | 5    | P99   | P63   | P6                          | Y8                          | 410   |

| GND                   | -    | P98   | P64   | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 5    | -     | P65   | V <sub>CCO</sub><br>Bank 5* | V <sub>CCO</sub><br>Bank 5* | -     |

| V <sub>CCINT</sub>    | -    | P97   | P66   | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| I/O                   | 5    | P96   | P67   | R6                          | AA8                         | 413   |

| I/O                   | 5    | P95   | P68   | M7                          | V9                          | 416   |

| I/O                   | 5    | -     | -     | -                           | AB9                         | 419   |

| I/O                   | 5    | -     | P69   | N7                          | Y9                          | 422   |

| I/O                   | 5    | -     | P70   | T6                          | W10                         | 428   |

| I/O                   | 5    | -     | P71   | P7                          | AB10                        | 431   |

| GND                   | -    | -     | P72   | GND*                        | GND*                        | -     |

| I/O, V <sub>REF</sub> | 5    | P94   | P73   | P8                          | Y10                         | 434   |

| I/O                   | 5    | -     | P74   | R7                          | V11                         | 437   |

| I/O                   | 5    | -     | -     | T7                          | W11                         | 440   |

| I/O                   | 5    | P93   | P75   | Т8                          | AB11                        | 443   |

| V <sub>CCINT</sub>    | -    | P92   | P76   | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| I, GCK1               | 5    | P91   | P77   | R8                          | Y11                         | 455   |

| V <sub>CCO</sub>      | 5    | P90   | P78   | V <sub>CCO</sub><br>Bank 5* | V <sub>CCO</sub><br>Bank 5* | -     |

| V <sub>CCO</sub>      | 4    | P90   | P78   | V <sub>CCO</sub><br>Bank 4* | V <sub>CCO</sub><br>Bank 4* | -     |

| GND                   | -    | P89   | P79   | GND*                        | GND*                        | -     |

| I, GCK0               | 4    | P88   | P80   | N8                          | W12                         | 456   |

| I/O                   | 4    | P87   | P81   | N9                          | U12                         | 460   |

| I/O                   | 4    | P86   | P82   | R9                          | Y12                         | 466   |

| I/O                   | 4    | -     | -     | N10                         | AA12                        | 469   |

| I/O                   | 4    | -     | P83   | Т9                          | AB13                        | 472   |

| I/O, V <sub>REF</sub> | 4    | P85   | P84   | P9                          | AA13                        | 475   |

| GND                   | -    | -     | P85   | GND*                        | GND*                        | -     |

| I/O                   | 4    | -     | P86   | M10                         | Y13                         | 478   |

| I/O                   | 4    | -     | P87   | R10                         | V13                         | 481   |

| I/O                   | 4    | -     | P88   | P10                         | AA14                        | 487   |

| I/O                   | 4    | -     | -     | -                           | V14                         | 490   |

| I/O                   | 4    | P84   | P89   | T10                         | AB15                        | 493   |

| I/O                   | 4    | P83   | P90   | R11                         | AA15                        | 496   |

| V <sub>CCINT</sub>    | -    | P82   | P91   | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| V <sub>CCO</sub>      | 4    | -     | P92   | V <sub>CCO</sub><br>Bank 4* | V <sub>CCO</sub><br>Bank 4* | -     |

| GND                   | -    | P81   | P93   | GND*                        | GND*                        | -     |

| I/O                   | 4    | P80   | P94   | M11                         | Y15                         | 499   |

|                       | XC2S100 Pad<br>Name |       |       |                             |                             | Bndry |

|-----------------------|---------------------|-------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank                | TQ144 | PQ208 | FG256                       | FG456                       | Scan  |

| I/O, V <sub>REF</sub> | 4                   | P79   | P95   | T11                         | AB16                        | 502   |

| I/O                   | 4                   | -     | -     | -                           | AB17                        | 505   |

| I/O                   | 4                   | P78   | P96   | N11                         | V15                         | 508   |

| I/O                   | 4                   | -     | -     | R12                         | Y16                         | 511   |

| I/O                   | 4                   | -     | P97   | P11                         | AB18                        | 517   |

| I/O, V <sub>REF</sub> | 4                   | P77   | P98   | T12                         | AB19                        | 520   |

| V <sub>CCO</sub>      | 4                   | -     | -     | V <sub>CCO</sub><br>Bank 4* | V <sub>CCO</sub><br>Bank 4* | -     |

| GND                   | -                   | -     | -     | GND*                        | GND*                        | -     |

| I/O                   | 4                   | -     | P99   | T13                         | Y17                         | 523   |

| I/O                   | 4                   | -     | -     | N12                         | V16                         | 526   |

| I/O                   | 4                   | -     | -     | -                           | W17                         | 529   |

| I/O                   | 4                   | P76   | P100  | R13                         | AB20                        | 532   |

| I/O                   | 4                   | -     | -     | P12                         | AA19                        | 535   |

| I/O                   | 4                   | P75   | P101  | P13                         | AA20                        | 541   |

| I/O                   | 4                   | P74   | P102  | T14                         | W18                         | 544   |

| GND                   | -                   | P73   | P103  | GND*                        | GND*                        | -     |

| DONE                  | 3                   | P72   | P104  | R14                         | Y19                         | 547   |

| V <sub>CCO</sub>      | 4                   | P71   | P105  | V <sub>CCO</sub><br>Bank 4* | V <sub>CCO</sub><br>Bank 4* | -     |

| V <sub>CCO</sub>      | 3                   | P70   | P105  | V <sub>CCO</sub><br>Bank 3* | V <sub>CCO</sub><br>Bank 3* | -     |

| PROGRAM               | -                   | P69   | P106  | P15                         | W20                         | 550   |

| I/O (INIT)            | 3                   | P68   | P107  | N15                         | V19                         | 551   |

| I/O (D7)              | 3                   | P67   | P108  | N14                         | Y21                         | 554   |

| I/O                   | 3                   | -     | -     | T15                         | W21                         | 560   |

| I/O                   | 3                   | P66   | P109  | M13                         | U20                         | 563   |

| I/O                   | 3                   | -     | -     | -                           | U19                         | 566   |

| I/O                   | 3                   | -     | -     | R16                         | T18                         | 569   |

| I/O                   | 3                   | -     | P110  | M14                         | W22                         | 572   |

| GND                   | -                   | -     | -     | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 3                   | -     | -     | V <sub>CCO</sub><br>Bank 3* | V <sub>CCO</sub><br>Bank 3* | -     |

| I/O, V <sub>REF</sub> | 3                   | P65   | P111  | L14                         | U21                         | 575   |

| I/O                   | 3                   | -     | P112  | M15                         | T20                         | 578   |

| I/O                   | 3                   | -     | -     | L12                         | T21                         | 584   |

| I/O                   | 3                   | P64   | P113  | P16                         | R18                         | 587   |

| I/O                   | 3                   | -     | -     | -                           | U22                         | 590   |

| I/O, V <sub>REF</sub> | 3                   | P63   | P114  | L13                         | R19                         | 593   |

| I/O (D6)              | 3                   | P62   | P115  | N16                         | T22                         | 596   |

| GND                   | -                   | P61   | P116  | GND*                        | GND*                        | -     |

| XC2S100 Pad<br>Name      |      |       |       |                             |                             | Bndry |

|--------------------------|------|-------|-------|-----------------------------|-----------------------------|-------|

| Function                 | Bank | TQ144 | PQ208 | FG256                       | FG456                       | Scan  |

| V <sub>CCO</sub>         | 3    | -     | P117  | V <sub>CCO</sub><br>Bank 3* | V <sub>CCO</sub><br>Bank 3* | -     |

| V <sub>CCINT</sub>       | -    | -     | P118  | $V_{CCINT}^{}^{*}$          | $V_{CCINT}^{*}$             | -     |

| I/O (D5)                 | 3    | P60   | P119  | M16                         | R21                         | 599   |

| I/O                      | 3    | P59   | P120  | K14                         | P18                         | 602   |

| I/O                      | 3    | -     | -     | L16                         | P20                         | 605   |

| I/O                      | 3    | -     | P121  | K13                         | P21                         | 608   |

| I/O                      | 3    | -     | P122  | L15                         | N18                         | 614   |

| I/O                      | 3    | -     | P123  | K12                         | N20                         | 617   |

| GND                      | -    | -     | P124  | GND*                        | GND*                        | -     |

| I/O, V <sub>REF</sub>    | 3    | P58   | P125  | K16                         | N21                         | 620   |

| I/O (D4)                 | 3    | P57   | P126  | J16                         | N22                         | 623   |

| I/O                      | 3    | -     | -     | J14                         | M19                         | 626   |

| I/O                      | 3    | P56   | P127  | K15                         | M20                         | 629   |

| V <sub>CCINT</sub>       | -    | P55   | P128  | E5                          | $V_{CCINT}^{*}$             | -     |

| I/O, TRDY <sup>(1)</sup> | 3    | P54   | P129  | J15                         | M22                         | 638   |

| V <sub>CCO</sub>         | 3    | P53   | P130  | V <sub>CCO</sub><br>Bank 3* | V <sub>CCO</sub><br>Bank 3* | -     |

| V <sub>CCO</sub>         | 2    | P53   | P130  | V <sub>CCO</sub><br>Bank 2* | V <sub>CCO</sub><br>Bank 2* | -     |

| GND                      | -    | P52   | P131  | GND*                        | GND*                        | -     |

| I/O, IRDY <sup>(1)</sup> | 2    | P51   | P132  | H16                         | L20                         | 641   |

| I/O                      | 2    | -     | P133  | H14                         | L17                         | 644   |

| I/O                      | 2    | P50   | P134  | H15                         | L21                         | 650   |

| I/O                      | 2    | -     | -     | J13                         | L22                         | 653   |

| I/O (D3)                 | 2    | P49   | P135  | G16                         | K20                         | 656   |

| I/O, V <sub>REF</sub>    | 2    | P48   | P136  | H13                         | K21                         | 659   |

| GND                      | -    | -     | P137  | GND*                        | GND*                        | -     |

| I/O                      | 2    | -     | P138  | G14                         | K22                         | 662   |

| I/O                      | 2    | -     | P139  | G15                         | J21                         | 665   |

| I/O                      | 2    | -     | P140  | G12                         | J18                         | 671   |

| I/O                      | 2    | -     | -     | F16                         | J22                         | 674   |

| I/O                      | 2    | P47   | P141  | G13                         | H19                         | 677   |

| I/O (D2)                 | 2    | P46   | P142  | F15                         | H20                         | 680   |

| V <sub>CCINT</sub>       | -    | -     | P143  | $V_{CCINT}^{*}$             | $V_{CCINT}^{*}$             | -     |

| V <sub>CCO</sub>         | 2    | -     | P144  | V <sub>CCO</sub><br>Bank 2* | V <sub>CCO</sub><br>Bank 2* | -     |

| GND                      | -    | P45   | P145  | GND*                        | GND*                        | -     |

| I/O (D1)                 | 2    | P44   | P146  | E16                         | H22                         | 683   |

| I/O, V <sub>REF</sub>    | 2    | P43   | P147  | F14                         | H18                         | 686   |

| I/O                      | 2    | -     | -     | -                           | G21                         | 689   |

| I/O                      | 2    | P42   | P148  | D16                         | G18                         | 692   |

| XC2S100<br>Name       |      |       |       |                             |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | FG456                       | Scan  |

| I/O                   | 2    | -     | -     | F12                         | G20                         | 695   |

| I/O                   | 2    | -     | P149  | E15                         | F19                         | 701   |

| I/O, V <sub>REF</sub> | 2    | P41   | P150  | F13                         | F21                         | 704   |

| V <sub>CCO</sub>      | 2    | -     | -     | V <sub>CCO</sub><br>Bank 2* | V <sub>CCO</sub><br>Bank 2* | -     |

| GND                   | -    | -     | -     | GND*                        | GND*                        | -     |

| I/O                   | 2    | -     | P151  | E14                         | F20                         | 707   |

| I/O                   | 2    | -     | -     | C16                         | F18                         | 710   |

| I/O                   | 2    | -     | -     | -                           | E21                         | 713   |

| I/O                   | 2    | P40   | P152  | E13                         | D22                         | 716   |

| I/O                   | 2    | -     | -     | B16                         | E20                         | 719   |

| I/O (DIN,<br>D0)      | 2    | P39   | P153  | D14                         | D20                         | 725   |

| I/O (DOUT,<br>BUSY)   | 2    | P38   | P154  | C15                         | C21                         | 728   |

| CCLK                  | 2    | P37   | P155  | D15                         | B22                         | 731   |

| V <sub>CCO</sub>      | 2    | P36   | P156  | V <sub>CCO</sub><br>Bank 2* | V <sub>CCO</sub><br>Bank 2* | -     |

| V <sub>CCO</sub>      | 1    | P35   | P156  | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| TDO                   | 2    | P34   | P157  | B14                         | A21                         | -     |

| GND                   | -    | P33   | P158  | GND*                        | GND*                        | -     |

| TDI                   | -    | P32   | P159  | A15                         | B20                         | -     |

| I/O (CS)              | 1    | P31   | P160  | B13                         | C19                         | 0     |

| I/O (WRITE)           | 1    | P30   | P161  | C13                         | A20                         | 3     |

| I/O                   | 1    | -     | -     | C12                         | D17                         | 9     |

| I/O                   | 1    | P29   | P162  | A14                         | A19                         | 12    |

| I/O                   | 1    | -     | -     | -                           | B18                         | 15    |

| I/O                   | 1    | -     | -     | D12                         | C17                         | 18    |

| I/O                   | 1    | -     | P163  | B12                         | D16                         | 21    |

| GND                   | -    | -     | -     | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 1    | -     | -     | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| I/O, V <sub>REF</sub> | 1    | P28   | P164  | C11                         | A18                         | 24    |

| I/O                   | 1    | -     | P165  | A13                         | B17                         | 27    |

| I/O                   | 1    | -     | -     | D11                         | D15                         | 33    |

| I/O                   | 1    | -     | P166  | A12                         | C16                         | 36    |

| I/O                   | 1    | -     | -     | -                           | D14                         | 39    |

| I/O, V <sub>REF</sub> | 1    | P27   | P167  | E11                         | E14                         | 42    |

| I/O                   | 1    | P26   | P168  | B11                         | A16                         | 45    |

| GND                   | -    | P25   | P169  | GND*                        | GND*                        | -     |

## XC2S100 Device Pinouts (Continued)

| XC2S100<br>Name       | Pad  |       |       |                             |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | FG456                       | Scan  |

| V <sub>CCO</sub>      | 1    | -     | P170  | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| V <sub>CCINT</sub>    | -    | P24   | P171  | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| I/O                   | 1    | P23   | P172  | A11                         | C15                         | 48    |

| I/O                   | 1    | P22   | P173  | C10                         | B15                         | 51    |

| I/O                   | 1    | -     | -     | -                           | F12                         | 54    |

| I/O                   | 1    | -     | P174  | B10                         | C14                         | 57    |

| I/O                   | 1    | -     | P175  | D10                         | D13                         | 63    |

| I/O                   | 1    | -     | P176  | A10                         | C13                         | 66    |

| GND                   | -    | -     | P177  | GND*                        | GND*                        | -     |

| I/O, V <sub>REF</sub> | 1    | P21   | P178  | B9                          | B13                         | 69    |

| I/O                   | 1    | -     | P179  | E10                         | E12                         | 72    |

| I/O                   | 1    | -     | -     | A9                          | B12                         | 75    |

| I/O                   | 1    | P20   | P180  | D9                          | D12                         | 78    |

| I/O                   | 1    | P19   | P181  | A8                          | D11                         | 84    |

| I, GCK2               | 1    | P18   | P182  | C9                          | A11                         | 90    |

| GND                   | -    | P17   | P183  | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 1    | P16   | P184  | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| V <sub>CCO</sub>      | 0    | P16   | P184  | V <sub>CCO</sub><br>Bank 0* | V <sub>CCO</sub><br>Bank 0* | -     |

| I, GCK3               | 0    | P15   | P185  | B8                          | C11                         | 91    |

| V <sub>CCINT</sub>    | -    | P14   | P186  | V <sub>CCINT</sub> *        | $V_{CCINT}^{*}$             | -     |

| I/O                   | 0    | P13   | P187  | A7                          | A10                         | 101   |

| I/O                   | 0    | -     | -     | D8                          | B10                         | 104   |

| XC2S100 Pad<br>Name   |      |       |       |                             |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | FG456                       | Scan  |

| I/O                   | 0    | -     | P188  | A6                          | C10                         | 107   |

| I/O, V <sub>REF</sub> | 0    | P12   | P189  | B7                          | A9                          | 110   |

| GND                   | -    | -     | P190  | GND*                        | GND*                        | -     |

| I/O                   | 0    | -     | P191  | C8                          | B9                          | 113   |

| I/O                   | 0    | -     | P192  | D7                          | E10                         | 116   |

| I/O                   | 0    | -     | P193  | E7                          | A8                          | 122   |

| I/O                   | 0    | -     | -     | -                           | D9                          | 125   |

| I/O                   | 0    | P11   | P194  | C7                          | E9                          | 128   |

| I/O                   | 0    | P10   | P195  | B6                          | A7                          | 131   |

| V <sub>CCINT</sub>    | -    | P9    | P196  | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| V <sub>CCO</sub>      | 0    | -     | P197  | V <sub>CCO</sub><br>Bank 0* | V <sub>CCO</sub><br>Bank 0* | -     |

| GND                   | -    | P8    | P198  | GND*                        | GND*                        | -     |

| I/O                   | 0    | P7    | P199  | A5                          | B7                          | 134   |

| I/O, V <sub>REF</sub> | 0    | P6    | P200  | C6                          | E8                          | 137   |

| I/O                   | 0    | -     | -     | -                           | D8                          | 140   |

| I/O                   | 0    | -     | P201  | B5                          | C7                          | 143   |

| I/O                   | 0    | -     | -     | D6                          | D7                          | 146   |