Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Active                                                       |

| Number of LABs/CLBs            | 1176                                                         |

| Number of Logic Elements/Cells | 5292                                                         |

| Total RAM Bits                 | 57344                                                        |

| Number of I/O                  | 284                                                          |

| Number of Gates                | 200000                                                       |

| Voltage - Supply               | 2.375V ~ 2.625V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 456-BBGA                                                     |

| Supplier Device Package        | 456-FBGA (23x23)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xillinx/xc2s200-6fg456c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Spartan-II Product Availability**

Table 2 shows the maximum user I/Os available on the device and the number of user I/Os available for each device/package combination. The four global clock pins are usable as additional user I/Os when not used as a global clock pin. These pins are not included in user I/O counts.

Table 2: Spartan-II FPGA User I/O Chart(1)

|         |                     | Available User I/O According to Package Type |                 |                 |                 |                 |                 |  |

|---------|---------------------|----------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|--|

| Device  | Maximum<br>User I/O | VQ100<br>VQG100                              | TQ144<br>TQG144 | CS144<br>CSG144 | PQ208<br>PQG208 | FG256<br>FGG256 | FG456<br>FGG456 |  |

| XC2S15  | 86                  | 60                                           | 86              | (Note 2)        | -               | -               | -               |  |

| XC2S30  | 92                  | 60                                           | 92              | 92              | (Note 2)        | -               | -               |  |

| XC2S50  | 176                 | -                                            | 92              | -               | 140             | 176             | -               |  |

| XC2S100 | 176                 | -                                            | 92              | -               | 140             | 176             | (Note 2)        |  |

| XC2S150 | 260                 | -                                            | -               | -               | 140             | 176             | 260             |  |

| XC2S200 | 284                 | -                                            | -               | -               | 140             | 176             | 284             |  |

#### Notes:

- 1. All user I/O counts do not include the four global clock/user input pins.

- 2. Discontinued by PDN2004-01.

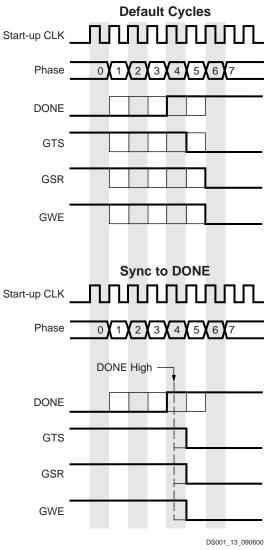

By default, these operations are synchronized to CCLK. The entire start-up sequence lasts eight cycles, called C0-C7, after which the loaded design is fully functional. The default timing for start-up is shown in the top half of Figure 13. The four operations can be selected to switch on any CCLK cycle C1-C6 through settings in the Xilinx software. Heavy lines show default settings.

Figure 13: Start-Up Waveforms

The bottom half of Figure 13 shows another commonly used version of the start-up timing known as Sync-to-DONE. This version makes the GTS, GSR, and GWE events conditional upon the DONE pin going High. This timing is important for a daisy chain of multiple FPGAs in serial mode, since it ensures that all FPGAs go through start-up together, after all their DONE pins have gone High.

Sync-to-DONE timing is selected by setting the GTS, GSR, and GWE cycles to a value of DONE in the configuration options. This causes these signals to transition one clock cycle after DONE externally transitions High.

#### **Serial Modes**

There are two serial configuration modes: In Master Serial mode, the FPGA controls the configuration process by driving CCLK as an output. In Slave Serial mode, the FPGA passively receives CCLK as an input from an external agent (e.g., a microprocessor, CPLD, or second FPGA in master mode) that is controlling the configuration process. In both modes, the FPGA is configured by loading one bit per CCLK cycle. The MSB of each configuration data byte is always written to the DIN pin first.

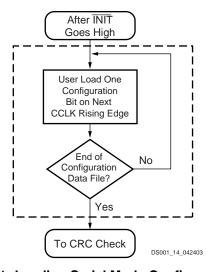

See Figure 14 for the sequence for loading data into the Spartan-II FPGA serially. This is an expansion of the "Load Configuration Data Frames" block in Figure 11. Note that  $\overline{\text{CS}}$  and  $\overline{\text{WRITE}}$  normally are not used during serial configuration. To ensure successful loading of the FPGA, do not toggle  $\overline{\text{WRITE}}$  with  $\overline{\text{CS}}$  Low during serial configuration.

Figure 14: Loading Serial Mode Configuration Data

DS001\_16\_032300

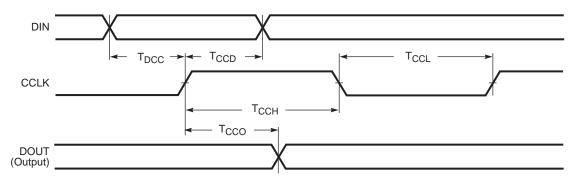

| Symbol           |      | Description       |    | Units    |

|------------------|------|-------------------|----|----------|

| T <sub>DCC</sub> |      | DIN setup         | 5  | ns, min  |

| T <sub>CCD</sub> |      | DIN hold          | 0  | ns, min  |

| T <sub>CCO</sub> | CCLK | DOUT              | 12 | ns, max  |

| T <sub>CCH</sub> | COLK | High time         | 5  | ns, min  |

| T <sub>CCL</sub> |      | Low time          | 5  | ns, min  |

| F <sub>CC</sub>  |      | Maximum frequency | 66 | MHz, max |

Figure 16: Slave Serial Mode Timing

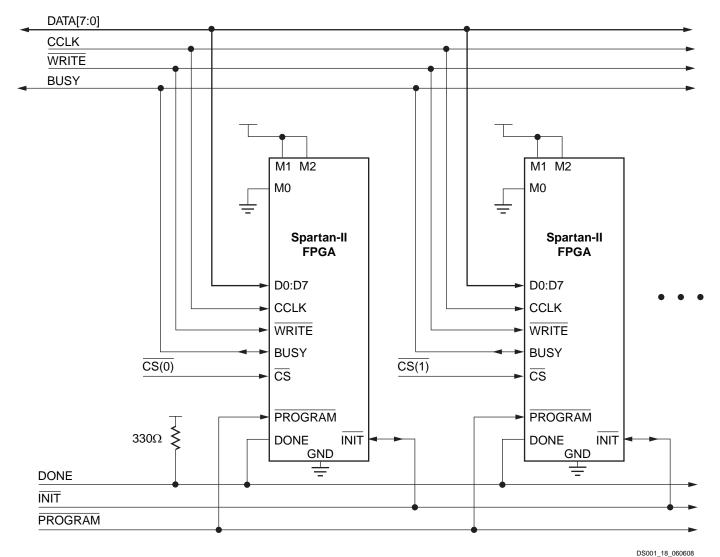

Figure 18: Slave Parallel Configuration Circuit Diagram

Multiple Spartan-II FPGAs can be configured using the Slave Parallel mode, and be made to start-up simultaneously. To configure multiple devices in this way, wire the individual CCLK, Data,  $\overline{WRITE}$ , and BUSY pins of all the devices in parallel. The individual devices are loaded separately by asserting the  $\overline{CS}$  pin of each device in turn and writing the appropriate data. Sync-to-DONE start-up timing is used to ensure that the start-up sequence does not begin until all the FPGAs have been loaded. See "Start-up," page 19.

## Write

When using the Slave Parallel Mode, write operations send packets of byte-wide configuration data into the FPGA. Figure 19, page 25 shows a flowchart of the write sequence used to load data into the Spartan-II FPGA. This is an expansion of the "Load Configuration Data Frames" block in Figure 11, page 18. The timing for write operations is shown in Figure 20, page 26.

For the present example, the user holds  $\overline{\text{WRITE}}$  and  $\overline{\text{CS}}$  Low throughout the sequence of write operations. Note that when  $\overline{\text{CS}}$  is asserted on successive CCLKs,  $\overline{\text{WRITE}}$  must remain either asserted or de-asserted. Otherwise an abort will be initiated, as in the next section.

- 1. Drive data onto D0-D7. Note that to avoid contention, the data source should not be enabled while  $\overline{CS}$  is Low and  $\overline{WRITE}$  is High. Similarly, while  $\overline{WRITE}$  is High, no more than one device's  $\overline{CS}$  should be asserted.

- On the rising edge of CCLK: If BUSY is Low, the data is accepted on this clock. If BUSY is High (from a previous write), the data is not accepted. Acceptance will instead occur on the first clock after BUSY goes Low, and the data must be held until this happens.

- 3. Repeat steps 1 and 2 until all the data has been sent.

- 4. De-assert CS and WRITE.

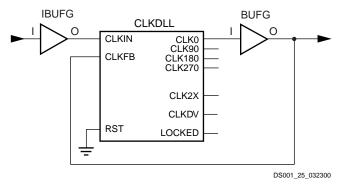

## **BUFGDLL Pin Descriptions**

Use the BUFGDLL macro as the simplest way to provide zero propagation delay for a high-fanout on-chip clock from an external input. This macro uses the IBUFG, CLKDLL and BUFG primitives to implement the most basic DLL application as shown in Figure 25.

Figure 25: BUFGDLL Block Diagram

This macro does not provide access to the advanced clock domain controls or to the clock multiplication or clock division features of the DLL. This macro also does not provide access to the RST or LOCKED pins of the DLL. For access to these features, a designer must use the DLL primitives described in the following sections.

## Source Clock Input — I

The I pin provides the user source clock, the clock signal on which the DLL operates, to the BUFGDLL. For the BUFGDLL macro the source clock frequency must fall in the low frequency range as specified in the data sheet. The BUFGDLL requires an external signal source clock. Therefore, only an external input port can source the signal that drives the BUFGDLL I pin.

#### Clock Output — O

The clock output pin O represents a delay-compensated version of the source clock (I) signal. This signal, sourced by a global clock buffer BUFG primitive, takes advantage of the dedicated global clock routing resources of the device.

The output clock has a 50/50 duty cycle unless you deactivate the duty cycle correction property.

## **CLKDLL Primitive Pin Descriptions**

The library CLKDLL primitives provide access to the complete set of DLL features needed when implementing more complex applications with the DLL.

### Source Clock Input — CLKIN

The CLKIN pin provides the user source clock (the clock signal on which the DLL operates) to the DLL. The CLKIN frequency must fall in the ranges specified in the data sheet. A global clock buffer (BUFG) driven from another CLKDLL

or one of the global clock input buffers (IBUFG) on the same edge of the device (top or bottom) must source this clock signal.

### Feedback Clock Input — CLKFB

The DLL requires a reference or feedback signal to provide the delay-compensated output. Connect only the CLK0 or CLK2X DLL outputs to the feedback clock input (CLKFB) pin to provide the necessary feedback to the DLL. Either a global clock buffer (BUFG) or one of the global clock input buffers (IBUFG) on the same edge of the device (top or bottom) must source this clock signal.

If an IBUFG sources the CLKFB pin, the following special rules apply.

- 1. An external input port must source the signal that drives the IBUFG I pin.

- The CLK2X output must feed back to the device if both the CLK0 and CLK2X outputs are driving off chip devices.

- That signal must directly drive only OBUFs and nothing else.

These rules enable the software to determine which DLL clock output sources the CLKFB pin.

### Reset Input — RST

When the reset pin RST activates, the LOCKED signal deactivates within four source clock cycles. The RST pin, active High, must either connect to a dynamic signal or be tied to ground. As the DLL delay taps reset to zero, glitches can occur on the DLL clock output pins. Activation of the RST pin can also severely affect the duty cycle of the clock output pins. Furthermore, the DLL output clocks no longer deskew with respect to one another. The DLL must be reset when the input clock frequency changes, if the device is reconfigured in Boundary-Scan mode, if the device undergoes a hot swap, and after the device is configured if the input clock is not stable during the startup sequence.

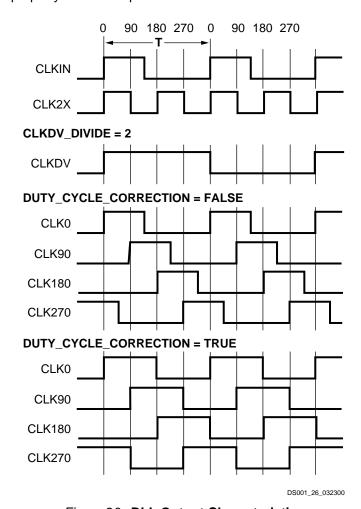

#### 2x Clock Output — CLK2X

The output pin CLK2X provides a frequency-doubled clock with an automatic 50/50 duty-cycle correction. Until the CLKDLL has achieved lock, the CLK2X output appears as a 1x version of the input clock with a 25/75 duty cycle. This behavior allows the DLL to lock on the correct edge with respect to source clock. This pin is not available on the CLKDLLHF primitive.

## Clock Divide Output — CLKDV

The clock divide output pin CLKDV provides a lower frequency version of the source clock. The CLKDV\_DIVIDE property controls CLKDV such that the source clock is divided by N where N is either 1.5, 2, 2.5, 3, 4, 5, 8, or 16.

This feature provides automatic duty cycle correction. The CLKDV output pin has a 50/50 duty cycle for all values of the

division factor N except for non-integer division in High Frequency (HF) mode. For division factor 1.5 the duty cycle in the HF mode is 33.3% High and 66.7% Low. For division factor 2.5, the duty cycle in the HF mode is 40.0% High and 60.0% Low.

## 1x Clock Outputs — CLK[0|90|180|270]

The 1x clock output pin CLK0 represents a delay-compensated version of the source clock (CLKIN) signal. The CLKDLL primitive provides three phase-shifted versions of the CLK0 signal while CLKDLLHF provides only the 180 degree phase-shifted version. The relationship between phase shift and the corresponding period shift appears in Table 10.

The timing diagrams in Figure 26 illustrate the DLL clock output characteristics.

Table 10: Relationship of Phase-Shifted Output Clock to Period Shift

| Phase (degrees) | Period Shift (percent) |

|-----------------|------------------------|

| 0               | 0%                     |

| 90              | 25%                    |

| 180             | 50%                    |

| 270             | 75%                    |

The DLL provides duty cycle correction on all 1x clock outputs such that all 1x clock outputs by default have a 50/50 duty cycle. The DUTY\_CYCLE\_CORRECTION property (TRUE by default), controls this feature. In order to deactivate the DLL duty cycle correction, attach the DUTY\_CYCLE\_CORRECTION=FALSE property to the DLL primitive. When duty cycle correction deactivates, the output clock has the same duty cycle as the source clock.

The DLL clock outputs can drive an OBUF, a BUFG, or they can route directly to destination clock pins. The DLL clock outputs can only drive the BUFGs that reside on the same edge (top or bottom).

### Locked Output — LOCKED

In order to achieve lock, the DLL may need to sample several thousand clock cycles. After the DLL achieves lock the LOCKED signal activates. The "DLL Timing Parameters" section of Module 3 provides estimates for locking times.

In order to guarantee that the system clock is established prior to the device "waking up," the DLL can delay the completion of the device configuration process until after the DLL locks. The STARTUP\_WAIT property activates this feature.

Until the LOCKED signal activates, the DLL output clocks are not valid and can exhibit glitches, spikes, or other

spurious movement. In particular the CLK2X output will appear as a 1x clock with a 25/75 duty cycle.

### **DLL Properties**

Properties provide access to some of the Spartan-II family DLL features, (for example, clock division and duty cycle correction).

### **Duty Cycle Correction Property**

The 1x clock outputs, CLK0, CLK90, CLK180, and CLK270, use the duty-cycle corrected default, such that they exhibit a 50/50 duty cycle. The DUTY\_CYCLE\_CORRECTION property (by default TRUE) controls this feature. To deactivate the DLL duty-cycle correction for the 1x clock outputs, attach the DUTY\_CYCLE\_CORRECTION=FALSE property to the DLL primitive.

Figure 26: DLL Output Characteristics

#### Clock Divide Property

The CLKDV\_DIVIDE property specifies how the signal on the CLKDV pin is frequency divided with respect to the CLK0 pin. The values allowed for this property are 1.5, 2, 2.5, 3, 4, 5, 8, or 16; the default value is 2.

### Startup Delay Property

This property, STARTUP\_WAIT, takes on a value of TRUE or FALSE (the default value). When TRUE the Startup Sequence following device configuration is paused at a user-specified point until the DLL locks. XAPP176: Configuration and Readback of the Spartan-II and Spartan-IIE Families explains how this can result in delaying the assertion of the DONE pin until the DLL locks.

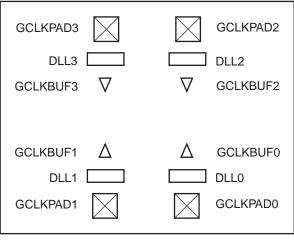

#### **DLL Location Constraints**

The DLLs are distributed such that there is one DLL in each corner of the device. The location constraint LOC, attached to the DLL primitive with the numeric identifier 0, 1, 2, or 3, controls DLL location. The orientation of the four DLLs and their corresponding clock resources appears in Figure 27.

The LOC property uses the following form.

LOC = DLL2

DS001\_27\_061308

Figure 27: Orientation of DLLs

## **Design Considerations**

Use the following design considerations to avoid pitfalls and improve success designing with Xilinx devices.

### Input Clock

The output clock signal of a DLL, essentially a delayed version of the input clock signal, reflects any instability on the input clock in the output waveform. For this reason the quality of the DLL input clock relates directly to the quality of the output clock waveforms generated by the DLL. The DLL input clock requirements are specified in the "DLL Timing Parameters" section of the data sheet.

In most systems a crystal oscillator generates the system clock. The DLL can be used with any commercially available quartz crystal oscillator. For example, most crystal oscillators produce an output waveform with a frequency tolerance of 100 PPM, meaning 0.01 percent change in the

clock period. The DLL operates reliably on an input waveform with a frequency drift of up to 1 ns — orders of magnitude in excess of that needed to support any crystal oscillator in the industry. However, the cycle-to-cycle jitter must be kept to less than 300 ps in the low frequencies and 150 ps for the high frequencies.

### Input Clock Changes

Changing the period of the input clock beyond the maximum drift amount requires a manual reset of the CLKDLL. Failure to reset the DLL will produce an unreliable lock signal and output clock.

It is possible to stop the input clock in a way that has little impact to the DLL. Stopping the clock should be limited to less than approximately 100 µs to keep device cooling to a minimum and maintain the validity of the current tap setting. The clock should be stopped during a Low phase, and when restored the full High period should be seen. During this time LOCKED will stay High and remain High when the clock is restored. If these conditions may not be met in the design, apply a manual reset to the DLL after re-starting the input clock, even if the LOCKED signal has not changed.

When the clock is stopped, one to four more clocks will still be observed as the delay line is flushed. When the clock is restarted, the output clocks will not be observed for one to four clocks as the delay line is filled. The most common case will be two or three clocks.

In a similar manner, a phase shift of the input clock is also possible. The phase shift will propagate to the output one to four clocks after the original shift, with no disruption to the CLKDLL control.

## **Output Clocks**

As mentioned earlier in the DLL pin descriptions, some restrictions apply regarding the connectivity of the output pins. The DLL clock outputs can drive an OBUF, a global clock buffer BUFG, or route directly to destination clock pins. The only BUFGs that the DLL clock outputs can drive are the two on the same edge of the device (top or bottom). One DLL output can drive more than one OBUF; however, this adds skew.

Do not use the DLL output clock signals until after activation of the LOCKED signal. Prior to the activation of the LOCKED signal, the DLL output clocks are not valid and can exhibit glitches, spikes, or other spurious movement.

## **Creating Larger RAM Structures**

The block RAM columns have specialized routing to allow cascading blocks together with minimal routing delays. This achieves wider or deeper RAM structures with a smaller timing penalty than when using normal routing channels.

### **Location Constraints**

Block RAM instances can have LOC properties attached to them to constrain the placement. The block RAM placement locations are separate from the CLB location naming convention, allowing the LOC properties to transfer easily from array to array.

The LOC properties use the following form:

LOC = RAMB4\_R#C#

RAMB4\_R0C0 is the upper left RAMB4 location on the device.

#### **Conflict Resolution**

The block RAM memory is a true dual-read/write port RAM that allows simultaneous access of the same memory cell from both ports. When one port writes to a given memory cell, the other port must not address that memory cell (for a write or a read) within the clock-to-clock setup window. The following lists specifics of port and memory cell write conflict resolution.

- If both ports write to the same memory cell simultaneously, violating the clock-to-clock setup requirement, consider the data stored as invalid.

- If one port attempts a read of the same memory cell the other simultaneously writes, violating the clock-to-clock setup requirement, the following occurs.

- The write succeeds

- The data out on the writing port accurately reflects the data written.

- The data out on the reading port is invalid.

Conflicts do not cause any physical damage.

### Single Port Timing

Figure 33 shows a timing diagram for a single port of a block RAM memory. The block RAM AC switching characteristics are specified in the data sheet. The block RAM memory is initially disabled.

At the first rising edge of the CLK pin, the ADDR, DI, EN, WE, and RST pins are sampled. The EN pin is High and the WE pin is Low indicating a read operation. The DO bus contains the contents of the memory location, 0x00, as indicated by the ADDR bus.

At the second rising edge of the CLK pin, the ADDR, DI, EN, WR, and RST pins are sampled again. The EN and WE pins are High indicating a write operation. The DO bus mirrors

the DI bus. The DI bus is written to the memory location 0x0F.

At the third rising edge of the CLK pin, the ADDR, DI, EN, WR, and RST pins are sampled again. The EN pin is High and the WE pin is Low indicating a read operation. The DO bus contains the contents of the memory location 0x7E as indicated by the ADDR bus.

At the fourth rising edge of the CLK pin, the ADDR, DI, EN, WR, and RST pins are sampled again. The EN pin is Low indicating that the block RAM memory is now disabled. The DO bus retains the last value.

## **Dual Port Timing**

Figure 34 shows a timing diagram for a true dual-port read/write block RAM memory. The clock on port A has a longer period than the clock on Port B. The timing parameter  $T_{BCCS}$ , (clock-to-clock setup) is shown on this diagram. The parameter,  $T_{BCCS}$  is violated once in the diagram. All other timing parameters are identical to the single port version shown in Figure 33.

T<sub>BCCS</sub> is only of importance when the address of both ports are the same and at least one port is performing a write operation. When the clock-to-clock set-up parameter is violated for a WRITE-WRITE condition, the contents of the memory at that location will be invalid. When the clock-to-clock set-up parameter is violated for a WRITE-READ condition, the contents of the memory will be correct, but the read port will have invalid data. At the first rising edge of the CLKA, memory location 0x00 is to be written with the value 0xAAAA and is mirrored on the DOA bus. The last operation of Port B was a read to the same memory location 0x00. The DOB bus of Port B does not change with the new value on Port A, and retains the last read value. A short time later, Port B executes another read to memory location 0x00, and the DOB bus now reflects the new memory value written by Port A.

At the second rising edge of CLKA, memory location 0x7E is written with the value 0x9999 and is mirrored on the DOA bus. Port B then executes a read operation to the same memory location without violating the  $T_{BCCS}$  parameter and the DOB reflects the new memory values written by Port A.

## PCI — Peripheral Component Interface

The Peripheral Component Interface (PCI) standard specifies support for both 33 MHz and 66 MHz PCI bus applications. It uses a LVTTL input buffer and a push-pull output buffer. This standard does not require the use of a reference voltage ( $V_{REF}$ ) or a board termination voltage ( $V_{TT}$ ), however, it does require a 3.3V output source voltage ( $V_{CCO}$ ). I/Os configured for the PCI, 33 MHz, 5V standard are also 5V-tolerant.

## GTL — Gunning Transceiver Logic Terminated

The Gunning Transceiver Logic (GTL) standard is a high-speed bus standard (JESD8.3). Xilinx has implemented the terminated variation of this standard. This standard requires a differential amplifier input buffer and an open-drain output buffer.

## GTL+ — Gunning Transceiver Logic Plus

The Gunning Transceiver Logic Plus (GTL+) standard is a high-speed bus standard (JESD8.3).

### HSTL — High-Speed Transceiver Logic

The High-Speed Transceiver Logic (HSTL) standard is a general purpose high-speed, 1.5V bus standard (EIA/JESD 8-6). This standard has four variations or classes. Versatile I/O devices support Class I, III, and IV. This standard requires a Differential Amplifier input buffer and a Push-Pull output buffer.

### SSTL3 — Stub Series Terminated Logic for 3.3V

The Stub Series Terminated Logic for 3.3V (SSTL3) standard is a general purpose 3.3V memory bus standard (JESD8-8). This standard has two classes, I and II. Versatile I/O devices support both classes for the SSTL3 standard. This standard requires a Differential Amplifier input buffer and an Push-Pull output buffer.

#### SSTL2 — Stub Series Terminated Logic for 2.5V

The Stub Series Terminated Logic for 2.5V (SSTL2) standard is a general purpose 2.5V memory bus standard (JESD8-9). This standard has two classes, I and II. Versatile I/O devices support both classes for the SSTL2 standard. This standard requires a Differential Amplifier input buffer and an Push-Pull output buffer.

### CTT — Center Tap Terminated

The Center Tap Terminated (CTT) standard is a 3.3V memory bus standard (JESD8-4). This standard requires a Differential Amplifier input buffer and a Push-Pull output buffer.

### AGP-2X — Advanced Graphics Port

The AGP standard is a 3.3V Advanced Graphics Port-2X bus standard used with processors for graphics applications. This standard requires a Push-Pull output buffer and a Differential Amplifier input buffer.

## **Library Primitives**

The Xilinx library includes an extensive list of primitives designed to provide support for the variety of Versatile I/O features. Most of these primitives represent variations of the five generic Versatile I/O primitives:

- IBUF (input buffer)

- IBUFG (global clock input buffer)

- OBUF (output buffer)

- OBUFT (3-state output buffer)

- IOBUF (input/output buffer)

These primitives are available with various extensions to define the desired I/O standard. However, it is recommended that customers use a a property or attribute on the generic primitive to specify the I/O standard. See "Versatile I/O Properties".

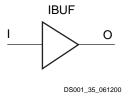

#### **IBUF**

Signals used as inputs to the Spartan-II device must source an input buffer (IBUF) via an external input port. The generic IBUF primitive appears in Figure 35. The assumed standard is LVTTL when the generic IBUF has no specified extension or property.

Figure 35: Input Buffer (IBUF) Primitive

When the IBUF primitive supports an I/O standard such as LVTTL, LVCMOS, or PCI33\_5, the IBUF automatically configures as a 5V tolerant input buffer unless the  $V_{CCO}$  for the bank is less than 2V. If the single-ended IBUF is placed in a bank with an HSTL standard ( $V_{CCO}$  < 2V), the input buffer is not 5V tolerant.

The voltage reference signal is "banked" within the Spartan-II device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 36 for a representation of the I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input.

IBUF placement restrictions require that any differential amplifier input signals within a bank be of the same standard. How to specify a specific location for the IBUF via

## **Recommended Operating Conditions**

| Symbol             | Description                                     |            | Min      | Max      | Units |

|--------------------|-------------------------------------------------|------------|----------|----------|-------|

| T <sub>J</sub>     | Junction temperature <sup>(1)</sup>             | Commercial | 0        | 85       | °C    |

|                    |                                                 | Industrial | -40      | 100      | °C    |

| V <sub>CCINT</sub> | Supply voltage relative to GND <sup>(2,5)</sup> | Commercial | 2.5 – 5% | 2.5 + 5% | V     |

|                    |                                                 | Industrial | 2.5 – 5% | 2.5 + 5% | V     |

| V <sub>cco</sub>   | Supply voltage relative to GND <sup>(3,5)</sup> | Commercial | 1.4      | 3.6      | V     |

|                    |                                                 | Industrial | 1.4      | 3.6      | V     |

| T <sub>IN</sub>    | Input signal transition time <sup>(4)</sup>     |            | -        | 250      | ns    |

#### Notes:

- 1. At junction temperatures above those listed as Operating Conditions, all delay parameters increase by 0.35% per °C.

- 2. Functional operation is guaranteed down to a minimum  $V_{CCINT}$  of 2.25V (Nominal  $V_{CCINT}$  10%). For every 50 mV reduction in  $V_{CCINT}$  below 2.375V (nominal  $V_{CCINT}$  5%), all delay parameters increase by 3%.

- Minimum and maximum values for V<sub>CCO</sub> vary according to the I/O standard selected.

- 4. Input and output measurement threshold is ~50% of V<sub>CCO</sub>. See "Delay Measurement Methodology," page 60 for specific levels.

- 5. Supply voltages may be applied in any order desired.

## **DC Characteristics Over Operating Conditions**

| Symbol              | Description                                                                    |                                                                                               |                  |     | Тур | Max  | Units |

|---------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------|-----|-----|------|-------|

| $V_{DRINT}$         | Data Retention V <sub>CCINT</sub> voltage (below may be lost)                  | w which conf                                                                                  | iguration data   | 2.0 | -   | -    | V     |

| $V_{DRIO}$          | Data Retention V <sub>CCO</sub> voltage (below be lost)                        | which configu                                                                                 | uration data may | 1.2 | -   | -    | V     |

| I <sub>CCINTQ</sub> | Quiescent V <sub>CCINT</sub> supply current <sup>(1)</sup>                     | XC2S15                                                                                        | Commercial       | -   | 10  | 30   | mA    |

|                     |                                                                                |                                                                                               | Industrial       | -   | 10  | 60   | mA    |

|                     |                                                                                | XC2S30                                                                                        | Commercial       | -   | 10  | 30   | mA    |

|                     |                                                                                |                                                                                               | Industrial       | -   | 10  | 60   | mA    |

|                     |                                                                                | XC2S50                                                                                        | Commercial       | -   | 12  | 50   | mA    |

|                     |                                                                                |                                                                                               | Industrial       | -   | 12  | 100  | mA    |

|                     |                                                                                | XC2S100                                                                                       | Commercial       | -   | 12  | 50   | mA    |

|                     |                                                                                |                                                                                               | Industrial       | -   | 12  | 100  | mA    |

|                     |                                                                                | XC2S150                                                                                       | Commercial       | -   | 15  | 50   | mA    |

|                     |                                                                                |                                                                                               | Industrial       | -   | 15  | 100  | mA    |

|                     |                                                                                | XC2S200                                                                                       | Commercial       | -   | 15  | 75   | mA    |

|                     |                                                                                |                                                                                               | Industrial       | -   | 15  | 150  | mA    |

| Iccoq               | Quiescent V <sub>CCO</sub> supply current <sup>(1)</sup>                       | -1-                                                                                           |                  | -   | -   | 2    | mA    |

| I <sub>REF</sub>    | V <sub>REF</sub> current per V <sub>REF</sub> pin                              |                                                                                               |                  | -   | -   | 20   | μΑ    |

| Ι <sub>L</sub>      | Input or output leakage current <sup>(2)</sup>                                 |                                                                                               |                  | -10 | -   | +10  | μΑ    |

| C <sub>IN</sub>     | Input capacitance (sample tested)                                              | VQ, CS, TQ, PQ, FG<br>packages                                                                |                  | -   | -   | 8    | pF    |

| I <sub>RPU</sub>    | Pad pull-up (when selected) @ V <sub>IN</sub> = (sample tested) <sup>(3)</sup> | Pad pull-up (when selected) @ $V_{IN} = 0V$ , $V_{CCO} = 3.3V$ (sample tested) <sup>(3)</sup> |                  |     | -   | 0.25 | mA    |

| I <sub>RPD</sub>    | Pad pull-down (when selected) @ V <sub>I</sub>                                 | <sub>N</sub> = 3.6V (sai                                                                      | mple tested)(3)  | -   | -   | 0.15 | mA    |

#### Notes

- With no output current loads, no active input pull-up resistors, all I/O pins 3-stated and floating.

- The I/O leakage current specification applies only when the V<sub>CCINT</sub> and V<sub>CCO</sub> supply voltages have reached their respective minimum Recommended Operating Conditions.

- 3. Internal pull-up and pull-down resistors guarantee valid logic levels at unconnected input pins. These pull-up and pull-down resistors do not provide valid logic levels when input pins are connected to other circuits.

| Input/Output |        | V <sub>IL</sub> V <sub>IH</sub> |                        | V <sub>OL</sub> | V <sub>OH</sub>        | I <sub>OL</sub>        | I <sub>OH</sub> |          |

|--------------|--------|---------------------------------|------------------------|-----------------|------------------------|------------------------|-----------------|----------|

| Standard     | V, Min | V, Max                          | V, Min                 | V, Max          | V, Max                 | V, Min                 | mA              | mA       |

| CTT          | -0.5   | V <sub>REF</sub> – 0.2          | V <sub>REF</sub> + 0.2 | 3.6             | V <sub>REF</sub> – 0.4 | V <sub>REF</sub> + 0.4 | 8               | -8       |

| AGP          | -0.5   | V <sub>REF</sub> – 0.2          | V <sub>REF</sub> + 0.2 | 3.6             | 10% V <sub>CCO</sub>   | 90% V <sub>CCO</sub>   | Note (2)        | Note (2) |

#### Notes:

- V<sub>OL</sub> and V<sub>OH</sub> for lower drive currents are sample tested. 1.

- Tested according to the relevant specifications.

## Switching Characteristics

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all Spartan-II devices unless otherwise noted.

## Global Clock Input to Output Delay for LVTTL, with DLL (Pin-to-Pin)(1)

|           |                                                                                                       |        | S   |     |     |       |

|-----------|-------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-------|

|           |                                                                                                       |        | All | -6  | -5  |       |

| Symbol    | Description                                                                                           | Device | Min | Max | Max | Units |

| TICKOFDLL | Global clock input to output delay using output flip-flop for LVTTL, 12 mA, fast slew rate, with DLL. | All    |     | 2.9 | 3.3 | ns    |

#### Notes:

- Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

- Output timing is measured at 1.4V with 35 pF external capacitive load for LVTTL. The 35 pF load does not apply to the Min values. For other I/O standards and different loads, see the tables "Constants for Calculating TIOOP" and "Delay Measurement Methodology," page 60.

- DLL output jitter is already included in the timing calculation.

- For data output with different standards, adjust delays with the values shown in "IOB Output Delay Adjustments for Different Standards," page 59. For a global clock input with standards other than LVTTL, adjust delays with values from the "I/O Standard Global Clock Input Adjustments," page 61.

## Global Clock Input to Output Delay for LVTTL, without DLL (Pin-to-Pin)(1)

|                    |                                                                       |         | All | -6  | -5  |       |

|--------------------|-----------------------------------------------------------------------|---------|-----|-----|-----|-------|

| Symbol             | Description                                                           | Device  | Min | Max | Max | Units |

| T <sub>ICKOF</sub> | Global clock input to output delay                                    | XC2S15  |     | 4.5 | 5.4 | ns    |

|                    | using output flip-flop for LVTTL, 12 mA, fast slew rate, without DLL. | XC2S30  |     | 4.5 | 5.4 | ns    |

|                    |                                                                       | XC2S50  |     | 4.5 | 5.4 | ns    |

|                    |                                                                       | XC2S100 |     | 4.6 | 5.5 | ns    |

|                    |                                                                       | XC2S150 |     | 4.6 | 5.5 | ns    |

|                    |                                                                       | XC2S200 |     | 4.7 | 5.6 | ns    |

#### Notes:

- Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

- Output timing is measured at 1.4V with 35 pF external capacitive load for LVTTL. The 35 pF load does not apply to the Min values. For other I/O standards and different loads, see the tables "Constants for Calculating TIOOP" and "Delay Measurement Methodology," page 60.

- For data output with different standards, adjust delays with the values shown in "IOB Output Delay Adjustments for Different Standards," page 59. For a global clock input with standards other than LVTTL, adjust delays with values from the "I/O Standard Global Clock Input Adjustments," page 61.

DS001-3 (v2.8) June 13, 2008 www.xilinx.com 54

## Global Clock Setup and Hold for LVTTL Standard, with DLL (Pin-to-Pin)

|                                         |                                                                                                                            |        | Speed   | Speed Grade |       |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------|---------|-------------|-------|--|

|                                         |                                                                                                                            |        | -6      | -5          |       |  |

| Symbol                                  | Description                                                                                                                | Device | Min     | Min         | Units |  |

| T <sub>PSDLL</sub> / T <sub>PHDLL</sub> | Input setup and hold time relative to global clock input signal for LVTTL standard, no delay, IFF, <sup>(1)</sup> with DLL | All    | 1.7 / 0 | 1.9 / 0     | ns    |  |

#### Notes:

- 1. IFF = Input Flip-Flop or Latch

- 2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

- 3. DLL output jitter is already included in the timing calculation.

- 4. A zero hold time listing indicates no hold time or a negative hold time.

- 5. For data input with different standards, adjust the setup time delay by the values shown in "IOB Input Delay Adjustments for Different Standards," page 57. For a global clock input with standards other than LVTTL, adjust delays with values from the "I/O Standard Global Clock Input Adjustments," page 61.

## Global Clock Setup and Hold for LVTTL Standard, without DLL (Pin-to-Pin)

|                                       |                                                           |         | Speed   |         |       |

|---------------------------------------|-----------------------------------------------------------|---------|---------|---------|-------|

|                                       |                                                           |         | -6      | -5      |       |

| Symbol                                | Description                                               | Device  | Min     | Min     | Units |

| T <sub>PSFD</sub> / T <sub>PHFD</sub> | to global clock input signal for                          | XC2S15  | 2.2 / 0 | 2.7 / 0 | ns    |

|                                       |                                                           | XC2S30  | 2.2 / 0 | 2.7 / 0 | ns    |

|                                       | LVTTL standard, no delay, IFF, <sup>(1)</sup> without DLL | XC2S50  | 2.2 / 0 | 2.7 / 0 | ns    |

|                                       | Without BLE                                               | XC2S100 | 2.3 / 0 | 2.8 / 0 | ns    |

|                                       |                                                           | XC2S150 | 2.4 / 0 | 2.9 / 0 | ns    |

|                                       |                                                           | XC2S200 | 2.4 / 0 | 3.0 / 0 | ns    |

## Notes:

- 1. IFF = Input Flip-Flop or Latch

- 2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

- 3. A zero hold time listing indicates no hold time or a negative hold time.

- 4. For data input with different standards, adjust the setup time delay by the values shown in "IOB Input Delay Adjustments for Different Standards," page 57. For a global clock input with standards other than LVTTL, adjust delays with values from the "I/O Standard Global Clock Input Adjustments," page 61.

## Clock Distribution Guidelines<sup>(1)</sup>

|                       |                                          | Speed Grade |      |       |  |  |  |  |  |

|-----------------------|------------------------------------------|-------------|------|-------|--|--|--|--|--|

|                       |                                          | -6          | -5   |       |  |  |  |  |  |

| Symbol                | Description                              | Max         | Max  | Units |  |  |  |  |  |

| GCLK Clock Skew       | GCLK Clock Skew                          |             |      |       |  |  |  |  |  |

| T <sub>GSKEWIOB</sub> | Global clock skew between IOB flip-flops | 0.13        | 0.14 | ns    |  |  |  |  |  |

#### Notes:

## **Clock Distribution Switching Characteristics**

T<sub>GPIO</sub> is specified for LVTTL levels. For other standards, adjust T<sub>GPIO</sub> with the values shown in "I/O Standard Global Clock Input Adjustments".

|                   |                                         | Speed Grade        |     |       |

|-------------------|-----------------------------------------|--------------------|-----|-------|

|                   |                                         | -6 -5              |     |       |

| Symbol            | Description                             | escription Max Max |     | Units |

| GCLK IOB and Bu   | ffer                                    |                    |     |       |

| T <sub>GPIO</sub> | Global clock pad to output              | 0.7                | 0.8 | ns    |

| T <sub>GIO</sub>  | Global clock buffer I input to O output | 0.7                | 0.8 | ns    |

## I/O Standard Global Clock Input Adjustments

Delays associated with a global clock input pad are specified for LVTTL levels. For other standards, adjust the delays by the values shown. A delay adjusted in this way constitutes a worst-case limit.

|                              |                                |                   | Speed | Grade |       |  |  |  |  |  |

|------------------------------|--------------------------------|-------------------|-------|-------|-------|--|--|--|--|--|

| Symbol                       | Description                    | Standard          | -6    | -5    | Units |  |  |  |  |  |

| Data Input Delay Adjustments |                                |                   |       |       |       |  |  |  |  |  |

| T <sub>GPLVTTL</sub>         | Standard-specific global clock | LVTTL             | 0     | 0     | ns    |  |  |  |  |  |

| T <sub>GPLVCMOS2</sub>       | input delay adjustments        | LVCMOS2           | -0.04 | -0.05 | ns    |  |  |  |  |  |

| T <sub>GPPCl33_3</sub>       |                                | PCI, 33 MHz, 3.3V | -0.11 | -0.13 | ns    |  |  |  |  |  |

| T <sub>GPPCl33_5</sub>       |                                | PCI, 33 MHz, 5.0V | 0.26  | 0.30  | ns    |  |  |  |  |  |

| T <sub>GPPCI66_3</sub>       |                                | PCI, 66 MHz, 3.3V | -0.11 | -0.13 | ns    |  |  |  |  |  |

| T <sub>GPGTL</sub>           |                                | GTL               | 0.80  | 0.84  | ns    |  |  |  |  |  |

| T <sub>GPGTLP</sub>          |                                | GTL+              | 0.71  | 0.73  | ns    |  |  |  |  |  |

| T <sub>GPHSTL</sub>          |                                | HSTL              | 0.63  | 0.64  | ns    |  |  |  |  |  |

| T <sub>GPSSTL2</sub>         |                                | SSTL2             | 0.52  | 0.51  | ns    |  |  |  |  |  |

| T <sub>GPSSTL3</sub>         |                                | SSTL3             | 0.56  | 0.55  | ns    |  |  |  |  |  |

| T <sub>GPCTT</sub>           | _                              | CTT               | 0.62  | 0.62  | ns    |  |  |  |  |  |

| T <sub>GPAGP</sub>           |                                | AGP               | 0.54  | 0.53  | ns    |  |  |  |  |  |

#### Notes:

Input timing for GPLVTTL is measured at 1.4V. For other I/O standards, see the table "Delay Measurement Methodology," page 60.

These clock distribution delays are provided for guidance only. They reflect the delays encountered in a typical design under worst-case conditions. Precise values for a particular design are provided by the timing analyzer.

## **CLB Arithmetic Switching Characteristics**

Setup times not listed explicitly can be approximated by decreasing the combinatorial delays by the setup time adjustment listed. Precise values are provided by the timing analyzer.

|                                       |                                            |          | Speed | d Grade |     |       |

|---------------------------------------|--------------------------------------------|----------|-------|---------|-----|-------|

|                                       |                                            | -(       | 6     |         | 5   |       |

| Symbol                                | Description                                | Min      | Max   | Min     | Max | Units |

| Combinatorial Del                     | ays                                        | "        |       |         |     | "     |

| T <sub>OPX</sub>                      | F operand inputs to X via XOR              | -        | 8.0   | -       | 0.9 | ns    |

| T <sub>OPXB</sub>                     | F operand input to XB output               | -        | 1.3   | -       | 1.5 | ns    |

| T <sub>OPY</sub>                      | F operand input to Y via XOR               | -        | 1.7   | -       | 2.0 | ns    |

| T <sub>OPYB</sub>                     | F operand input to YB output               | -        | 1.7   | -       | 2.0 | ns    |

| T <sub>OPCYF</sub>                    | F operand input to COUT output             | -        | 1.3   | -       | 1.5 | ns    |

| T <sub>OPGY</sub>                     | G operand inputs to Y via XOR              | -        | 0.9   | -       | 1.1 | ns    |

| T <sub>OPGYB</sub>                    | G operand input to YB output               | -        | 1.6   | -       | 2.0 | ns    |

| T <sub>OPCYG</sub>                    | G operand input to COUT output             | -        | 1.2   | -       | 1.4 | ns    |

| T <sub>BXCY</sub>                     | BX initialization input to COUT            | -        | 0.9   | -       | 1.0 | ns    |

| T <sub>CINX</sub>                     | CIN input to X output via XOR              | -        | 0.4   | -       | 0.5 | ns    |

| T <sub>CINXB</sub>                    | CIN input to XB                            | -        | 0.1   | -       | 0.1 | ns    |

| T <sub>CINY</sub>                     | CIN input to Y via XOR                     | -        | 0.5   | -       | 0.6 | ns    |

| T <sub>CINYB</sub>                    | CIN input to YB                            | -        | 0.6   | -       | 0.7 | ns    |

| T <sub>BYP</sub>                      | CIN input to COUT output                   | -        | 0.1   | -       | 0.1 | ns    |

| Multiplier Operation                  | on                                         | <u> </u> |       |         |     | 1     |

| T <sub>FANDXB</sub>                   | F1/2 operand inputs to XB output via AND   | -        | 0.5   | -       | 0.5 | ns    |

| T <sub>FANDYB</sub>                   | F1/2 operand inputs to YB output via AND   | -        | 0.9   | -       | 1.1 | ns    |

| T <sub>FANDCY</sub>                   | F1/2 operand inputs to COUT output via AND | -        | 0.5   | -       | 0.6 | ns    |

| T <sub>GANDYB</sub>                   | G1/2 operand inputs to YB output via AND   | -        | 0.6   | -       | 0.7 | ns    |

| T <sub>GANDCY</sub>                   | G1/2 operand inputs to COUT output via AND | -        | 0.2   | -       | 0.2 | ns    |

| Setup/Hold Times                      | with Respect to Clock CLK <sup>(1)</sup>   | 1        |       |         |     | 1     |

| T <sub>CCKX</sub> / T <sub>CKCX</sub> | CIN input to FFX                           | 1.1 / 0  | -     | 1.2/0   | -   | ns    |

| T <sub>CCKY</sub> / T <sub>CKCY</sub> | CIN input to FFY                           | 1.2 / 0  | -     | 1.3 / 0 | -   | ns    |

#### Notes:

<sup>1.</sup> A zero hold time listing indicates no hold time or a negative hold time.

# **Revision History**

| Date     | Version No. | Description                                                                                                                                                                                                                                                                                                                                 |

|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09/18/00 | 2.0         | Sectioned the Spartan-II Family data sheet into four modules. Updated timing to reflect the latest speed files. Added current supply numbers and XC2S200 -5 timing numbers. Approved -5 timing numbers as preliminary information with exceptions as noted.                                                                                 |

| 11/02/00 | 2.1         | Removed Power Down feature.                                                                                                                                                                                                                                                                                                                 |

| 01/19/01 | 2.2         | DC and timing numbers updated to Preliminary for the XC2S50 and XC2S100. Industrial power-on current specifications and -6 DLL timing numbers added. Power-on specification clarified.                                                                                                                                                      |

| 03/09/01 | 2.3         | Added note on power sequencing. Clarified power-on current requirement.                                                                                                                                                                                                                                                                     |

| 08/28/01 | 2.4         | Added -6 preliminary timing. Added typical and industrial standby current numbers. Specified min. power-on current by junction temperature instead of by device type (Commercial vs. Industrial). Eliminated minimum V <sub>CCINT</sub> ramp time requirement. Removed footnote limiting DLL operation to the Commercial temperature range. |

| 07/26/02 | 2.5         | Clarified that I/O leakage current is specified over the Recommended Operating Conditions for $V_{\text{CCINT}}$ and $V_{\text{CCO}}$ .                                                                                                                                                                                                     |

| 08/26/02 | 2.6         | Added references for XAPP450 to Power-On Current Specification.                                                                                                                                                                                                                                                                             |

| 09/03/03 | 2.7         | Added relaxed minimum power-on current (I <sub>CCPO</sub> ) requirements to page 53. On page 64, moved T <sub>RPW</sub> values from maximum to minimum column.                                                                                                                                                                              |

| 06/13/08 | 2.8         | Updated I/O measurement thresholds. Updated description and links. Updated all modules for continuous page, figure, and table numbering. Synchronized all modules to v2.8.                                                                                                                                                                  |

## **Package Thermal Characteristics**

Table 39 provides the thermal characteristics for the various Spartan-II FPGA package offerings. This information is also available using the Thermal Query tool on xilinx.com (www.xilinx.com/cgi-bin/thermal/thermal.pl).

The junction-to-case thermal resistance  $(\theta_{JC})$  indicates the difference between the temperature measured on the package body (case) and the die junction temperature per watt of power consumption. The junction-to-board  $(\theta_{JB})$

Table 39: Spartan-II Package Thermal Characteristics

value similarly reports the difference between the board and junction temperature. The junction-to-ambient  $(\theta_{JA})$  value reports the temperature difference between the ambient environment and the junction temperature. The  $\theta_{JA}$  value is reported at different air velocities, measured in linear feet per minute (LFM). The "Still Air (0 LFM)" column shows the  $\theta_{JA}$  value in a system without a fan. The thermal resistance drops with increasing air flow.

|                 |         |                                      |                                          | Junction-to-Ambient (θ <sub>JA</sub> )<br>at Different Air Flows |         |         |         |         |

|-----------------|---------|--------------------------------------|------------------------------------------|------------------------------------------------------------------|---------|---------|---------|---------|

| Package         | Device  | Junction-to-Case $(\theta_{\sf JC})$ | Junction-to-<br>Board (θ <sub>JB</sub> ) | Still Air<br>(0 LFM)                                             | 250 LFM | 500 LFM | 750 LFM | Units   |

| VQ100           | XC2S15  | 11.3                                 | N/A                                      | 44.1                                                             | 36.7    | 34.2    | 33.3    | °C/Watt |

| VQG100          | XC2S30  | 10.1                                 | N/A                                      | 40.7                                                             | 33.9    | 31.5    | 30.8    | °C/Watt |

|                 | XC2S15  | 7.3                                  | N/A                                      | 38.6                                                             | 30.0    | 25.7    | 24.1    | °C/Watt |

| TQ144           | XC2S30  | 6.7                                  | N/A                                      | 34.7                                                             | 27.0    | 23.1    | 21.7    | °C/Watt |

| TQG144          | XC2S50  | 5.8                                  | N/A                                      | 32.2                                                             | 25.1    | 21.4    | 20.1    | °C/Watt |

|                 | XC2S100 | 5.3                                  | N/A                                      | 31.4                                                             | 24.4    | 20.9    | 19.6    | °C/Watt |

| CS144<br>CSG144 | XC2S30  | 2.8                                  | N/A                                      | 34.0                                                             | 26.0    | 23.9    | 23.2    | °C/Watt |

|                 | XC2S50  | 6.7                                  | N/A                                      | 25.2                                                             | 18.6    | 16.4    | 15.2    | °C/Watt |

| PQ208           | XC2S100 | 5.9                                  | N/A                                      | 24.6                                                             | 18.1    | 16.0    | 14.9    | °C/Watt |

| PQG208          | XC2S150 | 5.0                                  | N/A                                      | 23.8                                                             | 17.6    | 15.6    | 14.4    | °C/Watt |

|                 | XC2S200 | 4.1                                  | N/A                                      | 23.0                                                             | 17.0    | 15.0    | 13.9    | °C/Watt |

|                 | XC2S50  | 7.1                                  | 17.6                                     | 27.2                                                             | 21.4    | 20.3    | 19.8    | °C/Watt |

| FG256           | XC2S100 | 5.8                                  | 15.1                                     | 25.1                                                             | 19.5    | 18.3    | 17.8    | °C/Watt |

| FGG256          | XC2S150 | 4.6                                  | 12.7                                     | 23.0                                                             | 17.6    | 16.3    | 15.8    | °C/Watt |

|                 | XC2S200 | 3.5                                  | 10.7                                     | 21.4                                                             | 16.1    | 14.7    | 14.2    | °C/Watt |

| FG456           | XC2S150 | 2.0                                  | N/A                                      | 21.9                                                             | 17.3    | 15.8    | 15.2    | °C/Watt |

| FGG456          | XC2S200 | 2.0                                  | N/A                                      | 21.0                                                             | 16.6    | 15.1    | 14.5    | °C/Watt |

## **XC2S30 Device Pinouts**

| XC2S30 Pad Name          |      |       |       |       |       |               |

|--------------------------|------|-------|-------|-------|-------|---------------|

| Function                 | Bank | VQ100 | TQ144 | CS144 | PQ208 | Bndry<br>Scan |

| GND                      | -    | P1    | P143  | A1    | P1    | -             |

| TMS                      | -    | P2    | P142  | B1    | P2    | -             |

| I/O                      | 7    | P3    | P141  | C2    | P3    | 113           |

| I/O                      | 7    | -     | P140  | C1    | P4    | 116           |

| I/O                      | 7    | -     | -     | -     | P5    | 119           |

| I/O, V <sub>REF</sub>    | 7    | P4    | P139  | D4    | P6    | 122           |

| I/O                      | 7    | -     | P138  | D3    | P8    | 125           |

| I/O                      | 7    | P5    | P137  | D2    | P9    | 128           |

| I/O                      | 7    | P6    | P136  | D1    | P10   | 131           |

| GND                      | -    | -     | P135  | E4    | P11   | -             |

| V <sub>CCO</sub>         | 7    | -     | -     | -     | P12   | -             |

| I/O                      | 7    | P7    | P134  | E3    | P14   | 134           |

| I/O                      | 7    | -     | P133  | E2    | P15   | 137           |

| I/O                      | 7    | -     | -     | -     | P16   | 140           |

| I/O                      | 7    | -     | -     | -     | P17   | 143           |

| I/O                      | 7    | -     | -     | -     | P18   | 146           |

| GND                      | -    | -     | -     | -     | P19   | -             |

| I/O, V <sub>REF</sub>    | 7    | P8    | P132  | E1    | P20   | 149           |

| I/O                      | 7    | P9    | P131  | F4    | P21   | 152           |

| I/O                      | 7    | -     | P130  | F3    | P22   | 155           |

| I/O                      | 7    | -     | -     | -     | P23   | 158           |

| I/O, IRDY <sup>(1)</sup> | 7    | P10   | P129  | F2    | P24   | 161           |

| GND                      | -    | P11   | P128  | F1    | P25   | -             |

| V <sub>CCO</sub>         | 7    | P12   | P127  | G2    | P26   | -             |

| V <sub>CCO</sub>         | 6    | P12   | P127  | G2    | P26   | -             |

| I/O, TRDY <sup>(1)</sup> | 6    | P13   | P126  | G1    | P27   | 164           |

| V <sub>CCINT</sub>       | -    | P14   | P125  | G3    | P28   | -             |

| I/O                      | 6    | -     | P124  | G4    | P29   | 170           |

| I/O                      | 6    | P15   | P123  | H1    | P30   | 173           |

| I/O, V <sub>REF</sub>    | 6    | P16   | P122  | H2    | P31   | 176           |

| GND                      | -    | -     | -     | -     | P32   | -             |

| I/O                      | 6    | -     | -     | -     | P33   | 179           |

| I/O                      | 6    | -     | -     | -     | P34   | 182           |

| I/O                      | 6    | -     | -     | -     | P35   | 185           |

| I/O                      | 6    | -     | P121  | НЗ    | P36   | 188           |

| I/O                      | 6    | P17   | P120  | H4    | P37   | 191           |

| V <sub>CCO</sub>         | 6    | -     | -     | -     | P39   | -             |

| GND                      | -    | -     | P119  | J1    | P40   | -             |

| I/O                      | 6    | P18   | P118  | J2    | P41   | 194           |

| I/O                      | 6    | P19   | P117  | J3    | P42   | 197           |

| I/O                      | 6    | -     | P116  | J4    | P43   | 200           |

## XC2S30 Device Pinouts (Continued)

| XC2S30 Pad Name       |      |       |       |       |       | Bndry |

|-----------------------|------|-------|-------|-------|-------|-------|

| Function              | Bank | VQ100 | TQ144 | CS144 | PQ208 | Scan  |

| I/O, V <sub>REF</sub> | 6    | P20   | P115  | K1    | P45   | 203   |

| I/O                   | 6    | -     | -     | -     | P46   | 206   |

| I/O                   | 6    | -     | P114  | K2    | P47   | 209   |

| I/O                   | 6    | P21   | P113  | K3    | P48   | 212   |

| I/O                   | 6    | P22   | P112  | L1    | P49   | 215   |

| M1                    | -    | P23   | P111  | L2    | P50   | 218   |

| GND                   | -    | P24   | P110  | L3    | P51   | -     |

| M0                    | -    | P25   | P109  | M1    | P52   | 219   |

| $V_{CCO}$             | 6    | P26   | P108  | M2    | P53   | -     |

| V <sub>CCO</sub>      | 5    | P26   | P107  | N1    | P53   | -     |

| M2                    | -    | P27   | P106  | N2    | P54   | 220   |

| I/O                   | 5    | -     | P103  | K4    | P57   | 227   |

| I/O                   | 5    | -     | -     | -     | P58   | 230   |

| I/O, V <sub>REF</sub> | 5    | P30   | P102  | L4    | P59   | 233   |

| I/O                   | 5    | -     | P101  | M4    | P61   | 236   |

| I/O                   | 5    | P31   | P100  | N4    | P62   | 239   |

| I/O                   | 5    | P32   | P99   | K5    | P63   | 242   |

| GND                   | -    | -     | P98   | L5    | P64   | -     |

| V <sub>CCO</sub>      | 5    | -     | -     | -     | P65   | -     |

| V <sub>CCINT</sub>    | -    | P33   | P97   | M5    | P66   | -     |

| I/O                   | 5    | -     | P96   | N5    | P67   | 245   |

| I/O                   | 5    | -     | P95   | K6    | P68   | 248   |

| I/O                   | 5    | -     | -     | -     | P69   | 251   |

| I/O                   | 5    | -     | -     | -     | P70   | 254   |

| I/O                   | 5    | -     | -     | -     | P71   | 257   |

| GND                   | -    | -     | -     | -     | P72   | -     |

| I/O, V <sub>REF</sub> | 5    | P34   | P94   | L6    | P73   | 260   |

| I/O                   | 5    | -     | -     | -     | P74   | 263   |

| I/O                   | 5    | -     | P93   | M6    | P75   | 266   |

| V <sub>CCINT</sub>    | -    | P35   | P92   | N6    | P76   | -     |

| I, GCK1               | 5    | P36   | P91   | M7    | P77   | 275   |

| V <sub>CCO</sub>      | 5    | P37   | P90   | N7    | P78   | -     |

| V <sub>CCO</sub>      | 4    | P37   | P90   | N7    | P78   | -     |

| GND                   | -    | P38   | P89   | L7    | P79   | -     |

| I, GCK0               | 4    | P39   | P88   | K7    | P80   | 276   |

| I/O                   | 4    | P40   | P87   | N8    | P81   | 280   |

| I/O                   | 4    | -     | P86   | M8    | P82   | 283   |

| I/O                   | 4    | -     | -     | -     | P83   | 286   |

| I/O, V <sub>REF</sub> | 4    | P41   | P85   | L8    | P84   | 289   |

| GND                   | -    | -     | -     | -     | P85   | -     |

| I/O                   | 4    | -     | -     | -     | P86   | 292   |

|                       |      |       |       |       |       |       |

## XC2S50 Device Pinouts (Continued)

| XC2S50 Pad            | Name |       |       |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | Scan  |

| I/O                   | 0    | -     | -     | D8                          | 83    |

| I/O                   | 0    | -     | P188  | A6                          | 86    |

| I/O, V <sub>REF</sub> | 0    | P12   | P189  | В7                          | 89    |

| GND                   | -    | -     | P190  | GND*                        | -     |

| I/O                   | 0    | -     | P191  | C8                          | 92    |

| I/O                   | 0    | -     | P192  | D7                          | 95    |

| I/O                   | 0    | -     | P193  | E7                          | 98    |

| I/O                   | 0    | P11   | P194  | C7                          | 104   |

| I/O                   | 0    | P10   | P195  | B6                          | 107   |

| V <sub>CCINT</sub>    | -    | P9    | P196  | V <sub>CCINT</sub> *        | -     |

| V <sub>CCO</sub>      | 0    | -     | P197  | V <sub>CCO</sub><br>Bank 0* | -     |

| GND                   | -    | P8    | P198  | GND*                        | -     |

| I/O                   | 0    | P7    | P199  | A5                          | 110   |

| I/O                   | 0    | P6    | P200  | C6                          | 113   |

| I/O                   | 0    | -     | P201  | B5                          | 116   |

| I/O                   | 0    | -     | -     | D6                          | 119   |

| I/O                   | 0    | -     | P202  | A4                          | 122   |

| I/O, V <sub>REF</sub> | 0    | P5    | P203  | B4                          | 125   |

| GND                   | -    | -     | -     | GND*                        | -     |

| I/O                   | 0    | -     | P204  | E6                          | 128   |

| I/O                   | 0    | -     | -     | D5                          | 131   |

| I/O                   | 0    | P4    | P205  | А3                          | 134   |

| I/O                   | 0    | -     | -     | C5                          | 137   |

| I/O                   | 0    | P3    | P206  | В3                          | 140   |

| TCK                   | -    | P2    | P207  | C4                          | -     |

| V <sub>cco</sub>      | 0    | P1    | P208  | V <sub>CCO</sub><br>Bank 0* | -     |

| V <sub>CCO</sub>      | 7    | P144  | P208  | V <sub>CCO</sub><br>Bank 7* | -     |

### 04/18/01

#### Notes:

- IRDY and TRDY can only be accessed when using Xilinx PCI cores.

- Pads labelled GND\*, V<sub>CCINT</sub>\*, V<sub>CCO</sub> Bank 0\*, V<sub>CCO</sub> Bank 1\*, V<sub>CCO</sub> Bank 2\*, V<sub>CCO</sub> Bank 3\*, V<sub>CCO</sub> Bank 4\*, V<sub>CCO</sub> Bank 5\*, V<sub>CCO</sub> Bank 6\*, V<sub>CCO</sub> Bank 7\* are internally bonded to independent ground or power planes within the package.

- 3. See "VCCO Banks" for details on  $V_{CCO}$  banking.

## **Additional XC2S50 Package Pins**

### TQ144

| Not Connected Pins |           |  |   |  |  |  |  |  |  |  |

|--------------------|-----------|--|---|--|--|--|--|--|--|--|

| P104               | P104 P105 |  |   |  |  |  |  |  |  |  |

| 11/02/00           |           |  | 1 |  |  |  |  |  |  |  |

nally bonded to vithin the package.

O banking.

## Additional XC2S50 Package Pins (Continued)

### PQ208

| Not Connected Pins |     |   |   |   |   |  |  |  |  |

|--------------------|-----|---|---|---|---|--|--|--|--|

| P55                | P56 | - | - | - | - |  |  |  |  |

| 11/02/00           |     |   |   |   |   |  |  |  |  |

#### FG256

| F G 2 3 0                    |                              |                     |                   |    |     |  |  |  |  |  |

|------------------------------|------------------------------|---------------------|-------------------|----|-----|--|--|--|--|--|

|                              |                              | V <sub>CCIN</sub>   | <sub>T</sub> Pins |    |     |  |  |  |  |  |

| C3                           | C14                          | D4                  | D13               | E5 | E12 |  |  |  |  |  |

| M5                           | M12                          | N4                  | N13               | P3 | P14 |  |  |  |  |  |

| V <sub>CCO</sub> Bank 0 Pins |                              |                     |                   |    |     |  |  |  |  |  |

| E8                           | F8                           | -                   | -                 | -  | -   |  |  |  |  |  |

| V <sub>CCO</sub> Bank 1 Pins |                              |                     |                   |    |     |  |  |  |  |  |

| E9                           | F9                           | -                   | -                 | -  | -   |  |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 2 Pins         |    |     |  |  |  |  |  |

| H11                          | H12                          | -                   | -                 | -  | -   |  |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 3 Pins         |    |     |  |  |  |  |  |

| J11                          | J12                          | -                   | -                 | -  | -   |  |  |  |  |  |

|                              | V <sub>CCO</sub> Bank 4 Pins |                     |                   |    |     |  |  |  |  |  |

| L9                           | M9                           | -                   | -                 | -  | -   |  |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 5 Pins         |    |     |  |  |  |  |  |

| L8                           | M8                           | -                   | -                 | -  | -   |  |  |  |  |  |