# E·XFL

#### AMD Xilinx - XC2S50-5FG256I Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                     |

|--------------------------------|------------------------------------------------------------|

| Number of LABs/CLBs            | 384                                                        |

| Number of Logic Elements/Cells | 1728                                                       |

| Total RAM Bits                 | 32768                                                      |

| Number of I/O                  | 176                                                        |

| Number of Gates                | 50000                                                      |

| Voltage - Supply               | 2.375V ~ 2.625V                                            |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 256-BGA                                                    |

| Supplier Device Package        | 256-FBGA (17x17)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s50-5fg256i |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#

# Signals

There are two kinds of pins that are used to configure Spartan-II devices: Dedicated pins perform only specific configuration-related functions; the other pins can serve as general purpose I/Os once user operation has begun.

The dedicated pins comprise the mode pins (M2, M1, M0), the configuration clock pin (CCLK), the PROGRAM pin, the DONE pin and the boundary-scan pins (TDI, TDO, TMS, TCK). Depending on the selected configuration mode, CCLK may be an output generated by the FPGA, or may be generated externally, and provided to the FPGA as an input.

Note that some configuration pins can act as outputs. For correct operation, these pins require a V<sub>CCO</sub> of 3.3V to drive an LVTTL signal or 2.5V to drive an LVCMOS signal. All the relevant pins fall in banks 2 or 3. The  $\overline{\text{CS}}$  and  $\overline{\text{WRITE}}$  pins for Slave Parallel mode are located in bank 1.

For a more detailed description than that given below, see "Pinout Tables" in Module 4 and XAPP176, Spartan-II FPGA Series Configuration and Readback.

# The Process

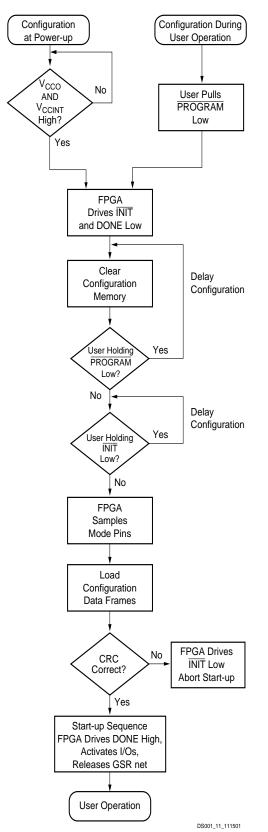

The sequence of steps necessary to configure Spartan-II devices are shown in Figure 11. The overall flow can be divided into three different phases.

- Initiating Configuration

- Configuration memory clear

- Loading data frames

- Start-up

The memory clearing and start-up phases are the same for all configuration modes; however, the steps for the loading of data frames are different. Thus, the details for data frame loading are described separately in the sections devoted to each mode.

# Initiating Configuration

There are two different ways to initiate the configuration process: applying power to the device or asserting the PROGRAM input.

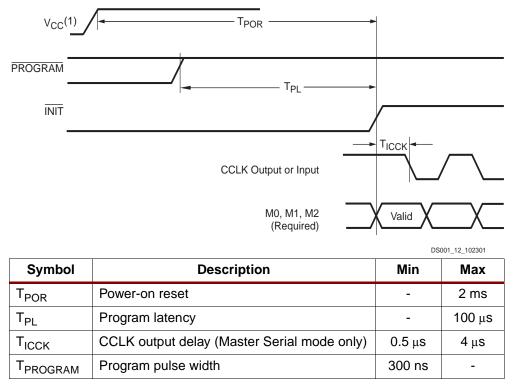

Configuration on power-up occurs automatically unless it is delayed by the user, as described in a separate section below. The waveform for configuration on power-up is shown in Figure 12, page 19. Before configuration can begin,  $V_{CCO}$  Bank 2 must be greater than 1.0V. Furthermore, all  $V_{CCINT}$  power pins must be connected to a 2.5V supply. For more information on delaying configuration, see "Clearing Configuration Memory," page 19.

Once in user operation, the device can be re-configured simply by pulling the PROGRAM pin Low. The device acknowledges the beginning of the configuration process

by driving DONE Low, then enters the memory-clearing phase.

Figure 11: Configuration Flow Diagram

#### Notes: (referring to waveform above:)

1. Before configuration can begin,  $V_{CCINT}$  must be greater than 1.6V and  $V_{CCO}$  Bank 2 must be greater than 1.0V.

Figure 12: Configuration Timing on Power-Up

#### **Clearing Configuration Memory**

The device indicates that clearing the configuration memory is in progress by driving INIT Low. At this time, the user can delay configuration by holding either PROGRAM or INIT Low, which causes the device to remain in the memory clearing phase. Note that the bidirectional INIT line is driving a Low logic level during memory clearing. To avoid contention, use an open-drain driver to keep INIT Low.

With no delay in force, the device indicates that the memory is completely clear by driving INIT High. The FPGA samples its mode pins on this Low-to-High transition.

# Loading Configuration Data

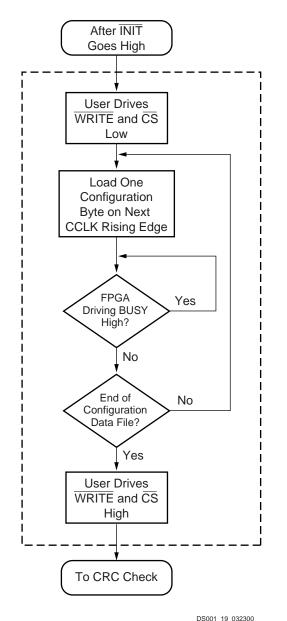

Once INIT is High, the user can begin loading configuration data frames into the device. The details of loading the configuration data are discussed in the sections treating the configuration modes individually. The sequence of operations necessary to load configuration data using the serial modes is shown in Figure 14. Loading data using the Slave Parallel mode is shown in Figure 19, page 25.

#### **CRC Error Checking**

During the loading of configuration data, a CRC value embedded in the configuration file is checked against a CRC value calculated within the FPGA. If the CRC values do not match, the FPGA drives INIT Low to indicate that a frame error has occurred and configuration is aborted.

To reconfigure the device, the PROGRAM pin should be asserted to reset the configuration logic. Recycling power also resets the FPGA for configuration. See "Clearing Configuration Memory".

#### Start-up

The start-up sequence oversees the transition of the FPGA from the configuration state to full user operation. A match of CRC values, indicating a successful loading of the configuration data, initiates the sequence.

During start-up, the device performs four operations:

- 1. The assertion of DONE. The failure of DONE to go High may indicate the unsuccessful loading of configuration data.

- 2. The release of the Global Three State net. This activates I/Os to which signals are assigned. The remaining I/Os stay in a high-impedance state with internal weak pull-down resistors present.

- 3. Negates Global Set Reset (GSR). This allows all flip-flops to change state.

- 4. The assertion of Global Write Enable (GWE). This allows all RAMs and flip-flops to change state.

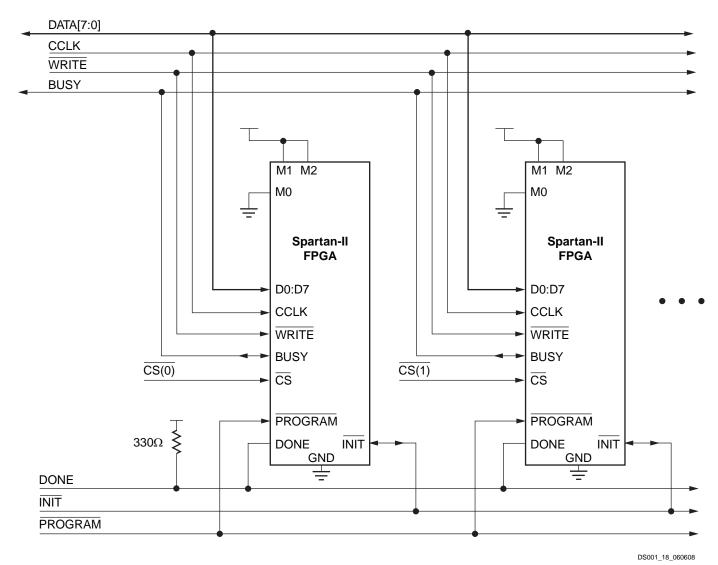

Figure 18: Slave Parallel Configuration Circuit Diagram

Multiple Spartan-II FPGAs can be configured using the Slave Parallel mode, and be made to start-up simultaneously. To configure multiple devices in this way, wire the individual CCLK, Data, WRITE, and BUSY pins of all the devices in parallel. The individual devices are loaded separately by asserting the CS pin of each device in turn and writing the appropriate data. Sync-to-DONE start-up timing is used to ensure that the start-up sequence does not begin until all the FPGAs have been loaded. See "Start-up," page 19.

#### Write

When using the Slave Parallel Mode, write operations send packets of byte-wide configuration data into the FPGA. Figure 19, page 25 shows a flowchart of the write sequence used to load data into the Spartan-II FPGA. This is an expansion of the "Load Configuration Data Frames" block in Figure 11, page 18. The timing for write operations is shown in Figure 20, page 26. For the present example, the user holds  $\overline{\text{WRITE}}$  and  $\overline{\text{CS}}$ Low throughout the sequence of write operations. Note that when  $\overline{\text{CS}}$  is asserted on successive CCLKs,  $\overline{\text{WRITE}}$  must remain either asserted or de-asserted. Otherwise an abort will be initiated, as in the next section.

- 1. Drive data onto D0-D7. Note that to avoid contention, the data source should not be enabled while  $\overline{CS}$  is Low and  $\overline{WRITE}$  is High. Similarly, while  $\overline{WRITE}$  is High, no more than one device's  $\overline{CS}$  should be asserted.

- 2. On the rising edge of CCLK: If BUSY is Low, the data is accepted on this clock. If BUSY is High (from a previous write), the data is not accepted. Acceptance will instead occur on the first clock after BUSY goes Low, and the data must be held until this happens.

- 3. Repeat steps 1 and 2 until all the data has been sent.

- 4. De-assert  $\overline{\text{CS}}$  and  $\overline{\text{WRITE}}$ .

If CCLK is slower than  $\rm F_{CCNH},$  the FPGA will never assert BUSY. In this case, the above handshake is unnecessary, and data can simply be entered into the FPGA every CCLK cycle.

#### Figure 19: Loading Configuration Data for the Slave Parallel Mode

A configuration packet does not have to be written in one continuous stretch, rather it can be split into many write sequences. Each sequence would involve assertion of  $\overline{CS}$ .

In applications where multiple clock cycles may be required to access the configuration data before each byte can be loaded into the Slave Parallel interface, a new byte of data may not be ready for each consecutive CCLK edge. In such a case the  $\overline{CS}$  signal may be de-asserted until the next byte is valid on D0-D7. While  $\overline{CS}$  is High, the Slave Parallel interface does not expect any data and ignores all CCLK transitions. However, to avoid aborting configuration, WRITE must continue to be asserted while CS is asserted.

#### Abort

To abort configuration during a write sequence, de-assert  $\overline{\text{WRITE}}$  while holding  $\overline{\text{CS}}$  Low. The abort operation is initiated at the rising edge of CCLK, as shown in Figure 21, page 26. The device will remain BUSY until the aborted operation is complete. After aborting configuration, data is assumed to be unaligned to word boundaries and the FPGA requires a new synchronization word prior to accepting any new packets.

# **Boundary-Scan Mode**

In the boundary-scan mode, no nondedicated pins are required, configuration being done entirely through the IEEE 1149.1 Test Access Port.

Configuration through the TAP uses the special CFG\_IN instruction. This instruction allows data input on TDI to be converted into data packets for the internal configuration bus.

The following steps are required to configure the FPGA through the boundary-scan port.

- 1. Load the CFG\_IN instruction into the boundary-scan instruction register (IR)

- 2. Enter the Shift-DR (SDR) state

- 3. Shift a standard configuration bitstream into TDI

- 4. Return to Run-Test-Idle (RTI)

- 5. Load the JSTART instruction into IR

- 6. Enter the SDR state

- 7. Clock TCK through the sequence (the length is programmable)

- 8. Return to RTI

Configuration and readback via the TAP is always available. The boundary-scan mode simply locks out the other modes. The boundary-scan mode is selected by a <10x> on the mode pins (M0, M1, M2).

# Readback

The configuration data stored in the Spartan-II FPGA configuration memory can be readback for verification. Along with the configuration data it is possible to readback the contents of all flip-flops/latches, LUT RAMs, and block RAMs. This capability is used for real-time debugging.

For more detailed information see <u>XAPP176</u>, Spartan-II FPGA Family Configuration and Readback.

# Startup Delay Property

This property, STARTUP\_WAIT, takes on a value of TRUE or FALSE (the default value). When TRUE the Startup Sequence following device configuration is paused at a user-specified point until the DLL locks. <u>XAPP176</u>: *Configuration and Readback of the Spartan-II and Spartan-IIE Families* explains how this can result in delaying the assertion of the DONE pin until the DLL locks.

#### **DLL Location Constraints**

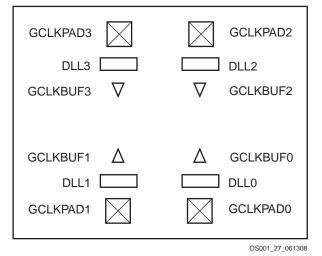

The DLLs are distributed such that there is one DLL in each corner of the device. The location constraint LOC, attached to the DLL primitive with the numeric identifier 0, 1, 2, or 3, controls DLL location. The orientation of the four DLLs and their corresponding clock resources appears in Figure 27.

The LOC property uses the following form.

LOC = DLL2

Figure 27: Orientation of DLLs

# **Design Considerations**

Use the following design considerations to avoid pitfalls and improve success designing with Xilinx devices.

# Input Clock

The output clock signal of a DLL, essentially a delayed version of the input clock signal, reflects any instability on the input clock in the output waveform. For this reason the quality of the DLL input clock relates directly to the quality of the output clock waveforms generated by the DLL. The DLL input clock requirements are specified in the "DLL Timing Parameters" section of the data sheet.

In most systems a crystal oscillator generates the system clock. The DLL can be used with any commercially available quartz crystal oscillator. For example, most crystal oscillators produce an output waveform with a frequency tolerance of 100 PPM, meaning 0.01 percent change in the clock period. The DLL operates reliably on an input waveform with a frequency drift of up to 1 ns — orders of magnitude in excess of that needed to support any crystal oscillator in the industry. However, the cycle-to-cycle jitter must be kept to less than 300 ps in the low frequencies and 150 ps for the high frequencies.

#### Input Clock Changes

Changing the period of the input clock beyond the maximum drift amount requires a manual reset of the CLKDLL. Failure to reset the DLL will produce an unreliable lock signal and output clock.

It is possible to stop the input clock in a way that has little impact to the DLL. Stopping the clock should be limited to less than approximately 100  $\mu$ s to keep device cooling to a minimum and maintain the validity of the current tap setting. The clock should be stopped during a Low phase, and when restored the full High period should be seen. During this time LOCKED will stay High and remain High when the clock is restored. If these conditions may not be met in the design, apply a manual reset to the DLL after re-starting the input clock, even if the LOCKED signal has not changed.

When the clock is stopped, one to four more clocks will still be observed as the delay line is flushed. When the clock is restarted, the output clocks will not be observed for one to four clocks as the delay line is filled. The most common case will be two or three clocks.

In a similar manner, a phase shift of the input clock is also possible. The phase shift will propagate to the output one to four clocks after the original shift, with no disruption to the CLKDLL control.

# **Output Clocks**

As mentioned earlier in the DLL pin descriptions, some restrictions apply regarding the connectivity of the output pins. The DLL clock outputs can drive an OBUF, a global clock buffer BUFG, or route directly to destination clock pins. The only BUFGs that the DLL clock outputs can drive are the two on the same edge of the device (top or bottom). One DLL output can drive more than one OBUF; however, this adds skew.

Do not use the DLL output clock signals until after activation of the LOCKED signal. Prior to the activation of the LOCKED signal, the DLL output clocks are not valid and can exhibit glitches, spikes, or other spurious movement.

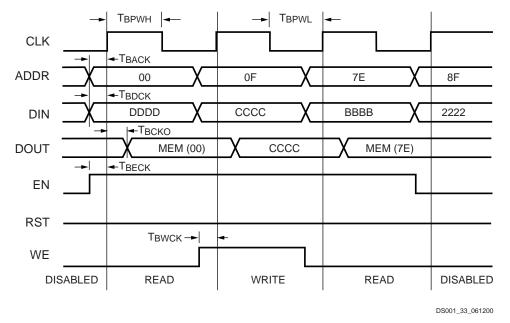

Figure 33: Timing Diagram for Single-Port Block RAM Memory

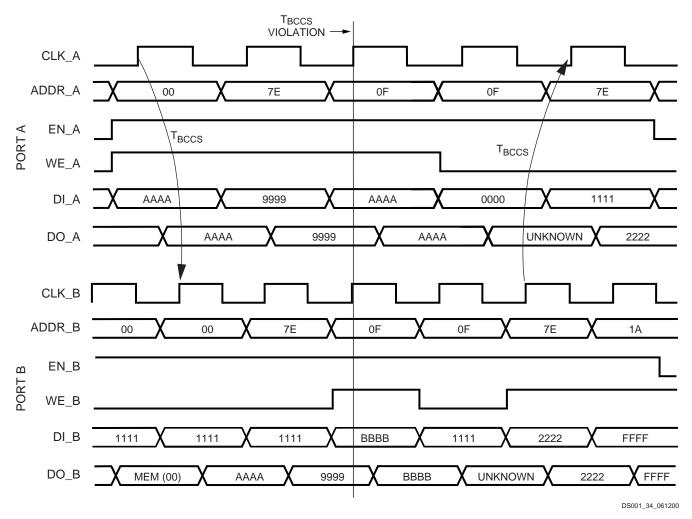

Figure 34: Timing Diagram for a True Dual-Port Read/Write Block RAM Memory

support of a wide variety of applications, from general purpose standard applications to high-speed low-voltage memory busses.

Versatile I/O blocks also provide selectable output drive strengths and programmable slew rates for the LVTTL output buffers, as well as an optional, programmable weak pull-up, weak pull-down, or weak "keeper" circuit ideal for use in external bussing applications.

Each Input/Output Block (IOB) includes three registers, one each for the input, output, and 3-state signals within the IOB. These registers are optionally configurable as either a D-type flip-flop or as a level sensitive latch.

The input buffer has an optional delay element used to guarantee a zero hold time requirement for input signals registered within the IOB.

The Versatile I/O features also provide dedicated resources for input reference voltage ( $V_{REF}$ ) and output source voltage ( $V_{CCO}$ ), along with a convenient banking system that simplifies board design.

By taking advantage of the built-in features and wide variety of I/O standards supported by the Versatile I/O features, system-level design and board design can be greatly simplified and improved.

# **Fundamentals**

Modern bus applications, pioneered by the largest and most influential companies in the digital electronics industry, are commonly introduced with a new I/O standard tailored specifically to the needs of that application. The bus I/O standards provide specifications to other vendors who create products designed to interface with these applications. Each standard often has its own specifications for current, voltage, I/O buffering, and termination techniques.

The ability to provide the flexibility and time-to-market advantages of programmable logic is increasingly dependent on the capability of the programmable logic device to support an ever increasing variety of I/O standards

The Versatile I/O resources feature highly configurable input and output buffers which provide support for a wide variety of I/O standards. As shown in Table 15, each buffer type can support a variety of voltage requirements.

# Table 15: Versatile I/O Supported Standards (Typical Values)

| ,                             | 1                                                    |                                                    | , , , , , , , , , , , , , , , , , , , ,               |

|-------------------------------|------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|

| I/O Standard                  | Input<br>Reference<br>Voltage<br>(V <sub>REF</sub> ) | Output<br>Source<br>Voltage<br>(V <sub>CCO</sub> ) | Board<br>Termination<br>Voltage<br>(V <sub>TT</sub> ) |

| LVTTL (2-24 mA)               | N/A                                                  | 3.3                                                | N/A                                                   |

| LVCMOS2                       | N/A                                                  | 2.5                                                | N/A                                                   |

| PCI (3V/5V,<br>33 MHz/66 MHz) | N/A                                                  | 3.3                                                | N/A                                                   |

| GTL                           | 0.8                                                  | N/A                                                | 1.2                                                   |

| GTL+                          | 1.0                                                  | N/A                                                | 1.5                                                   |

| HSTL Class I                  | 0.75                                                 | 1.5                                                | 0.75                                                  |

| HSTL Class III                | 0.9                                                  | 1.5                                                | 1.5                                                   |

| HSTL Class IV                 | 0.9                                                  | 1.5                                                | 1.5                                                   |

| SSTL3 Class I<br>and II       | 1.5                                                  | 3.3                                                | 1.5                                                   |

| SSTL2 Class I<br>and II       | 1.25                                                 | 2.5                                                | 1.25                                                  |

| CTT                           | 1.5                                                  | 3.3                                                | 1.5                                                   |

| AGP-2X                        | 1.32                                                 | 3.3                                                | N/A                                                   |

# **Overview of Supported I/O Standards**

This section provides a brief overview of the I/O standards supported by all Spartan-II devices.

While most I/O standards specify a range of allowed voltages, this document records typical voltage values only. Detailed information on each specification may be found on the Electronic Industry Alliance JEDEC website at <a href="http://www.jedec.org">http://www.jedec.org</a>. For more details on the I/O standards and termination application examples, see <a href="http://www.seetandards">XAPP179</a>, "Using SelectIO Interfaces in Spartan-II and Spartan-IIE FPGAs."

# LVTTL — Low-Voltage TTL

The Low-Voltage TTL (LVTTL) standard is a general purpose EIA/JESDSA standard for 3.3V applications that uses an LVTTL input buffer and a Push-Pull output buffer. This standard requires a 3.3V output source voltage ( $V_{CCO}$ ), but does not require the use of a reference voltage ( $V_{REF}$ ) or a termination voltage ( $V_{TT}$ ).

# LVCMOS2 — Low-Voltage CMOS for 2.5V

The Low-Voltage CMOS for 2.5V or lower (LVCMOS2) standard is an extension of the LVCMOS standard (JESD 8.5) used for general purpose 2.5V applications. This standard requires a 2.5V output source voltage ( $V_{CCO}$ ), but does not require the use of a reference voltage ( $V_{REF}$ ) or a board termination voltage ( $V_{TT}$ ).

# PCI — Peripheral Component Interface

The Peripheral Component Interface (PCI) standard specifies support for both 33 MHz and 66 MHz PCI bus applications. It uses a LVTTL input buffer and a push-pull output buffer. This standard does not require the use of a reference voltage ( $V_{REF}$ ) or a board termination voltage ( $V_{TT}$ ), however, it does require a 3.3V output source voltage ( $V_{CCO}$ ). I/Os configured for the PCI, 33 MHz, 5V standard are also 5V-tolerant.

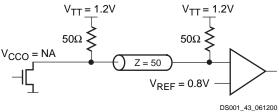

#### GTL — Gunning Transceiver Logic Terminated

The Gunning Transceiver Logic (GTL) standard is a high-speed bus standard (JESD8.3). Xilinx has implemented the terminated variation of this standard. This standard requires a differential amplifier input buffer and an open-drain output buffer.

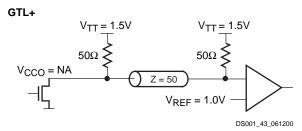

#### GTL+ — Gunning Transceiver Logic Plus

The Gunning Transceiver Logic Plus (GTL+) standard is a high-speed bus standard (JESD8.3).

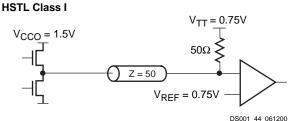

#### HSTL — High-Speed Transceiver Logic

The High-Speed Transceiver Logic (HSTL) standard is a general purpose high-speed, 1.5V bus standard (EIA/JESD 8-6). This standard has four variations or classes. Versatile I/O devices support Class I, III, and IV. This standard requires a Differential Amplifier input buffer and a Push-Pull output buffer.

#### SSTL3 — Stub Series Terminated Logic for 3.3V

The Stub Series Terminated Logic for 3.3V (SSTL3) standard is a general purpose 3.3V memory bus standard (JESD8-8). This standard has two classes, I and II. Versatile I/O devices support both classes for the SSTL3 standard. This standard requires a Differential Amplifier input buffer and an Push-Pull output buffer.

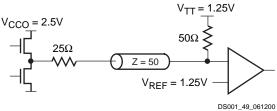

# SSTL2 — Stub Series Terminated Logic for 2.5V

The Stub Series Terminated Logic for 2.5V (SSTL2) standard is a general purpose 2.5V memory bus standard (JESD8-9). This standard has two classes, I and II. Versatile I/O devices support both classes for the SSTL2 standard. This standard requires a Differential Amplifier input buffer and an Push-Pull output buffer.

# CTT — Center Tap Terminated

The Center Tap Terminated (CTT) standard is a 3.3V memory bus standard (JESD8-4). This standard requires a Differential Amplifier input buffer and a Push-Pull output buffer.

#### AGP-2X — Advanced Graphics Port

The AGP standard is a 3.3V Advanced Graphics Port-2X bus standard used with processors for graphics applications. This standard requires a Push-Pull output buffer and a Differential Amplifier input buffer.

# **Library Primitives**

The Xilinx library includes an extensive list of primitives designed to provide support for the variety of Versatile I/O features. Most of these primitives represent variations of the five generic Versatile I/O primitives:

- IBUF (input buffer)

- IBUFG (global clock input buffer)

- OBUF (output buffer)

- OBUFT (3-state output buffer)

- IOBUF (input/output buffer)

These primitives are available with various extensions to define the desired I/O standard. However, it is recommended that customers use a a property or attribute on the generic primitive to specify the I/O standard. See "Versatile I/O Properties".

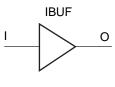

#### **IBUF**

Signals used as inputs to the Spartan-II device must source an input buffer (IBUF) via an external input port. The generic IBUF primitive appears in Figure 35. The assumed standard is LVTTL when the generic IBUF has no specified extension or property.

DS001\_35\_061200

Figure 35: Input Buffer (IBUF) Primitive

When the IBUF primitive supports an I/O standard such as LVTTL, LVCMOS, or PCI33\_5, the IBUF automatically configures as a 5V tolerant input buffer unless the V<sub>CCO</sub> for the bank is less than 2V. If the single-ended IBUF is placed in a bank with an HSTL standard (V<sub>CCO</sub> < 2V), the input buffer is not 5V tolerant.

The voltage reference signal is "banked" within the Spartan-II device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 36 for a representation of the I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input.

IBUF placement restrictions require that any differential amplifier input signals within a bank be of the same standard. How to specify a specific location for the IBUF via

# XILINX<sup>®</sup>

# GTL

A sample circuit illustrating a valid termination technique for GTL is shown in Figure 42. Table 20 lists DC voltage specifications for the GTL standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 42: Terminated GTL

#### Table 20: GTL Voltage Specifications

| Parameter                                       | Min  | Тур  | Max  |

|-------------------------------------------------|------|------|------|

| V <sub>CCO</sub>                                | -    | N/A  | -    |

| $V_{REF} = N \times V_{TT}^{(1)}$               | 0.74 | 0.8  | 0.86 |

| V <sub>TT</sub>                                 | 1.14 | 1.2  | 1.26 |

| $V_{IH} \ge V_{REF} + 0.05$                     | 0.79 | 0.85 | -    |

| $V_{IL} \leq V_{REF} - 0.05$                    | -    | 0.75 | 0.81 |

| V <sub>OH</sub>                                 | -    | -    | -    |

| V <sub>OL</sub>                                 | -    | 0.2  | 0.4  |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)         | -    | -    | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.4V | 32   | -    | -    |

| $I_{OL}$ at $V_{OL}$ (mA) at 0.2V               | -    | -    | 40   |

#### Notes:

1. N must be greater than or equal to 0.653 and less than or equal to 0.68.

# GTL+

A sample circuit illustrating a valid termination technique for GTL+ appears in Figure 43. DC voltage specifications appear in Table 21 for the GTL+ standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 43: Terminated GTL+

#### Table 21: GTL+ Voltage Specifications

| Parameter                                       | Min  | Тур  | Max  |

|-------------------------------------------------|------|------|------|

| V <sub>CCO</sub>                                | -    | -    | -    |

| $V_{REF} = N \times V_{TT}^{(1)}$               | 0.88 | 1.0  | 1.12 |

| V <sub>TT</sub>                                 | 1.35 | 1.5  | 1.65 |

| $V_{IH} \ge V_{REF} + 0.1$                      | 0.98 | 1.1  | -    |

| $V_{IL} \le V_{REF} - 0.1$                      | -    | 0.9  | 1.02 |

| V <sub>OH</sub>                                 | -    | -    | -    |

| V <sub>OL</sub>                                 | 0.3  | 0.45 | 0.6  |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)         | -    | -    | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.6V | 36   | -    | -    |

| $I_{OL}$ at $V_{OL}$ (mA) at 0.3V               | -    | -    | 48   |

#### Notes:

#### HSTL Class I

A sample circuit illustrating a valid termination technique for HSTL\_I appears in Figure 44. DC voltage specifications appear in Table 22 for the HSTL\_1 standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

DS001\_44\_061.

Figure 44: Terminated HSTL Class I

#### Table 22: HSTL Class I Voltage Specification

| Parameter                               | Min                    | Тур                 | Max             |

|-----------------------------------------|------------------------|---------------------|-----------------|

| V <sub>CCO</sub>                        | 1.40                   | 1.50                | 1.60            |

| V <sub>REF</sub>                        | 0.68                   | 0.75                | 0.90            |

| V <sub>TT</sub>                         | -                      | $V_{CCO} 	imes 0.5$ | -               |

| V <sub>IH</sub>                         | V <sub>REF</sub> + 0.1 | -                   | -               |

| V <sub>IL</sub>                         | -                      | -                   | $V_{REF} - 0.1$ |

| V <sub>OH</sub>                         | $V_{CCO} - 0.4$        | -                   | -               |

| V <sub>OL</sub>                         |                        |                     | 0.4             |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -8                     | -                   | -               |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 8                      | -                   | -               |

<sup>1.</sup> N must be greater than or equal to 0.653 and less than or equal to 0.68.

#### SSTL2\_I

A sample circuit illustrating a valid termination technique for SSTL2\_I appears in Figure 49. DC voltage specifications appear in Table 27 for the SSTL2\_I standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics

#### SSTL2 Class I

Figure 49: Terminated SSTL2 Class I

| Table | 27: | SSTL2_I | Voltage | Specifications |

|-------|-----|---------|---------|----------------|

|-------|-----|---------|---------|----------------|

| Parameter                                 | Min                 | Тур  | Max                |

|-------------------------------------------|---------------------|------|--------------------|

| V <sub>CCO</sub>                          | 2.3                 | 2.5  | 2.7                |

| $V_{REF} = 0.5 \times V_{CCO}$            | 1.15                | 1.25 | 1.35               |

| $V_{TT} = V_{REF} + N^{(1)}$              | 1.11                | 1.25 | 1.39               |

| $V_{IH} \ge V_{REF} + 0.18$               | 1.33                | 1.43 | 3.0 <sup>(2)</sup> |

| $V_{IL} \leq V_{REF} - 0.18$              | -0.3 <sup>(3)</sup> | 1.07 | 1.17               |

| V <sub>OH</sub> ≥ V <sub>REF</sub> + 0.61 | 1.76                | -    | -                  |

| $V_{OL} \leq V_{REF} - 0.61$              | -                   | -    | 0.74               |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)   | -7.6                | -    | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA)   | 7.6                 | -    | -                  |

#### Notes:

- 1. N must be greater than or equal to -0.04 and less than or equal to 0.04.

- 2.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3.

- 3. V<sub>IL</sub> minimum does not conform to the formula.

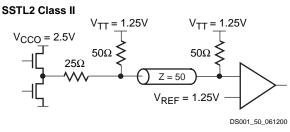

#### SSTL2 Class II

A sample circuit illustrating a valid termination technique for SSTL2\_II appears in Figure 50. DC voltage specifications appear in Table 28 for the SSTL2\_II standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 50: Terminated SSTL2 Class II

#### Table 28: SSTL2\_II Voltage Specifications

| Parameter                               | Min                 | Тур  | Max                |

|-----------------------------------------|---------------------|------|--------------------|

| V <sub>CCO</sub>                        | 2.3                 | 2.5  | 2.7                |

| $V_{REF} = 0.5 \times V_{CCO}$          | 1.15                | 1.25 | 1.35               |

| $V_{TT} = V_{REF} + N^{(1)}$            | 1.11                | 1.25 | 1.39               |

| $V_{IH} \ge V_{REF} + 0.18$             | 1.33                | 1.43 | 3.0 <sup>(2)</sup> |

| $V_{IL} \leq V_{REF} - 0.18$            | -0.3 <sup>(3)</sup> | 1.07 | 1.17               |

| $V_{OH} \ge V_{REF} + 0.8$              | 1.95                | -    | -                  |

| $V_{OL} \leq V_{REF} - 0.8$             | -                   | -    | 0.55               |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -15.2               | -    | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 15.2                | -    | -                  |

#### Notes:

- 1. N must be greater than or equal to -0.04 and less than or equal to 0.04.

- 2.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3.

- 3. V<sub>IL</sub> minimum does not conform to the formula.

# XILINX<sup>®</sup>

# LVTTL

LVTTL requires no termination. DC voltage specifications appears in Table 32 for the LVTTL standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

| Table | 32: | LVTTL | Voltage | Specifications |

|-------|-----|-------|---------|----------------|

|-------|-----|-------|---------|----------------|

| Parameter                               | Min  | Тур | Max |

|-----------------------------------------|------|-----|-----|

| V <sub>CCO</sub>                        | 3.0  | 3.3 | 3.6 |

| V <sub>REF</sub>                        | -    | -   | -   |

| V <sub>TT</sub>                         | -    | -   | -   |

| V <sub>IH</sub>                         | 2.0  | -   | 5.5 |

| V <sub>IL</sub>                         | -0.5 | -   | 0.8 |

| V <sub>OH</sub>                         | 2.4  | -   | -   |

| V <sub>OL</sub>                         | -    | -   | 0.4 |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -24  | -   | -   |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 24   | -   | -   |

#### Notes:

1.  $V_{OL}$  and  $V_{OH}$  for lower drive currents sample tested.

#### LVCMOS2

LVCMOS2 requires no termination. DC voltage specifications appear in Table 33 for the LVCMOS2 standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

#### Table 33: LVCMOS2 Voltage Specifications

| Parameter                               | Min  | Тур | Max |

|-----------------------------------------|------|-----|-----|

| V <sub>CCO</sub>                        | 2.3  | 2.5 | 2.7 |

| V <sub>REF</sub>                        | -    | -   | -   |

| V <sub>TT</sub>                         | -    | -   | -   |

| V <sub>IH</sub>                         | 1.7  | -   | 5.5 |

| V <sub>IL</sub>                         | -0.5 | -   | 0.7 |

| V <sub>OH</sub>                         | 1.9  | -   | -   |

| V <sub>OL</sub>                         | -    | -   | 0.4 |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -12  | -   | -   |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 12   | -   | -   |

#### AGP-2X

The specification for the AGP-2X standard does not document a recommended termination technique. DC voltage specifications appear in Table 34 for the AGP-2X standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

#### Table 34: AGP-2X Voltage Specifications

| Parameter                               | Min    | Тур  | Max  |

|-----------------------------------------|--------|------|------|

| V <sub>CCO</sub>                        | 3.0    | 3.3  | 3.6  |

| $V_{REF} = N \times V_{CCO}^{(1)}$      | 1.17   | 1.32 | 1.48 |

| V <sub>TT</sub>                         | -      | -    | -    |

| $V_{IH} \ge V_{REF} + 0.2$              | 1.37   | 1.52 | -    |

| $V_{IL} \le V_{REF} - 0.2$              | -      | 1.12 | 1.28 |

| $V_{OH} \ge 0.9 \times V_{CCO}$         | 2.7    | 3.0  | -    |

| $V_{OL} \le 0.1 \times V_{CCO}$         | -      | 0.33 | 0.36 |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | Note 2 | -    | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | Note 2 | -    | -    |

#### Notes:

For design examples and more information on using the I/O, see <u>XAPP179</u>, Using SelectIO Interfaces in Spartan-II and Spartan-IIE FPGAs.

<sup>1.</sup> N must be greater than or equal to 0.39 and less than or equal to 0.41.

<sup>2.</sup> Tested according to the relevant specification.

| Input/Output |        | V <sub>IL</sub>        | V                      | н      | V <sub>OL</sub>        | V <sub>OH</sub>        | I <sub>OL</sub> | I <sub>ОН</sub> |

|--------------|--------|------------------------|------------------------|--------|------------------------|------------------------|-----------------|-----------------|

| Standard     | V, Min | V, Max                 | V, Min                 | V, Max | V, Max                 | V, Min                 | mA              | mA              |

| CTT          | -0.5   | V <sub>REF</sub> – 0.2 | V <sub>REF</sub> + 0.2 | 3.6    | V <sub>REF</sub> – 0.4 | V <sub>REF</sub> + 0.4 | 8               | -8              |

| AGP          | -0.5   | V <sub>REF</sub> – 0.2 | V <sub>REF</sub> + 0.2 | 3.6    | 10% V <sub>CCO</sub>   | 90% V <sub>CCO</sub>   | Note (2)        | Note (2)        |

#### Notes:

1. V<sub>OL</sub> and V<sub>OH</sub> for lower drive currents are sample tested.

2. Tested according to the relevant specifications.

# **Switching Characteristics**

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all Spartan-II devices unless otherwise noted.

# Global Clock Input to Output Delay for LVTTL, with DLL (Pin-to-Pin)<sup>(1)</sup>

|                       |                                                                                                                    |        | S   | peed Grac | le  |       |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|--------|-----|-----------|-----|-------|

|                       |                                                                                                                    |        | All | -6        | -5  |       |

| Symbol                | Description                                                                                                        | Device | Min | Max       | Max | Units |

| T <sub>ICKOFDLL</sub> | Global clock input to output delay<br>using output flip-flop for LVTTL,<br>12 mA, fast slew rate, <i>with</i> DLL. | All    |     | 2.9       | 3.3 | ns    |

#### Notes:

1. Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

- Output timing is measured at 1.4V with 35 pF external capacitive load for LVTTL. The 35 pF load does not apply to the Min values. For other I/O standards and different loads, see the tables "Constants for Calculating TIOOP" and "Delay Measurement Methodology," page 60.

- 3. DLL output jitter is already included in the timing calculation.

- 4. For data *output* with different standards, adjust delays with the values shown in "IOB Output Delay Adjustments for Different Standards," page 59. For a global clock input with standards other than LVTTL, adjust delays with values from the "I/O Standard Global Clock Input Adjustments," page 61.

# Global Clock Input to Output Delay for LVTTL, *without* DLL (Pin-to-Pin)<sup>(1)</sup>

|                    |                                            |         | Speed Grade |     |     |       |

|--------------------|--------------------------------------------|---------|-------------|-----|-----|-------|

|                    |                                            |         | All         | -6  | -5  | -     |

| Symbol             | Description                                | Device  | Min         | Max | Max | Units |

| T <sub>ICKOF</sub> | Global clock input to output delay         | XC2S15  |             | 4.5 | 5.4 | ns    |

|                    | using output flip-flop for LVTTL,          | XC2S30  |             | 4.5 | 5.4 | ns    |

|                    | 12 mA, fast slew rate, <i>without</i> DLL. | XC2S50  |             | 4.5 | 5.4 | ns    |

|                    |                                            | XC2S100 |             | 4.6 | 5.5 | ns    |

|                    |                                            | XC2S150 |             | 4.6 | 5.5 | ns    |

|                    |                                            | XC2S200 |             | 4.7 | 5.6 | ns    |

Notes:

1. Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

Output timing is measured at 1.4V with 35 pF external capacitive load for LVTTL. The 35 pF load does not apply to the Min values. For other I/O standards and different loads, see the tables "Constants for Calculating TIOOP" and "Delay Measurement Methodology," page 60.

For data *output* with different standards, adjust delays with the values shown in "IOB Output Delay Adjustments for Different Standards," page 59. For a global clock input with standards other than LVTTL, adjust delays with values from the "I/O Standard Global Clock Input Adjustments," page 61.

# IOB Input Delay Adjustments for Different Standards<sup>(1)</sup>

Input delays associated with the pad are specified for LVTTL. For other standards, adjust the delays by the values shown. A delay adjusted in this way constitutes a worst-case limit.

|                       |                                    |                   | Speed | Grade |       |  |  |  |  |

|-----------------------|------------------------------------|-------------------|-------|-------|-------|--|--|--|--|

| Symbol                | Description                        | Standard          | -6    | -5    | Units |  |  |  |  |

| Data Input I          | Data Input Delay Adjustments       |                   |       |       |       |  |  |  |  |

| T <sub>ILVTTL</sub>   | Standard-specific data input delay | LVTTL             | 0     | 0     | ns    |  |  |  |  |

| T <sub>ILVCMOS2</sub> | adjustments                        | LVCMOS2           | -0.04 | -0.05 | ns    |  |  |  |  |

| T <sub>IPCI33_3</sub> |                                    | PCI, 33 MHz, 3.3V | -0.11 | -0.13 | ns    |  |  |  |  |

| T <sub>IPCI33_5</sub> | -                                  | PCI, 33 MHz, 5.0V | 0.26  | 0.30  | ns    |  |  |  |  |

| T <sub>IPCI66_3</sub> | -                                  | PCI, 66 MHz, 3.3V | -0.11 | -0.13 | ns    |  |  |  |  |

| T <sub>IGTL</sub>     | -                                  | GTL               | 0.20  | 0.24  | ns    |  |  |  |  |

| T <sub>IGTLP</sub>    | -                                  | GTL+              | 0.11  | 0.13  | ns    |  |  |  |  |

| T <sub>IHSTL</sub>    | -                                  | HSTL              | 0.03  | 0.04  | ns    |  |  |  |  |

| T <sub>ISSTL2</sub>   | -                                  | SSTL2             | -0.08 | -0.09 | ns    |  |  |  |  |

| T <sub>ISSTL3</sub>   | -                                  | SSTL3             | -0.04 | -0.05 | ns    |  |  |  |  |

| T <sub>ICTT</sub>     |                                    | CTT               | 0.02  | 0.02  | ns    |  |  |  |  |

| T <sub>IAGP</sub>     | ]                                  | AGP               | -0.06 | -0.07 | ns    |  |  |  |  |

Notes:

1. Input timing for LVTTL is measured at 1.4V. For other I/O standards, see the table "Delay Measurement Methodology," page 60.

# Calculation of T<sub>IOOP</sub> as a Function of Capacitance

$T_{\rm IOOP}$  is the propagation delay from the O Input of the IOB to the pad. The values for  $T_{\rm IOOP}$  are based on the standard capacitive load (C<sub>SL</sub>) for each I/O standard as listed in the table "Constants for Calculating TIOOP", below.

For other capacitive loads, use the formulas below to calculate an adjusted propagation delay,  $T_{IOOP1}$ .

$$T_{IOOP1} = T_{IOOP} + Adj + (C_{LOAD} - C_{SL}) * F_{L}$$

Where:

Adj is selected from "IOB Output Delay Adjustments for Different Standards", page 59, according to the I/O standard used

$C_{\text{LOAD}}\,$  is the capacitive load for the design

F<sub>L</sub> is the capacitance scaling factor

#### **Delay Measurement Methodology**

| Standard       | V <sub>L</sub> (1)                            | V <sub>H</sub> (1)                            | Meas.<br>Point   | V <sub>REF</sub><br>Typ <sup>(2)</sup> |

|----------------|-----------------------------------------------|-----------------------------------------------|------------------|----------------------------------------|

| LVTTL          | 0                                             | 3                                             | 1.4              | -                                      |

| LVCMOS2        | 0                                             | 2.5                                           | 1.125            | -                                      |

| PCI33_5        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| PCI33_3        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| PCI66_3        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| GTL            | V <sub>REF</sub> - 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 0.80                                   |

| GTL+           | V <sub>REF</sub> - 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 1.0                                    |

| HSTL Class I   | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.75                                   |

| HSTL Class III | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.90                                   |

| HSTL Class IV  | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.90                                   |

| SSTL3 I and II | V <sub>REF</sub> – 1.0                        | V <sub>REF</sub> + 1.0                        | $V_{REF}$        | 1.5                                    |

| SSTL2 I and II | V <sub>REF</sub> -0.75                        | V <sub>REF</sub> + 0.75                       | $V_{REF}$        | 1.25                                   |

| СТТ            | V <sub>REF</sub> – 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 1.5                                    |

| AGP            | V <sub>REF</sub> –<br>(0.2xV <sub>CCO</sub> ) | V <sub>REF</sub> +<br>(0.2xV <sub>CCO</sub> ) | V <sub>REF</sub> | Per AGP<br>Spec                        |

#### Notes:

- 1. Input waveform switches between V<sub>L</sub> and V<sub>H</sub>.

- 2. Measurements are made at V<sub>REF</sub> Typ, Maximum, and Minimum. Worst-case values are reported.

- I/O parameter measurements are made with the capacitance values shown in the table, "Constants for Calculating TIOOP". See Xilinx application note <u>XAPP179</u> for the appropriate terminations.

- 4. I/O standard measurements are reflected in the IBIS model information except where the IBIS format precludes it.

# Constants for Calculating T<sub>IOOP</sub>

| Standard                          | C <sub>SL</sub> <sup>(1)</sup><br>(pF) | F <sub>L</sub><br>(ns/pF) |

|-----------------------------------|----------------------------------------|---------------------------|

| LVTTL Fast Slew Rate, 2 mA drive  | 35                                     | 0.41                      |

| LVTTL Fast Slew Rate, 4 mA drive  | 35                                     | 0.20                      |

| LVTTL Fast Slew Rate, 6 mA drive  | 35                                     | 0.13                      |

| LVTTL Fast Slew Rate, 8 mA drive  | 35                                     | 0.079                     |

| LVTTL Fast Slew Rate, 12 mA drive | 35                                     | 0.044                     |

| LVTTL Fast Slew Rate, 16 mA drive | 35                                     | 0.043                     |

| LVTTL Fast Slew Rate, 24 mA drive | 35                                     | 0.033                     |

| LVTTL Slow Slew Rate, 2 mA drive  | 35                                     | 0.41                      |

| LVTTL Slow Slew Rate, 4 mA drive  | 35                                     | 0.20                      |

| LVTTL Slow Slew Rate, 6 mA drive  | 35                                     | 0.100                     |

| LVTTL Slow Slew Rate, 8 mA drive  | 35                                     | 0.086                     |

| LVTTL Slow Slew Rate, 12 mA drive | 35                                     | 0.058                     |

| LVTTL Slow Slew Rate, 16 mA drive | 35                                     | 0.050                     |

| LVTTL Slow Slew Rate, 24 mA drive | 35                                     | 0.048                     |

| LVCMOS2                           | 35                                     | 0.041                     |

| PCI 33 MHz 5V                     | 50                                     | 0.050                     |

| PCI 33 MHZ 3.3V                   | 10                                     | 0.050                     |

| PCI 66 MHz 3.3V                   | 10                                     | 0.033                     |

| GTL                               | 0                                      | 0.014                     |

| GTL+                              | 0                                      | 0.017                     |

| HSTL Class I                      | 20                                     | 0.022                     |

| HSTL Class III                    | 20                                     | 0.016                     |

| HSTL Class IV                     | 20                                     | 0.014                     |

| SSTL2 Class I                     | 30                                     | 0.028                     |

| SSTL2 Class II                    | 30                                     | 0.016                     |

| SSTL3 Class I                     | 30                                     | 0.029                     |

| SSTL3 Class II                    | 30                                     | 0.016                     |

| СТТ                               | 20                                     | 0.035                     |

| AGP                               | 10                                     | 0.037                     |

#### Notes:

- 1. I/O parameter measurements are made with the capacitance values shown above. See Xilinx application note <u>XAPP179</u> for the appropriate terminations.

- 2. I/O standard measurements are reflected in the IBIS model information except where the IBIS format precludes it.

# XC2S30 Device Pinouts (Continued)

| XC2S30 Pad Name       |      |       |       |       |       | Bndry |

|-----------------------|------|-------|-------|-------|-------|-------|

| Function              | Bank | VQ100 | TQ144 | CS144 | PQ208 | Scan  |

| V <sub>CCINT</sub>    | -    | P85   | P24   | A9    | P171  | -     |

| I/O                   | 1    | -     | P23   | D8    | P172  | 24    |

| I/O                   | 1    | -     | P22   | C8    | P173  | 27    |

| I/O                   | 1    | -     | -     | -     | P174  | 30    |

| I/O                   | 1    | -     | -     | -     | P175  | 33    |

| I/O                   | 1    | -     | -     | -     | P176  | 36    |

| GND                   | -    | -     | -     | -     | P177  | -     |

| I/O, V <sub>REF</sub> | 1    | P86   | P21   | B8    | P178  | 39    |

| I/O                   | 1    | -     | -     | -     | P179  | 42    |

| I/O                   | 1    | -     | P20   | A8    | P180  | 45    |

| I/O                   | 1    | P87   | P19   | B7    | P181  | 48    |

| I, GCK2               | 1    | P88   | P18   | A7    | P182  | 54    |

| GND                   | -    | P89   | P17   | C7    | P183  | -     |

| V <sub>CCO</sub>      | 1    | P90   | P16   | D7    | P184  | -     |

| V <sub>CCO</sub>      | 0    | P90   | P16   | D7    | P184  | -     |

| I, GCK3               | 0    | P91   | P15   | A6    | P185  | 55    |

| V <sub>CCINT</sub>    | -    | P92   | P14   | B6    | P186  | -     |

| I/O                   | 0    | -     | P13   | C6    | P187  | 62    |

| I/O                   | 0    | -     | -     | -     | P188  | 65    |

| I/O, V <sub>REF</sub> | 0    | P93   | P12   | D6    | P189  | 68    |

| GND                   | -    | -     | -     | -     | P190  | -     |

| I/O                   | 0    | -     | -     | -     | P191  | 71    |

| I/O                   | 0    | -     | -     | -     | P192  | 74    |

| I/O                   | 0    | -     | -     | -     | P193  | 77    |

| I/O                   | 0    | -     | P11   | A5    | P194  | 80    |

| I/O                   | 0    | -     | P10   | B5    | P195  | 83    |

| V <sub>CCINT</sub>    | -    | P94   | P9    | C5    | P196  | -     |

| V <sub>CCO</sub>      | 0    | -     | -     | -     | P197  | -     |

| GND                   | -    | -     | P8    | D5    | P198  | -     |

| I/O                   | 0    | P95   | P7    | A4    | P199  | 86    |

| I/O                   | 0    | P96   | P6    | B4    | P200  | 89    |

| I/O                   | 0    | -     | -     | -     | P201  | 92    |

# XC2S30 Device Pinouts (Continued)

| XC2S30 Pad Name       |      |       |       |       |       | Bndry |

|-----------------------|------|-------|-------|-------|-------|-------|

| Function              | Bank | VQ100 | TQ144 | CS144 | PQ208 | Scan  |

| I/O, V <sub>REF</sub> | 0    | P97   | P5    | C4    | P203  | 95    |

| I/O                   | 0    | -     | -     | -     | P204  | 98    |

| I/O                   | 0    | -     | P4    | A3    | P205  | 101   |

| I/O                   | 0    | P98   | P3    | B3    | P206  | 104   |

| тск                   | -    | P99   | P2    | C3    | P207  | -     |

| V <sub>CCO</sub>      | 0    | P100  | P1    | A2    | P208  | -     |

| V <sub>CCO</sub>      | 7    | P100  | P144  | B2    | P208  | -     |

04/18/01

#### Notes:

- 1. IRDY and TRDY can only be accessed when using Xilinx PCI cores.

- 2. See "VCCO Banks" for details on  $V_{CCO}$  banking.

# Additional XC2S30 Package Pins

#### VQ100

| Not Connected Pins |          |  |  |  |  |  |  |  |  |

|--------------------|----------|--|--|--|--|--|--|--|--|

| P28                | P28 P29  |  |  |  |  |  |  |  |  |

| 11/02/00           | 11/02/00 |  |  |  |  |  |  |  |  |

#### TQ144

| Not Connected Pins |           |  |  |  |  |  |  |  |

|--------------------|-----------|--|--|--|--|--|--|--|

| P104               | P104 P105 |  |  |  |  |  |  |  |

| 11/02/00           |           |  |  |  |  |  |  |  |

#### CS144

| Not Connected Pins |       |  |  |  |  |  |  |  |  |

|--------------------|-------|--|--|--|--|--|--|--|--|

| M3                 | M3 N3 |  |  |  |  |  |  |  |  |

| 11/02/00           |       |  |  |  |  |  |  |  |  |

#### PQ208

| Not Connected Pins |      |      |      |      |      |  |  |  |

|--------------------|------|------|------|------|------|--|--|--|

| P7                 | P13  | P38  | P44  | P55  | P56  |  |  |  |

| P60                | P97  | P112 | P118 | P143 | P149 |  |  |  |

| P165               | P202 | -    | -    | -    | -    |  |  |  |

| 11/02/00           |      |      |      |      |      |  |  |  |

#### Notes:

1. For the PQ208 package, P13, P38, P118, and P143, which are Not Connected Pins on the XC2S30, are assigned to  $V_{\rm CCINT}$  on larger devices.

# XC2S50 Device Pinouts (Continued)

| XC2S50 Pad Name       |      |       |       |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | Scan  |

| I/O                   | 0    | -     | -     | D8                          | 83    |

| I/O                   | 0    | -     | P188  | A6                          | 86    |

| I/O, V <sub>REF</sub> | 0    | P12   | P189  | B7                          | 89    |

| GND                   | -    | -     | P190  | GND*                        | -     |

| I/O                   | 0    | -     | P191  | C8                          | 92    |

| I/O                   | 0    | -     | P192  | D7                          | 95    |

| I/O                   | 0    | -     | P193  | E7                          | 98    |

| I/O                   | 0    | P11   | P194  | C7                          | 104   |

| I/O                   | 0    | P10   | P195  | B6                          | 107   |

| V <sub>CCINT</sub>    | -    | P9    | P196  | V <sub>CCINT</sub> *        | -     |

| V <sub>CCO</sub>      | 0    | -     | P197  | V <sub>CCO</sub><br>Bank 0* | -     |

| GND                   | -    | P8    | P198  | GND*                        | -     |

| I/O                   | 0    | P7    | P199  | A5                          | 110   |

| I/O                   | 0    | P6    | P200  | C6                          | 113   |

| I/O                   | 0    | -     | P201  | B5                          | 116   |

| I/O                   | 0    | -     | -     | D6                          | 119   |

| I/O                   | 0    | -     | P202  | A4                          | 122   |

| I/O, V <sub>REF</sub> | 0    | P5    | P203  | B4                          | 125   |

| GND                   | -    | -     | -     | GND*                        | -     |

| I/O                   | 0    | -     | P204  | E6                          | 128   |

| I/O                   | 0    | -     | -     | D5                          | 131   |

| I/O                   | 0    | P4    | P205  | A3                          | 134   |

| I/O                   | 0    | -     | -     | C5                          | 137   |

| I/O                   | 0    | P3    | P206  | B3                          | 140   |

| TCK                   | -    | P2    | P207  | C4                          | -     |

| V <sub>cco</sub>      | 0    | P1    | P208  | V <sub>CCO</sub><br>Bank 0* | -     |

| V <sub>CCO</sub>      | 7    | P144  | P208  | V <sub>CCO</sub><br>Bank 7* | -     |

04/18/01

#### Notes:

- 1. IRDY and TRDY can only be accessed when using Xilinx PCI cores.

- Pads labelled GND\*, V<sub>CCINT</sub>\*, V<sub>CCO</sub> Bank 0\*, V<sub>CCO</sub> Bank 1\*, V<sub>CCO</sub> Bank 2\*, V<sub>CCO</sub> Bank 3\*, V<sub>CCO</sub> Bank 4\*, V<sub>CCO</sub> Bank 5\*, V<sub>CCO</sub> Bank 6\*, V<sub>CCO</sub> Bank 7\* are internally bonded to independent ground or power planes within the package.

- 3. See "VCCO Banks" for details on  $V_{CCO}$  banking.

# Additional XC2S50 Package Pins

| TQ144 |  |

|-------|--|

|-------|--|

| Not Connected Pins |      |   |   |   |   |  |  |  |

|--------------------|------|---|---|---|---|--|--|--|

| P104               | P105 | - | - | - | - |  |  |  |

| 11/02/00           |      |   |   |   |   |  |  |  |

# **XC2S150 Device Pinouts**

| XC2S150 Pa            | d Name |       |                             |                             | Bndry |

|-----------------------|--------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank   | PQ208 | FG256                       | FG456                       | Scan  |

| GND                   | -      | P1    | GND*                        | GND*                        | -     |

| TMS                   | -      | P2    | D3                          | D3                          | -     |

| I/O                   | 7      | P3    | C2                          | B1                          | 221   |

| I/O                   | 7      | -     | -                           | E4                          | 224   |

| I/O                   | 7      | -     | -                           | C1                          | 227   |

| I/O                   | 7      | -     | A2                          | F5                          | 230   |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| I/O                   | 7      | P4    | B1                          | D2                          | 233   |

| I/O                   | 7      | -     | -                           | E3                          | 236   |

| I/O                   | 7      | -     | -                           | F4                          | 239   |

| I/O                   | 7      | -     | E3                          | G5                          | 242   |

| I/O                   | 7      | P5    | D2                          | F3                          | 245   |

| GND                   | -      | -     | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 7      | -     | V <sub>CCO</sub><br>Bank 7* | V <sub>CCO</sub><br>Bank 7* | -     |

| I/O, V <sub>REF</sub> | 7      | P6    | C1                          | E2                          | 248   |

| I/O                   | 7      | P7    | F3                          | E1                          | 251   |

| I/O                   | 7      | -     | -                           | G4                          | 254   |

| I/O                   | 7      | -     | -                           | G3                          | 257   |

| I/O                   | 7      | -     | E2                          | H5                          | 260   |

| I/O                   | 7      | P8    | E4                          | F2                          | 263   |

| I/O                   | 7      | -     | -                           | F1                          | 266   |

| I/O, V <sub>REF</sub> | 7      | P9    | D1                          | H4                          | 269   |

| I/O                   | 7      | P10   | E1                          | G1                          | 272   |

| GND                   | -      | P11   | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 7      | P12   | V <sub>CCO</sub><br>Bank 7* | V <sub>CCO</sub><br>Bank 7* | -     |

| V <sub>CCINT</sub>    | -      | P13   | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| I/O                   | 7      | P14   | F2                          | H3                          | 275   |

| I/O                   | 7      | P15   | G3                          | H2                          | 278   |

| I/O                   | 7      | -     | -                           | H1                          | 284   |

| I/O                   | 7      | -     | F1                          | J5                          | 287   |

| I/O                   | 7      | P16   | F4                          | J2                          | 290   |

| I/O                   | 7      | -     | -                           | J3                          | 293   |

| I/O                   | 7      | P17   | F5                          | K5                          | 299   |

| I/O                   | 7      | P18   | G2                          | K1                          | 302   |

| GND                   | -      | P19   | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 7      | -     | V <sub>CCO</sub><br>Bank 7* | V <sub>CCO</sub><br>Bank 7* | -     |

| I/O, V <sub>REF</sub> | 7      | P20   | H3                          | K3                          | 305   |

| I/O                   | 7      | P21   | G4                          | K4                          | 308   |

| I/O                   | 7      | -     | H2                          | L6                          | 311   |

# XC2S150 Device Pinouts (Continued)

| Function   I/O   I/O   I/O   I/O, IRDY <sup>(1)</sup> GND | Bank<br>7<br>7<br>7<br>7<br>7<br>- | PQ208<br>P22<br>-<br>P23 | <b>FG256</b><br>G5          | <b>FG456</b><br>L1          | Bndry<br>Scan<br>314 |

|-----------------------------------------------------------|------------------------------------|--------------------------|-----------------------------|-----------------------------|----------------------|

| I/O<br>I/O<br>I/O, IRDY <sup>(1)</sup><br>GND             | 7<br>7                             | -                        |                             |                             | 314                  |

| I/O<br>I/O, IRDY <sup>(1)</sup><br>GND                    | 7                                  |                          | -                           |                             |                      |

| I/O, IRDY <sup>(1)</sup><br>GND                           |                                    | P23                      | 1                           | L5                          | 317                  |

| GND                                                       | 7                                  |                          | H4                          | L4                          | 320                  |

|                                                           | -                                  | P24                      | G1                          | L3                          | 323                  |

| M                                                         |                                    | P25                      | GND*                        | GND*                        | -                    |

| V <sub>CCO</sub>                                          | 7                                  | P26                      | V <sub>CCO</sub><br>Bank 7* | V <sub>CCO</sub><br>Bank 7* | -                    |

| V <sub>CCO</sub>                                          | 6                                  | P26                      | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -                    |

| I/O, TRDY <sup>(1)</sup>                                  | 6                                  | P27                      | J2                          | M1                          | 326                  |

| V <sub>CCINT</sub>                                        | -                                  | P28                      | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -                    |

| I/O                                                       | 6                                  | -                        | -                           | M6                          | 332                  |

| I/O                                                       | 6                                  | P29                      | H1                          | M3                          | 335                  |

| I/O                                                       | 6                                  | -                        | J4                          | M4                          | 338                  |

| I/O                                                       | 6                                  | P30                      | J1                          | M5                          | 341                  |

| I/O, V <sub>REF</sub>                                     | 6                                  | P31                      | J3                          | N2                          | 344                  |

| V <sub>CCO</sub>                                          | 6                                  | -                        | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -                    |

| GND                                                       | -                                  | P32                      | GND*                        | GND*                        | -                    |

| I/O                                                       | 6                                  | P33                      | K5                          | N3                          | 347                  |

| I/O                                                       | 6                                  | P34                      | K2                          | N4                          | 350                  |

| I/O                                                       | 6                                  | -                        | -                           | N5                          | 356                  |

| I/O                                                       | 6                                  | P35                      | K1                          | P2                          | 359                  |

| I/O                                                       | 6                                  | -                        | K3                          | P4                          | 362                  |

| I/O                                                       | 6                                  | -                        | -                           | R1                          | 365                  |

| I/O                                                       | 6                                  | P36                      | L1                          | P3                          | 371                  |

| I/O                                                       | 6                                  | P37                      | L2                          | R2                          | 374                  |

| V <sub>CCINT</sub>                                        | -                                  | P38                      | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -                    |

| V <sub>CCO</sub>                                          | 6                                  | P39                      | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -                    |

| GND                                                       | -                                  | P40                      | GND*                        | GND*                        | -                    |

| I/O                                                       | 6                                  | P41                      | K4                          | T1                          | 377                  |

| I/O, V <sub>REF</sub>                                     | 6                                  | P42                      | M1                          | R4                          | 380                  |

| I/O                                                       | 6                                  | -                        | -                           | T2                          | 383                  |

| I/O                                                       | 6                                  | P43                      | L4                          | U1                          | 386                  |

| I/O                                                       | 6                                  | -                        | M2                          | R5                          | 389                  |

| I/O                                                       | 6                                  | -                        | -                           | V1                          | 392                  |

| I/O                                                       | 6                                  | -                        | -                           | T5                          | 395                  |

| I/O                                                       | 6                                  | P44                      | L3                          | U2                          | 398                  |

| I/O, V <sub>REF</sub>                                     | 6                                  | P45                      | N1                          | Т3                          | 401                  |

| V <sub>CCO</sub>                                          | 6                                  | -                        | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -                    |

| GND                                                       | -                                  | -                        | GND*                        | GND*                        | -                    |

# XC2S200 Device Pinouts (Continued)

| XC2S200 Pac           |      |       |                             |                             |               |

|-----------------------|------|-------|-----------------------------|-----------------------------|---------------|

| Function              | Bank | PQ208 | FG256                       | FG456                       | Bndry<br>Scan |

| I, GCK0               | 4    | P80   | N8                          | W12                         | 636           |

| I/O                   | 4    | P81   | N9                          | U12                         | 640           |

| I/O                   | 4    | -     | -                           | V12                         | 646           |

| I/O                   | 4    | P82   | R9                          | Y12                         | 649           |

| I/O                   | 4    | -     | N10                         | AA12                        | 652           |

| I/O                   | 4    | -     | -                           | W13                         | 655           |

| I/O                   | 4    | P83   | Т9                          | AB13                        | 661           |

| I/O, V <sub>REF</sub> | 4    | P84   | P9                          | AA13                        | 664           |

| V <sub>CCO</sub>      | 4    | -     | V <sub>CCO</sub><br>Bank 4* | V <sub>CCO</sub><br>Bank 4* | -             |