# E·XFL

#### AMD Xilinx - XC2S50-5TQG144I Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| D | eta | ail | s |

|---|-----|-----|---|

| _ |     |     | - |

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | 384                                                         |

| Number of Logic Elements/Cells | 1728                                                        |

| Total RAM Bits                 | 32768                                                       |

| Number of I/O                  | 92                                                          |

| Number of Gates                | 50000                                                       |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                          |

| Package / Case                 | 144-LQFP                                                    |

| Supplier Device Package        | 144-TQFP (20x20)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s50-5tqg144i |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#

DS001-1 (v2.8) June 13, 2008

# Spartan-II FPGA Family: Introduction and Ordering Information

#### **Product Specification**

# Introduction

The Spartan<sup>®</sup>-II Field-Programmable Gate Array family gives users high performance, abundant logic resources, and a rich feature set, all at an exceptionally low price. The six-member family offers densities ranging from 15,000 to 200,000 system gates, as shown in Table 1. System performance is supported up to 200 MHz. Features include block RAM (to 56K bits), distributed RAM (to 75,264 bits), 16 selectable I/O standards, and four DLLs. Fast, predictable interconnect means that successive design iterations continue to meet timing requirements.

The Spartan-II family is a superior alternative to mask-programmed ASICs. The FPGA avoids the initial cost, lengthy development cycles, and inherent risk of conventional ASICs. Also, FPGA programmability permits design upgrades in the field with no hardware replacement necessary (impossible with ASICs).

# **Features**

- Second generation ASIC replacement technology

- Densities as high as 5,292 logic cells with up to 200,000 system gates

- Streamlined features based on Virtex<sup>®</sup> FPGA architecture

- Unlimited reprogrammability

- Very low cost

- Cost-effective 0.18 micron process

- System level features

- SelectRAM<sup>™</sup> hierarchical memory:

- · 16 bits/LUT distributed RAM

- Configurable 4K bit block RAM

- Fast interfaces to external RAM

- Fully PCI compliant

- Low-power segmented routing architecture

- Full readback ability for verification/observability

- Dedicated carry logic for high-speed arithmetic

- Efficient multiplier support

- Cascade chain for wide-input functions

- Abundant registers/latches with enable, set, reset

- Four dedicated DLLs for advanced clock control

- Four primary low-skew global clock distribution nets

- IEEE 1149.1 compatible boundary scan logic

- Versatile I/O and packaging

- Pb-free package options

- Low-cost packages available in all densities

- Family footprint compatibility in common packages

- 16 high-performance interface standards

- Hot swap Compact PCI friendly

- Zero hold time simplifies system timing

- Core logic powered at 2.5V and I/Os powered at 1.5V, 2.5V, or 3.3V

- Fully supported by powerful Xilinx<sup>®</sup> ISE<sup>®</sup> development system

- Fully automatic mapping, placement, and routing

| Table 1: Spartan-II FPGA Family Members |                |                                 |                         |               |                                                 |                                  |                            |  |

|-----------------------------------------|----------------|---------------------------------|-------------------------|---------------|-------------------------------------------------|----------------------------------|----------------------------|--|

| Device                                  | Logic<br>Cells | System Gates<br>(Logic and RAM) | CLB<br>Array<br>(R x C) | Total<br>CLBs | Maximum<br>Available<br>User I/O <sup>(1)</sup> | Total<br>Distributed RAM<br>Bits | Total<br>Block RAM<br>Bits |  |

| XC2S15                                  | 432            | 15,000                          | 8 x 12                  | 96            | 86                                              | 6,144                            | 16K                        |  |

| XC2S30                                  | 972            | 30,000                          | 12 x 18                 | 216           | 92                                              | 13,824                           | 24K                        |  |

| XC2S50                                  | 1,728          | 50,000                          | 16 x 24                 | 384           | 176                                             | 24,576                           | 32K                        |  |

| XC2S100                                 | 2,700          | 100,000                         | 20 x 30                 | 600           | 176                                             | 38,400                           | 40K                        |  |

| XC2S150                                 | 3,888          | 150,000                         | 24 x 36                 | 864           | 260                                             | 55,296                           | 48K                        |  |

| XC2S200                                 | 5,292          | 200,000                         | 28 x 42                 | 1,176         | 284                                             | 75,264                           | 56K                        |  |

#### Notes:

1. All user I/O counts do not include the four global clock/user input pins. See details in Table 2, page 4.

© 2000-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

# **Spartan-II Product Availability**

Table 2 shows the maximum user I/Os available on the device and the number of user I/Os available for each device/package combination. The four global clock pins are usable as additional user I/Os when not used as a global clock pin. These pins are not included in user I/O counts.

#### Table 2: Spartan-II FPGA User I/O Chart<sup>(1)</sup>

|         |                     | Available User I/O According to Package Type |                 |                 |                 |                 |                 |

|---------|---------------------|----------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Device  | Maximum<br>User I/O | VQ100<br>VQG100                              | TQ144<br>TQG144 | CS144<br>CSG144 | PQ208<br>PQG208 | FG256<br>FGG256 | FG456<br>FGG456 |

| XC2S15  | 86                  | 60                                           | 86              | (Note 2)        | -               | -               | -               |

| XC2S30  | 92                  | 60                                           | 92              | 92              | (Note 2)        | -               | -               |

| XC2S50  | 176                 | -                                            | 92              | -               | 140             | 176             | -               |

| XC2S100 | 176                 | -                                            | 92              | -               | 140             | 176             | (Note 2)        |

| XC2S150 | 260                 | -                                            | -               | -               | 140             | 176             | 260             |

| XC2S200 | 284                 | -                                            | -               | -               | 140             | 176             | 284             |

#### Notes:

1. All user I/O counts do not include the four global clock/user input pins.

2. Discontinued by PDN2004-01.

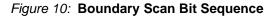

| Bit 0 ( TDO end)<br>Bit 1 | TDO.T<br>TDO.O                   |

|---------------------------|----------------------------------|

| Bit 2                     | Top-edge IOBs (Right to Left)    |

|                           | Left-edge IOBs (Top to Bottom)   |

|                           | MODE.I                           |

|                           | Bottom-edge IOBs (Left to Right) |

|                           | Right-edge IOBs (Bottom to Top)  |

| ▼ (TDI end)               | BSCANT.UPD                       |

DS001\_10\_032300

# **Development System**

Spartan-II FPGAs are supported by the Xilinx ISE<sup>®</sup> development tools. The basic methodology for Spartan-II FPGA design consists of three interrelated steps: design entry, implementation, and verification. Industry-standard tools are used for design entry and simulation, while Xilinx provides proprietary architecture-specific tools for implementation.

The Xilinx development system is integrated under a single graphical interface, providing designers with a common user interface regardless of their choice of entry and verification tools. The software simplifies the selection of implementation options with pull-down menus and on-line help.

For HDL design entry, the Xilinx FPGA development system provides interfaces to several synthesis design environments.

A standard interface-file specification, Electronic Design Interchange Format (EDIF), simplifies file transfers into and out of the development system.

Spartan-II FPGAs supported by a unified library of standard functions. This library contains over 400 primitives and macros, ranging from 2-input AND gates to 16-bit accumulators, and includes arithmetic functions, comparators, counters, data registers, decoders, encoders, I/O functions, latches, Boolean functions, multiplexers, shift registers, and barrel shifters.

The design environment supports hierarchical design entry. These hierarchical design elements are automatically combined by the implementation tools. Different design entry tools can be combined within a hierarchical design, thus allowing the most convenient entry method to be used for each portion of the design.

#### **Design Implementation**

The place-and-route tools (PAR) automatically provide the implementation flow described in this section. The partitioner takes the EDIF netlist for the design and maps the logic into the architectural resources of the FPGA (CLBs and IOBs, for example). The placer then determines the best locations for these blocks based on their interconnections and the desired performance. Finally, the router interconnects the blocks.

The PAR algorithms support fully automatic implementation of most designs. For demanding applications, however, the user can exercise various degrees of control over the process. User partitioning, placement, and routing information is optionally specified during the design-entry process. The implementation of highly structured designs can benefit greatly from basic floorplanning.

The implementation software incorporates timing-driven placement and routing. Designers specify timing requirements along entire paths during design entry. The timing path analysis routines in PAR then recognize these user-specified requirements and accommodate them.

Timing requirements are entered in a form directly relating to the system requirements, such as the targeted clock frequency, or the maximum allowable delay between two registers. In this way, the overall performance of the system along entire signal paths is automatically tailored to user-generated specifications. Specific timing information for individual nets is unnecessary.

### **Design Verification**

In addition to conventional software simulation, FPGA users can use in-circuit debugging techniques. Because Xilinx devices are infinitely reprogrammable, designs can be verified in real time without the need for extensive sets of software simulation vectors.

The development system supports both software simulation and in-circuit debugging techniques. For simulation, the system extracts the post-layout timing information from the design database, and back-annotates this information into the netlist for use by the simulator. Alternatively, the user can verify timing-critical portions of the design using the static timing analyzer.

For in-circuit debugging, the development system includes a download cable, which connects the FPGA in the target system to a PC or workstation. After downloading the design into the FPGA, the designer can read back the contents of the flip-flops, and so observe the internal logic state. Simple modifications can be downloaded into the system in a matter of minutes.

#

# Signals

There are two kinds of pins that are used to configure Spartan-II devices: Dedicated pins perform only specific configuration-related functions; the other pins can serve as general purpose I/Os once user operation has begun.

The dedicated pins comprise the mode pins (M2, M1, M0), the configuration clock pin (CCLK), the PROGRAM pin, the DONE pin and the boundary-scan pins (TDI, TDO, TMS, TCK). Depending on the selected configuration mode, CCLK may be an output generated by the FPGA, or may be generated externally, and provided to the FPGA as an input.

Note that some configuration pins can act as outputs. For correct operation, these pins require a V<sub>CCO</sub> of 3.3V to drive an LVTTL signal or 2.5V to drive an LVCMOS signal. All the relevant pins fall in banks 2 or 3. The  $\overline{\text{CS}}$  and  $\overline{\text{WRITE}}$  pins for Slave Parallel mode are located in bank 1.

For a more detailed description than that given below, see "Pinout Tables" in Module 4 and XAPP176, Spartan-II FPGA Series Configuration and Readback.

# The Process

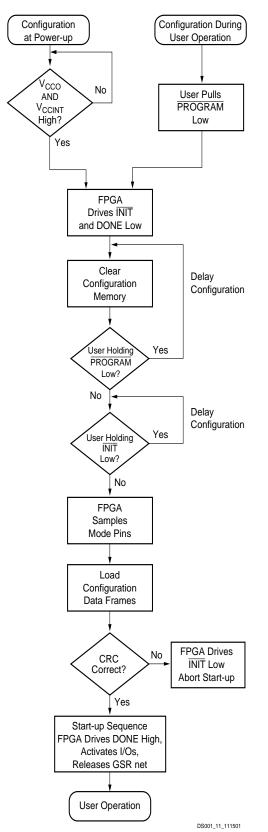

The sequence of steps necessary to configure Spartan-II devices are shown in Figure 11. The overall flow can be divided into three different phases.

- Initiating Configuration

- Configuration memory clear

- Loading data frames

- Start-up

The memory clearing and start-up phases are the same for all configuration modes; however, the steps for the loading of data frames are different. Thus, the details for data frame loading are described separately in the sections devoted to each mode.

#### Initiating Configuration

There are two different ways to initiate the configuration process: applying power to the device or asserting the PROGRAM input.

Configuration on power-up occurs automatically unless it is delayed by the user, as described in a separate section below. The waveform for configuration on power-up is shown in Figure 12, page 19. Before configuration can begin,  $V_{CCO}$  Bank 2 must be greater than 1.0V. Furthermore, all  $V_{CCINT}$  power pins must be connected to a 2.5V supply. For more information on delaying configuration, see "Clearing Configuration Memory," page 19.

Once in user operation, the device can be re-configured simply by pulling the PROGRAM pin Low. The device acknowledges the beginning of the configuration process

by driving DONE Low, then enters the memory-clearing phase.

Figure 11: Configuration Flow Diagram

DS001\_16\_032300

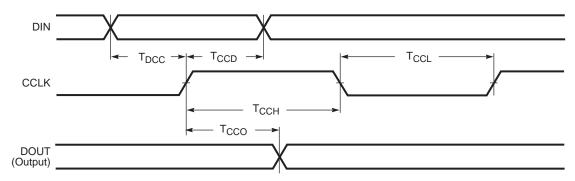

| Symbol           |      | Description       |    | Units    |

|------------------|------|-------------------|----|----------|

| T <sub>DCC</sub> |      | DIN setup         | 5  | ns, min  |

| T <sub>CCD</sub> |      | DIN hold          | 0  | ns, min  |

| T <sub>CCO</sub> | CCLK | DOUT              | 12 | ns, max  |

| ТССН             | COLK | High time         | 5  | ns, min  |

| T <sub>CCL</sub> |      | Low time          | 5  | ns, min  |

| F <sub>CC</sub>  | -    | Maximum frequency | 66 | MHz, max |

Figure 16: Slave Serial Mode Timing

If CCLK is slower than  $\rm F_{CCNH},$  the FPGA will never assert BUSY. In this case, the above handshake is unnecessary, and data can simply be entered into the FPGA every CCLK cycle.

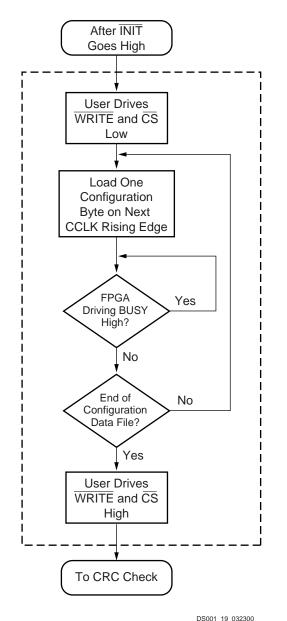

#### Figure 19: Loading Configuration Data for the Slave Parallel Mode

A configuration packet does not have to be written in one continuous stretch, rather it can be split into many write sequences. Each sequence would involve assertion of  $\overline{CS}$ .

In applications where multiple clock cycles may be required to access the configuration data before each byte can be loaded into the Slave Parallel interface, a new byte of data may not be ready for each consecutive CCLK edge. In such a case the  $\overline{CS}$  signal may be de-asserted until the next byte is valid on D0-D7. While  $\overline{CS}$  is High, the Slave Parallel interface does not expect any data and ignores all CCLK transitions. However, to avoid aborting configuration, WRITE must continue to be asserted while CS is asserted.

#### Abort

To abort configuration during a write sequence, de-assert  $\overline{\text{WRITE}}$  while holding  $\overline{\text{CS}}$  Low. The abort operation is initiated at the rising edge of CCLK, as shown in Figure 21, page 26. The device will remain BUSY until the aborted operation is complete. After aborting configuration, data is assumed to be unaligned to word boundaries and the FPGA requires a new synchronization word prior to accepting any new packets.

#### **Boundary-Scan Mode**

In the boundary-scan mode, no nondedicated pins are required, configuration being done entirely through the IEEE 1149.1 Test Access Port.

Configuration through the TAP uses the special CFG\_IN instruction. This instruction allows data input on TDI to be converted into data packets for the internal configuration bus.

The following steps are required to configure the FPGA through the boundary-scan port.

- 1. Load the CFG\_IN instruction into the boundary-scan instruction register (IR)

- 2. Enter the Shift-DR (SDR) state

- 3. Shift a standard configuration bitstream into TDI

- 4. Return to Run-Test-Idle (RTI)

- 5. Load the JSTART instruction into IR

- 6. Enter the SDR state

- 7. Clock TCK through the sequence (the length is programmable)

- 8. Return to RTI

Configuration and readback via the TAP is always available. The boundary-scan mode simply locks out the other modes. The boundary-scan mode is selected by a <10x> on the mode pins (M0, M1, M2).

# Readback

The configuration data stored in the Spartan-II FPGA configuration memory can be readback for verification. Along with the configuration data it is possible to readback the contents of all flip-flops/latches, LUT RAMs, and block RAMs. This capability is used for real-time debugging.

For more detailed information see <u>XAPP176</u>, Spartan-II FPGA Family Configuration and Readback.

# **Design Considerations**

This section contains more detailed design information on the following features:

- Delay-Locked Loop . . . see page 27

- Block RAM . . . see page 32

- Versatile I/O . . . see page 36

# Using Delay-Locked Loops

The Spartan-II FPGA family provides up to four fully digital dedicated on-chip Delay-Locked Loop (DLL) circuits which provide zero propagation delay, low clock skew between output clock signals distributed throughout the device, and advanced clock domain control. These dedicated DLLs can be used to implement several circuits that improve and simplify system level design.

#### Introduction

Quality on-chip clock distribution is important. Clock skew and clock delay impact device performance and the task of managing clock skew and clock delay with conventional clock trees becomes more difficult in large devices. The Spartan-II family of devices resolve this potential problem by providing up to four fully digital dedicated on-chip Delay-Locked Loop (DLL) circuits which provide zero propagation delay and low clock skew between output clock signals distributed throughout the device.

Each DLL can drive up to two global clock routing networks within the device. The global clock distribution network minimizes clock skews due to loading differences. By monitoring a sample of the DLL output clock, the DLL can compensate for the delay on the routing network, effectively eliminating the delay from the external input port to the individual clock loads within the device.

In addition to providing zero delay with respect to a user source clock, the DLL can provide multiple phases of the source clock. The DLL can also act as a clock doubler or it can divide the user source clock by up to 16.

Clock multiplication gives the designer a number of design alternatives. For instance, a 50 MHz source clock doubled by the DLL can drive an FPGA design operating at 100 MHz. This technique can simplify board design because the clock path on the board no longer distributes such a high-speed signal. A multiplied clock also provides designers the option of time-domain-multiplexing, using one circuit twice per clock cycle, consuming less area than two copies of the same circuit.

The DLL can also act as a clock mirror. By driving the DLL output off-chip and then back in again, the DLL can be used to de-skew a board level clock between multiple devices.

In order to guarantee the system clock establishes prior to the device "waking up," the DLL can delay the completion of the device configuration process until after the DLL achieves lock.

By taking advantage of the DLL to remove on-chip clock delay, the designer can greatly simplify and improve system level design involving high-fanout, high-performance clocks.

#### **Library DLL Primitives**

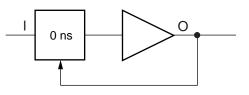

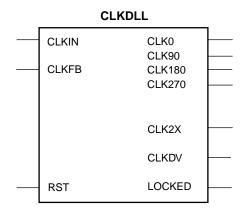

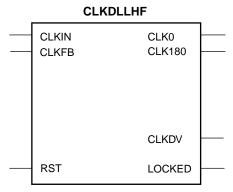

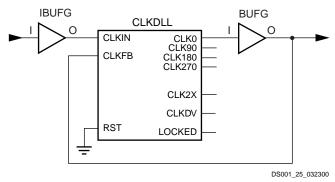

Figure 22 shows the simplified Xilinx library DLL macro, BUFGDLL. This macro delivers a quick and efficient way to provide a system clock with zero propagation delay throughout the device. Figure 23 and Figure 24 show the two library DLL primitives. These primitives provide access to the complete set of DLL features when implementing more complex applications.

Figure 22: Simplified DLL Macro BUFGDLL

DS001\_23\_032300

DS001\_24\_032300

# **BUFGDLL Pin Descriptions**

Use the BUFGDLL macro as the simplest way to provide zero propagation delay for a high-fanout on-chip clock from an external input. This macro uses the IBUFG, CLKDLL and BUFG primitives to implement the most basic DLL application as shown in Figure 25.

Figure 25: BUFGDLL Block Diagram

This macro does not provide access to the advanced clock domain controls or to the clock multiplication or clock division features of the DLL. This macro also does not provide access to the RST or LOCKED pins of the DLL. For access to these features, a designer must use the DLL primitives described in the following sections.

#### Source Clock Input — I

The I pin provides the user source clock, the clock signal on which the DLL operates, to the BUFGDLL. For the BUFGDLL macro the source clock frequency must fall in the low frequency range as specified in the data sheet. The BUFGDLL requires an external signal source clock. Therefore, only an external input port can source the signal that drives the BUFGDLL I pin.

#### Clock Output — O

The clock output pin O represents a delay-compensated version of the source clock (I) signal. This signal, sourced by a global clock buffer BUFG primitive, takes advantage of the dedicated global clock routing resources of the device.

The output clock has a 50/50 duty cycle unless you deactivate the duty cycle correction property.

### **CLKDLL Primitive Pin Descriptions**

The library CLKDLL primitives provide access to the complete set of DLL features needed when implementing more complex applications with the DLL.

#### Source Clock Input — CLKIN

The CLKIN pin provides the user source clock (the clock signal on which the DLL operates) to the DLL. The CLKIN frequency must fall in the ranges specified in the data sheet. A global clock buffer (BUFG) driven from another CLKDLL

or one of the global clock input buffers (IBUFG) on the same edge of the device (top or bottom) must source this clock signal.

#### Feedback Clock Input — CLKFB

The DLL requires a reference or feedback signal to provide the delay-compensated output. Connect only the CLK0 or CLK2X DLL outputs to the feedback clock input (CLKFB) pin to provide the necessary feedback to the DLL. Either a global clock buffer (BUFG) or one of the global clock input buffers (IBUFG) on the same edge of the device (top or bottom) must source this clock signal.

If an IBUFG sources the CLKFB pin, the following special rules apply.

- 1. An external input port must source the signal that drives the IBUFG I pin.

- The CLK2X output must feed back to the device if both the CLK0 and CLK2X outputs are driving off chip devices.

- 3. That signal must directly drive only OBUFs and nothing else.

These rules enable the software to determine which DLL clock output sources the CLKFB pin.

#### Reset Input — RST

When the reset pin RST activates, the LOCKED signal deactivates within four source clock cycles. The RST pin, active High, must either connect to a dynamic signal or be tied to ground. As the DLL delay taps reset to zero, glitches can occur on the DLL clock output pins. Activation of the RST pin can also severely affect the duty cycle of the clock output pins. Furthermore, the DLL output clocks no longer deskew with respect to one another. The DLL must be reset when the input clock frequency changes, if the device is reconfigured in Boundary-Scan mode, if the device undergoes a hot swap, and after the device is configured if the input clock is not stable during the startup sequence.

#### 2x Clock Output — CLK2X

The output pin CLK2X provides a frequency-doubled clock with an automatic 50/50 duty-cycle correction. Until the CLKDLL has achieved lock, the CLK2X output appears as a 1x version of the input clock with a 25/75 duty cycle. This behavior allows the DLL to lock on the correct edge with respect to source clock. This pin is not available on the CLKDLLHF primitive.

#### Clock Divide Output — CLKDV

The clock divide output pin CLKDV provides a lower frequency version of the source clock. The CLKDV\_DIVIDE property controls CLKDV such that the source clock is divided by N where N is either 1.5, 2, 2.5, 3, 4, 5, 8, or 16.

This feature provides automatic duty cycle correction. The CLKDV output pin has a 50/50 duty cycle for all values of the

support of a wide variety of applications, from general purpose standard applications to high-speed low-voltage memory busses.

Versatile I/O blocks also provide selectable output drive strengths and programmable slew rates for the LVTTL output buffers, as well as an optional, programmable weak pull-up, weak pull-down, or weak "keeper" circuit ideal for use in external bussing applications.

Each Input/Output Block (IOB) includes three registers, one each for the input, output, and 3-state signals within the IOB. These registers are optionally configurable as either a D-type flip-flop or as a level sensitive latch.

The input buffer has an optional delay element used to guarantee a zero hold time requirement for input signals registered within the IOB.

The Versatile I/O features also provide dedicated resources for input reference voltage ( $V_{REF}$ ) and output source voltage ( $V_{CCO}$ ), along with a convenient banking system that simplifies board design.

By taking advantage of the built-in features and wide variety of I/O standards supported by the Versatile I/O features, system-level design and board design can be greatly simplified and improved.

### **Fundamentals**

Modern bus applications, pioneered by the largest and most influential companies in the digital electronics industry, are commonly introduced with a new I/O standard tailored specifically to the needs of that application. The bus I/O standards provide specifications to other vendors who create products designed to interface with these applications. Each standard often has its own specifications for current, voltage, I/O buffering, and termination techniques.

The ability to provide the flexibility and time-to-market advantages of programmable logic is increasingly dependent on the capability of the programmable logic device to support an ever increasing variety of I/O standards

The Versatile I/O resources feature highly configurable input and output buffers which provide support for a wide variety of I/O standards. As shown in Table 15, each buffer type can support a variety of voltage requirements.

# Table 15: Versatile I/O Supported Standards (Typical Values)

| ,                             | 1                                                    |                                                    | , , , , , , , , , , , , , , , , , , , ,               |

|-------------------------------|------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|

| I/O Standard                  | Input<br>Reference<br>Voltage<br>(V <sub>REF</sub> ) | Output<br>Source<br>Voltage<br>(V <sub>CCO</sub> ) | Board<br>Termination<br>Voltage<br>(V <sub>TT</sub> ) |

| LVTTL (2-24 mA)               | N/A                                                  | 3.3                                                | N/A                                                   |

| LVCMOS2                       | N/A                                                  | 2.5                                                | N/A                                                   |

| PCI (3V/5V,<br>33 MHz/66 MHz) | N/A                                                  | 3.3                                                | N/A                                                   |

| GTL                           | 0.8                                                  | N/A                                                | 1.2                                                   |

| GTL+                          | 1.0                                                  | N/A                                                | 1.5                                                   |

| HSTL Class I                  | 0.75                                                 | 1.5                                                | 0.75                                                  |

| HSTL Class III                | 0.9                                                  | 1.5                                                | 1.5                                                   |

| HSTL Class IV                 | 0.9                                                  | 1.5                                                | 1.5                                                   |

| SSTL3 Class I<br>and II       | 1.5                                                  | 3.3                                                | 1.5                                                   |

| SSTL2 Class I<br>and II       | 1.25                                                 | 2.5                                                | 1.25                                                  |

| CTT                           | 1.5                                                  | 3.3                                                | 1.5                                                   |

| AGP-2X                        | 1.32                                                 | 3.3                                                | N/A                                                   |

### **Overview of Supported I/O Standards**

This section provides a brief overview of the I/O standards supported by all Spartan-II devices.

While most I/O standards specify a range of allowed voltages, this document records typical voltage values only. Detailed information on each specification may be found on the Electronic Industry Alliance JEDEC website at <a href="http://www.jedec.org">http://www.jedec.org</a>. For more details on the I/O standards and termination application examples, see <a href="http://www.seetandards">XAPP179</a>, "Using SelectIO Interfaces in Spartan-II and Spartan-IIE FPGAs."

### LVTTL — Low-Voltage TTL

The Low-Voltage TTL (LVTTL) standard is a general purpose EIA/JESDSA standard for 3.3V applications that uses an LVTTL input buffer and a Push-Pull output buffer. This standard requires a 3.3V output source voltage ( $V_{CCO}$ ), but does not require the use of a reference voltage ( $V_{REF}$ ) or a termination voltage ( $V_{TT}$ ).

#### LVCMOS2 — Low-Voltage CMOS for 2.5V

The Low-Voltage CMOS for 2.5V or lower (LVCMOS2) standard is an extension of the LVCMOS standard (JESD 8.5) used for general purpose 2.5V applications. This standard requires a 2.5V output source voltage ( $V_{CCO}$ ), but does not require the use of a reference voltage ( $V_{REF}$ ) or a board termination voltage ( $V_{TT}$ ).

LVTTL output buffers have selectable drive strengths.

The format for LVTTL OBUF primitive names is as follows.

OBUF <slew rate> <drive strength>

<slew\_rate> is either F (Fast), or S (Slow) and <drive\_strength> is specified in milliamps (2, 4, 6, 8, 12, 16, or 24). The default is slew rate limited with 12 mA drive.

OBUF placement restrictions require that within a given  $V_{CCO}$  bank each OBUF share the same output source drive voltage. Input buffers of any type and output buffers that do not require  $V_{CCO}$  can be placed within any  $V_{CCO}$  bank. Table 17 summarizes the output compatibility requirements. The LOC property can specify a location for the OBUF.

# Table 17: Output Standards Compatibility Requirements

| Rule 1           | Only outputs with standards which share compatible $\rm V_{\rm CCO}$ may be used within the same bank.  |

|------------------|---------------------------------------------------------------------------------------------------------|

| Rule 2           | There are no placement restrictions for outputs with standards that do not require a $\rm V_{\rm CCO}.$ |

| V <sub>CCO</sub> | Compatible Standards                                                                                    |

| 3.3              | LVTTL, SSTL3_I, SSTL3_II, CTT, AGP, GTL, GTL+, PCI33_3, PCI66_3                                         |

| 2.5              | SSTL2_I, SSTL2_II, LVCMOS2, GTL, GTL+                                                                   |

| 1.5              | HSTL_I, HSTL_III, HSTL_IV, GTL, GTL+                                                                    |

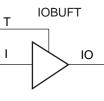

#### OBUFT

The generic 3-state output buffer OBUFT, shown in Figure 39, typically implements 3-state outputs or bidirectional I/O.

With no extension or property specified for the generic OBUFT primitive, the assumed standard is slew rate limited LVTTL with 12 mA drive strength.

The LVTTL OBUFT can support one of two slew rate modes to minimize bus transients. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals.

LVTTL 3-state output buffers have selectable drive strengths.

The format for LVTTL OBUFT primitive names is as follows.

OBUFT\_<slew\_rate>\_<drive\_strength>

<slew\_rate> can be either F (Fast), or S (Slow) and <drive\_strength> is specified in milliamps (2, 4, 6, 8, 12, 16, or 24).

DS001\_39\_032300

Figure 39: 3-State Output Buffer Primitive (OBUFT

The Versatile I/O OBUFT placement restrictions require that within a given V<sub>CCO</sub> bank each OBUFT share the same output source drive voltage. Input buffers of any type and output buffers that do not require V<sub>CCO</sub> can be placed within the same V<sub>CCO</sub> bank.

The LOC property can specify a location for the OBUFT.

3-state output buffers and bidirectional buffers can have either a weak pull-up resistor, a weak pull-down resistor, or a weak "keeper" circuit. Control this feature by adding the appropriate primitive to the output net of the OBUFT (PULLUP, PULLDOWN, or KEEPER).

The weak "keeper" circuit requires the input buffer within the IOB to sample the I/O signal. So, OBUFTs programmed for an I/O standard that requires a  $V_{REF}$  have automatic placement of a  $V_{REF}$  in the bank with an OBUFT configured with a weak "keeper" circuit. This restriction does not affect most circuit design as applications using an OBUFT configured with a weak "keeper" typically implement a bidirectional I/O. In this case the IBUF (and the corresponding  $V_{REF}$ ) are explicitly placed.

The LOC property can specify a location for the OBUFT.

#### IOBUF

Use the IOBUF primitive for bidirectional signals that require both an input buffer and a 3-state output buffer with an active high 3-state pin. The generic input/output buffer IOBUF appears in Figure 40.

With no extension or property specified for the generic IOBUF primitive, the assumed standard is LVTTL input buffer and slew rate limited LVTTL with 12 mA drive strength for the output buffer.

The LVTTL IOBUF can support one of two slew rate modes to minimize bus transients. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals.

LVTTL bidirectional buffers have selectable output drive strengths.

The format for LVTTL IOBUF primitive names is as follows:

# **Revision History**

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09/18/00 | 2.0     | Sectioned the Spartan-II Family data sheet into four modules. Corrected banking description.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 03/05/01 | 2.1     | Clarified guidelines for applying power to $V_{\mbox{CCINT}}$ and $V_{\mbox{CCO}}$                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 09/03/03 | 2.2     | <ul> <li>The following changes were made:</li> <li>"Serial Modes," page 20 cautions about toggling WRITE during serial configuration.</li> <li>Maximum V<sub>IH</sub> values in Table 32 and Table 33 changed to 5.5V.</li> <li>In "Boundary Scan," page 13, removed sentence about lack of INTEST support.</li> <li>In Table 9, page 17, added note about the state of I/Os after power-on.</li> <li>In "Slave Parallel Mode," page 23, explained configuration bit alignment to SelectMap port.</li> </ul> |

| 06/13/08 | 2.8     | Added note that TDI, TMS, and TCK have a default pull-up resistor. Added note on maximum daisy chain limit. Updated Figure 15 and Figure 18 since Mode pins can be pulled up to either 2.5V or 3.3V. Updated DLL section. Recommended using property or attribute instead of primitive to define I/O properties. Updated description and links. Updated all modules for continuous page, figure, and table numbering. Synchronized all modules to v2.8.                                                      |

# Spartan-II FPGA Family: DC and Switching Characteristics

DS001-3 (v2.8) June 13, 2008

**Product Specification**

# **Definition of Terms**

In this document, some specifications may be designated as Advance or Preliminary. These terms are defined as follows:

Advance: Initial estimates based on simulation and/or extrapolation from other speed grades, devices, or families. Values are subject to change. Use as estimates, not for production.

Preliminary: Based on preliminary characterization. Further changes are not expected.

Unmarked: Specifications not identified as either Advance or Preliminary are to be considered Final.

Except for pin-to-pin input and output parameters, the AC parameter delay specifications included in this document are derived from measuring internal test patterns. All limits are representative of worst-case supply voltage and junction temperature conditions. Typical numbers are based on measurements taken at a nominal  $V_{CCINT}$  level of 2.5V and a junction temperature of 25°C. The parameters included are common to popular designs and typical applications. All specifications are subject to change without notice.

# **DC Specifications**

#### Absolute Maximum Ratings<sup>(1)</sup>

| Symbol             | Descriptio                                    | Description                                   |      | Max                   | Units |

|--------------------|-----------------------------------------------|-----------------------------------------------|------|-----------------------|-------|

| V <sub>CCINT</sub> | Supply voltage relative to GND <sup>(2)</sup> | Supply voltage relative to GND <sup>(2)</sup> |      | 3.0                   | V     |

| V <sub>CCO</sub>   | Supply voltage relative to GND <sup>(2)</sup> | Supply voltage relative to GND <sup>(2)</sup> |      | 4.0                   | V     |

| V <sub>REF</sub>   | Input reference voltage                       | put reference voltage                         |      | 3.6                   | V     |

| V <sub>IN</sub>    | Input voltage relative to GND <sup>(3)</sup>  | 5V tolerant I/O <sup>(4)</sup>                | -0.5 | 5.5                   | V     |

|                    |                                               | No 5V tolerance <sup>(5)</sup>                | -0.5 | V <sub>CCO</sub> +0.5 | V     |

| V <sub>TS</sub>    | Voltage applied to 3-state output             | 5V tolerant I/O <sup>(4)</sup>                | -0.5 | 5.5                   | V     |

|                    |                                               | No 5V tolerance <sup>(5)</sup>                | -0.5 | V <sub>CCO</sub> +0.5 | V     |

| T <sub>STG</sub>   | Storage temperature (ambient)                 | Storage temperature (ambient)                 |      | +150                  | °C    |

| TJ                 | Junction temperature                          |                                               | -    | +125                  | °C    |

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

2. Power supplies may turn on in any order.

3. V<sub>IN</sub> should not exceed V<sub>CCO</sub> by more than 3.6V over extended periods of time (e.g., longer than a day).

4. Spartan<sup>®</sup>-II device I/Os are 5V Tolerant whenever the LVTTL, LVCMOS2, or PCI33\_5 signal standard has been selected. With 5V Tolerant I/Os selected, the Maximum DC overshoot must be limited to either +5.5V or 10 mA, and undershoot must be limited to either -0.5V or 10 mA, whichever is easier to achieve. The Maximum AC conditions are as follows: The device pins may undershoot to -2.0V or overshoot to +7.0V, provided this over/undershoot lasts no more than 11 ns with a forcing current no greater than 100 mA.

5. Without 5V Tolerant I/Os selected, the Maximum DC overshoot must be limited to either V<sub>CCO</sub> + 0.5V or 10 mA, and undershoot must be limited to -0.5V or 10 mA, whichever is easier to achieve. The Maximum AC conditions are as follows: The device pins may undershoot to -2.0V or overshoot to V<sub>CCO</sub> + 2.0V, provided this over/undershoot lasts no more than 11 ns with a forcing current no greater than 100 mA.

6. For soldering guidelines, see the <u>Packaging Information</u> on the Xilinx<sup>®</sup> web site.

© 2000-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

#### Global Clock Setup and Hold for LVTTL Standard, with DLL (Pin-to-Pin)

|                                         |                                                                                                                                     |        | Speed Grade |         |       |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|---------|-------|

|                                         |                                                                                                                                     | -6     | -5          |         |       |

| Symbol                                  | Description                                                                                                                         | Device | Min         | Min     | Units |

| T <sub>PSDLL</sub> / T <sub>PHDLL</sub> | Input setup and hold time relative<br>to global clock input signal for<br>LVTTL standard, no delay, IFF, <sup>(1)</sup><br>with DLL | All    | 1.7 / 0     | 1.9 / 0 | ns    |

Notes:

1. IFF = Input Flip-Flop or Latch

2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

3. DLL output jitter is already included in the timing calculation.

4. A zero hold time listing indicates no hold time or a negative hold time.

For data input with different standards, adjust the setup time delay by the values shown in "IOB Input Delay Adjustments for Different Standards," page 57. For a global clock input with standards other than LVTTL, adjust delays with values from the "I/O Standard Global Clock Input Adjustments," page 61.

### Global Clock Setup and Hold for LVTTL Standard, without DLL (Pin-to-Pin)

|                                                                          |                                                                                                  |         | Speed Grade |         |       |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------|-------------|---------|-------|

|                                                                          |                                                                                                  |         | -6          | -5      |       |

| Symbol                                                                   | Description                                                                                      | Device  | Min         | Min     | Units |

| T <sub>PSFD</sub> / T <sub>PHFD</sub> Input setup and hold time relative | XC2S15                                                                                           | 2.2 / 0 | 2.7 / 0     | ns      |       |

|                                                                          | to global clock input signal for<br>LVTTL standard, no delay, IFF, <sup>(1)</sup><br>without DLL | XC2S30  | 2.2 / 0     | 2.7 / 0 | ns    |

|                                                                          |                                                                                                  | XC2S50  | 2.2 / 0     | 2.7 / 0 | ns    |

|                                                                          |                                                                                                  | XC2S100 | 2.3 / 0     | 2.8 / 0 | ns    |

|                                                                          |                                                                                                  | XC2S150 | 2.4 / 0     | 2.9/0   | ns    |

|                                                                          |                                                                                                  | XC2S200 | 2.4 / 0     | 3.0 / 0 | ns    |

Notes:

1. IFF = Input Flip-Flop or Latch

2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

- 3. A zero hold time listing indicates no hold time or a negative hold time.

- 4. For data input with different standards, adjust the setup time delay by the values shown in "IOB Input Delay Adjustments for Different Standards," page 57. For a global clock input with standards other than LVTTL, adjust delays with values from the "I/O Standard Global Clock Input Adjustments," page 61.

### **DLL Timing Parameters**

All devices are 100 percent functionally tested. Because of the difficulty in directly measuring many internal timing parameters, those parameters are derived from benchmark timing patterns. The following guidelines reflect worst-case values across the recommended operating conditions.

|                      |                                    |     | Speed Grade |     |     |       |

|----------------------|------------------------------------|-----|-------------|-----|-----|-------|

|                      |                                    | -6  |             | -5  |     | =     |

| Symbol               | Description                        | Min | Max         | Min | Max | Units |

| F <sub>CLKINHF</sub> | Input clock frequency (CLKDLLHF)   | 60  | 200         | 60  | 180 | MHz   |

| F <sub>CLKINLF</sub> | Input clock frequency (CLKDLL)     | 25  | 100         | 25  | 90  | MHz   |

| T <sub>DLLPWHF</sub> | Input clock pulse width (CLKDLLHF) | 2.0 | -           | 2.4 | -   | ns    |

| T <sub>DLLPWLF</sub> | Input clock pulse width (CLKDLL)   | 2.5 | -           | 3.0 | -   | ns    |

#### **DLL Clock Tolerance, Jitter, and Phase Information**

All DLL output jitter and phase specifications were determined through statistical measurement at the package pins using a clock mirror configuration and matched drivers.

Figure 52, page 63, provides definitions for various parameters in the table below.

|                     |                                                                |                               | CLKE | DLLHF | CLK | DLL  |       |

|---------------------|----------------------------------------------------------------|-------------------------------|------|-------|-----|------|-------|

| Symbol              | Description                                                    | F <sub>CLKIN</sub>            | Min  | Max   | Min | Max  | Units |

| T <sub>IPTOL</sub>  | Input clock period tolerance                                   |                               | -    | 1.0   | -   | 1.0  | ns    |

| T <sub>IJITCC</sub> | Input clock jitter tolerance (cycle-to-cycle)                  |                               | -    | ±150  | -   | ±300 | ps    |

| T <sub>LOCK</sub>   | Time required for DLL to acquire lock                          | > 60 MHz                      | -    | 20    | -   | 20   | μs    |

|                     |                                                                | 50-60 MHz                     | -    | -     | -   | 25   | μs    |

|                     |                                                                | 40-50 MHz                     | -    | -     | -   | 50   | μs    |

|                     |                                                                | 30-40 MHz                     | -    | -     | -   | 90   | μs    |

|                     |                                                                | 25-30 MHz                     | -    | -     | -   | 120  | μs    |

| T <sub>OJITCC</sub> | Output jitter (cycle-to-cycle) for any DLL clock c             | output <sup>(1)</sup>         | -    | ±60   | -   | ±60  | ps    |

| T <sub>PHIO</sub>   | Phase offset between CLKIN and CLKO <sup>(2)</sup>             |                               | -    | ±100  | -   | ±100 | ps    |

| T <sub>PHOO</sub>   | Phase offset between clock outputs on the DLL <sup>(3)</sup>   |                               | -    | ±140  | -   | ±140 | ps    |

| T <sub>PHIOM</sub>  | Maximum phase difference between CLKIN and CLKO <sup>(4)</sup> |                               | -    | ±160  | -   | ±160 | ps    |

| T <sub>PHOOM</sub>  | Maximum phase difference between clock outp                    | uts on the DLL <sup>(5)</sup> | -    | ±200  | -   | ±200 | ps    |

Notes:

1. **Output Jitter** is cycle-to-cycle jitter measured on the DLL output clock, *excluding* input clock jitter.

2. Phase Offset between CLKIN and CLKO is the worst-case fixed time difference between rising edges of CLKIN and CLKO, *excluding* output jitter and input clock jitter.

3. Phase Offset between Clock Outputs on the DLL is the worst-case fixed time difference between rising edges of any two DLL outputs, *excluding* Output Jitter and input clock jitter.

4. Maximum Phase Difference between CLKIN an CLKO is the sum of Output Jitter and Phase Offset between CLKIN and CLKO, or the greatest difference between CLKIN and CLKO rising edges due to DLL alone (*excluding* input clock jitter).

5. **Maximum Phase Difference between Clock Outputs on the DLL** is the sum of Output JItter and Phase Offset between any DLL clock outputs, or the greatest difference between any two DLL output rising edges due to DLL alone (*excluding* input clock jitter).

#### **Block RAM Switching Characteristics**

|                                       |                                             |         | Speed | _       |     |       |

|---------------------------------------|---------------------------------------------|---------|-------|---------|-----|-------|

|                                       |                                             | -6      |       |         | -5  |       |

| Symbol                                | Description                                 | Min     | Max   | Min     | Max | Units |

| Sequential Delays                     | ·                                           |         |       |         |     |       |

| Т <sub>ВСКО</sub>                     | Clock CLK to DOUT output                    | -       | 3.4   | -       | 4.0 | ns    |

| Setup/Hold Times                      | with Respect to Clock CLK <sup>(1)</sup>    | 1       |       |         |     | 1     |

| T <sub>BACK</sub> / T <sub>BCKA</sub> | ADDR inputs                                 | 1.4 / 0 | -     | 1.4 / 0 | -   | ns    |

| T <sub>BDCK</sub> / T <sub>BCKD</sub> | DIN inputs                                  | 1.4 / 0 | -     | 1.4 / 0 | -   | ns    |

| T <sub>BECK</sub> / T <sub>BCKE</sub> | EN inputs                                   | 2.9/0   | -     | 3.2 / 0 | -   | ns    |

| T <sub>BRCK</sub> / T <sub>BCKR</sub> | RST input                                   | 2.7 / 0 | -     | 2.9/0   | -   | ns    |

| T <sub>BWCK</sub> / T <sub>BCKW</sub> | WEN input                                   | 2.6 / 0 | -     | 2.8 / 0 | -   | ns    |

| Clock CLK                             |                                             |         |       |         |     | 1     |

| T <sub>BPWH</sub>                     | Minimum pulse width, High                   | -       | 1.9   | -       | 1.9 | ns    |

| T <sub>BPWL</sub>                     | Minimum pulse width, Low                    | -       | 1.9   | -       | 1.9 | ns    |

| T <sub>BCCS</sub>                     | CLKA -> CLKB setup time for different ports | -       | 3.0   | -       | 4.0 | ns    |

#### Notes:

1. A zero hold time listing indicates no hold time or a negative hold time.

#### **TBUF Switching Characteristics**

|                  |                                        | Speed | Speed Grade |       |  |

|------------------|----------------------------------------|-------|-------------|-------|--|

|                  |                                        | -6    | -5          |       |  |

| Symbol           | Description                            | Max   | Max         | Units |  |

| Combinatorial De | lays                                   |       |             |       |  |

| T <sub>IO</sub>  | IN input to OUT output                 | 0     | 0           | ns    |  |

| T <sub>OFF</sub> | TRI input to OUT output high impedance | 0.1   | 0.2         | ns    |  |

| T <sub>ON</sub>  | TRI input to valid data on OUT output  | 0.1   | 0.2         | ns    |  |

#### **JTAG Test Access Port Switching Characteristics**

|                                           |                                           |         | Speed | d Grade   |      |       |

|-------------------------------------------|-------------------------------------------|---------|-------|-----------|------|-------|

|                                           |                                           | -€      | 6     | -5        |      |       |

| Symbol                                    | Description                               | Min     | Max   | Min       | Мах  | Units |

| Setup and Hold Time                       | es with Respect to TCK                    |         |       |           |      |       |

| T <sub>TAPTCK /</sub> T <sub>TCKTAP</sub> | TMS and TDI setup and hold times          | 4.0/2.0 | -     | 4.0 / 2.0 | -    | ns    |

| Sequential Delays                         |                                           |         |       |           |      |       |

| T <sub>TCKTDO</sub>                       | Output delay from clock TCK to output TDO | -       | 11.0  | -         | 11.0 | ns    |

| FTCK                                      | Maximum TCK clock frequency               | -       | 33    | -         | 33   | MHz   |

### **XC2S50 Device Pinouts**

| XC2S50 Dev<br>XC2S50 Pad I |      |       |       |                             | Bndry |

|----------------------------|------|-------|-------|-----------------------------|-------|

| Function                   | Bank | TQ144 | PQ208 | FG256                       | Scan  |

| GND                        | -    | P143  | P1    | GND*                        | -     |

| TMS                        | -    | P142  | P2    | D3                          | -     |

| I/O                        | 7    | P141  | P3    | C2                          | 149   |

| I/O                        | 7    | -     | -     | A2                          | 152   |

| I/O                        | 7    | P140  | P4    | B1                          | 155   |

| I/O                        | 7    | -     | -     | E3                          | 158   |

| I/O                        | 7    | -     | P5    | D2                          | 161   |

| GND                        | -    | -     | -     | GND*                        | -     |

| I/O, V <sub>REF</sub>      | 7    | P139  | P6    | C1                          | 164   |

| I/O                        | 7    | -     | P7    | F3                          | 167   |

| I/O                        | 7    | -     | -     | E2                          | 170   |

| I/O                        | 7    | P138  | P8    | E4                          | 173   |

| I/O                        | 7    | P137  | P9    | D1                          | 176   |

| I/O                        | 7    | P136  | P10   | E1                          | 179   |

| GND                        | -    | P135  | P11   | GND*                        | -     |

| V <sub>CCO</sub>           | 7    | -     | P12   | V <sub>CCO</sub><br>Bank 7* | -     |

| V <sub>CCINT</sub>         | -    | -     | P13   | V <sub>CCINT</sub> *        | -     |

| I/O                        | 7    | P134  | P14   | F2                          | 182   |

| I/O                        | 7    | P133  | P15   | G3                          | 185   |

| I/O                        | 7    | -     | -     | F1                          | 188   |

| I/O                        | 7    | -     | P16   | F4                          | 191   |

| I/O                        | 7    | -     | P17   | F5                          | 194   |

| I/O                        | 7    | -     | P18   | G2                          | 197   |

| GND                        | -    | -     | P19   | GND*                        | -     |

| I/O, V <sub>REF</sub>      | 7    | P132  | P20   | H3                          | 200   |

| I/O                        | 7    | P131  | P21   | G4                          | 203   |

| I/O                        | 7    | -     | -     | H2                          | 206   |

| I/O                        | 7    | P130  | P22   | G5                          | 209   |

| I/O                        | 7    | -     | P23   | H4                          | 212   |

| I/O, IRDY <sup>(1)</sup>   | 7    | P129  | P24   | G1                          | 215   |

| GND                        | -    | P128  | P25   | GND*                        | -     |

| V <sub>CCO</sub>           | 7    | P127  | P26   | V <sub>CCO</sub><br>Bank 7* | -     |

| V <sub>CCO</sub>           | 6    | P127  | P26   | V <sub>CCO</sub><br>Bank 6* | -     |

| I/O, TRDY <sup>(1)</sup>   | 6    | P126  | P27   | J2                          | 218   |

| V <sub>CCINT</sub>         | -    | P125  | P28   | V <sub>CCINT</sub> *        | -     |

| I/O                        | 6    | P124  | P29   | H1                          | 224   |

| I/O                        | 6    | -     | -     | J4                          | 227   |

| I/O                        | 6    | P123  | P30   | J1                          | 230   |

| I/O, V <sub>REF</sub>      | 6    | P122  | P31   | J3                          | 233   |

# XC2S50 Device Pinouts (Continued)

| XC2S50 Pad Name       |      |       |       |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | Scan  |

| GND                   | -    | -     | P32   | GND*                        | -     |

| I/O                   | 6    | -     | P33   | K5                          | 236   |

| I/O                   | 6    | -     | P34   | K2                          | 239   |

| I/O                   | 6    | -     | P35   | K1                          | 242   |

| I/O                   | 6    | -     | -     | K3                          | 245   |

| I/O                   | 6    | P121  | P36   | L1                          | 248   |

| I/O                   | 6    | P120  | P37   | L2                          | 251   |

| V <sub>CCINT</sub>    | -    | -     | P38   | V <sub>CCINT</sub> *        | -     |

| V <sub>CCO</sub>      | 6    | -     | P39   | V <sub>CCO</sub><br>Bank 6* | -     |

| GND                   | -    | P119  | P40   | GND*                        | -     |

| I/O                   | 6    | P118  | P41   | K4                          | 254   |

| I/O                   | 6    | P117  | P42   | M1                          | 257   |

| I/O                   | 6    | P116  | P43   | L4                          | 260   |

| I/O                   | 6    | -     | -     | M2                          | 263   |

| I/O                   | 6    | -     | P44   | L3                          | 266   |

| I/O, V <sub>REF</sub> | 6    | P115  | P45   | N1                          | 269   |

| GND                   | -    | -     | -     | GND*                        | -     |

| I/O                   | 6    | -     | P46   | P1                          | 272   |

| I/O                   | 6    | -     | -     | L5                          | 275   |

| I/O                   | 6    | P114  | P47   | N2                          | 278   |

| I/O                   | 6    | -     | -     | M4                          | 281   |

| I/O                   | 6    | P113  | P48   | R1                          | 284   |

| I/O                   | 6    | P112  | P49   | M3                          | 287   |

| M1                    | -    | P111  | P50   | P2                          | 290   |

| GND                   | -    | P110  | P51   | GND*                        | -     |

| MO                    | -    | P109  | P52   | N3                          | 291   |

| V <sub>CCO</sub>      | 6    | P108  | P53   | V <sub>CCO</sub><br>Bank 6* | -     |

| V <sub>CCO</sub>      | 5    | P107  | P53   | V <sub>CCO</sub><br>Bank 5* | -     |

| M2                    | -    | P106  | P54   | R3                          | 292   |

| I/O                   | 5    | -     | -     | N5                          | 299   |

| I/O                   | 5    | P103  | P57   | T2                          | 302   |

| I/O                   | 5    | -     | -     | P5                          | 305   |

| I/O                   | 5    | -     | P58   | Т3                          | 308   |

| GND                   | -    | -     | -     | GND*                        | -     |

| I/O, V <sub>REF</sub> | 5    | P102  | P59   | T4                          | 311   |

| I/O                   | 5    | -     | P60   | M6                          | 314   |

| I/O                   | 5    | -     | -     | T5                          | 317   |

| I/O                   | 5    | P101  | P61   | N6                          | 320   |

| I/O                   | 5    | P100  | P62   | R5                          | 323   |

# XC2S50 Device Pinouts (Continued)

| XC2S50 Pad Name       |      |       |       |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | Scan  |

| I/O                   | 0    | -     | -     | D8                          | 83    |

| I/O                   | 0    | -     | P188  | A6                          | 86    |

| I/O, V <sub>REF</sub> | 0    | P12   | P189  | B7                          | 89    |

| GND                   | -    | -     | P190  | GND*                        | -     |

| I/O                   | 0    | -     | P191  | C8                          | 92    |

| I/O                   | 0    | -     | P192  | D7                          | 95    |

| I/O                   | 0    | -     | P193  | E7                          | 98    |

| I/O                   | 0    | P11   | P194  | C7                          | 104   |

| I/O                   | 0    | P10   | P195  | B6                          | 107   |

| V <sub>CCINT</sub>    | -    | P9    | P196  | V <sub>CCINT</sub> *        | -     |

| V <sub>CCO</sub>      | 0    | -     | P197  | V <sub>CCO</sub><br>Bank 0* | -     |

| GND                   | -    | P8    | P198  | GND*                        | -     |

| I/O                   | 0    | P7    | P199  | A5                          | 110   |

| I/O                   | 0    | P6    | P200  | C6                          | 113   |

| I/O                   | 0    | -     | P201  | B5                          | 116   |

| I/O                   | 0    | -     | -     | D6                          | 119   |

| I/O                   | 0    | -     | P202  | A4                          | 122   |

| I/O, V <sub>REF</sub> | 0    | P5    | P203  | B4                          | 125   |

| GND                   | -    | -     | -     | GND*                        | -     |

| I/O                   | 0    | -     | P204  | E6                          | 128   |

| I/O                   | 0    | -     | -     | D5                          | 131   |

| I/O                   | 0    | P4    | P205  | A3                          | 134   |

| I/O                   | 0    | -     | -     | C5                          | 137   |

| I/O                   | 0    | P3    | P206  | B3                          | 140   |

| TCK                   | -    | P2    | P207  | C4                          | -     |

| V <sub>CCO</sub>      | 0    | P1    | P208  | V <sub>CCO</sub><br>Bank 0* | -     |

| V <sub>CCO</sub>      | 7    | P144  | P208  | V <sub>CCO</sub><br>Bank 7* | -     |

04/18/01

#### Notes:

- 1. IRDY and TRDY can only be accessed when using Xilinx PCI cores.

- Pads labelled GND\*, V<sub>CCINT</sub>\*, V<sub>CCO</sub> Bank 0\*, V<sub>CCO</sub> Bank 1\*, V<sub>CCO</sub> Bank 2\*, V<sub>CCO</sub> Bank 3\*, V<sub>CCO</sub> Bank 4\*, V<sub>CCO</sub> Bank 5\*, V<sub>CCO</sub> Bank 6\*, V<sub>CCO</sub> Bank 7\* are internally bonded to independent ground or power planes within the package.

- 3. See "VCCO Banks" for details on  $V_{CCO}$  banking.

#### Additional XC2S50 Package Pins

| TQ144 |  |

|-------|--|

|-------|--|

| Not Connected Pins |      |   |   |   |   |  |  |  |  |

|--------------------|------|---|---|---|---|--|--|--|--|

| P104               | P105 | - | - | - | - |  |  |  |  |

| 11/02/00           |      |   |   |   |   |  |  |  |  |

#### Additional XC2S100 Package Pins

#### TQ144

| Not Connected Pins |      |   |   |   |   |  |  |  |  |

|--------------------|------|---|---|---|---|--|--|--|--|

| P104               | P105 | - | - | - | - |  |  |  |  |

| 11/02/00           |      |   |   |   |   |  |  |  |  |

# PQ208

| Not Connected Pins |     |    |    |    |    |  |  |  |  |  |

|--------------------|-----|----|----|----|----|--|--|--|--|--|

| P55                | P56 | -  | -  | -  | -  |  |  |  |  |  |

| 11/02/00           |     | I. | I. | I. | I. |  |  |  |  |  |

#### FG256

| V <sub>CCINT</sub> Pins      |                              |                     |           |    |     |  |  |  |  |

|------------------------------|------------------------------|---------------------|-----------|----|-----|--|--|--|--|

| C3                           | C14                          | D4                  | D13       | E5 | E12 |  |  |  |  |

| M5                           | M12                          | N4                  | N13       | P3 | P14 |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 0 Pins |    |     |  |  |  |  |

| E8                           | F8                           | -                   | -         | -  | -   |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 1 Pins |    |     |  |  |  |  |

| E9                           | F9                           | -                   | -         | -  | -   |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 2 Pins |    |     |  |  |  |  |

| H11                          | H12                          | -                   | -         | -  | -   |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 3 Pins |    |     |  |  |  |  |

| J11                          | J12                          | -                   | -         | -  | -   |  |  |  |  |

|                              | V <sub>CCO</sub> Bank 4 Pins |                     |           |    |     |  |  |  |  |

| L9                           | M9                           | -                   | -         | -  | -   |  |  |  |  |

| V <sub>CCO</sub> Bank 5 Pins |                              |                     |           |    |     |  |  |  |  |

| L8                           | M8                           | -                   | -         | -  | -   |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 6 Pins |    |     |  |  |  |  |

| J5                           | J6                           | -                   | -         | -  | -   |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 7 Pins |    |     |  |  |  |  |

| H5                           | H6                           | -                   | -         | -  | -   |  |  |  |  |

|                              |                              | GND                 | Pins      |    |     |  |  |  |  |

| A1                           | A16                          | B2                  | B15       | F6 | F7  |  |  |  |  |

| F10                          | F11                          | G6                  | G7        | G8 | G9  |  |  |  |  |

| G10                          | G11                          | H7                  | H8        | H9 | H10 |  |  |  |  |

| J7                           | J8                           | J9                  | J10       | K6 | K7  |  |  |  |  |

| K8                           | K9                           | K10                 | K11       | L6 | L7  |  |  |  |  |

| L10                          | L11                          | R2                  | R15       | T1 | T16 |  |  |  |  |

| Not Connected Pins           |                              |                     |           |    |     |  |  |  |  |

| P4                           | R4                           | -                   | -         | -  | -   |  |  |  |  |

| 11/02/00                     |                              |                     |           |    |     |  |  |  |  |

#### 11/02/00

#### FG456

| V <sub>CCINT</sub> Pins      |     |     |     |     |     |  |  |

|------------------------------|-----|-----|-----|-----|-----|--|--|

| E5                           | E18 | F6  | F17 | G7  | G8  |  |  |

| G9                           | G14 | G15 | G16 | H7  | H16 |  |  |

| J7                           | J16 | P7  | P16 | R7  | R16 |  |  |

| T7                           | T8  | Т9  | T14 | T15 | T16 |  |  |

| U6                           | U17 | V5  | V18 | -   | -   |  |  |

| V <sub>CCO</sub> Bank 0 Pins |     |     |     |     |     |  |  |

#### Additional XC2S100 Package Pins (Continued)

|                              |                              | IUU Fach             | ago i int  |      | uou) |  |  |  |  |

|------------------------------|------------------------------|----------------------|------------|------|------|--|--|--|--|

| F10                          | F7                           | F8                   | F9         | G10  | G11  |  |  |  |  |