Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 384                                                         |

| Number of Logic Elements/Cells | 1728                                                        |

| Total RAM Bits                 | 32768                                                       |

| Number of I/O                  | 140                                                         |

| Number of Gates                | 50000                                                       |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 208-BFQFP                                                   |

| Supplier Device Package        | 208-PQFP (28x28)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s50-6pqg208c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Spartan-II FPGA Family: Introduction and Ordering Information

DS001-1 (v2.8) June 13, 2008

**Product Specification**

## Introduction

The Spartan®-II Field-Programmable Gate Array family gives users high performance, abundant logic resources, and a rich feature set, all at an exceptionally low price. The six-member family offers densities ranging from 15,000 to 200,000 system gates, as shown in Table 1. System performance is supported up to 200 MHz. Features include block RAM (to 56K bits), distributed RAM (to 75,264 bits), 16 selectable I/O standards, and four DLLs. Fast, predictable interconnect means that successive design iterations continue to meet timing requirements.

The Spartan-II family is a superior alternative to mask-programmed ASICs. The FPGA avoids the initial cost, lengthy development cycles, and inherent risk of conventional ASICs. Also, FPGA programmability permits design upgrades in the field with no hardware replacement necessary (impossible with ASICs).

## **Features**

- Second generation ASIC replacement technology

- Densities as high as 5,292 logic cells with up to 200,000 system gates

- Streamlined features based on Virtex<sup>®</sup> FPGA architecture

- Unlimited reprogrammability

- Very low cost

- Cost-effective 0.18 micron process

- System level features

- SelectRAM™ hierarchical memory:

- · 16 bits/LUT distributed RAM

- · Configurable 4K bit block RAM

- · Fast interfaces to external RAM

- Fully PCI compliant

- Low-power segmented routing architecture

- Full readback ability for verification/observability

- Dedicated carry logic for high-speed arithmetic

- Efficient multiplier support

- Cascade chain for wide-input functions

- Abundant registers/latches with enable, set, reset

- Four dedicated DLLs for advanced clock control

- Four primary low-skew global clock distribution nets

- IEEE 1149.1 compatible boundary scan logic

- Versatile I/O and packaging

- Pb-free package options

- Low-cost packages available in all densities

- Family footprint compatibility in common packages

- 16 high-performance interface standards

- Hot swap Compact PCI friendly

- Zero hold time simplifies system timing

- Core logic powered at 2.5V and I/Os powered at 1.5V, 2.5V, or 3.3V

- Fully supported by powerful Xilinx® ISE® development system

- Fully automatic mapping, placement, and routing

Table 1: Spartan-II FPGA Family Members

| Device  | Logic<br>Cells | System Gates<br>(Logic and RAM) | CLB<br>Array<br>(R x C) | Total<br>CLBs | Maximum<br>Available<br>User I/O <sup>(1)</sup> | Total<br>Distributed RAM<br>Bits | Total<br>Block RAM<br>Bits |

|---------|----------------|---------------------------------|-------------------------|---------------|-------------------------------------------------|----------------------------------|----------------------------|

| XC2S15  | 432            | 15,000                          | 8 x 12                  | 96            | 86                                              | 6,144                            | 16K                        |

| XC2S30  | 972            | 30,000                          | 12 x 18                 | 216           | 92                                              | 13,824                           | 24K                        |

| XC2S50  | 1,728          | 50,000                          | 16 x 24                 | 384           | 176                                             | 24,576                           | 32K                        |

| XC2S100 | 2,700          | 100,000                         | 20 x 30                 | 600           | 176                                             | 38,400                           | 40K                        |

| XC2S150 | 3,888          | 150,000                         | 24 x 36                 | 864           | 260                                             | 55,296                           | 48K                        |

| XC2S200 | 5,292          | 200,000                         | 28 x 42                 | 1,176         | 284                                             | 75,264                           | 56K                        |

#### Notes:

© 2000-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

<sup>1.</sup> All user I/O counts do not include the four global clock/user input pins. See details in Table 2, page 4.

## **General Overview**

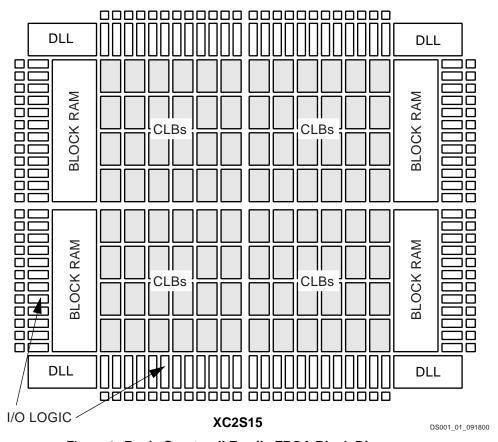

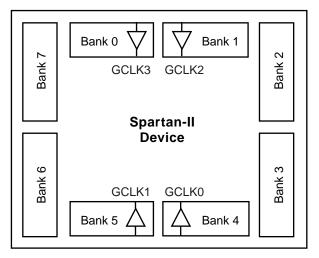

The Spartan-II family of FPGAs have a regular, flexible, programmable architecture of Configurable Logic Blocks (CLBs), surrounded by a perimeter of programmable Input/Output Blocks (IOBs). There are four Delay-Locked Loops (DLLs), one at each corner of the die. Two columns of block RAM lie on opposite sides of the die, between the CLBs and the IOB columns. These functional elements are interconnected by a powerful hierarchy of versatile routing channels (see Figure 1).

Spartan-II FPGAs are customized by loading configuration data into internal static memory cells. Unlimited reprogramming cycles are possible with this approach. Stored values in these cells determine logic functions and interconnections implemented in the FPGA. Configuration data can be read from an external serial PROM (master

serial mode), or written into the FPGA in slave serial, slave parallel, or Boundary Scan modes.

Spartan-II FPGAs are typically used in high-volume applications where the versatility of a fast programmable solution adds benefits. Spartan-II FPGAs are ideal for shortening product development cycles while offering a cost-effective solution for high volume production.

Spartan-II FPGAs achieve high-performance, low-cost operation through advanced architecture and semiconductor technology. Spartan-II devices provide system clock rates up to 200 MHz. In addition to the conventional benefits of high-volume programmable logic solutions, Spartan-II FPGAs also offer on-chip synchronous single-port and dual-port RAM (block and distributed form), DLL clock drivers, programmable set and reset on all flip-flops, fast carry logic, and many other features.

Figure 1: Basic Spartan-II Family FPGA Block Diagram

Similarly, the F6 multiplexer combines the outputs of all four function generators in the CLB by selecting one of the F5-multiplexer outputs. This permits the implementation of any 6-input function, an 8:1 multiplexer, or selected functions of up to 19 inputs.

Each CLB has four direct feedthrough paths, one per LC. These paths provide extra data input lines or additional local routing that does not consume logic resources.

## Arithmetic Logic

Dedicated carry logic provides capability for high-speed arithmetic functions. The Spartan-II FPGA CLB supports two separate carry chains, one per slice. The height of the carry chains is two bits per CLB.

The arithmetic logic includes an XOR gate that allows a 1-bit full adder to be implemented within an LC. In addition, a dedicated AND gate improves the efficiency of multiplier implementation.

The dedicated carry path can also be used to cascade function generators for implementing wide logic functions.

#### **BUFTs**

Each Spartan-II FPGA CLB contains two 3-state drivers (BUFTs) that can drive on-chip busses. See "Dedicated Routing," page 12. Each Spartan-II FPGA BUFT has an independent 3-state control pin and an independent input pin.

## **Block RAM**

Spartan-II FPGAs incorporate several large block RAM memories. These complement the distributed RAM Look-Up Tables (LUTs) that provide shallow memory structures implemented in CLBs.

Block RAM memory blocks are organized in columns. All Spartan-II devices contain two such columns, one along each vertical edge. These columns extend the full height of the chip. Each memory block is four CLBs high, and consequently, a Spartan-II device eight CLBs high will contain two memory blocks per column, and a total of four blocks.

Table 5: Spartan-II Block RAM Amounts

| Spartan-II<br>Device | # of Blocks | Total Block RAM<br>Bits |

|----------------------|-------------|-------------------------|

| XC2S15               | 4           | 16K                     |

| XC2S30               | 6           | 24K                     |

| XC2S50               | 8           | 32K                     |

| XC2S100              | 10          | 40K                     |

| XC2S150              | 12          | 48K                     |

| XC2S200              | 14          | 56K                     |

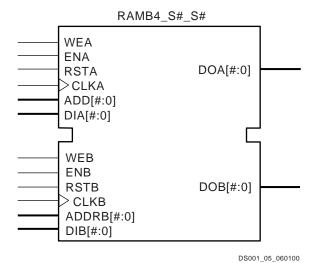

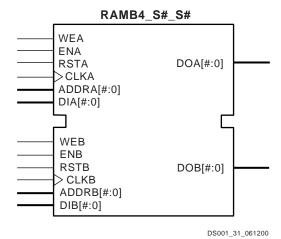

Each block RAM cell, as illustrated in Figure 5, is a fully synchronous dual-ported 4096-bit RAM with independent control signals for each port. The data widths of the two ports can be configured independently, providing built-in bus-width conversion.

Figure 5: Dual-Port Block RAM

Table 6 shows the depth and width aspect ratios for the block RAM.

Table 6: Block RAM Port Aspect Ratios

| Width | Depth | ADDR Bus   | Data Bus   |

|-------|-------|------------|------------|

| 1     | 4096  | ADDR<11:0> | DATA<0>    |

| 2     | 2048  | ADDR<10:0> | DATA<1:0>  |

| 4     | 1024  | ADDR<9:0>  | DATA<3:0>  |

| 8     | 512   | ADDR<8:0>  | DATA<7:0>  |

| 16    | 256   | ADDR<7:0>  | DATA<15:0> |

The Spartan-II FPGA block RAM also includes dedicated routing to provide an efficient interface with both CLBs and other block RAMs.

## **Programmable Routing Matrix**

It is the longest delay path that limits the speed of any worst-case design. Consequently, the Spartan-II routing architecture and its place-and-route software were defined in a single optimization process. This joint optimization minimizes long-path delays, and consequently, yields the best system performance.

The joint optimization also reduces design compilation times because the architecture is software-friendly. Design cycles are correspondingly reduced due to shorter design iteration times.

Boundary-scan operation is independent of individual IOB configurations, and unaffected by package type. All IOBs, including unbonded ones, are treated as independent 3-state bidirectional pins in a single scan chain. Retention of the bidirectional test capability after configuration facilitates the testing of external interconnections.

Table 7 lists the boundary-scan instructions supported in Spartan-II FPGAs. Internal signals can be captured during EXTEST by connecting them to unbonded or unused IOBs. They may also be connected to the unused outputs of IOBs defined as unidirectional input pins.

Table 7: Boundary-Scan Instructions

| Boundary-Scan<br>Command | Binary<br>Code[4:0] | Description                                                   |

|--------------------------|---------------------|---------------------------------------------------------------|

| EXTEST                   | 00000               | Enables boundary-scan EXTEST operation                        |

| SAMPLE                   | 00001               | Enables boundary-scan SAMPLE operation                        |

| USR1                     | 00010               | Access user-defined register 1                                |

| USR2                     | 00011               | Access user-defined register 2                                |

| CFG_OUT                  | 00100               | Access the configuration bus for Readback                     |

| CFG_IN                   | 00101               | Access the configuration bus for Configuration                |

| INTEST                   | 00111               | Enables boundary-scan INTEST operation                        |

| USRCODE                  | 01000               | Enables shifting out USER code                                |

| IDCODE                   | 01001               | Enables shifting out of ID Code                               |

| HIZ                      | 01010               | Disables output pins<br>while enabling the<br>Bypass Register |

| JSTART                   | 01100               | Clock the start-up<br>sequence when<br>StartupClk is TCK      |

| BYPASS                   | 11111               | Enables BYPASS                                                |

| RESERVED                 | All other codes     | Xilinx <sup>®</sup> reserved instructions                     |

The public boundary-scan instructions are available prior to configuration. After configuration, the public instructions remain available together with any USERCODE instructions installed during the configuration. While the SAMPLE and BYPASS instructions are available during configuration, it is recommended that boundary-scan operations not be performed during this transitional period.

In addition to the test instructions outlined above, the boundary-scan circuitry can be used to configure the FPGA, and also to read back the configuration data.

To facilitate internal scan chains, the User Register provides three outputs (Reset, Update, and Shift) that represent the corresponding states in the boundary-scan internal state machine.

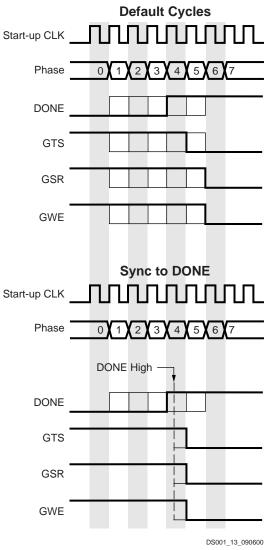

By default, these operations are synchronized to CCLK. The entire start-up sequence lasts eight cycles, called C0-C7, after which the loaded design is fully functional. The default timing for start-up is shown in the top half of Figure 13. The four operations can be selected to switch on any CCLK cycle C1-C6 through settings in the Xilinx software. Heavy lines show default settings.

Figure 13: Start-Up Waveforms

The bottom half of Figure 13 shows another commonly used version of the start-up timing known as Sync-to-DONE. This version makes the GTS, GSR, and GWE events conditional upon the DONE pin going High. This timing is important for a daisy chain of multiple FPGAs in serial mode, since it ensures that all FPGAs go through start-up together, after all their DONE pins have gone High.

Sync-to-DONE timing is selected by setting the GTS, GSR, and GWE cycles to a value of DONE in the configuration options. This causes these signals to transition one clock cycle after DONE externally transitions High.

#### **Serial Modes**

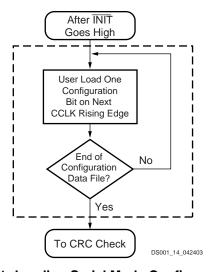

There are two serial configuration modes: In Master Serial mode, the FPGA controls the configuration process by driving CCLK as an output. In Slave Serial mode, the FPGA passively receives CCLK as an input from an external agent (e.g., a microprocessor, CPLD, or second FPGA in master mode) that is controlling the configuration process. In both modes, the FPGA is configured by loading one bit per CCLK cycle. The MSB of each configuration data byte is always written to the DIN pin first.

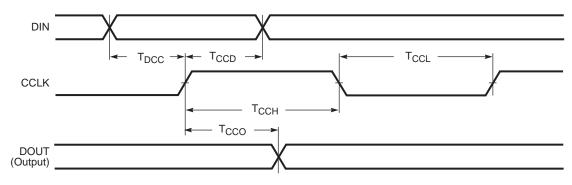

See Figure 14 for the sequence for loading data into the Spartan-II FPGA serially. This is an expansion of the "Load Configuration Data Frames" block in Figure 11. Note that  $\overline{\text{CS}}$  and  $\overline{\text{WRITE}}$  normally are not used during serial configuration. To ensure successful loading of the FPGA, do not toggle  $\overline{\text{WRITE}}$  with  $\overline{\text{CS}}$  Low during serial configuration.

Figure 14: Loading Serial Mode Configuration Data

DS001\_16\_032300

| Symbol           |      | Description       |    | Units    |

|------------------|------|-------------------|----|----------|

| T <sub>DCC</sub> |      | DIN setup         | 5  | ns, min  |

| T <sub>CCD</sub> |      | DIN hold          | 0  | ns, min  |

| T <sub>CCO</sub> | CCLK | DOUT              | 12 | ns, max  |

| T <sub>CCH</sub> | COLK | High time         | 5  | ns, min  |

| T <sub>CCL</sub> |      | Low time          | 5  | ns, min  |

| F <sub>CC</sub>  |      | Maximum frequency | 66 | MHz, max |

Figure 16: Slave Serial Mode Timing

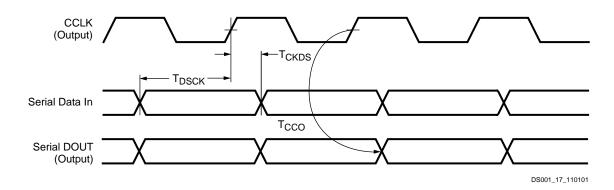

#### Master Serial Mode

In Master Serial mode, the CCLK output of the FPGA drives a Xilinx PROM which feeds a serial stream of configuration data to the FPGA's DIN input. Figure 15 shows a Master Serial FPGA configuring a Slave Serial FPGA from a PROM. A Spartan-II device in Master Serial mode should be connected as shown for the device on the left side. Master Serial mode is selected by a <00x> on the mode pins (M0, M1, M2). The PROM RESET pin is driven by INIT, and CE input is driven by DONE. The interface is identical to the slave serial mode except that an oscillator internal to the FPGA is used to generate the configuration clock (CCLK). Any of a number of different frequencies ranging from 4 to 60 MHz can be set using the ConfigRate option in the Xilinx software. On power-up, while the first 60 bytes of

the configuration data are being loaded, the CCLK frequency is always 2.5 MHz. This frequency is used until the ConfigRate bits, part of the configuration file, have been loaded into the FPGA, at which point, the frequency changes to the selected ConfigRate. Unless a different frequency is specified in the design, the default ConfigRate is 4 MHz. The frequency of the CCLK signal created by the internal oscillator has a variance of +45%, -30% from the specified value.

Figure 17 shows the timing for Master Serial configuration. The FPGA accepts one bit of configuration data on each rising CCLK edge. After the FPGA has been loaded, the data for the next device in a daisy-chain is presented on the DOUT pin after the rising CCLK edge.

| Symbol            |      | Description                                 |            | Units   |

|-------------------|------|---------------------------------------------|------------|---------|

| T <sub>DSCK</sub> |      | DIN setup                                   | 5.0        | ns, min |

| T <sub>CKDS</sub> | CCLK | DIN hold                                    | 0.0        | ns, min |

|                   |      | Frequency tolerance with respect to nominal | +45%, -30% | -       |

Figure 17: Master Serial Mode Timing

#### **Slave Parallel Mode**

The Slave Parallel mode is the fastest configuration option. Byte-wide data is written into the FPGA. A BUSY flag is provided for controlling the flow of data at a clock frequency  $F_{\rm CCNH}$  above 50 MHz.

Figure 18, page 24 shows the connections for two Spartan-II devices using the Slave Parallel mode. Slave Parallel mode is selected by a <011> on the mode pins (M0, M1, M2).

If a configuration file of the format .bit, .rbt, or non-swapped HEX is used for parallel programming, then the most significant bit (i.e. the left-most bit of each configuration byte, as displayed in a text editor) must be routed to the D0 input on the FPGA.

The agent controlling configuration is not shown. Typically, a processor, a microcontroller, or CPLD controls the Slave Parallel interface. The controlling agent provides byte-wide configuration data, CCLK, a Chip Select  $(\overline{CS})$  signal and a Write signal  $(\overline{WRITE})$ . If BUSY is asserted (High) by the FPGA, the data must be held until BUSY goes Low.

After configuration, the pins of the Slave Parallel port (D0-D7) can be used as additional user I/O. Alternatively, the port may be retained to permit high-speed 8-bit readback. Then data can be read by de-asserting WRITE. See "Readback," page 25.

## **Useful Application Examples**

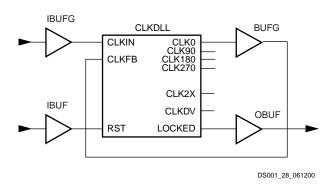

The Spartan-II FPGA DLL can be used in a variety of creative and useful applications. The following examples show some of the more common applications.

## Standard Usage

The circuit shown in Figure 28 resembles the BUFGDLL macro implemented to provide access to the RST and LOCKED pins of the CLKDLL.

Figure 28: Standard DLL Implementation

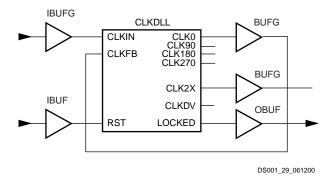

## Deskew of Clock and Its 2x Multiple

The circuit shown in Figure 29 implements a 2x clock multiplier and also uses the CLK0 clock output with zero ns skew between registers on the same chip. A clock divider circuit could alternatively be implemented using similar connections.

Figure 29: DLL Deskew of Clock and 2x Multiple

Because any single DLL can only access at most two BUFGs, any additional output clock signals must be routed from the DLL in this example on the high speed backbone routing.

#### Generating a 4x Clock

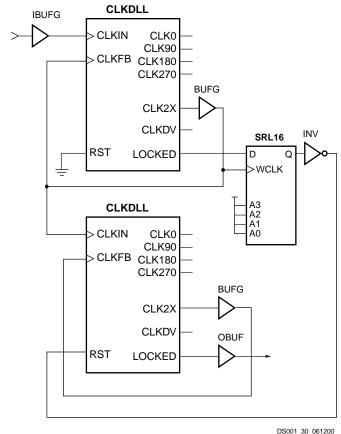

By connecting two DLL circuits each implementing a 2x clock multiplier in series as shown in Figure 30, a 4x clock multiply can be implemented with zero skew between registers in the same device.

If other clock output is needed, the clock could access a BUFG only if the DLLs are constrained to exist on opposite edges (Top or Bottom) of the device.

DS001\_30\_061200

Figure 30: DLL Generation of 4x Clock

When using this circuit it is vital to use the SRL16 cell to reset the second DLL after the initial chip reset. If this is not done, the second DLL may not recognize the change of frequencies from when the input changes from a 1x (25/75) waveform to a 2x (50/50) waveform. It is not recommended to cascade more than two DLLs.

For design examples and more information on using the DLL, see XAPP174, Using Delay-Locked Loops in Spartan-II FPGAs.

## **Using Block RAM Features**

The Spartan-II FPGA family provides dedicated blocks of on-chip, true dual-read/write port synchronous RAM, with 4096 memory cells. Each port of the block RAM memory can be independently configured as a read/write port, a read port, a write port, and can be configured to a specific data width. The block RAM memory offers new capabilities allowing the FPGA designer to simplify designs.

## **Operating Modes**

Block RAM memory supports two operating modes.

- Read Through

- Write Back

## Read Through (One Clock Edge)

The read address is registered on the read port clock edge and data appears on the output after the RAM access time. Some memories may place the latch/register at the outputs depending on the desire to have a faster clock-to-out versus setup time. This is generally considered to be an inferior solution since it changes the read operation to an asynchronous function with the possibility of missing an address/control line transition during the generation of the read pulse clock.

## Write Back (One Clock Edge)

The write address is registered on the write port clock edge and the data input is written to the memory and mirrored on the write port input.

#### **Block RAM Characteristics**

- 1. All inputs are registered with the port clock and have a setup to clock timing specification.

- All outputs have a read through or write back function depending on the state of the port WE pin. The outputs relative to the port clock are available after the clock-to-out timing specification.

- The block RAM are true SRAM memories and do not have a combinatorial path from the address to the output. The LUT cells in the CLBs are still available with this function.

- 4. The ports are completely independent from each other (*i.e.*, clocking, control, address, read/write function, and data width) without arbitration.

- 5. A write operation requires only one clock edge.

- 6. A read operation requires only one clock edge.

The output ports are latched with a self timed circuit to guarantee a glitch free read. The state of the output port will not change until the port executes another read or write operation.

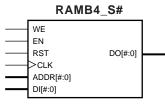

## **Library Primitives**

Figure 31 and Figure 32 show the two generic library block RAM primitives. Table 11 describes all of the available primitives for synthesis and simulation.

Figure 31: Dual-Port Block RAM Memory

DS001\_32\_061200

Figure 32: Single-Port Block RAM Memory

Table 11: Available Library Primitives

| Primitive    | Port A Width | Port B Width |

|--------------|--------------|--------------|

| RAMB4_S1     | 1            | N/A          |

| RAMB4_S1_S1  |              | 1            |

| RAMB4_S1_S2  |              | 2            |

| RAMB4_S1_S4  |              | 4            |

| RAMB4_S1_S8  |              | 8            |

| RAMB4_S1_S16 |              | 16           |

| RAMB4_S2     | 2            | N/A          |

| RAMB4_S2_S2  |              | 2            |

| RAMB4_S2_S4  |              | 4            |

| RAMB4_S2_S8  |              | 8            |

| RAMB4_S2_S16 |              | 16           |

Table 11: Available Library Primitives

| Primitive     | Port A Width | Port B Width |

|---------------|--------------|--------------|

| RAMB4_S4      | 4            | N/A          |

| RAMB4_S4_S4   |              | 4            |

| RAMB4_S4_S8   |              | 8            |

| RAMB4_S4_S16  |              | 16           |

| RAMB4_S8      | 8            | N/A          |

| RAMB4_S8_S8   |              | 8            |

| RAMB4_S8_S16  |              | 16           |

| RAMB4_S16     | 16           | N/A          |

| RAMB4_S16_S16 |              | 16           |

## **Port Signals**

Each block RAM port operates independently of the others while accessing the same set of 4096 memory cells.

Table 12 describes the depth and width aspect ratios for the block RAM memory.

Table 12: Block RAM Port Aspect Ratios

| Width | Depth | ADDR Bus   | Data Bus   |

|-------|-------|------------|------------|

| 1     | 4096  | ADDR<11:0> | DATA<0>    |

| 2     | 2048  | ADDR<10:0> | DATA<1:0>  |

| 4     | 1024  | ADDR<9:0>  | DATA<3:0>  |

| 8     | 512   | ADDR<8:0>  | DATA<7:0>  |

| 16    | 256   | ADDR<7:0>  | DATA<15:0> |

#### Clock—CLK[A|B]

Each port is fully synchronous with independent clock pins. All port input pins have setup time referenced to the port CLK pin. The data output bus has a clock-to-out time referenced to the CLK pin.

## Enable—EN[A/B]

The enable pin affects the read, write and reset functionality of the port. Ports with an inactive enable pin keep the output pins in the previous state and do not write data to the memory cells.

## Write Enable—WE[A|B]

Activating the write enable pin allows the port to write to the memory cells. When active, the contents of the data input bus are written to the RAM at the address pointed to by the address bus, and the new data also reflects on the data out bus. When inactive, a read operation occurs and the contents of the memory cells referenced by the address bus reflect on the data out bus.

#### Reset—RST[A|B]

The reset pin forces the data output bus latches to zero synchronously. This does not affect the memory cells of the RAM and does not disturb a write operation on the other port.

#### Address Bus-ADDR[A|B]<#:0>

The address bus selects the memory cells for read or write. The width of the port determines the required width of this bus as shown in Table 12.

## Data In Bus-DI[A/B]<#:0>

The data in bus provides the new data value to be written into the RAM. This bus and the port have the same width, as shown in Table 12.

## Data Output Bus-DO[A|B]<#:0>

The data out bus reflects the contents of the memory cells referenced by the address bus at the last active clock edge. During a write operation, the data out bus reflects the data in bus. The width of this bus equals the width of the port. The allowed widths appear in Table 12.

## **Inverting Control Pins**

The four control pins (CLK, EN, WE and RST) for each port have independent inversion control as a configuration option.

## **Address Mapping**

Each port accesses the same set of 4096 memory cells using an addressing scheme dependent on the width of the port. The physical RAM location addressed for a particular width are described in the following formula (of interest only when the two ports use different aspect ratios).

Start =

$$([ADDR_{port} + 1] * Width_{port}) - 1$$

End =  $ADDR_{port} * Width_{port}$

Table 13 shows low order address mapping for each port width.

Table 13: Port Address Mapping

| Port<br>Widt<br>h |      |            |            | Ac      |        | ort<br>es |        | s      |        |        |        |        |        |        |        |

|-------------------|------|------------|------------|---------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 1                 | 4095 | 1 1<br>5 4 | 1 1<br>3 2 | 1<br>1  | 1<br>0 | 0<br>9    | 0<br>8 | 0<br>7 | 0<br>6 | 0<br>5 | 0<br>4 | 0<br>3 | 0<br>2 | 0<br>1 | 0<br>0 |

| 2                 | 2047 | 07         | 06         | 6 05 04 |        | 4         | 03 02  |        | 2      | 01     |        | 00     |        |        |        |

| 4                 | 1023 | C          | 03 02      |         |        |           | 0      | 1      |        |        | 0      | 0      |        |        |        |

| 8                 | 511  | 01 00      |            |         |        |           |        |        |        |        |        |        |        |        |        |

| 16                | 255  |            | 00         |         |        |           |        |        |        |        |        |        |        |        |        |

support of a wide variety of applications, from general purpose standard applications to high-speed low-voltage memory busses.

Versatile I/O blocks also provide selectable output drive strengths and programmable slew rates for the LVTTL output buffers, as well as an optional, programmable weak pull-up, weak pull-down, or weak "keeper" circuit ideal for use in external bussing applications.

Each Input/Output Block (IOB) includes three registers, one each for the input, output, and 3-state signals within the IOB. These registers are optionally configurable as either a D-type flip-flop or as a level sensitive latch.

The input buffer has an optional delay element used to guarantee a zero hold time requirement for input signals registered within the IOB.

The Versatile I/O features also provide dedicated resources for input reference voltage ( $V_{REF}$ ) and output source voltage ( $V_{CCO}$ ), along with a convenient banking system that simplifies board design.

By taking advantage of the built-in features and wide variety of I/O standards supported by the Versatile I/O features, system-level design and board design can be greatly simplified and improved.

#### **Fundamentals**

Modern bus applications, pioneered by the largest and most influential companies in the digital electronics industry, are commonly introduced with a new I/O standard tailored specifically to the needs of that application. The bus I/O standards provide specifications to other vendors who create products designed to interface with these applications. Each standard often has its own specifications for current, voltage, I/O buffering, and termination techniques.

The ability to provide the flexibility and time-to-market advantages of programmable logic is increasingly dependent on the capability of the programmable logic device to support an ever increasing variety of I/O standards

The Versatile I/O resources feature highly configurable input and output buffers which provide support for a wide variety of I/O standards. As shown in Table 15, each buffer type can support a variety of voltage requirements.

Table 15: Versatile I/O Supported Standards (Typical Values)

|                               | T                                                    |                                                    | T                                                     |

|-------------------------------|------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|

| I/O Standard                  | Input<br>Reference<br>Voltage<br>(V <sub>REF</sub> ) | Output<br>Source<br>Voltage<br>(V <sub>CCO</sub> ) | Board<br>Termination<br>Voltage<br>(V <sub>TT</sub> ) |

| LVTTL (2-24 mA)               | N/A                                                  | 3.3                                                | N/A                                                   |

| LVCMOS2                       | N/A                                                  | 2.5                                                | N/A                                                   |

| PCI (3V/5V,<br>33 MHz/66 MHz) | N/A                                                  | 3.3                                                | N/A                                                   |

| GTL                           | 0.8                                                  | N/A                                                | 1.2                                                   |

| GTL+                          | 1.0                                                  | N/A                                                | 1.5                                                   |

| HSTL Class I                  | 0.75                                                 | 1.5                                                | 0.75                                                  |

| HSTL Class III                | 0.9                                                  | 1.5                                                | 1.5                                                   |

| HSTL Class IV                 | 0.9                                                  | 1.5                                                | 1.5                                                   |

| SSTL3 Class I and II          | 1.5                                                  | 3.3                                                | 1.5                                                   |

| SSTL2 Class I and II          | 1.25                                                 | 2.5                                                | 1.25                                                  |

| CTT                           | 1.5                                                  | 3.3                                                | 1.5                                                   |

| AGP-2X                        | 1.32                                                 | 3.3                                                | N/A                                                   |

## Overview of Supported I/O Standards

This section provides a brief overview of the I/O standards supported by all Spartan-II devices.

While most I/O standards specify a range of allowed voltages, this document records typical voltage values only. Detailed information on each specification may be found on the Electronic Industry Alliance JEDEC website at <a href="http://www.jedec.org">http://www.jedec.org</a>. For more details on the I/O standards and termination application examples, see <a href="XAPP179">XAPP179</a>, "Using SelectIO Interfaces in Spartan-II and Spartan-IIE FPGAs."

## LVTTL — Low-Voltage TTL

The Low-Voltage TTL (LVTTL) standard is a general purpose EIA/JESDSA standard for 3.3V applications that uses an LVTTL input buffer and a Push-Pull output buffer. This standard requires a 3.3V output source voltage ( $V_{CCO}$ ), but does not require the use of a reference voltage ( $V_{REF}$ ) or a termination voltage ( $V_{TT}$ ).

#### LVCMOS2 — Low-Voltage CMOS for 2.5V

The Low-Voltage CMOS for 2.5V or lower (LVCMOS2) standard is an extension of the LVCMOS standard (JESD 8.5) used for general purpose 2.5V applications. This standard requires a 2.5V output source voltage ( $V_{CCO}$ ), but does not require the use of a reference voltage ( $V_{REF}$ ) or a board termination voltage ( $V_{TT}$ ).

the LOC property is described below. Table 16 summarizes the input standards compatibility requirements.

An optional delay element is associated with each IBUF. When the IBUF drives a flip-flop within the IOB, the delay element by default activates to ensure a zero hold-time requirement. The NODELAY=TRUE property overrides this default.

When the IBUF does not drive a flip-flop within the IOB, the delay element de-activates by default to provide higher performance. To delay the input signal, activate the delay element with the DELAY=TRUE property.

DS001\_03\_060100

Figure 36: I/O Banks

**Table 16: Xilinx Input Standards Compatibility Requirements**

| Rule 1 | All differential amplifier input signals within a bank are required to be of the same standard.         |

|--------|---------------------------------------------------------------------------------------------------------|

| Rule 2 | There are no placement restrictions for inputs with standards that require a single-ended input buffer. |

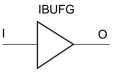

#### **IBUFG**

Signals used as high fanout clock inputs to the Spartan-II device should drive a global clock input buffer (IBUFG) via an external input port in order to take advantage of one of the four dedicated global clock distribution networks. The output of the IBUFG primitive can

only drive a CLKDLL, CLKDLLHF, or a BUFG primitive. The generic IBUFG primitive appears in Figure 37.

Figure 37: Global Clock Input Buffer (IBUFG) Primitive

DS001 37 061200

With no extension or property specified for the generic IBUFG primitive, the assumed standard is LVTTL.

The voltage reference signal is "banked" within the Spartan-II device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 36 for a representation of the I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input.

IBUFG placement restrictions require any differential amplifier input signals within a bank be of the same standard. The LOC property can specify a location for the IBUFG.

As an added convenience, the BUFGP can be used to instantiate a high fanout clock input. The BUFGP primitive represents a combination of the LVTTL IBUFG and BUFG primitives, such that the output of the BUFGP can connect directly to the clock pins throughout the design.

The Spartan-II FPGA BUFGP primitive can only be placed in a global clock pad location. The LOC property can specify a location for the BUFGP.

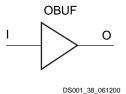

#### **OBUF**

An OBUF must drive outputs through an external output port. The generic output buffer (OBUF) primitive appears in Figure 38.

Figure 38: Output Buffer (OBUF) Primitive

With no extension or property specified for the generic OBUF primitive, the assumed standard is slew rate limited LVTTL with 12 mA drive strength.

The LVTTL OBUF additionally can support one of two slew rate modes to minimize bus transients. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals.

# **Revision History**

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09/18/00 | 2.0     | Sectioned the Spartan-II Family data sheet into four modules. Corrected banking description.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 03/05/01 | 2.1     | Clarified guidelines for applying power to V <sub>CCINT</sub> and V <sub>CCO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 09/03/03 | 2.2     | <ul> <li>The following changes were made:</li> <li>"Serial Modes," page 20 cautions about toggling WRITE during serial configuration.</li> <li>Maximum V<sub>IH</sub> values in Table 32 and Table 33 changed to 5.5V.</li> <li>In "Boundary Scan," page 13, removed sentence about lack of INTEST support.</li> <li>In Table 9, page 17, added note about the state of I/Os after power-on.</li> <li>In "Slave Parallel Mode," page 23, explained configuration bit alignment to SelectMap port.</li> </ul> |

| 06/13/08 | 2.8     | Added note that TDI, TMS, and TCK have a default pull-up resistor. Added note on maximum daisy chain limit. Updated Figure 15 and Figure 18 since Mode pins can be pulled up to either 2.5V or 3.3V. Updated DLL section. Recommended using property or attribute instead of primitive to define I/O properties. Updated description and links. Updated all modules for continuous page, figure, and table numbering. Synchronized all modules to v2.8.                                                      |

## **Power-On Requirements**

Spartan-II FPGAs require that a minimum supply current  $I_{CCPO}$  be provided to the  $V_{CCINT}$  lines for a successful power-on. If more current is available, the FPGA can consume more than  $I_{CCPO}$  minimum, though this cannot adversely affect reliability.

A maximum limit for  $I_{CCPO}$  is not specified. Therefore the use of foldback/crowbar supplies and fuses deserves special attention. In these cases, limit the  $I_{CCPO}$  current to a level below the trip point for over-current protection in order to avoid inadvertently shutting down the supply.

|                                    |                                 | Conditions                                                           |                                | New Requirements <sup>(1)</sup> For Devices with Date Code 0321 or Later |     | Old Requirements <sup>(1)</sup> For Devices with Date Code before 0321 |     |       |

|------------------------------------|---------------------------------|----------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------|-----|------------------------------------------------------------------------|-----|-------|

| Symbol                             | Description                     | Junction<br>Temperature <sup>(2)</sup>                               | Device<br>Temperature<br>Grade | Min                                                                      | Max | Min                                                                    | Max | Units |

| I <sub>CCPO</sub> (3)              | Total V <sub>CCINT</sub> supply | $-40^{\circ}\text{C} \le T_{J} < -20^{\circ}\text{C}$                | Industrial                     | 1.50                                                                     | -   | 2.00                                                                   | -   | Α     |

|                                    | current required                | $-20^{\circ}\text{C} \le T_{\text{J}} < 0^{\circ}\text{C}$           | Industrial                     | 1.00                                                                     | -   | 2.00                                                                   | -   | Α     |

|                                    | during power-on                 | $0^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 85^{\circ}\text{C}$ | Commercial                     | 0.25                                                                     | -   | 0.50                                                                   | -   | Α     |

|                                    |                                 | $85^{\circ}\text{C} < \text{T}_{\text{J}} \le 100^{\circ}\text{C}$   | Industrial                     | 0.50                                                                     | -   | 0.50                                                                   | -   | Α     |

| T <sub>CCPO</sub> <sup>(4,5)</sup> | V <sub>CCINT</sub> ramp time    | –40°C≤ T <sub>J</sub> ≤ 100°C                                        | All                            | -                                                                        | 50  | -                                                                      | 50  | ms    |

#### Notes:

- 1. The date code is printed on the top of the device's package. See the "Device Part Marking" section in Module 1.

- 2. The expected T<sub>J</sub> range for the design determines the I<sub>CCPO</sub> minimum requirement. Use the applicable ranges in the junction temperature column to find the associated current values in the appropriate new or old requirements column according to the date code. Then choose the highest of these current values to serve as the minimum I<sub>CCPO</sub> requirement that must be met. For example, if the junction temperature for a given design is -25°C ≤ T<sub>J</sub> ≤ 75°C, then the new minimum I<sub>CCPO</sub> requirement is 1.5A. If 5°C ≤ T<sub>J</sub> ≤ 90°C, then the new minimum I<sub>CCPO</sub> requirement is 0.5A.

- 3. The I<sub>CCPO</sub> requirement applies for a brief time (commonly only a few milliseconds) when V<sub>CCINT</sub> ramps from 0 to 2.5V.

- The ramp time is measured from GND to V<sub>CCINT</sub> max on a fully loaded board.

- 5. During power-on, the V<sub>CCINT</sub> ramp must increase steadily in voltage with no dips.

- 6. For more information on designing to meet the power-on specifications, refer to the application note <a href="XAPP450">XAPP450 "Power-On Current Requirements for the Spartan-II and Spartan-IIE Families"</a>

## **DC Input and Output Levels**

Values for  $V_{IL}$  and  $V_{IH}$  are recommended input voltages. Values for  $V_{OL}$  and  $V_{OH}$  are guaranteed output voltages over the recommended operating conditions. Only selected standards are tested. These are chosen to ensure that all

standards meet their specifications. The selected standards are tested at minimum  $V_{CCO}$  with the respective  $I_{OL}$  and  $I_{OH}$  currents shown. Other standards are sample tested.

| Input/Output         |        | V <sub>IL</sub>         | V                       | İH                     | V <sub>OL</sub>        | V <sub>OH</sub>        | l <sub>OL</sub> | I <sub>OH</sub> |

|----------------------|--------|-------------------------|-------------------------|------------------------|------------------------|------------------------|-----------------|-----------------|

| Standard             | V, Min | V, Max                  | V, Min                  | V, Max                 | V, Max                 | V, Min                 | mA              | mA              |

| LVTTL <sup>(1)</sup> | -0.5   | 0.8                     | 2.0                     | 5.5                    | 0.4                    | 2.4                    | 24              | -24             |

| LVCMOS2              | -0.5   | 0.7                     | 1.7                     | 5.5                    | 0.4                    | 1.9                    | 12              | -12             |

| PCI, 3.3V            | -0.5   | 44% V <sub>CCINT</sub>  | 60% V <sub>CCINT</sub>  | V <sub>CCO</sub> + 0.5 | 10% V <sub>CCO</sub>   | 90% V <sub>CCO</sub>   | Note (2)        | Note (2)        |

| PCI, 5.0V            | -0.5   | 0.8                     | 2.0                     | 5.5                    | 0.55                   | 2.4                    | Note (2)        | Note (2)        |

| GTL                  | -0.5   | V <sub>REF</sub> - 0.05 | V <sub>REF</sub> + 0.05 | 3.6                    | 0.4                    | N/A                    | 40              | N/A             |

| GTL+                 | -0.5   | V <sub>REF</sub> – 0.1  | V <sub>REF</sub> + 0.1  | 3.6                    | 0.6                    | N/A                    | 36              | N/A             |

| HSTL I               | -0.5   | V <sub>REF</sub> – 0.1  | V <sub>REF</sub> + 0.1  | 3.6                    | 0.4                    | V <sub>CCO</sub> - 0.4 | 8               | -8              |

| HSTL III             | -0.5   | V <sub>REF</sub> – 0.1  | V <sub>REF</sub> + 0.1  | 3.6                    | 0.4                    | V <sub>CCO</sub> - 0.4 | 24              | -8              |

| HSTL IV              | -0.5   | V <sub>REF</sub> – 0.1  | V <sub>REF</sub> + 0.1  | 3.6                    | 0.4                    | V <sub>CCO</sub> - 0.4 | 48              | -8              |

| SSTL3 I              | -0.5   | V <sub>REF</sub> – 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | V <sub>REF</sub> - 0.6 | V <sub>REF</sub> + 0.6 | 8               | -8              |

| SSTL3 II             | -0.5   | V <sub>REF</sub> – 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | V <sub>REF</sub> - 0.8 | V <sub>REF</sub> + 0.8 | 16              | -16             |

| SSTL2 I              | -0.5   | V <sub>REF</sub> – 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | V <sub>REF</sub> - 0.6 | V <sub>REF</sub> + 0.6 | 7.6             | -7.6            |

| SSTL2 II             | -0.5   | V <sub>REF</sub> – 0.2  | V <sub>REF</sub> + 0.2  | 3.6                    | V <sub>REF</sub> - 0.8 | V <sub>REF</sub> + 0.8 | 15.2            | -15.2           |

## **CLB Switching Characteristics**

Delays originating at F/G inputs vary slightly according to the input used. The values listed below are worst-case. Precise values are provided by the timing analyzer.

|                                           |                                                                      | -6      | 6   |         | 5    |       |

|-------------------------------------------|----------------------------------------------------------------------|---------|-----|---------|------|-------|

| Symbol                                    | Description                                                          | Min     | Max | Min     | Max  | Units |

| Combinatorial Dela                        | ays                                                                  |         |     |         |      |       |

| T <sub>ILO</sub>                          | 4-input function: F/G inputs to X/Y outputs                          | -       | 0.6 | -       | 0.7  | ns    |

| T <sub>IF5</sub>                          | 5-input function: F/G inputs to F5 output                            | -       | 0.7 | -       | 0.9  | ns    |

| T <sub>IF5X</sub>                         | 5-input function: F/G inputs to X output                             | -       | 0.9 | -       | 1.1  | ns    |

| T <sub>IF6Y</sub>                         | 6-input function: F/G inputs to Y output via F6 MUX                  | -       | 1.0 | -       | 1.1  | ns    |

| T <sub>F5INY</sub>                        | 6-input function: F5IN input to Y output                             | -       | 0.4 | -       | 0.4  | ns    |

| T <sub>IFNCTL</sub>                       | Incremental delay routing through transparent latch to XQ/YQ outputs | -       | 0.7 | -       | 0.9  | ns    |

| T <sub>BYYB</sub>                         | BY input to YB output                                                | -       | 0.6 | -       | 0.7  | ns    |

| Sequential Delays                         | 1                                                                    |         |     |         |      |       |

| T <sub>CKO</sub>                          | FF clock CLK to XQ/YQ outputs                                        | -       | 1.1 | -       | 1.3  | ns    |

| T <sub>CKLO</sub>                         | Latch clock CLK to XQ/YQ outputs                                     | -       | 1.2 | -       | 1.5  | ns    |

| Setup/Hold Times                          | with Respect to Clock CLK <sup>(1)</sup>                             |         |     |         |      |       |

| T <sub>ICK</sub> / T <sub>CKI</sub>       | 4-input function: F/G inputs                                         | 1.3 / 0 | -   | 1.4 / 0 | -    | ns    |

| T <sub>IF5CK</sub> / T <sub>CKIF5</sub>   | 5-input function: F/G inputs                                         | 1.6 / 0 | -   | 1.8 / 0 | -    | ns    |

| T <sub>F5INCK</sub> / T <sub>CKF5IN</sub> | 6-input function: F5IN input                                         | 1.0 / 0 | -   | 1.1 / 0 | -    | ns    |

| T <sub>IF6CK</sub> / T <sub>CKIF6</sub>   | 6-input function: F/G inputs via F6 MUX                              | 1.6 / 0 | -   | 1.8 / 0 | -    | ns    |

| T <sub>DICK</sub> / T <sub>CKDI</sub>     | BX/BY inputs                                                         | 0.8 / 0 | -   | 0.8 / 0 | -    | ns    |

| T <sub>CECK</sub> / T <sub>CKCE</sub>     | CE input                                                             | 0.9 / 0 | -   | 0.9 / 0 | -    | ns    |

| T <sub>RCK</sub> / T <sub>CKR</sub>       | SR/BY inputs (synchronous)                                           | 0.8 / 0 | -   | 0.8/0   | -    | ns    |

| Clock CLK                                 |                                                                      |         |     |         |      |       |

| T <sub>CH</sub>                           | Minimum pulse width, High                                            | -       | 1.9 | -       | 1.9  | ns    |

| T <sub>CL</sub>                           | Minimum pulse width, Low                                             | -       | 1.9 | -       | 1.9  | ns    |

| Set/Reset                                 |                                                                      |         |     |         |      |       |

| T <sub>RPW</sub>                          | Minimum pulse width, SR/BY inputs                                    | 3.1     | -   | 3.1     | -    | ns    |

| $T_RQ$                                    | Delay from SR/BY inputs to XQ/YQ outputs (asynchronous)              | -       | 1.1 | -       | 1.3  | ns    |

| T <sub>IOGSRQ</sub>                       | Delay from GSR to XQ/YQ outputs                                      | -       | 9.9 | -       | 11.7 | ns    |

| F <sub>TOG</sub>                          | Toggle frequency (for export control)                                | -       | 263 | -       | 263  | MHz   |

#### Notes:

<sup>1.</sup> A zero hold time listing indicates no hold time or a negative hold time.

## **CLB Arithmetic Switching Characteristics**

Setup times not listed explicitly can be approximated by decreasing the combinatorial delays by the setup time adjustment listed. Precise values are provided by the timing analyzer.

|                                       |                                            |          | Speed Grade |         |     |       |  |

|---------------------------------------|--------------------------------------------|----------|-------------|---------|-----|-------|--|

|                                       |                                            | -(       | 6           |         | 5   |       |  |

| Symbol                                | Description                                | Min      | Max         | Min     | Max | Units |  |

| Combinatorial Del                     | ays                                        | "        |             |         |     | "     |  |

| T <sub>OPX</sub>                      | F operand inputs to X via XOR              | -        | 8.0         | -       | 0.9 | ns    |  |

| T <sub>OPXB</sub>                     | F operand input to XB output               | -        | 1.3         | -       | 1.5 | ns    |  |

| T <sub>OPY</sub>                      | F operand input to Y via XOR               | -        | 1.7         | -       | 2.0 | ns    |  |

| T <sub>OPYB</sub>                     | F operand input to YB output               | -        | 1.7         | -       | 2.0 | ns    |  |

| T <sub>OPCYF</sub>                    | F operand input to COUT output             | -        | 1.3         | -       | 1.5 | ns    |  |

| T <sub>OPGY</sub>                     | G operand inputs to Y via XOR              | -        | 0.9         | -       | 1.1 | ns    |  |

| T <sub>OPGYB</sub>                    | G operand input to YB output               | -        | 1.6         | -       | 2.0 | ns    |  |

| T <sub>OPCYG</sub>                    | G operand input to COUT output             | -        | 1.2         | -       | 1.4 | ns    |  |

| T <sub>BXCY</sub>                     | BX initialization input to COUT            | -        | 0.9         | -       | 1.0 | ns    |  |

| T <sub>CINX</sub>                     | CIN input to X output via XOR              | -        | 0.4         | -       | 0.5 | ns    |  |

| T <sub>CINXB</sub>                    | CIN input to XB                            | -        | 0.1         | -       | 0.1 | ns    |  |

| T <sub>CINY</sub>                     | CIN input to Y via XOR                     | -        | 0.5         | -       | 0.6 | ns    |  |

| T <sub>CINYB</sub>                    | CIN input to YB                            | -        | 0.6         | -       | 0.7 | ns    |  |

| T <sub>BYP</sub>                      | CIN input to COUT output                   | -        | 0.1         | -       | 0.1 | ns    |  |

| Multiplier Operation                  | on                                         | <u> </u> |             |         |     | 1     |  |

| T <sub>FANDXB</sub>                   | F1/2 operand inputs to XB output via AND   | -        | 0.5         | -       | 0.5 | ns    |  |

| T <sub>FANDYB</sub>                   | F1/2 operand inputs to YB output via AND   | -        | 0.9         | -       | 1.1 | ns    |  |

| T <sub>FANDCY</sub>                   | F1/2 operand inputs to COUT output via AND | -        | 0.5         | -       | 0.6 | ns    |  |

| T <sub>GANDYB</sub>                   | G1/2 operand inputs to YB output via AND   | -        | 0.6         | -       | 0.7 | ns    |  |

| T <sub>GANDCY</sub>                   | G1/2 operand inputs to COUT output via AND | -        | 0.2         | -       | 0.2 | ns    |  |

| Setup/Hold Times                      | with Respect to Clock CLK <sup>(1)</sup>   | 1        |             |         |     | 1     |  |

| T <sub>CCKX</sub> / T <sub>CKCX</sub> | CIN input to FFX                           | 1.1 / 0  | -           | 1.2/0   | -   | ns    |  |

| T <sub>CCKY</sub> / T <sub>CKCY</sub> | CIN input to FFY                           | 1.2 / 0  | -           | 1.3 / 0 | -   | ns    |  |

#### Notes:

<sup>1.</sup> A zero hold time listing indicates no hold time or a negative hold time.

## **Package Thermal Characteristics**

Table 39 provides the thermal characteristics for the various Spartan-II FPGA package offerings. This information is also available using the Thermal Query tool on xilinx.com (www.xilinx.com/cgi-bin/thermal/thermal.pl).

The junction-to-case thermal resistance  $(\theta_{JC})$  indicates the difference between the temperature measured on the package body (case) and the die junction temperature per watt of power consumption. The junction-to-board  $(\theta_{JB})$

Table 39: Spartan-II Package Thermal Characteristics

value similarly reports the difference between the board and junction temperature. The junction-to-ambient  $(\theta_{JA})$  value reports the temperature difference between the ambient environment and the junction temperature. The  $\theta_{JA}$  value is reported at different air velocities, measured in linear feet per minute (LFM). The "Still Air (0 LFM)" column shows the  $\theta_{JA}$  value in a system without a fan. The thermal resistance drops with increasing air flow.

| Package         | Device  | Junction-to-Case $(\theta_{\sf JC})$ | Junction-to-<br>Board (θ <sub>JB</sub> ) | Still Air<br>(0 LFM) | 250 LFM | 500 LFM | 750 LFM | Units   |

|-----------------|---------|--------------------------------------|------------------------------------------|----------------------|---------|---------|---------|---------|

| VQ100           | XC2S15  | 11.3                                 | N/A                                      | 44.1                 | 36.7    | 34.2    | 33.3    | °C/Watt |

| VQG100          | XC2S30  | 10.1                                 | N/A                                      | 40.7                 | 33.9    | 31.5    | 30.8    | °C/Watt |

|                 | XC2S15  | 7.3                                  | N/A                                      | 38.6                 | 30.0    | 25.7    | 24.1    | °C/Watt |

| TQ144           | XC2S30  | 6.7                                  | N/A                                      | 34.7                 | 27.0    | 23.1    | 21.7    | °C/Watt |

| TQG144          | XC2S50  | 5.8                                  | N/A                                      | 32.2                 | 25.1    | 21.4    | 20.1    | °C/Watt |

|                 | XC2S100 | 5.3                                  | N/A                                      | 31.4                 | 24.4    | 20.9    | 19.6    | °C/Watt |

| CS144<br>CSG144 | XC2S30  | 2.8                                  | N/A                                      | 34.0                 | 26.0    | 23.9    | 23.2    | °C/Watt |

|                 | XC2S50  | 6.7                                  | N/A                                      | 25.2                 | 18.6    | 16.4    | 15.2    | °C/Watt |

| PQ208           | XC2S100 | 5.9                                  | N/A                                      | 24.6                 | 18.1    | 16.0    | 14.9    | °C/Watt |

| PQG208          | XC2S150 | 5.0                                  | N/A                                      | 23.8                 | 17.6    | 15.6    | 14.4    | °C/Watt |

|                 | XC2S200 | 4.1                                  | N/A                                      | 23.0                 | 17.0    | 15.0    | 13.9    | °C/Watt |

|                 | XC2S50  | 7.1                                  | 17.6                                     | 27.2                 | 21.4    | 20.3    | 19.8    | °C/Watt |

| FG256           | XC2S100 | 5.8                                  | 15.1                                     | 25.1                 | 19.5    | 18.3    | 17.8    | °C/Watt |

| FGG256          | XC2S150 | 4.6                                  | 12.7                                     | 23.0                 | 17.6    | 16.3    | 15.8    | °C/Watt |

|                 | XC2S200 | 3.5                                  | 10.7                                     | 21.4                 | 16.1    | 14.7    | 14.2    | °C/Watt |

| FG456           | XC2S150 | 2.0                                  | N/A                                      | 21.9                 | 17.3    | 15.8    | 15.2    | °C/Watt |

| FGG456          | XC2S200 | 2.0                                  | N/A                                      | 21.0                 | 16.6    | 15.1    | 14.5    | °C/Watt |

## **XC2S30 Device Pinouts**

| XC2S30 Pad               | Name |       |       |       |       |               |

|--------------------------|------|-------|-------|-------|-------|---------------|

| Function                 | Bank | VQ100 | TQ144 | CS144 | PQ208 | Bndry<br>Scan |

| GND                      | -    | P1    | P143  | A1    | P1    | -             |

| TMS                      | -    | P2    | P142  | B1    | P2    | -             |

| I/O                      | 7    | P3    | P141  | C2    | P3    | 113           |

| I/O                      | 7    | -     | P140  | C1    | P4    | 116           |

| I/O                      | 7    | -     | -     | -     | P5    | 119           |

| I/O, V <sub>REF</sub>    | 7    | P4    | P139  | D4    | P6    | 122           |

| I/O                      | 7    | -     | P138  | D3    | P8    | 125           |

| I/O                      | 7    | P5    | P137  | D2    | P9    | 128           |

| I/O                      | 7    | P6    | P136  | D1    | P10   | 131           |

| GND                      | -    | -     | P135  | E4    | P11   | -             |

| V <sub>CCO</sub>         | 7    | -     | -     | -     | P12   | -             |

| I/O                      | 7    | P7    | P134  | E3    | P14   | 134           |

| I/O                      | 7    | -     | P133  | E2    | P15   | 137           |

| I/O                      | 7    | -     | -     | -     | P16   | 140           |

| I/O                      | 7    | -     | -     | -     | P17   | 143           |

| I/O                      | 7    | -     | -     | -     | P18   | 146           |

| GND                      | -    | -     | -     | -     | P19   | -             |

| I/O, V <sub>REF</sub>    | 7    | P8    | P132  | E1    | P20   | 149           |

| I/O                      | 7    | P9    | P131  | F4    | P21   | 152           |

| I/O                      | 7    | -     | P130  | F3    | P22   | 155           |

| I/O                      | 7    | -     | -     | -     | P23   | 158           |

| I/O, IRDY <sup>(1)</sup> | 7    | P10   | P129  | F2    | P24   | 161           |

| GND                      | -    | P11   | P128  | F1    | P25   | -             |

| V <sub>CCO</sub>         | 7    | P12   | P127  | G2    | P26   | -             |

| V <sub>CCO</sub>         | 6    | P12   | P127  | G2    | P26   | -             |

| I/O, TRDY <sup>(1)</sup> | 6    | P13   | P126  | G1    | P27   | 164           |

| V <sub>CCINT</sub>       | -    | P14   | P125  | G3    | P28   | -             |

| I/O                      | 6    | -     | P124  | G4    | P29   | 170           |

| I/O                      | 6    | P15   | P123  | H1    | P30   | 173           |

| I/O, V <sub>REF</sub>    | 6    | P16   | P122  | H2    | P31   | 176           |

| GND                      | -    | -     | -     | -     | P32   | -             |

| I/O                      | 6    | -     | -     | -     | P33   | 179           |

| I/O                      | 6    | -     | -     | -     | P34   | 182           |

| I/O                      | 6    | -     | -     | -     | P35   | 185           |

| I/O                      | 6    | -     | P121  | НЗ    | P36   | 188           |

| I/O                      | 6    | P17   | P120  | H4    | P37   | 191           |

| V <sub>CCO</sub>         | 6    | -     | -     | -     | P39   | -             |

| GND                      | -    | -     | P119  | J1    | P40   | -             |

| I/O                      | 6    | P18   | P118  | J2    | P41   | 194           |

| I/O                      | 6    | P19   | P117  | J3    | P42   | 197           |

| I/O                      | 6    | -     | P116  | J4    | P43   | 200           |

## XC2S30 Device Pinouts (Continued)

| XC2S30 Pad            | Name |       |       |       |       | Bndry |

|-----------------------|------|-------|-------|-------|-------|-------|

| Function              | Bank | VQ100 | TQ144 | CS144 | PQ208 | Scan  |

| I/O, V <sub>REF</sub> | 6    | P20   | P115  | K1    | P45   | 203   |

| I/O                   | 6    | -     | -     | -     | P46   | 206   |

| I/O                   | 6    | -     | P114  | K2    | P47   | 209   |

| I/O                   | 6    | P21   | P113  | K3    | P48   | 212   |

| I/O                   | 6    | P22   | P112  | L1    | P49   | 215   |

| M1                    | -    | P23   | P111  | L2    | P50   | 218   |

| GND                   | -    | P24   | P110  | L3    | P51   | -     |

| M0                    | -    | P25   | P109  | M1    | P52   | 219   |

| $V_{CCO}$             | 6    | P26   | P108  | M2    | P53   | -     |

| V <sub>CCO</sub>      | 5    | P26   | P107  | N1    | P53   | -     |

| M2                    | -    | P27   | P106  | N2    | P54   | 220   |

| I/O                   | 5    | -     | P103  | K4    | P57   | 227   |

| I/O                   | 5    | -     | -     | -     | P58   | 230   |

| I/O, V <sub>REF</sub> | 5    | P30   | P102  | L4    | P59   | 233   |

| I/O                   | 5    | -     | P101  | M4    | P61   | 236   |

| I/O                   | 5    | P31   | P100  | N4    | P62   | 239   |

| I/O                   | 5    | P32   | P99   | K5    | P63   | 242   |

| GND                   | -    | -     | P98   | L5    | P64   | -     |

| V <sub>CCO</sub>      | 5    | -     | -     | -     | P65   | -     |

| V <sub>CCINT</sub>    | -    | P33   | P97   | M5    | P66   | -     |

| I/O                   | 5    | -     | P96   | N5    | P67   | 245   |

| I/O                   | 5    | -     | P95   | K6    | P68   | 248   |

| I/O                   | 5    | -     | -     | -     | P69   | 251   |

| I/O                   | 5    | -     | -     | -     | P70   | 254   |

| I/O                   | 5    | -     | -     | -     | P71   | 257   |

| GND                   | -    | -     | -     | -     | P72   | -     |

| I/O, V <sub>REF</sub> | 5    | P34   | P94   | L6    | P73   | 260   |

| I/O                   | 5    | -     | -     | -     | P74   | 263   |

| I/O                   | 5    | -     | P93   | M6    | P75   | 266   |

| V <sub>CCINT</sub>    | -    | P35   | P92   | N6    | P76   | -     |

| I, GCK1               | 5    | P36   | P91   | M7    | P77   | 275   |

| V <sub>CCO</sub>      | 5    | P37   | P90   | N7    | P78   | -     |

| V <sub>CCO</sub>      | 4    | P37   | P90   | N7    | P78   | -     |

| GND                   | -    | P38   | P89   | L7    | P79   | -     |

| I, GCK0               | 4    | P39   | P88   | K7    | P80   | 276   |

| I/O                   | 4    | P40   | P87   | N8    | P81   | 280   |

| I/O                   | 4    | -     | P86   | M8    | P82   | 283   |

| I/O                   | 4    | -     | -     | -     | P83   | 286   |

| I/O, V <sub>REF</sub> | 4    | P41   | P85   | L8    | P84   | 289   |

| GND                   | -    | -     | -     | -     | P85   | -     |

| I/O                   | 4    | -     | -     | -     | P86   | 292   |

|                       |      |       |       |       |       |       |

## Additional XC2S50 Package Pins (Continued)

#### PQ208

| Not Connected Pins |     |   |   |   |   |  |  |  |

|--------------------|-----|---|---|---|---|--|--|--|

| P55                | P56 | - | - | - | - |  |  |  |

| 11/02/00           |     |   |   |   |   |  |  |  |

#### FG256

| F G 2 3 0                    |                              |                     |                   |    |     |  |  |  |  |  |

|------------------------------|------------------------------|---------------------|-------------------|----|-----|--|--|--|--|--|

|                              |                              | V <sub>CCIN</sub>   | <sub>T</sub> Pins |    |     |  |  |  |  |  |

| C3                           | C14                          | D4                  | D13               | E5 | E12 |  |  |  |  |  |

| M5                           | M12                          | N4                  | N13               | P3 | P14 |  |  |  |  |  |

| V <sub>CCO</sub> Bank 0 Pins |                              |                     |                   |    |     |  |  |  |  |  |

| E8                           | F8                           | -                   | -                 | -  | -   |  |  |  |  |  |

|                              | V <sub>CCO</sub> Bank 1 Pins |                     |                   |    |     |  |  |  |  |  |

| E9                           | F9                           | -                   | -                 | -  | -   |  |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 2 Pins         |    |     |  |  |  |  |  |

| H11                          | H12                          | -                   | -                 | -  | -   |  |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 3 Pins         |    |     |  |  |  |  |  |

| J11                          | J12                          | -                   | -                 | -  | -   |  |  |  |  |  |

| V <sub>CCO</sub> Bank 4 Pins |                              |                     |                   |    |     |  |  |  |  |  |

| L9                           | M9                           | -                   | -                 | -  | -   |  |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 5 Pins         |    |     |  |  |  |  |  |

| L8                           | M8                           | -                   | -                 | -  | -   |  |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 6 Pins         |    |     |  |  |  |  |  |

| J5                           | J6                           | -                   | -                 | -  | -   |  |  |  |  |  |

|                              |                              | V <sub>CCO</sub> Ba | nk 7 Pins         |    |     |  |  |  |  |  |

| H5                           | H6                           | -                   | -                 | -  | -   |  |  |  |  |  |

|                              |                              | GND                 | Pins              |    |     |  |  |  |  |  |

| A1                           | A16                          | B2                  | B15               | F6 | F7  |  |  |  |  |  |

| F10                          | F11                          | G6                  | G7                | G8 | G9  |  |  |  |  |  |

| G10                          | G11                          | H7                  | H8                | H9 | H10 |  |  |  |  |  |

| J7                           | J8                           | J9                  | J10               | K6 | K7  |  |  |  |  |  |

| K8                           | K9                           | K10                 | K11               | L6 | L7  |  |  |  |  |  |

| L10                          | L11                          | R2                  | R15               | T1 | T16 |  |  |  |  |  |

|                              | l .                          | Not Conn            | ected Pins        | ı  | ı   |  |  |  |  |  |

| P4                           | R4                           | -                   | -                 | -  | -   |  |  |  |  |  |