# E·XFL

#### AMD Xilinx - XC2S50-6TQ144C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| De | ta | i | ls |

|----|----|---|----|

|    |    |   |    |

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 384                                                        |

| Number of Logic Elements/Cells | 1728                                                       |

| Total RAM Bits                 | 32768                                                      |

| Number of I/O                  | 92                                                         |

| Number of Gates                | 50000                                                      |

| Voltage - Supply               | 2.375V ~ 2.625V                                            |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 144-LQFP                                                   |

| Supplier Device Package        | 144-TQFP (20x20)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s50-6tq144c |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#

DS001-2 (v2.8) June 13, 2008

# **Architectural Description**

#### Spartan-II FPGA Array

The Spartan<sup>®</sup>-II field-programmable gate array, shown in Figure 2, is composed of five major configurable elements:

- IOBs provide the interface between the package pins and the internal logic

- CLBs provide the functional elements for constructing most logic

- Dedicated block RAM memories of 4096 bits each

- Clock DLLs for clock-distribution delay compensation and clock domain control

- Versatile multi-level interconnect structure

As can be seen in Figure 2, the CLBs form the central logic structure with easy access to all support and routing structures. The IOBs are located around all the logic and

# Spartan-II FPGA Family: Functional Description

#### **Product Specification**

memory elements for easy and quick routing of signals on and off the chip.

Values stored in static memory cells control all the configurable logic elements and interconnect resources. These values load into the memory cells on power-up, and can reload if necessary to change the function of the device.

Each of these elements will be discussed in detail in the following sections.

#### **Input/Output Block**

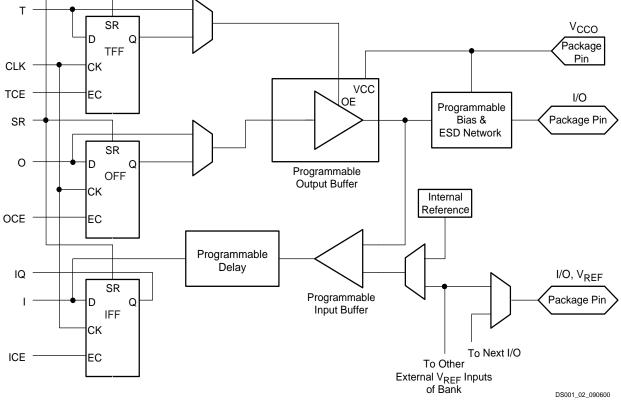

The Spartan-II FPGA IOB, as seen in Figure 2, features inputs and outputs that support a wide variety of I/O signaling standards. These high-speed inputs and outputs are capable of supporting various state of the art memory and bus interfaces. Table 3 lists several of the standards which are supported along with the required reference, output and termination voltages needed to meet the standard.

Figure 2: Spartan-II FPGA Input/Output Block (IOB)

© 2000-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

drivers are disabled. Maintaining a valid logic level in this way helps eliminate bus chatter.

Because the weak-keeper circuit uses the IOB input buffer to monitor the input level, an appropriate  $V_{REF}$  voltage must be provided if the signaling standard requires one. The provision of this voltage must comply with the I/O banking rules.

#### I/O Banking

Some of the I/O standards described above require  $V_{CCO}$  and/or  $V_{REF}$  voltages. These voltages are externally connected to device pins that serve groups of IOBs, called banks. Consequently, restrictions exist about which I/O standards can be combined within a given bank.

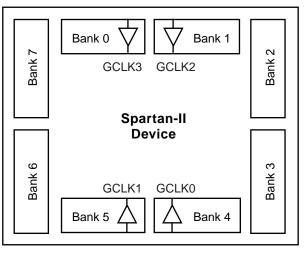

Eight I/O banks result from separating each edge of the FPGA into two banks (see Figure 3). Each bank has multiple  $V_{CCO}$  pins which must be connected to the same voltage. Voltage is determined by the output standards in use.

DS001\_03\_060100

Figure 3: Spartan-II I/O Banks

Within a bank, output standards may be mixed only if they use the same  $V_{CCO}$ . Compatible standards are shown in Table 4. GTL and GTL+ appear under all voltages because their open-drain outputs do not depend on  $V_{CCO}$ .

#### Table 4: Compatible Output Standards

| V <sub>cco</sub> | Compatible Standards                                  |

|------------------|-------------------------------------------------------|

| 3.3V             | PCI, LVTTL, SSTL3 I, SSTL3 II, CTT, AGP,<br>GTL, GTL+ |

| 2.5V             | SSTL2 I, SSTL2 II, LVCMOS2, GTL, GTL+                 |

| 1.5V             | HSTL I, HSTL III, HSTL IV, GTL, GTL+                  |

Some input standards require a user-supplied threshold voltage,  $V_{\text{REF}}$  In this case, certain user-I/O pins are

automatically configured as inputs for the V<sub>REF</sub> voltage. About one in six of the I/O pins in the bank assume this role.

$V_{\text{REF}}$  pins within a bank are interconnected internally and consequently only one  $V_{\text{REF}}$  voltage can be used within each bank. All  $V_{\text{REF}}$  pins in the bank, however, must be connected to the external voltage source for correct operation.

In a bank, inputs requiring V<sub>REF</sub> can be mixed with those that do not but only one V<sub>REF</sub> voltage may be used within a bank. Input buffers that use V<sub>REF</sub> are not 5V tolerant. LVTTL, LVCMOS2, and PCI are 5V tolerant. The V<sub>CCO</sub> and V<sub>REF</sub> pins for each bank appear in the device pinout tables.

Within a given package, the number of  $V_{REF}$  and  $V_{CCO}$  pins can vary depending on the size of device. In larger devices, more I/O pins convert to  $V_{REF}$  pins. Since these are always a superset of the  $V_{REF}$  pins used for smaller devices, it is possible to design a PCB that permits migration to a larger device. All  $V_{REF}$  pins for the largest device anticipated must be connected to the  $V_{REF}$  voltage, and not used for I/O.

Independent Banks Available

| Package           | VQ100 | CS144 | FG256 |

|-------------------|-------|-------|-------|

|                   | PQ208 | TQ144 | FG456 |

| Independent Banks | 1     | 4     | 8     |

#### **Configurable Logic Block**

The basic building block of the Spartan-II FPGA CLB is the logic cell (LC). An LC includes a 4-input function generator, carry logic, and storage element. Output from the function generator in each LC drives the CLB output and the D input of the flip-flop. Each Spartan-II FPGA CLB contains four LCs, organized in two similar slices; a single slice is shown in Figure 4.

In addition to the four basic LCs, the Spartan-II FPGA CLB contains logic that combines function generators to provide functions of five or six inputs.

#### Look-Up Tables

Spartan-II FPGA function generators are implemented as 4-input look-up tables (LUTs). In addition to operating as a function generator, each LUT can provide a 16 x 1-bit synchronous RAM. Furthermore, the two LUTs within a slice can be combined to create a 16 x 2-bit or 32 x 1-bit synchronous RAM, or a 16 x 1-bit dual-port synchronous RAM.

The Spartan-II FPGA LUT can also provide a 16-bit shift register that is ideal for capturing high-speed or burst-mode data. This mode can also be used to store data in applications such as Digital Signal Processing.

# **∑**XILINX<sup>®</sup>

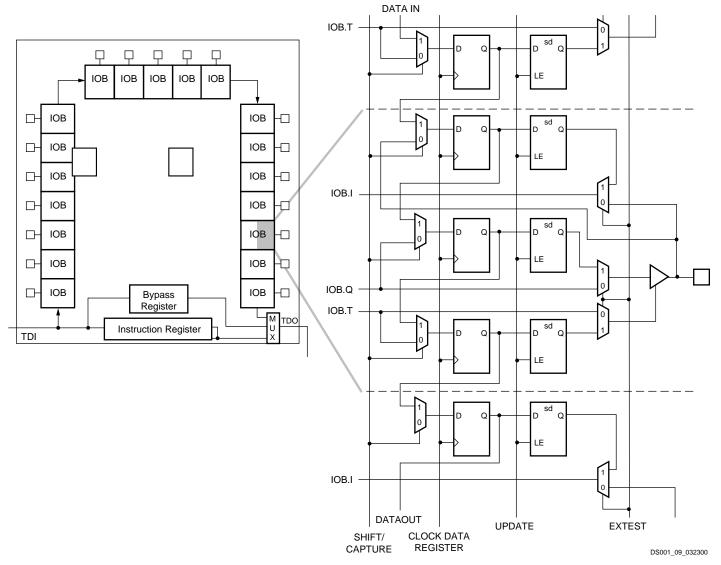

Figure 9 is a diagram of the Spartan-II family boundary scan logic. It includes three bits of Data Register per IOB, the IEEE 1149.1 Test Access Port controller, and the Instruction Register with decodes.

#### **Bit Sequence**

The bit sequence within each IOB is: In, Out, 3-State. The input-only pins contribute only the In bit to the boundary scan I/O data register, while the output-only pins contributes all three bits.

From a cavity-up view of the chip (as shown in the FPGA Editor), starting in the upper right chip corner, the boundary scan data-register bits are ordered as shown in Figure 10.

BSDL (Boundary Scan Description Language) files for Spartan-II family devices are available on the Xilinx website, in the <u>Downloads</u> area.

# Configuration

Configuration is the process by which the bitstream of a design, as generated by the Xilinx software, is loaded into the internal configuration memory of the FPGA. Spartan-II devices support both serial configuration, using the master/slave serial and JTAG modes, as well as byte-wide configuration employing the Slave Parallel mode.

#### **Configuration File**

Spartan-II devices are configured by sequentially loading frames of data that have been concatenated into a configuration file. Table 8 shows how much nonvolatile storage space is needed for Spartan-II devices.

It is important to note that, while a PROM is commonly used to store configuration data before loading them into the FPGA, it is by no means required. Any of a number of different kinds of under populated nonvolatile storage already available either on or off the board (i.e., hard drives, FLASH cards, etc.) can be used. For more information on configuration without a PROM, refer to <u>XAPP098</u>, *The Low-Cost, Efficient Serial Configuration of Spartan FPGAs*.

| Device  | Configuration File Size (Bits) |

|---------|--------------------------------|

| XC2S15  | 197,696                        |

| XC2S30  | 336,768                        |

| XC2S50  | 559,200                        |

| XC2S100 | 781,216                        |

| XC2S150 | 1,040,096                      |

| XC2S200 | 1,335,840                      |

#### Table 8: Spartan-II Configuration File Size

#### Modes

Spartan-II devices support the following four configuration modes:

- Slave Serial mode

- Master Serial mode

- Slave Parallel mode

- Boundary-scan mode

The Configuration mode pins (M2, M1, M0) select among these configuration modes with the option in each case of having the IOB pins either pulled up or left floating prior to the end of configuration. The selection codes are listed in Table 9.

Configuration through the boundary-scan port is always available, independent of the mode selection. Selecting the boundary-scan mode simply turns off the other modes. The three mode pins have internal pull-up resistors, and default to a logic High if left unconnected.

| Configuration Mode  | Preconfiguration<br>Pull-ups | МО | M1 | M2 | CCLK<br>Direction | Data Width | Serial D <sub>OUT</sub> |

|---------------------|------------------------------|----|----|----|-------------------|------------|-------------------------|

| Master Serial mode  | No                           | 0  | 0  | 0  | Out               | 1          | Yes                     |

|                     | Yes                          | 0  | 0  | 1  |                   |            |                         |

| Slave Parallel mode | Yes                          | 0  | 1  | 0  | In                | 8          | No                      |

|                     | No                           | 0  | 1  | 1  |                   |            |                         |

| Boundary-Scan mode  | Yes                          | 1  | 0  | 0  | N/A 1             | No         |                         |

|                     | No                           | 1  | 0  | 1  |                   |            |                         |

| Slave Serial mode   | Yes                          | 1  | 1  | 0  | In                | 1          | Yes                     |

|                     | No                           | 1  | 1  | 1  |                   |            |                         |

#### Table 9: Configuration Modes

#### Notes:

During power-on and throughout configuration, the I/O drivers will be in a high-impedance state. After configuration, all unused I/Os (those not assigned signals) will remain in a high-impedance state. Pins used as outputs may pulse High at the end of configuration (see <u>Answer 10504</u>).

2. If the Mode pins are set for preconfiguration pull-ups, those resistors go into effect once the rising edge of INIT samples the Mode pins. They will stay in effect until GTS is released during startup, after which the UnusedPin bitstream generator option will determine whether the unused I/Os have a pull-up, pull-down, or no resistor.

#### Master Serial Mode

In Master Serial mode, the CCLK output of the FPGA drives a Xilinx PROM which feeds a serial stream of configuration data to the FPGA's DIN input. Figure 15 shows a Master Serial FPGA configuring a Slave Serial FPGA from a PROM. A Spartan-II device in Master Serial mode should be connected as shown for the device on the left side. Master Serial mode is selected by a <00x> on the mode pins (M0, M1, M2). The PROM RESET pin is driven by INIT, and CE input is driven by DONE. The interface is identical to the slave serial mode except that an oscillator internal to the FPGA is used to generate the configuration clock (CCLK). Any of a number of different frequencies ranging from 4 to 60 MHz can be set using the ConfigRate option in the Xilinx software. On power-up, while the first 60 bytes of the configuration data are being loaded, the CCLK frequency is always 2.5 MHz. This frequency is used until the ConfigRate bits, part of the configuration file, have been loaded into the FPGA, at which point, the frequency changes to the selected ConfigRate. Unless a different frequency is specified in the design, the default ConfigRate is 4 MHz. The frequency of the CCLK signal created by the internal oscillator has a variance of +45%, -30% from the specified value.

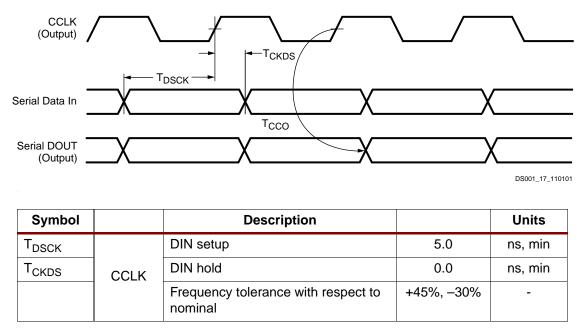

Figure 17 shows the timing for Master Serial configuration. The FPGA accepts one bit of configuration data on each rising CCLK edge. After the FPGA has been loaded, the data for the next device in a daisy-chain is presented on the DOUT pin after the rising CCLK edge.

Figure 17: Master Serial Mode Timing

#### **Slave Parallel Mode**

The Slave Parallel mode is the fastest configuration option. Byte-wide data is written into the FPGA. A BUSY flag is provided for controlling the flow of data at a clock frequency  $F_{CCNH}$  above 50 MHz.

Figure 18, page 24 shows the connections for two Spartan-II devices using the Slave Parallel mode. Slave Parallel mode is selected by a <011> on the mode pins (M0, M1, M2).

If a configuration file of the format .bit, .rbt, or non-swapped HEX is used for parallel programming, then the most significant bit (i.e. the left-most bit of each configuration byte, as displayed in a text editor) must be routed to the D0 input on the FPGA. The agent controlling configuration is not shown. Typically, a processor, a microcontroller, or CPLD controls the Slave Parallel interface. The controlling agent provides byte-wide configuration data, CCLK, a Chip Select ( $\overline{CS}$ ) signal and a Write signal (WRITE). If BUSY is asserted (High) by the FPGA, the data must be held until BUSY goes Low.

After configuration, the pins of the Slave Parallel port (D0-D7) can be used as additional user I/O. Alternatively, the port may be retained to permit high-speed 8-bit readback. Then data can be read by de-asserting WRITE. See "Readback," page 25.

www.xilinx.com

## **Design Considerations**

This section contains more detailed design information on the following features:

- Delay-Locked Loop . . . see page 27

- Block RAM . . . see page 32

- Versatile I/O . . . see page 36

## Using Delay-Locked Loops

The Spartan-II FPGA family provides up to four fully digital dedicated on-chip Delay-Locked Loop (DLL) circuits which provide zero propagation delay, low clock skew between output clock signals distributed throughout the device, and advanced clock domain control. These dedicated DLLs can be used to implement several circuits that improve and simplify system level design.

#### Introduction

Quality on-chip clock distribution is important. Clock skew and clock delay impact device performance and the task of managing clock skew and clock delay with conventional clock trees becomes more difficult in large devices. The Spartan-II family of devices resolve this potential problem by providing up to four fully digital dedicated on-chip Delay-Locked Loop (DLL) circuits which provide zero propagation delay and low clock skew between output clock signals distributed throughout the device.

Each DLL can drive up to two global clock routing networks within the device. The global clock distribution network minimizes clock skews due to loading differences. By monitoring a sample of the DLL output clock, the DLL can compensate for the delay on the routing network, effectively eliminating the delay from the external input port to the individual clock loads within the device.

In addition to providing zero delay with respect to a user source clock, the DLL can provide multiple phases of the source clock. The DLL can also act as a clock doubler or it can divide the user source clock by up to 16.

Clock multiplication gives the designer a number of design alternatives. For instance, a 50 MHz source clock doubled by the DLL can drive an FPGA design operating at 100 MHz. This technique can simplify board design because the clock path on the board no longer distributes such a high-speed signal. A multiplied clock also provides designers the option of time-domain-multiplexing, using one circuit twice per clock cycle, consuming less area than two copies of the same circuit.

The DLL can also act as a clock mirror. By driving the DLL output off-chip and then back in again, the DLL can be used to de-skew a board level clock between multiple devices.

In order to guarantee the system clock establishes prior to the device "waking up," the DLL can delay the completion of the device configuration process until after the DLL achieves lock.

By taking advantage of the DLL to remove on-chip clock delay, the designer can greatly simplify and improve system level design involving high-fanout, high-performance clocks.

#### **Library DLL Primitives**

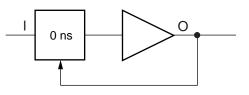

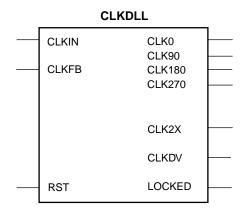

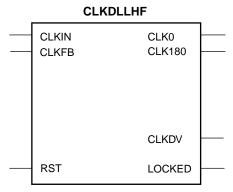

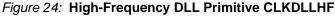

Figure 22 shows the simplified Xilinx library DLL macro, BUFGDLL. This macro delivers a quick and efficient way to provide a system clock with zero propagation delay throughout the device. Figure 23 and Figure 24 show the two library DLL primitives. These primitives provide access to the complete set of DLL features when implementing more complex applications.

Figure 22: Simplified DLL Macro BUFGDLL

DS001\_23\_032300

DS001\_24\_032300

division factor N except for non-integer division in High Frequency (HF) mode. For division factor 1.5 the duty cycle in the HF mode is 33.3% High and 66.7% Low. For division factor 2.5, the duty cycle in the HF mode is 40.0% High and 60.0% Low.

#### 1x Clock Outputs — CLK[0/90/180/270]

The 1x clock output pin CLK0 represents a delay-compensated version of the source clock (CLKIN) signal. The CLKDLL primitive provides three phase-shifted versions of the CLK0 signal while CLKDLLHF provides only the 180 degree phase-shifted version. The relationship between phase shift and the corresponding period shift appears in Table 10.

The timing diagrams in Figure 26 illustrate the DLL clock output characteristics.

# Table 10: Relationship of Phase-Shifted Output Clock to Period Shift

| Phase (degrees) | Period Shift (percent) |

|-----------------|------------------------|

| 0               | 0%                     |

| 90              | 25%                    |

| 180             | 50%                    |

| 270             | 75%                    |

The DLL provides duty cycle correction on all 1x clock outputs such that all 1x clock outputs by default have a 50/50 duty cycle. The DUTY\_CYCLE\_CORRECTION property (TRUE by default), controls this feature. In order to deactivate the DLL duty cycle correction, attach the DUTY\_CYCLE\_CORRECTION=FALSE property to the DLL primitive. When duty cycle correction deactivates, the output clock has the same duty cycle as the source clock.

The DLL clock outputs can drive an OBUF, a BUFG, or they can route directly to destination clock pins. The DLL clock outputs can only drive the BUFGs that reside on the same edge (top or bottom).

#### Locked Output — LOCKED

In order to achieve lock, the DLL may need to sample several thousand clock cycles. After the DLL achieves lock the LOCKED signal activates. The "DLL Timing Parameters" section of Module 3 provides estimates for locking times.

In order to guarantee that the system clock is established prior to the device "waking up," the DLL can delay the completion of the device configuration process until after the DLL locks. The STARTUP\_WAIT property activates this feature.

Until the LOCKED signal activates, the DLL output clocks are not valid and can exhibit glitches, spikes, or other

spurious movement. In particular the CLK2X output will appear as a 1x clock with a 25/75 duty cycle.

#### **DLL Properties**

Properties provide access to some of the Spartan-II family DLL features, (for example, clock division and duty cycle correction).

#### **Duty Cycle Correction Property**

The 1x clock outputs, CLK0, CLK90, CLK180, and CLK270, use the duty-cycle corrected default, such that they exhibit a 50/50 duty cycle. The DUTY\_CYCLE\_CORRECTION property (by default TRUE) controls this feature. To deactivate the DLL duty-cycle correction for the 1x clock outputs, attach the DUTY\_CYCLE\_CORRECTION=FALSE property to the DLL primitive.

Figure 26: DLL Output Characteristics

#### Clock Divide Property

The CLKDV\_DIVIDE property specifies how the signal on the CLKDV pin is frequency divided with respect to the CLK0 pin. The values allowed for this property are 1.5, 2, 2.5, 3, 4, 5, 8, or 16; the default value is 2.

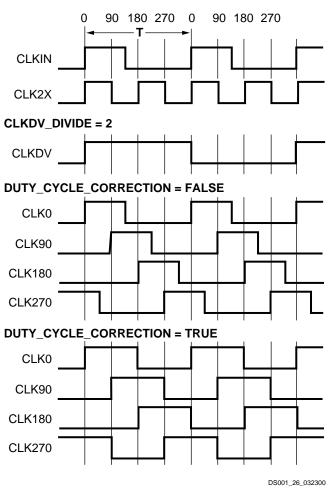

Figure 33: Timing Diagram for Single-Port Block RAM Memory

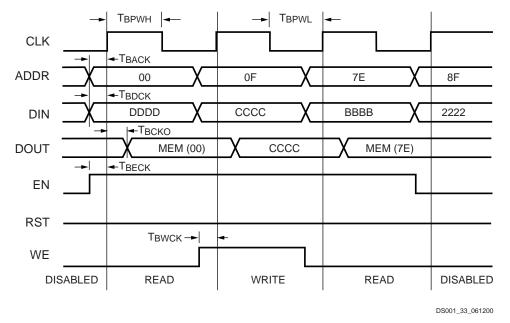

Figure 34: Timing Diagram for a True Dual-Port Read/Write Block RAM Memory

At the third rising edge of CLKA, the  $T_{BCCS}$  parameter is violated with two writes to memory location 0x0F. The DOA and DOB busses reflect the contents of the DIA and DIB busses, but the stored value at 0x7E is invalid.

At the fourth rising edge of CLKA, a read operation is performed at memory location 0x0F and invalid data is present on the DOA bus. Port B also executes a read operation to memory location 0x0F and also reads invalid data.

At the fifth rising edge of CLKA a read operation is performed that does not violate the  $T_{BCCS}$  parameter to the previous write of 0x7E by Port B. THe DOA bus reflects the recently written value by Port B.

#### Initialization

The block RAM memory can initialize during the device configuration sequence. The 16 initialization properties of 64 hex values each (a total of 4096 bits) set the initialization of each RAM. These properties appear in Table 14. Any initialization properties not explicitly set configure as zeros. Partial initialization strings pad with zeros. Initialization strings greater than 64 hex values generate an error. The RAMs can be simulated with the initialization values using generics in VHDL simulators and parameters in Verilog simulators.

#### **Initialization in VHDL**

The block RAM structures may be initialized in VHDL for both simulation and synthesis for inclusion in the EDIF output file. The simulation of the VHDL code uses a generic to pass the initialization.

#### **Initialization in Verilog**

The block RAM structures may be initialized in Verilog for both simulation and synthesis for inclusion in the EDIF output file. The simulation of the Verilog code uses a defparam to pass the initialization.

#### **Block Memory Generation**

The CORE Generator<sup>™</sup> software generates memory structures using the block RAM features. This program outputs VHDL or Verilog simulation code templates and an EDIF file for inclusion in a design.

| Property | Memory Cells |

|----------|--------------|

| INIT_00  | 255 to 0     |

| INIT_01  | 511 to 256   |

| INIT_02  | 767 to 512   |

| INIT_03  | 1023 to 768  |

| INIT_04  | 1279 to 1024 |

|          |              |

| Property | Memory Cells |

|----------|--------------|

| INIT_05  | 1535 to 1280 |

| INIT_06  | 1791 to 1536 |

| INIT_07  | 2047 to 1792 |

| INIT_08  | 2303 to 2048 |

| INIT_09  | 2559 to 2304 |

| INIT_0a  | 2815 to 2560 |

| INIT_0b  | 3071 to 2816 |

| INIT_0c  | 3327 to 3072 |

| INIT_0d  | 3583 to 3328 |

| INIT_0e  | 3839 to 3584 |

| INIT_0f  | 4095 to 3840 |

For design examples and more information on using the Block RAM, see <u>XAPP173</u>, Using Block SelectRAM+ Memory in Spartan-II FPGAs.

# **Using Versatile I/O**

The Spartan-II FPGA family includes a highly configurable, high-performance I/O resource called Versatile I/O to provide support for a wide variety of I/O standards. The Versatile I/O resource is a robust set of features including programmable control of output drive strength, slew rate, and input delay and hold time. Taking advantage of the flexibility and Versatile I/O features and the design considerations described in this document can improve and simplify system level design.

#### Introduction

As FPGAs continue to grow in size and capacity, the larger and more complex systems designed for them demand an increased variety of I/O standards. Furthermore, as system clock speeds continue to increase, the need for high-performance I/O becomes more important. While chip-to-chip delays have an increasingly substantial impact on overall system speed, the task of achieving the desired system performance becomes more difficult with the proliferation of low-voltage I/O standards. Versatile I/O, the revolutionary input/output resources of Spartan-II devices, has resolved this potential problem by providing a highly configurable, high-performance alternative to the I/O resources of more conventional programmable devices. The Spartan-II FPGA Versatile I/O features combine the flexibility and time-to-market advantages of programmable logic with the high performance previously available only with ASICs and custom ICs.

Each Versatile I/O block can support up to 16 I/O standards. Supporting such a variety of I/O standards allows the

LVTTL output buffers have selectable drive strengths.

The format for LVTTL OBUF primitive names is as follows.

OBUF <slew rate> <drive strength>

<slew\_rate> is either F (Fast), or S (Slow) and <drive\_strength> is specified in milliamps (2, 4, 6, 8, 12, 16, or 24). The default is slew rate limited with 12 mA drive.

OBUF placement restrictions require that within a given  $V_{CCO}$  bank each OBUF share the same output source drive voltage. Input buffers of any type and output buffers that do not require  $V_{CCO}$  can be placed within any  $V_{CCO}$  bank. Table 17 summarizes the output compatibility requirements. The LOC property can specify a location for the OBUF.

# Table 17: Output Standards Compatibility Requirements

| Rule 1           | Only outputs with standards which share compatible $\rm V_{\rm CCO}$ may be used within the same bank.  |

|------------------|---------------------------------------------------------------------------------------------------------|

| Rule 2           | There are no placement restrictions for outputs with standards that do not require a $\rm V_{\rm CCO}.$ |

| V <sub>CCO</sub> | Compatible Standards                                                                                    |

| 3.3              | LVTTL, SSTL3_I, SSTL3_II, CTT, AGP, GTL, GTL+, PCI33_3, PCI66_3                                         |

| 2.5              | SSTL2_I, SSTL2_II, LVCMOS2, GTL, GTL+                                                                   |

| 1.5              | HSTL_I, HSTL_III, HSTL_IV, GTL, GTL+                                                                    |

#### OBUFT

The generic 3-state output buffer OBUFT, shown in Figure 39, typically implements 3-state outputs or bidirectional I/O.

With no extension or property specified for the generic OBUFT primitive, the assumed standard is slew rate limited LVTTL with 12 mA drive strength.

The LVTTL OBUFT can support one of two slew rate modes to minimize bus transients. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals.

LVTTL 3-state output buffers have selectable drive strengths.

The format for LVTTL OBUFT primitive names is as follows.

OBUFT\_<slew\_rate>\_<drive\_strength>

<slew\_rate> can be either F (Fast), or S (Slow) and <drive\_strength> is specified in milliamps (2, 4, 6, 8, 12, 16, or 24).

DS001\_39\_032300

Figure 39: 3-State Output Buffer Primitive (OBUFT

The Versatile I/O OBUFT placement restrictions require that within a given V<sub>CCO</sub> bank each OBUFT share the same output source drive voltage. Input buffers of any type and output buffers that do not require V<sub>CCO</sub> can be placed within the same V<sub>CCO</sub> bank.

The LOC property can specify a location for the OBUFT.

3-state output buffers and bidirectional buffers can have either a weak pull-up resistor, a weak pull-down resistor, or a weak "keeper" circuit. Control this feature by adding the appropriate primitive to the output net of the OBUFT (PULLUP, PULLDOWN, or KEEPER).

The weak "keeper" circuit requires the input buffer within the IOB to sample the I/O signal. So, OBUFTs programmed for an I/O standard that requires a  $V_{REF}$  have automatic placement of a  $V_{REF}$  in the bank with an OBUFT configured with a weak "keeper" circuit. This restriction does not affect most circuit design as applications using an OBUFT configured with a weak "keeper" typically implement a bidirectional I/O. In this case the IBUF (and the corresponding  $V_{REF}$ ) are explicitly placed.

The LOC property can specify a location for the OBUFT.

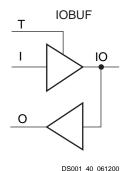

#### IOBUF

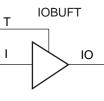

Use the IOBUF primitive for bidirectional signals that require both an input buffer and a 3-state output buffer with an active high 3-state pin. The generic input/output buffer IOBUF appears in Figure 40.

With no extension or property specified for the generic IOBUF primitive, the assumed standard is LVTTL input buffer and slew rate limited LVTTL with 12 mA drive strength for the output buffer.

The LVTTL IOBUF can support one of two slew rate modes to minimize bus transients. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals.

LVTTL bidirectional buffers have selectable output drive strengths.

The format for LVTTL IOBUF primitive names is as follows:

IOBUF\_<slew\_rate>\_<drive\_strength>

<slew\_rate> can be either F (Fast), or S (Slow) and <drive\_strength> is specified in milliamps (2, 4, 6, 8, 12, 16, or 24).

When the IOBUF primitive supports an I/O standard such as LVTTL, LVCMOS, or PCI33\_5, the IBUF automatically configures as a 5V tolerant input buffer unless the V<sub>CCO</sub> for the bank is less than 2V. If the single-ended IBUF is placed in a bank with an HSTL standard (V<sub>CCO</sub> < 2V), the input buffer is not 5V tolerant.

The voltage reference signal is "banked" within the Spartan-II device on a half-edge basis such that for all packages there are eight independent  $V_{REF}$  banks internally. See Figure 36, page 39 for a representation of the Spartan-II FPGA I/O banks. Within each bank approximately one of every six I/O pins is automatically configured as a  $V_{REF}$  input.

Additional restrictions on the Versatile I/O IOBUF placement require that within a given  $V_{CCO}$  bank each IOBUF must share the same output source drive voltage. Input buffers of any type and output buffers that do not require  $V_{CCO}$  can be placed within the same  $V_{CCO}$  bank. The LOC property can specify a location for the IOBUF.

An optional delay element is associated with the input path in each IOBUF. When the IOBUF drives an input flip-flop within the IOB, the delay element activates by default to ensure a zero hold-time requirement. Override this default with the NODELAY=TRUE property.

In the case when the IOBUF does not drive an input flip-flop within the IOB, the delay element de-activates by default to provide higher performance. To delay the input signal, activate the delay element with the DELAY=TRUE property.

3-state output buffers and bidirectional buffers can have either a weak pull-up resistor, a weak pull-down resistor, or a weak "keeper" circuit. Control this feature by adding the appropriate primitive to the output net of the IOBUF (PULLUP, PULLDOWN, or KEEPER).

#### **Versatile I/O Properties**

Access to some of the Versatile I/O features (for example, location constraints, input delay, output drive strength, and slew rate) is available through properties associated with these features.

#### Input Delay Properties

An optional delay element is associated with each IBUF. When the IBUF drives a flip-flop within the IOB, the delay element activates by default to ensure a zero hold-time requirement. Use the NODELAY=TRUE property to override this default.

In the case when the IBUF does not drive a flip-flop within the IOB, the delay element by default de-activates to provide higher performance. To delay the input signal, activate the delay element with the DELAY=TRUE property.

#### IOB Flip-Flop/Latch Property

The I/O Block (IOB) includes an optional register on the input path, an optional register on the output path, and an optional register on the 3-state control pin. The design implementation software automatically takes advantage of these registers when the following option for the Map program is specified:

#### map -pr b <filename>

Alternatively, the IOB = TRUE property can be placed on a register to force the mapper to place the register in an IOB.

#### **Location Constraints**

Specify the location of each Versatile I/O primitive with the location constraint LOC attached to the Versatile I/O primitive. The external port identifier indicates the value of the location constrain. The format of the port identifier depends on the package chosen for the specific design.

The LOC properties use the following form:

LOC=A42 LOC=P37

#### **Output Slew Rate Property**

In the case of the LVTTL output buffers (OBUF, OBUFT, and IOBUF), slew rate control can be programmed with the SLEW= property. By default, the slew rate for each output buffer is reduced to minimize power bus transients when switching non-critical signals. The SLEW= property has one of the two following values.

SLEW=SLOW

SLEW=FAST

#### **Output Drive Strength Property**

For the LVTTL output buffers (OBUF, OBUFT, and IOBUF, the desired drive strength can be specified with the DRIVE=

# Calculation of T<sub>IOOP</sub> as a Function of Capacitance

$T_{\rm IOOP}$  is the propagation delay from the O Input of the IOB to the pad. The values for  $T_{\rm IOOP}$  are based on the standard capacitive load (C<sub>SL</sub>) for each I/O standard as listed in the table "Constants for Calculating TIOOP", below.

For other capacitive loads, use the formulas below to calculate an adjusted propagation delay,  $T_{IOOP1}$ .

$$T_{IOOP1} = T_{IOOP} + Adj + (C_{LOAD} - C_{SL}) * F_{L}$$

Where:

Adj is selected from "IOB Output Delay Adjustments for Different Standards", page 59, according to the I/O standard used

$C_{\text{LOAD}}\,$  is the capacitive load for the design

F<sub>L</sub> is the capacitance scaling factor

#### **Delay Measurement Methodology**

| Standard       | V <sub>L</sub> (1)                            | V <sub>H</sub> (1)                            | Meas.<br>Point   | V <sub>REF</sub><br>Typ <sup>(2)</sup> |

|----------------|-----------------------------------------------|-----------------------------------------------|------------------|----------------------------------------|

| LVTTL          | 0                                             | 3                                             | 1.4              | -                                      |

| LVCMOS2        | 0                                             | 2.5                                           | 1.125            | -                                      |

| PCI33_5        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| PCI33_3        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| PCI66_3        | Pe                                            | r PCI Spec                                    |                  | -                                      |

| GTL            | V <sub>REF</sub> - 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 0.80                                   |

| GTL+           | V <sub>REF</sub> - 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 1.0                                    |

| HSTL Class I   | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.75                                   |

| HSTL Class III | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.90                                   |

| HSTL Class IV  | V <sub>REF</sub> – 0.5                        | V <sub>REF</sub> + 0.5                        | $V_{REF}$        | 0.90                                   |

| SSTL3 I and II | V <sub>REF</sub> – 1.0                        | V <sub>REF</sub> + 1.0                        | $V_{REF}$        | 1.5                                    |

| SSTL2 I and II | V <sub>REF</sub> -0.75                        | V <sub>REF</sub> + 0.75                       | $V_{REF}$        | 1.25                                   |

| СТТ            | V <sub>REF</sub> – 0.2                        | V <sub>REF</sub> + 0.2                        | $V_{REF}$        | 1.5                                    |

| AGP            | V <sub>REF</sub> –<br>(0.2xV <sub>CCO</sub> ) | V <sub>REF</sub> +<br>(0.2xV <sub>CCO</sub> ) | V <sub>REF</sub> | Per AGP<br>Spec                        |

#### Notes:

- 1. Input waveform switches between V<sub>L</sub> and V<sub>H</sub>.

- 2. Measurements are made at V<sub>REF</sub> Typ, Maximum, and Minimum. Worst-case values are reported.

- I/O parameter measurements are made with the capacitance values shown in the table, "Constants for Calculating TIOOP". See Xilinx application note <u>XAPP179</u> for the appropriate terminations.

- 4. I/O standard measurements are reflected in the IBIS model information except where the IBIS format precludes it.

#### Constants for Calculating T<sub>IOOP</sub>

| Standard                          | C <sub>SL</sub> <sup>(1)</sup><br>(pF) | F <sub>L</sub><br>(ns/pF) |

|-----------------------------------|----------------------------------------|---------------------------|

| LVTTL Fast Slew Rate, 2 mA drive  | 35                                     | 0.41                      |

| LVTTL Fast Slew Rate, 4 mA drive  | 35                                     | 0.20                      |

| LVTTL Fast Slew Rate, 6 mA drive  | 35                                     | 0.13                      |

| LVTTL Fast Slew Rate, 8 mA drive  | 35                                     | 0.079                     |

| LVTTL Fast Slew Rate, 12 mA drive | 35                                     | 0.044                     |

| LVTTL Fast Slew Rate, 16 mA drive | 35                                     | 0.043                     |

| LVTTL Fast Slew Rate, 24 mA drive | 35                                     | 0.033                     |

| LVTTL Slow Slew Rate, 2 mA drive  | 35                                     | 0.41                      |

| LVTTL Slow Slew Rate, 4 mA drive  | 35                                     | 0.20                      |

| LVTTL Slow Slew Rate, 6 mA drive  | 35                                     | 0.100                     |

| LVTTL Slow Slew Rate, 8 mA drive  | 35                                     | 0.086                     |

| LVTTL Slow Slew Rate, 12 mA drive | 35                                     | 0.058                     |

| LVTTL Slow Slew Rate, 16 mA drive | 35                                     | 0.050                     |

| LVTTL Slow Slew Rate, 24 mA drive | 35                                     | 0.048                     |

| LVCMOS2                           | 35                                     | 0.041                     |

| PCI 33 MHz 5V                     | 50                                     | 0.050                     |

| PCI 33 MHZ 3.3V                   | 10                                     | 0.050                     |

| PCI 66 MHz 3.3V                   | 10                                     | 0.033                     |

| GTL                               | 0                                      | 0.014                     |

| GTL+                              | 0                                      | 0.017                     |

| HSTL Class I                      | 20                                     | 0.022                     |

| HSTL Class III                    | 20                                     | 0.016                     |

| HSTL Class IV                     | 20                                     | 0.014                     |

| SSTL2 Class I                     | 30                                     | 0.028                     |

| SSTL2 Class II                    | 30                                     | 0.016                     |

| SSTL3 Class I                     | 30                                     | 0.029                     |

| SSTL3 Class II                    | 30                                     | 0.016                     |

| СТТ                               | 20                                     | 0.035                     |

| AGP                               | 10                                     | 0.037                     |

#### Notes:

- 1. I/O parameter measurements are made with the capacitance values shown above. See Xilinx application note <u>XAPP179</u> for the appropriate terminations.

- 2. I/O standard measurements are reflected in the IBIS model information except where the IBIS format precludes it.

#### Clock Distribution Guidelines<sup>(1)</sup>

|                       |                                          | Speed Grade |      |       |

|-----------------------|------------------------------------------|-------------|------|-------|

|                       |                                          | -6          | -5   |       |

| Symbol                | Description                              | Max         | Max  | Units |

| GCLK Clock Skew       |                                          | <u>.</u>    |      |       |

| T <sub>GSKEWIOB</sub> | Global clock skew between IOB flip-flops | 0.13        | 0.14 | ns    |

Notes:

1. These clock distribution delays are provided for guidance only. They reflect the delays encountered in a typical design under worst-case conditions. Precise values for a particular design are provided by the timing analyzer.

#### **Clock Distribution Switching Characteristics**

T<sub>GPIO</sub> is specified for LVTTL levels. For other standards, adjust T<sub>GPIO</sub> with the values shown in "I/O Standard Global Clock Input Adjustments".

|                   |                                         | Speed Grade |     |       |  |  |

|-------------------|-----------------------------------------|-------------|-----|-------|--|--|

|                   |                                         | -6          | -5  |       |  |  |

| Symbol            | Description                             | Max         | Max | Units |  |  |

| GCLK IOB and Bu   | GCLK IOB and Buffer                     |             |     |       |  |  |

| T <sub>GPIO</sub> | Global clock pad to output              | 0.7         | 0.8 | ns    |  |  |

| T <sub>GIO</sub>  | Global clock buffer I input to O output | 0.7         | 0.8 | ns    |  |  |

#### I/O Standard Global Clock Input Adjustments

Delays associated with a global clock input pad are specified for LVTTL levels. For other standards, adjust the delays by the values shown. A delay adjusted in this way constitutes a worst-case limit.

|                        |                                |                   | Speed | l Grade | Units |  |

|------------------------|--------------------------------|-------------------|-------|---------|-------|--|

| Symbol                 | Description                    | Standard          | -6    | -5      |       |  |

| Data Input Delay       | Adjustments                    |                   |       |         | -     |  |

| T <sub>GPLVTTL</sub>   | Standard-specific global clock | LVTTL             | 0     | 0       | ns    |  |

| T <sub>GPLVCMOS2</sub> | input delay adjustments        | LVCMOS2           | -0.04 | -0.05   | ns    |  |

| T <sub>GPPCI33_3</sub> |                                | PCI, 33 MHz, 3.3V | -0.11 | -0.13   | ns    |  |

| T <sub>GPPCI33_5</sub> |                                | PCI, 33 MHz, 5.0V | 0.26  | 0.30    | ns    |  |

| T <sub>GPPCI66_3</sub> |                                | PCI, 66 MHz, 3.3V | -0.11 | -0.13   | ns    |  |

| T <sub>GPGTL</sub>     | _                              | GTL               | 0.80  | 0.84    | ns    |  |

| T <sub>GPGTLP</sub>    | _                              | GTL+              | 0.71  | 0.73    | ns    |  |

| T <sub>GPHSTL</sub>    | _                              | HSTL              | 0.63  | 0.64    | ns    |  |

| T <sub>GPSSTL2</sub>   |                                | SSTL2             | 0.52  | 0.51    | ns    |  |

| T <sub>GPSSTL3</sub>   |                                | SSTL3             | 0.56  | 0.55    | ns    |  |

| T <sub>GPCTT</sub>     | _                              | CTT               | 0.62  | 0.62    | ns    |  |

| T <sub>GPAGP</sub>     |                                | AGP               | 0.54  | 0.53    | ns    |  |

Notes:

1. Input timing for GPLVTTL is measured at 1.4V. For other I/O standards, see the table "Delay Measurement Methodology," page 60.

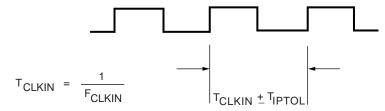

**Period Tolerance:** the allowed input clock period change in nanoseconds.

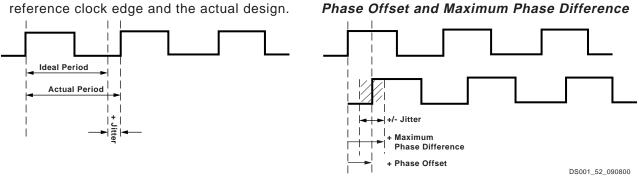

**Output Jitter:** the difference between an ideal reference clock edge and the actual design.

Figure 52: Period Tolerance and Clock Jitter

DS001-4 (v2.8) June 13, 2008

# Spartan-II FPGA Family: Pinout Tables

**Product Specification**

## Introduction

This section describes how the various pins on a Spartan<sup>®</sup>-II FPGA connect within the supported component packages, and provides device-specific thermal characteristics. Spartan-II FPGAs are available in both standard and Pb-free, RoHS versions of each package, with the Pb-free version adding a "G" to the middle of the package code. Except for the thermal characteristics, all

information for the standard package applies equally to the Pb-free package.

# **Pin Types**

Most pins on a Spartan-II FPGA are general-purpose, user-defined I/O pins. There are, however, different functional types of pins on Spartan-II FPGA packages, as outlined in Table 35.

#### Table 35: Pin Definitions

| Pin Name                              | Dedicated | Direction                     | Description                                                                                                                                                                                          |

|---------------------------------------|-----------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCK0, GCK1, GCK2,<br>GCK3             | No        | Input                         | Clock input pins that connect to Global Clock Buffers. These pins become user inputs when not needed for clocks.                                                                                     |

| M0, M1, M2                            | Yes       | Input                         | Mode pins are used to specify the configuration mode.                                                                                                                                                |

| CCLK                                  | Yes       | Input or Output               | The configuration Clock I/O pin. It is an input for slave-parallel and slave-serial modes, and output in master-serial mode.                                                                         |

| PROGRAM                               | Yes       | Input                         | Initiates a configuration sequence when asserted Low.                                                                                                                                                |

| DONE                                  | Yes       | Bidirectional                 | Indicates that configuration loading is complete, and that the start-up sequence is in progress. The output may be open drain.                                                                       |

| INIT                                  | No        | Bidirectional<br>(Open-drain) | When Low, indicates that the configuration memory is being cleared. This pin becomes a user I/O after configuration.                                                                                 |

| BUSY/DOUT                             | No        | Output                        | In Slave Parallel mode, BUSY controls the rate at which configuration data is loaded. This pin becomes a user I/O after configuration unless the Slave Parallel port is retained.                    |

|                                       |           |                               | In serial modes, DOUT provides configuration data to downstream devices in a daisy-chain. This pin becomes a user I/O after configuration.                                                           |

| D0/DIN, D1, D2, D3, D4,<br>D5, D6, D7 | No        | Input or Output               | In Slave Parallel mode, D0-D7 are configuration data input pins. During readback, D0-D7 are output pins. These pins become user I/Os after configuration unless the Slave Parallel port is retained. |

|                                       |           |                               | In serial modes, DIN is the single data input. This pin becomes a user I/O after configuration.                                                                                                      |

| WRITE                                 | No        | Input                         | In Slave Parallel mode, the active-low Write Enable signal. This pin becomes a user I/O after configuration unless the Slave Parallel port is retained.                                              |

| CS                                    | No        | Input                         | In Slave Parallel mode, the active-low Chip Select signal. This pin becomes a user I/O after configuration unless the Slave Parallel port is retained.                                               |

| TDI, TDO, TMS, TCK                    | Yes       | Mixed                         | Boundary Scan Test Access Port pins (IEEE 1149.1).                                                                                                                                                   |

| V <sub>CCINT</sub>                    | Yes       | Input                         | Power supply pins for the internal core logic.                                                                                                                                                       |

| V <sub>CCO</sub>                      | Yes       | Input                         | Power supply pins for output drivers (subject to banking rules)                                                                                                                                      |

| V <sub>REF</sub>                      | No        | Input                         | Input threshold voltage pins. Become user I/Os when an external threshold voltage is not needed (subject to banking rules).                                                                          |

| GND                                   | Yes       | Input                         | Ground.                                                                                                                                                                                              |

| IRDY, TRDY                            | No        | See PCI core documentation    | These signals can only be accessed when using Xilinx <sup>®</sup> PCI cores. If the cores are not used, these pins are available as user I/Os.                                                       |

© 2000-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

www.xilinx.com

| Package        | Leads | Туре                               | Maximum<br>I/O | Lead Pitch<br>(mm) | Footprint<br>Area (mm) | Height<br>(mm) | Mass <sup>(1)</sup><br>(g) |

|----------------|-------|------------------------------------|----------------|--------------------|------------------------|----------------|----------------------------|

| VQ100 / VQG100 | 100   | Very Thin Quad Flat Pack (VQFP)    | 60             | 0.5                | 16 x 16                | 1.20           | 0.6                        |

| TQ144 / TQG144 | 144   | Thin Quad Flat Pack (TQFP)         | 92             | 0.5                | 22 x 22                | 1.60           | 1.4                        |

| CS144 / CSG144 | 144   | Chip Scale Ball Grid Array (CSBGA) | 92             | 0.8                | 12 x 12                | 1.20           | 0.3                        |

| PQ208 / PQG208 | 208   | Plastic Quad Flat Pack (PQFP)      | 140            | 0.5                | 30.6 x 30.6            | 3.70           | 5.3                        |

| FG256 / FGG256 | 256   | Fine-pitch Ball Grid Array (FBGA)  | 176            | 1.0                | 17 x 17                | 2.00           | 0.9                        |

| FG456 / FGG456 | 456   | Fine-pitch Ball Grid Array (FBGA)  | 284            | 1.0                | 23 x 23                | 2.60           | 2.2                        |

#### Table 36: Spartan-II Family Package Options

#### Notes:

1. Package mass is  $\pm 10\%$ .

Note: Some early versions of Spartan-II devices, including the XC2S15 and XC2S30 ES devices and the XC2S150 with date code 0045 or earlier, included a power-down pin. For more information, see <u>Answer Record 10500</u>.

## VCCO Banks

Some of the I/O standards require specific V<sub>CCO</sub> voltages. These voltages are externally connected to device pins that serve groups of IOBs, called banks. Eight I/O banks result from separating each edge of the FPGA into two banks (see Figure 3 in Module 2). Each bank has multiple V<sub>CCO</sub> pins which must be connected to the same voltage. In the smaller packages, the V<sub>CCO</sub> pins are connected between banks, effectively reducing the number of independent banks available (see Table 37). These interconnected banks are shown in the Pinout Tables with V<sub>CCO</sub> pads for multiple banks connected to the same pin.

#### Table 37: Independent VCCO Banks Available

| Package           | VQ100 | CS144 | FG256 |

|-------------------|-------|-------|-------|

|                   | PQ208 | TQ144 | FG456 |

| Independent Banks | 1     | 4     | 8     |

### Package Overview

Table 36 shows the six low-cost, space-saving productionpackage styles for the Spartan-II family.

Each package style is available in an environmentally friendly lead-free (Pb-free) option. The Pb-free packages include an extra 'G' in the package style name. For example, the standard "CS144" package becomes "CSG144" when ordered as the Pb-free option. Leaded (non-Pb-free) packages may be available for selected devices, with the same pin-out and without the "G" in the ordering code; contact Xilinx sales for more information. The mechanical dimensions of the standard and Pb-free packages are similar, as shown in the mechanical drawings provided in Table 38. For additional package information, see <u>UG112</u>: *Device Package User Guide*.

#### **Mechanical Drawings**

Detailed mechanical drawings for each package type are available from the Xilinx web site at the specified location in Table 38.

Material Declaration Data Sheets (MDDS) are also available on the <u>Xilinx web site</u> for each package.

#### Table 38: Xilinx Package Documentation

| Package | Drawing         | MDDS         |

|---------|-----------------|--------------|

| VQ100   | Package Drawing | PK173_VQ100  |

| VQG100  |                 | PK130_VQG100 |

| TQ144   | Package Drawing | PK169_TQ144  |

| TQG144  |                 | PK126_TQG144 |

| CS144   | Package Drawing | PK149_CS144  |

| CSG144  | _               | PK103_CSG144 |

| PQ208   | Package Drawing | PK166_PQ208  |

| PQG208  | _               | PK123_PQG208 |

| FG256   | Package Drawing | PK151_FG256  |

| FGG256  |                 | PK105_FGG256 |

| FG456   | Package Drawing | PK154_FG456  |

| FGG456  |                 | PK109_FGG456 |

# **Package Thermal Characteristics**

Table 39 provides the thermal characteristics for the various Spartan-II FPGA package offerings. This information is also available using the Thermal Query tool on xilinx.com (www.xilinx.com/cgi-bin/thermal/thermal.pl).

The junction-to-case thermal resistance  $(\theta_{JC})$  indicates the difference between the temperature measured on the package body (case) and the die junction temperature per watt of power consumption. The junction-to-board  $(\theta_{JB})$

value similarly reports the difference between the board and junction temperature. The junction-to-ambient ( $\theta_{JA}$ ) value reports the temperature difference between the ambient environment and the junction temperature. The  $\theta_{JA}$  value is reported at different air velocities, measured in linear feet per minute (LFM). The "Still Air (0 LFM)" column shows the  $\theta_{JA}$  value in a system without a fan. The thermal resistance drops with increasing air flow.

|                 |         |                                        |                                          | Junction-to-Ambient (θ <sub>JA</sub> )<br>at Different Air Flows |         |         |         |         |

|-----------------|---------|----------------------------------------|------------------------------------------|------------------------------------------------------------------|---------|---------|---------|---------|

| Package         | Device  | Junction-to-Case<br>(θ <sub>JC</sub> ) | Junction-to-<br>Board (θ <sub>JB</sub> ) | Still Air<br>(0 LFM)                                             | 250 LFM | 500 LFM | 750 LFM | Units   |

| VQ100           | XC2S15  | 11.3                                   | N/A                                      | 44.1                                                             | 36.7    | 34.2    | 33.3    | °C/Watt |

| VQG100          | XC2S30  | 10.1                                   | N/A                                      | 40.7                                                             | 33.9    | 31.5    | 30.8    | °C/Watt |

|                 | XC2S15  | 7.3                                    | N/A                                      | 38.6                                                             | 30.0    | 25.7    | 24.1    | °C/Watt |

| TQ144           | XC2S30  | 6.7                                    | N/A                                      | 34.7                                                             | 27.0    | 23.1    | 21.7    | °C/Watt |

| TQG144          | XC2S50  | 5.8                                    | N/A                                      | 32.2                                                             | 25.1    | 21.4    | 20.1    | °C/Watt |

|                 | XC2S100 | 5.3                                    | N/A                                      | 31.4                                                             | 24.4    | 20.9    | 19.6    | °C/Watt |

| CS144<br>CSG144 | XC2S30  | 2.8                                    | N/A                                      | 34.0                                                             | 26.0    | 23.9    | 23.2    | °C/Watt |

|                 | XC2S50  | 6.7                                    | N/A                                      | 25.2                                                             | 18.6    | 16.4    | 15.2    | °C/Watt |

| PQ208           | XC2S100 | 5.9                                    | N/A                                      | 24.6                                                             | 18.1    | 16.0    | 14.9    | °C/Watt |

| PQG208          | XC2S150 | 5.0                                    | N/A                                      | 23.8                                                             | 17.6    | 15.6    | 14.4    | °C/Watt |

| -               | XC2S200 | 4.1                                    | N/A                                      | 23.0                                                             | 17.0    | 15.0    | 13.9    | °C/Watt |

|                 | XC2S50  | 7.1                                    | 17.6                                     | 27.2                                                             | 21.4    | 20.3    | 19.8    | °C/Watt |

| FG256           | XC2S100 | 5.8                                    | 15.1                                     | 25.1                                                             | 19.5    | 18.3    | 17.8    | °C/Watt |

| FGG256          | XC2S150 | 4.6                                    | 12.7                                     | 23.0                                                             | 17.6    | 16.3    | 15.8    | °C/Watt |

|                 | XC2S200 | 3.5                                    | 10.7                                     | 21.4                                                             | 16.1    | 14.7    | 14.2    | °C/Watt |

| FG456           | XC2S150 | 2.0                                    | N/A                                      | 21.9                                                             | 17.3    | 15.8    | 15.2    | °C/Watt |

| FGG456          | XC2S200 | 2.0                                    | N/A                                      | 21.0                                                             | 16.6    | 15.1    | 14.5    | °C/Watt |

#### XC2S100 Device Pinouts (Continued)

| XC2S100<br>Name       |      |       |       |                             |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | FG456                       | Scan  |

| V <sub>CCINT</sub>    | -    | -     | P38   | $V_{CCINT}^{*}$             | V <sub>CCINT</sub> *        | -     |

| V <sub>CCO</sub>      | 6    | -     | P39   | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -     |

| GND                   | -    | P119  | P40   | GND*                        | GND*                        | -     |

| I/O                   | 6    | P118  | P41   | K4                          | T1                          | 314   |

| I/O, V <sub>REF</sub> | 6    | P117  | P42   | M1                          | R4                          | 317   |

| I/O                   | 6    | -     | -     | -                           | T2                          | 320   |

| I/O                   | 6    | P116  | P43   | L4                          | U1                          | 323   |

| I/O                   | 6    | -     | -     | M2                          | R5                          | 326   |

| I/O                   | 6    | -     | P44   | L3                          | U2                          | 332   |

| I/O, V <sub>REF</sub> | 6    | P115  | P45   | N1                          | Т3                          | 335   |

| V <sub>CCO</sub>      | 6    | -     | -     | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -     |

| GND                   | -    | -     | -     | GND*                        | GND*                        | -     |

| I/O                   | 6    | -     | P46   | P1                          | T4                          | 338   |

| I/O                   | 6    | -     | -     | L5                          | W1                          | 341   |

| I/O                   | 6    | -     | -     | -                           | U4                          | 344   |

| I/O                   | 6    | P114  | P47   | N2                          | Y1                          | 347   |

| I/O                   | 6    | -     | -     | M4                          | W2                          | 350   |

| I/O                   | 6    | P113  | P48   | R1                          | Y2                          | 356   |

| I/O                   | 6    | P112  | P49   | М3                          | W3                          | 359   |

| M1                    | -    | P111  | P50   | P2                          | U5                          | 362   |

| GND                   | -    | P110  | P51   | GND*                        | GND*                        | -     |

| MO                    | -    | P109  | P52   | N3                          | AB2                         | 363   |

| V <sub>CCO</sub>      | 6    | P108  | P53   | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -     |

| V <sub>CCO</sub>      | 5    | P107  | P53   | V <sub>CCO</sub><br>Bank 5* | V <sub>CCO</sub><br>Bank 5* | -     |

| M2                    | -    | P106  | P54   | R3                          | Y4                          | 364   |

| I/O                   | 5    | -     | -     | N5                          | V7                          | 374   |

| I/O                   | 5    | P103  | P57   | T2                          | Y6                          | 377   |

| I/O                   | 5    | -     | -     | -                           | AA4                         | 380   |

| I/O                   | 5    | -     | -     | P5                          | W6                          | 383   |

| I/O                   | 5    | -     | P58   | Т3                          | Y7                          | 386   |

| GND                   | -    | -     | -     | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 5    | -     | -     | V <sub>CCO</sub><br>Bank 5* | V <sub>CCO</sub><br>Bank 5* | -     |

| I/O, V <sub>REF</sub> | 5    | P102  | P59   | T4                          | AA5                         | 389   |

| I/O                   | 5    | -     | P60   | M6                          | AB5                         | 392   |

| I/O                   | 5    | -     | -     | T5                          | AB6                         | 398   |

| I/O                   | 5    | P101  | P61   | N6                          | AA7                         | 401   |

| I/O                   | 5    | -     | -     | -                           | W7                          | 404   |

#### XC2S100 Device Pinouts (Continued)

| XC2S100 Pad<br>Name   |      |       |       |                             |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | FG456                       | Scan  |

| I/O, V <sub>REF</sub> | 5    | P100  | P62   | R5                          | W8                          | 407   |

| I/O                   | 5    | P99   | P63   | P6                          | Y8                          | 410   |

| GND                   | -    | P98   | P64   | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 5    | -     | P65   | V <sub>CCO</sub><br>Bank 5* | V <sub>CCO</sub><br>Bank 5* | -     |

| V <sub>CCINT</sub>    | -    | P97   | P66   | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| I/O                   | 5    | P96   | P67   | R6                          | AA8                         | 413   |

| I/O                   | 5    | P95   | P68   | M7                          | V9                          | 416   |

| I/O                   | 5    | -     | -     | -                           | AB9                         | 419   |

| I/O                   | 5    | -     | P69   | N7                          | Y9                          | 422   |

| I/O                   | 5    | -     | P70   | T6                          | W10                         | 428   |

| I/O                   | 5    | -     | P71   | P7                          | AB10                        | 431   |

| GND                   | -    | -     | P72   | GND*                        | GND*                        | -     |

| I/O, V <sub>REF</sub> | 5    | P94   | P73   | P8                          | Y10                         | 434   |

| I/O                   | 5    | -     | P74   | R7                          | V11                         | 437   |

| I/O                   | 5    | -     | -     | T7                          | W11                         | 440   |

| I/O                   | 5    | P93   | P75   | Т8                          | AB11                        | 443   |

| V <sub>CCINT</sub>    | -    | P92   | P76   | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| I, GCK1               | 5    | P91   | P77   | R8                          | Y11                         | 455   |

| V <sub>CCO</sub>      | 5    | P90   | P78   | V <sub>CCO</sub><br>Bank 5* | V <sub>CCO</sub><br>Bank 5* | -     |

| V <sub>CCO</sub>      | 4    | P90   | P78   | V <sub>CCO</sub><br>Bank 4* | V <sub>CCO</sub><br>Bank 4* | -     |

| GND                   | -    | P89   | P79   | GND*                        | GND*                        | -     |

| I, GCK0               | 4    | P88   | P80   | N8                          | W12                         | 456   |

| I/O                   | 4    | P87   | P81   | N9                          | U12                         | 460   |

| I/O                   | 4    | P86   | P82   | R9                          | Y12                         | 466   |

| I/O                   | 4    | -     | -     | N10                         | AA12                        | 469   |

| I/O                   | 4    | -     | P83   | Т9                          | AB13                        | 472   |

| I/O, V <sub>REF</sub> | 4    | P85   | P84   | P9                          | AA13                        | 475   |

| GND                   | -    | -     | P85   | GND*                        | GND*                        | -     |

| I/O                   | 4    | -     | P86   | M10                         | Y13                         | 478   |

| I/O                   | 4    | -     | P87   | R10                         | V13                         | 481   |

| I/O                   | 4    | -     | P88   | P10                         | AA14                        | 487   |

| I/O                   | 4    | -     | -     | -                           | V14                         | 490   |

| I/O                   | 4    | P84   | P89   | T10                         | AB15                        | 493   |

| I/O                   | 4    | P83   | P90   | R11                         | AA15                        | 496   |

| V <sub>CCINT</sub>    | -    | P82   | P91   | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| V <sub>CCO</sub>      | 4    | -     | P92   | V <sub>CCO</sub><br>Bank 4* | V <sub>CCO</sub><br>Bank 4* | -     |

| GND                   | -    | P81   | P93   | GND*                        | GND*                        | -     |

| I/O                   | 4    | P80   | P94   | M11                         | Y15                         | 499   |

#### XC2S100 Device Pinouts (Continued)

| XC2S100 Pad<br>Name   |      |       |       |                             |                             | Bndry |  |

|-----------------------|------|-------|-------|-----------------------------|-----------------------------|-------|--|

| Function              | Bank | TQ144 | PQ208 | FG256                       | FG456                       | Scan  |  |

| I/O                   | 0    | -     | P188  | A6                          | C10                         | 107   |  |

| I/O, V <sub>REF</sub> | 0    | P12   | P189  | B7                          | A9                          | 110   |  |

| GND                   | -    | -     | P190  | GND*                        | GND*                        | -     |  |

| I/O                   | 0    | -     | P191  | C8                          | B9                          | 113   |  |

| I/O                   | 0    | -     | P192  | D7                          | E10                         | 116   |  |

| I/O                   | 0    | -     | P193  | E7                          | A8                          | 122   |  |

| I/O                   | 0    | -     | -     | -                           | D9                          | 125   |  |

| I/O                   | 0    | P11   | P194  | C7                          | E9                          | 128   |  |

| I/O                   | 0    | P10   | P195  | B6                          | A7                          | 131   |  |

| V <sub>CCINT</sub>    | -    | P9    | P196  | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |  |

| V <sub>CCO</sub>      | 0    | -     | P197  | V <sub>CCO</sub><br>Bank 0* | V <sub>CCO</sub><br>Bank 0* | -     |  |

| GND                   | -    | P8    | P198  | GND*                        | GND*                        | -     |  |

| I/O                   | 0    | P7    | P199  | A5                          | B7                          | 134   |  |

| I/O, V <sub>REF</sub> | 0    | P6    | P200  | C6                          | E8                          | 137   |  |

| I/O                   | 0    | -     | -     | -                           | D8                          | 140   |  |

| I/O                   | 0    | -     | P201  | B5                          | C7                          | 143   |  |

| I/O                   | 0    | -     | -     | D6                          | D7                          | 146   |  |

| I/O                   | 0    | -     | P202  | A4                          | D6                          | 152   |  |

| I/O, V <sub>REF</sub> | 0    | P5    | P203  | B4                          | C6                          | 155   |  |

| V <sub>CCO</sub>      | 0    | -     | -     | V <sub>CCO</sub><br>Bank 0* | V <sub>CCO</sub><br>Bank 0* | -     |  |

| GND                   | -    | -     | -     | GND*                        | GND*                        | -     |  |

| I/O                   | 0    | -     | P204  | E6                          | B5                          | 158   |  |