## E·XFL

#### AMD Xilinx - XC2S50-6TQG144C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | 384                                                         |

| Number of Logic Elements/Cells | 1728                                                        |

| Total RAM Bits                 | 32768                                                       |

| Number of I/O                  | 92                                                          |

| Number of Gates                | 50000                                                       |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 144-LQFP                                                    |

| Supplier Device Package        | 144-TQFP (20x20)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s50-6tqg144c |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

##

DS001-1 (v2.8) June 13, 2008

## Spartan-II FPGA Family: Introduction and Ordering Information

#### **Product Specification**

## Introduction

The Spartan<sup>®</sup>-II Field-Programmable Gate Array family gives users high performance, abundant logic resources, and a rich feature set, all at an exceptionally low price. The six-member family offers densities ranging from 15,000 to 200,000 system gates, as shown in Table 1. System performance is supported up to 200 MHz. Features include block RAM (to 56K bits), distributed RAM (to 75,264 bits), 16 selectable I/O standards, and four DLLs. Fast, predictable interconnect means that successive design iterations continue to meet timing requirements.

The Spartan-II family is a superior alternative to mask-programmed ASICs. The FPGA avoids the initial cost, lengthy development cycles, and inherent risk of conventional ASICs. Also, FPGA programmability permits design upgrades in the field with no hardware replacement necessary (impossible with ASICs).

## **Features**

- Second generation ASIC replacement technology

- Densities as high as 5,292 logic cells with up to 200,000 system gates

- Streamlined features based on Virtex<sup>®</sup> FPGA architecture

- Unlimited reprogrammability

- Very low cost

- Cost-effective 0.18 micron process

- System level features

- SelectRAM<sup>™</sup> hierarchical memory:

- · 16 bits/LUT distributed RAM

- Configurable 4K bit block RAM

- Fast interfaces to external RAM

- Fully PCI compliant

- Low-power segmented routing architecture

- Full readback ability for verification/observability

- Dedicated carry logic for high-speed arithmetic

- Efficient multiplier support

- Cascade chain for wide-input functions

- Abundant registers/latches with enable, set, reset

- Four dedicated DLLs for advanced clock control

- Four primary low-skew global clock distribution nets

- IEEE 1149.1 compatible boundary scan logic

- Versatile I/O and packaging

- Pb-free package options

- Low-cost packages available in all densities

- Family footprint compatibility in common packages

- 16 high-performance interface standards

- Hot swap Compact PCI friendly

- Zero hold time simplifies system timing

- Core logic powered at 2.5V and I/Os powered at 1.5V, 2.5V, or 3.3V

- Fully supported by powerful Xilinx<sup>®</sup> ISE<sup>®</sup> development system

- Fully automatic mapping, placement, and routing

| Table 1: Spartan-II FPGA Family Members |                |                                 |                         |               |                                                 |                                  |                            |

|-----------------------------------------|----------------|---------------------------------|-------------------------|---------------|-------------------------------------------------|----------------------------------|----------------------------|

| Device                                  | Logic<br>Cells | System Gates<br>(Logic and RAM) | CLB<br>Array<br>(R x C) | Total<br>CLBs | Maximum<br>Available<br>User I/O <sup>(1)</sup> | Total<br>Distributed RAM<br>Bits | Total<br>Block RAM<br>Bits |

| XC2S15                                  | 432            | 15,000                          | 8 x 12                  | 96            | 86                                              | 6,144                            | 16K                        |

| XC2S30                                  | 972            | 30,000                          | 12 x 18                 | 216           | 92                                              | 13,824                           | 24K                        |

| XC2S50                                  | 1,728          | 50,000                          | 16 x 24                 | 384           | 176                                             | 24,576                           | 32K                        |

| XC2S100                                 | 2,700          | 100,000                         | 20 x 30                 | 600           | 176                                             | 38,400                           | 40K                        |

| XC2S150                                 | 3,888          | 150,000                         | 24 x 36                 | 864           | 260                                             | 55,296                           | 48K                        |

| XC2S200                                 | 5,292          | 200,000                         | 28 x 42                 | 1,176         | 284                                             | 75,264                           | 56K                        |

#### Notes:

1. All user I/O counts do not include the four global clock/user input pins. See details in Table 2, page 4.

© 2000-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

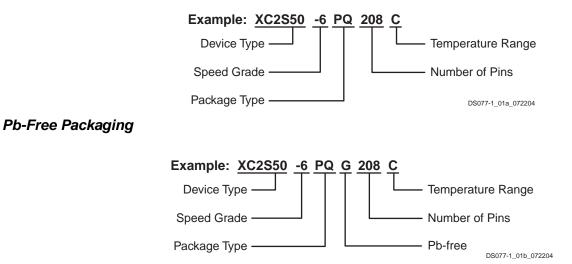

## **Ordering Information**

Spartan-II devices are available in both standard and Pb-free packaging options for all device/package combinations. The Pb-free packages include a special "G" character in the ordering code.

#### Standard Packaging

## **Device Ordering Options**

| Device  |    | Speed Grade                       | Number of Pins / Package Type |                               | Temperatur     | re Range (T <sub>J</sub> ) |

|---------|----|-----------------------------------|-------------------------------|-------------------------------|----------------|----------------------------|

| XC2S15  | -5 | Standard Performance              | VQ(G)100                      | 100-pin Plastic Very Thin QFP | C = Commercial | 0°C to +85°C               |

| XC2S30  | -6 | Higher Performance <sup>(1)</sup> | CS(G)144                      | 144-ball Chip-Scale BGA       | I = Industrial | -40°C to +100°C            |

| XC2S50  |    |                                   | TQ(G)144                      | 144-pin Plastic Thin QFP      |                | 1                          |

| XC2S100 |    |                                   | PQ(G)208                      | 208-pin Plastic QFP           |                |                            |

| XC2S150 |    |                                   | FG(G)256                      | 256-ball Fine Pitch BGA       |                |                            |

| XC2S200 |    |                                   | FG(G)456                      | 456-ball Fine Pitch BGA       |                |                            |

#### Notes:

1. The -6 speed grade is exclusively available in the Commercial temperature range.

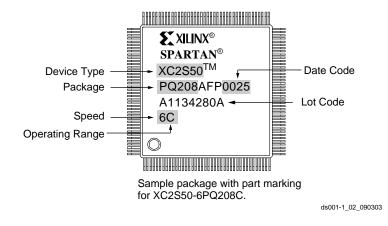

## **Device Part Marking**

www.xilinx.com

## **Revision History**

| Date     | Version No. | Description                                                                                                                            |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 09/18/00 | 2.0         | Sectioned the Spartan-II Family data sheet into four modules. Added industrial temperature range information.                          |

| 10/31/00 | 2.1         | Removed Power down feature.                                                                                                            |

| 03/05/01 | 2.2         | Added statement on PROMs.                                                                                                              |

| 11/01/01 | 2.3         | Updated Product Availability chart. Minor text edits.                                                                                  |

| 09/03/03 | 2.4         | Added device part marking.                                                                                                             |

| 08/02/04 | 2.5         | Added information on Pb-free packaging options and removed discontinued options.                                                       |

| 06/13/08 | 2.8         | Updated description and links. Updated all modules for continuous page, figure, and table numbering. Synchronized all modules to v2.8. |

#

DS001-2 (v2.8) June 13, 2008

## **Architectural Description**

## Spartan-II FPGA Array

The Spartan<sup>®</sup>-II field-programmable gate array, shown in Figure 2, is composed of five major configurable elements:

- IOBs provide the interface between the package pins and the internal logic

- CLBs provide the functional elements for constructing most logic

- Dedicated block RAM memories of 4096 bits each

- Clock DLLs for clock-distribution delay compensation and clock domain control

- Versatile multi-level interconnect structure

As can be seen in Figure 2, the CLBs form the central logic structure with easy access to all support and routing structures. The IOBs are located around all the logic and

## Spartan-II FPGA Family: Functional Description

#### **Product Specification**

memory elements for easy and quick routing of signals on and off the chip.

Values stored in static memory cells control all the configurable logic elements and interconnect resources. These values load into the memory cells on power-up, and can reload if necessary to change the function of the device.

Each of these elements will be discussed in detail in the following sections.

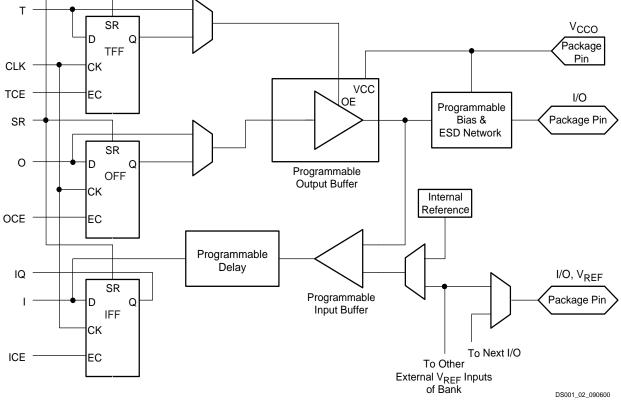

## Input/Output Block

The Spartan-II FPGA IOB, as seen in Figure 2, features inputs and outputs that support a wide variety of I/O signaling standards. These high-speed inputs and outputs are capable of supporting various state of the art memory and bus interfaces. Table 3 lists several of the standards which are supported along with the required reference, output and termination voltages needed to meet the standard.

Figure 2: Spartan-II FPGA Input/Output Block (IOB)

© 2000-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

Boundary-scan operation is independent of individual IOB configurations, and unaffected by package type. All IOBs, including unbonded ones, are treated as independent 3-state bidirectional pins in a single scan chain. Retention of the bidirectional test capability after configuration facilitates the testing of external interconnections.

Table 7 lists the boundary-scan instructions supported in Spartan-II FPGAs. Internal signals can be captured during EXTEST by connecting them to unbonded or unused IOBs. They may also be connected to the unused outputs of IOBs defined as unidirectional input pins.

| Boundary-Scan<br>Command | Binary<br>Code[4:0] | Description                                                   |

|--------------------------|---------------------|---------------------------------------------------------------|

| EXTEST                   | 00000               | Enables boundary-scan<br>EXTEST operation                     |

| SAMPLE                   | 00001               | Enables boundary-scan<br>SAMPLE operation                     |

| USR1                     | 00010               | Access user-defined<br>register 1                             |

| USR2                     | 00011               | Access user-defined<br>register 2                             |

| CFG_OUT                  | 00100               | Access the<br>configuration bus for<br>Readback               |

| CFG_IN                   | 00101               | Access the<br>configuration bus for<br>Configuration          |

| INTEST                   | 00111               | Enables boundary-scan<br>INTEST operation                     |

| USRCODE                  | 01000               | Enables shifting out<br>USER code                             |

| IDCODE                   | 01001               | Enables shifting out of<br>ID Code                            |

| HIZ                      | 01010               | Disables output pins<br>while enabling the<br>Bypass Register |

| JSTART                   | 01100               | Clock the start-up<br>sequence when<br>StartupClk is TCK      |

| BYPASS                   | 11111               | Enables BYPASS                                                |

| RESERVED                 | All other codes     | Xilinx <sup>®</sup> reserved<br>instructions                  |

#### Table 7: Boundary-Scan Instructions

The public boundary-scan instructions are available prior to configuration. After configuration, the public instructions remain available together with any USERCODE instructions installed during the configuration. While the SAMPLE and BYPASS instructions are available during configuration, it is recommended that boundary-scan operations not be performed during this transitional period.

In addition to the test instructions outlined above, the boundary-scan circuitry can be used to configure the FPGA, and also to read back the configuration data.

To facilitate internal scan chains, the User Register provides three outputs (Reset, Update, and Shift) that represent the corresponding states in the boundary-scan internal state machine.

DS001\_16\_032300

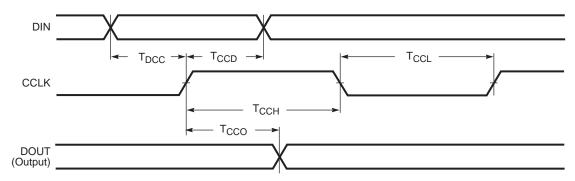

| Symbol           |      | Description       |    | Units    |

|------------------|------|-------------------|----|----------|

| T <sub>DCC</sub> |      | DIN setup         | 5  | ns, min  |

| T <sub>CCD</sub> | CCLK | DIN hold          | 0  | ns, min  |

| T <sub>CCO</sub> |      | DOUT              | 12 | ns, max  |

| ТССН             |      | High time         | 5  | ns, min  |

| T <sub>CCL</sub> |      | Low time          | 5  | ns, min  |

| F <sub>CC</sub>  |      | Maximum frequency | 66 | MHz, max |

Figure 16: Slave Serial Mode Timing

## **BUFGDLL Pin Descriptions**

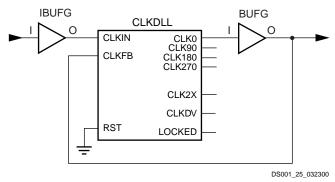

Use the BUFGDLL macro as the simplest way to provide zero propagation delay for a high-fanout on-chip clock from an external input. This macro uses the IBUFG, CLKDLL and BUFG primitives to implement the most basic DLL application as shown in Figure 25.

Figure 25: BUFGDLL Block Diagram

This macro does not provide access to the advanced clock domain controls or to the clock multiplication or clock division features of the DLL. This macro also does not provide access to the RST or LOCKED pins of the DLL. For access to these features, a designer must use the DLL primitives described in the following sections.

#### Source Clock Input — I

The I pin provides the user source clock, the clock signal on which the DLL operates, to the BUFGDLL. For the BUFGDLL macro the source clock frequency must fall in the low frequency range as specified in the data sheet. The BUFGDLL requires an external signal source clock. Therefore, only an external input port can source the signal that drives the BUFGDLL I pin.

#### Clock Output — O

The clock output pin O represents a delay-compensated version of the source clock (I) signal. This signal, sourced by a global clock buffer BUFG primitive, takes advantage of the dedicated global clock routing resources of the device.

The output clock has a 50/50 duty cycle unless you deactivate the duty cycle correction property.

## **CLKDLL Primitive Pin Descriptions**

The library CLKDLL primitives provide access to the complete set of DLL features needed when implementing more complex applications with the DLL.

#### Source Clock Input — CLKIN

The CLKIN pin provides the user source clock (the clock signal on which the DLL operates) to the DLL. The CLKIN frequency must fall in the ranges specified in the data sheet. A global clock buffer (BUFG) driven from another CLKDLL

or one of the global clock input buffers (IBUFG) on the same edge of the device (top or bottom) must source this clock signal.

#### Feedback Clock Input — CLKFB

The DLL requires a reference or feedback signal to provide the delay-compensated output. Connect only the CLK0 or CLK2X DLL outputs to the feedback clock input (CLKFB) pin to provide the necessary feedback to the DLL. Either a global clock buffer (BUFG) or one of the global clock input buffers (IBUFG) on the same edge of the device (top or bottom) must source this clock signal.

If an IBUFG sources the CLKFB pin, the following special rules apply.

- 1. An external input port must source the signal that drives the IBUFG I pin.

- The CLK2X output must feed back to the device if both the CLK0 and CLK2X outputs are driving off chip devices.

- 3. That signal must directly drive only OBUFs and nothing else.

These rules enable the software to determine which DLL clock output sources the CLKFB pin.

#### Reset Input — RST

When the reset pin RST activates, the LOCKED signal deactivates within four source clock cycles. The RST pin, active High, must either connect to a dynamic signal or be tied to ground. As the DLL delay taps reset to zero, glitches can occur on the DLL clock output pins. Activation of the RST pin can also severely affect the duty cycle of the clock output pins. Furthermore, the DLL output clocks no longer deskew with respect to one another. The DLL must be reset when the input clock frequency changes, if the device is reconfigured in Boundary-Scan mode, if the device undergoes a hot swap, and after the device is configured if the input clock is not stable during the startup sequence.

#### 2x Clock Output — CLK2X

The output pin CLK2X provides a frequency-doubled clock with an automatic 50/50 duty-cycle correction. Until the CLKDLL has achieved lock, the CLK2X output appears as a 1x version of the input clock with a 25/75 duty cycle. This behavior allows the DLL to lock on the correct edge with respect to source clock. This pin is not available on the CLKDLLHF primitive.

#### Clock Divide Output — CLKDV

The clock divide output pin CLKDV provides a lower frequency version of the source clock. The CLKDV\_DIVIDE property controls CLKDV such that the source clock is divided by N where N is either 1.5, 2, 2.5, 3, 4, 5, 8, or 16.

This feature provides automatic duty cycle correction. The CLKDV output pin has a 50/50 duty cycle for all values of the

At the third rising edge of CLKA, the  $T_{BCCS}$  parameter is violated with two writes to memory location 0x0F. The DOA and DOB busses reflect the contents of the DIA and DIB busses, but the stored value at 0x7E is invalid.

At the fourth rising edge of CLKA, a read operation is performed at memory location 0x0F and invalid data is present on the DOA bus. Port B also executes a read operation to memory location 0x0F and also reads invalid data.

At the fifth rising edge of CLKA a read operation is performed that does not violate the  $T_{BCCS}$  parameter to the previous write of 0x7E by Port B. THe DOA bus reflects the recently written value by Port B.

### Initialization

The block RAM memory can initialize during the device configuration sequence. The 16 initialization properties of 64 hex values each (a total of 4096 bits) set the initialization of each RAM. These properties appear in Table 14. Any initialization properties not explicitly set configure as zeros. Partial initialization strings pad with zeros. Initialization strings greater than 64 hex values generate an error. The RAMs can be simulated with the initialization values using generics in VHDL simulators and parameters in Verilog simulators.

#### **Initialization in VHDL**

The block RAM structures may be initialized in VHDL for both simulation and synthesis for inclusion in the EDIF output file. The simulation of the VHDL code uses a generic to pass the initialization.

## **Initialization in Verilog**

The block RAM structures may be initialized in Verilog for both simulation and synthesis for inclusion in the EDIF output file. The simulation of the Verilog code uses a defparam to pass the initialization.

#### **Block Memory Generation**

The CORE Generator<sup>™</sup> software generates memory structures using the block RAM features. This program outputs VHDL or Verilog simulation code templates and an EDIF file for inclusion in a design.

| Property | Memory Cells |

|----------|--------------|

| INIT_00  | 255 to 0     |

| INIT_01  | 511 to 256   |

| INIT_02  | 767 to 512   |

| INIT_03  | 1023 to 768  |

| INIT_04  | 1279 to 1024 |

|          |              |

| Property | Memory Cells |

|----------|--------------|

| INIT_05  | 1535 to 1280 |

| INIT_06  | 1791 to 1536 |

| INIT_07  | 2047 to 1792 |

| INIT_08  | 2303 to 2048 |

| INIT_09  | 2559 to 2304 |

| INIT_0a  | 2815 to 2560 |

| INIT_0b  | 3071 to 2816 |

| INIT_0c  | 3327 to 3072 |

| INIT_0d  | 3583 to 3328 |

| INIT_0e  | 3839 to 3584 |

| INIT_0f  | 4095 to 3840 |

For design examples and more information on using the Block RAM, see <u>XAPP173</u>, Using Block SelectRAM+ Memory in Spartan-II FPGAs.

## **Using Versatile I/O**

The Spartan-II FPGA family includes a highly configurable, high-performance I/O resource called Versatile I/O to provide support for a wide variety of I/O standards. The Versatile I/O resource is a robust set of features including programmable control of output drive strength, slew rate, and input delay and hold time. Taking advantage of the flexibility and Versatile I/O features and the design considerations described in this document can improve and simplify system level design.

## Introduction

As FPGAs continue to grow in size and capacity, the larger and more complex systems designed for them demand an increased variety of I/O standards. Furthermore, as system clock speeds continue to increase, the need for high-performance I/O becomes more important. While chip-to-chip delays have an increasingly substantial impact on overall system speed, the task of achieving the desired system performance becomes more difficult with the proliferation of low-voltage I/O standards. Versatile I/O, the revolutionary input/output resources of Spartan-II devices, has resolved this potential problem by providing a highly configurable, high-performance alternative to the I/O resources of more conventional programmable devices. The Spartan-II FPGA Versatile I/O features combine the flexibility and time-to-market advantages of programmable logic with the high performance previously available only with ASICs and custom ICs.

Each Versatile I/O block can support up to 16 I/O standards. Supporting such a variety of I/O standards allows the

## XILINX<sup>®</sup>

#### GTL

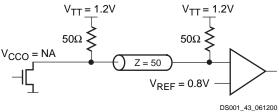

A sample circuit illustrating a valid termination technique for GTL is shown in Figure 42. Table 20 lists DC voltage specifications for the GTL standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 42: Terminated GTL

#### Table 20: GTL Voltage Specifications

| Parameter                                       | Min  | Тур  | Max  |

|-------------------------------------------------|------|------|------|

| V <sub>CCO</sub>                                | -    | N/A  | -    |

| $V_{REF} = N \times V_{TT}^{(1)}$               | 0.74 | 0.8  | 0.86 |

| V <sub>TT</sub>                                 | 1.14 | 1.2  | 1.26 |

| $V_{IH} \ge V_{REF} + 0.05$                     | 0.79 | 0.85 | -    |

| $V_{IL} \leq V_{REF} - 0.05$                    | -    | 0.75 | 0.81 |

| V <sub>OH</sub>                                 | -    | -    | -    |

| V <sub>OL</sub>                                 | -    | 0.2  | 0.4  |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)         | -    | -    | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.4V | 32   | -    | -    |

| $I_{OL}$ at $V_{OL}$ (mA) at 0.2V               | -    | -    | 40   |

#### Notes:

1. N must be greater than or equal to 0.653 and less than or equal to 0.68.

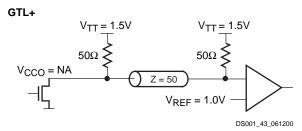

#### GTL+

A sample circuit illustrating a valid termination technique for GTL+ appears in Figure 43. DC voltage specifications appear in Table 21 for the GTL+ standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 43: Terminated GTL+

#### Table 21: GTL+ Voltage Specifications

| Parameter                                       | Min  | Тур  | Max  |

|-------------------------------------------------|------|------|------|

| V <sub>CCO</sub>                                | -    | -    | -    |

| $V_{REF} = N \times V_{TT}^{(1)}$               | 0.88 | 1.0  | 1.12 |

| V <sub>TT</sub>                                 | 1.35 | 1.5  | 1.65 |

| $V_{IH} \ge V_{REF} + 0.1$                      | 0.98 | 1.1  | -    |

| $V_{IL} \le V_{REF} - 0.1$                      | -    | 0.9  | 1.02 |

| V <sub>OH</sub>                                 | -    | -    | -    |

| V <sub>OL</sub>                                 | 0.3  | 0.45 | 0.6  |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)         | -    | -    | -    |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.6V | 36   | -    | -    |

| $I_{OL}$ at $V_{OL}$ (mA) at 0.3V               | -    | -    | 48   |

#### Notes:

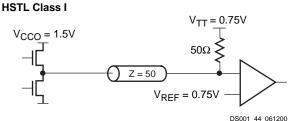

#### HSTL Class I

A sample circuit illustrating a valid termination technique for HSTL\_I appears in Figure 44. DC voltage specifications appear in Table 22 for the HSTL\_1 standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

DS001\_44\_061.

Figure 44: Terminated HSTL Class I

#### Table 22: HSTL Class I Voltage Specification

| Parameter                               | Min                    | Тур                 | Max             |

|-----------------------------------------|------------------------|---------------------|-----------------|

| V <sub>CCO</sub>                        | 1.40                   | 1.50                | 1.60            |

| V <sub>REF</sub>                        | 0.68                   | 0.75                | 0.90            |

| V <sub>TT</sub>                         | -                      | $V_{CCO} 	imes 0.5$ | -               |

| V <sub>IH</sub>                         | V <sub>REF</sub> + 0.1 | -                   | -               |

| V <sub>IL</sub>                         | -                      | -                   | $V_{REF} - 0.1$ |

| V <sub>OH</sub>                         | $V_{CCO} - 0.4$        | -                   | -               |

| V <sub>OL</sub>                         |                        |                     | 0.4             |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -8                     | -                   | -               |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 8                      | -                   | -               |

<sup>1.</sup> N must be greater than or equal to 0.653 and less than or equal to 0.68.

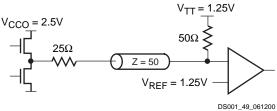

#### SSTL2\_I

A sample circuit illustrating a valid termination technique for SSTL2\_I appears in Figure 49. DC voltage specifications appear in Table 27 for the SSTL2\_I standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics

#### SSTL2 Class I

Figure 49: Terminated SSTL2 Class I

| Table | 27: | SSTL2_I | Voltage | Specifications |

|-------|-----|---------|---------|----------------|

|-------|-----|---------|---------|----------------|

| Parameter                                 | Min                 | Тур  | Max                |

|-------------------------------------------|---------------------|------|--------------------|

| V <sub>CCO</sub>                          | 2.3                 | 2.5  | 2.7                |

| $V_{REF} = 0.5 \times V_{CCO}$            | 1.15                | 1.25 | 1.35               |

| $V_{TT} = V_{REF} + N^{(1)}$              | 1.11                | 1.25 | 1.39               |

| $V_{IH} \ge V_{REF} + 0.18$               | 1.33                | 1.43 | 3.0 <sup>(2)</sup> |

| $V_{IL} \leq V_{REF} - 0.18$              | -0.3 <sup>(3)</sup> | 1.07 | 1.17               |

| V <sub>OH</sub> ≥ V <sub>REF</sub> + 0.61 | 1.76                | -    | -                  |

| $V_{OL} \leq V_{REF} - 0.61$              | -                   | -    | 0.74               |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)   | -7.6                | -    | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA)   | 7.6                 | -    | -                  |

#### Notes:

- 1. N must be greater than or equal to -0.04 and less than or equal to 0.04.

- 2.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3.

- 3. V<sub>IL</sub> minimum does not conform to the formula.

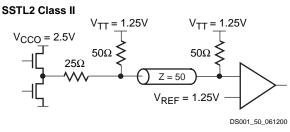

#### SSTL2 Class II

A sample circuit illustrating a valid termination technique for SSTL2\_II appears in Figure 50. DC voltage specifications appear in Table 28 for the SSTL2\_II standard. See "DC Specifications" in Module 3 for the actual FPGA characteristics.

Figure 50: Terminated SSTL2 Class II

#### Table 28: SSTL2\_II Voltage Specifications

| Parameter                               | Min                 | Тур  | Max                |

|-----------------------------------------|---------------------|------|--------------------|

| V <sub>CCO</sub>                        | 2.3                 | 2.5  | 2.7                |

| $V_{REF} = 0.5 \times V_{CCO}$          | 1.15                | 1.25 | 1.35               |

| $V_{TT} = V_{REF} + N^{(1)}$            | 1.11                | 1.25 | 1.39               |

| $V_{IH} \ge V_{REF} + 0.18$             | 1.33                | 1.43 | 3.0 <sup>(2)</sup> |

| $V_{IL} \leq V_{REF} - 0.18$            | -0.3 <sup>(3)</sup> | 1.07 | 1.17               |

| $V_{OH} \ge V_{REF} + 0.8$              | 1.95                | -    | -                  |

| $V_{OL} \leq V_{REF} - 0.8$             | -                   | -    | 0.55               |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -15.2               | -    | -                  |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) | 15.2                | -    | -                  |

#### Notes:

- 1. N must be greater than or equal to -0.04 and less than or equal to 0.04.

- 2.  $V_{IH}$  maximum is  $V_{CCO}$  + 0.3.

- 3. V<sub>IL</sub> minimum does not conform to the formula.

## Spartan-II FPGA Family: DC and Switching Characteristics

DS001-3 (v2.8) June 13, 2008

**Product Specification**

## **Definition of Terms**

In this document, some specifications may be designated as Advance or Preliminary. These terms are defined as follows:

Advance: Initial estimates based on simulation and/or extrapolation from other speed grades, devices, or families. Values are subject to change. Use as estimates, not for production.

Preliminary: Based on preliminary characterization. Further changes are not expected.

Unmarked: Specifications not identified as either Advance or Preliminary are to be considered Final.

Except for pin-to-pin input and output parameters, the AC parameter delay specifications included in this document are derived from measuring internal test patterns. All limits are representative of worst-case supply voltage and junction temperature conditions. Typical numbers are based on measurements taken at a nominal  $V_{CCINT}$  level of 2.5V and a junction temperature of 25°C. The parameters included are common to popular designs and typical applications. All specifications are subject to change without notice.

## **DC Specifications**

#### Absolute Maximum Ratings<sup>(1)</sup>

| Symbol             | Descriptio                                    | Description                    |      | Max                   | Units |

|--------------------|-----------------------------------------------|--------------------------------|------|-----------------------|-------|

| V <sub>CCINT</sub> | Supply voltage relative to GND <sup>(2)</sup> |                                | -0.5 | 3.0                   | V     |

| V <sub>CCO</sub>   | Supply voltage relative to GND <sup>(2)</sup> |                                | -0.5 | 4.0                   | V     |

| V <sub>REF</sub>   | Input reference voltage                       | Input reference voltage        |      | 3.6                   | V     |

| V <sub>IN</sub>    | Input voltage relative to GND <sup>(3)</sup>  | 5V tolerant I/O <sup>(4)</sup> | -0.5 | 5.5                   | V     |

|                    |                                               | No 5V tolerance <sup>(5)</sup> | -0.5 | V <sub>CCO</sub> +0.5 | V     |

| V <sub>TS</sub>    | Voltage applied to 3-state output             | 5V tolerant I/O <sup>(4)</sup> | -0.5 | 5.5                   | V     |

|                    |                                               | No 5V tolerance <sup>(5)</sup> | -0.5 | V <sub>CCO</sub> +0.5 | V     |

| T <sub>STG</sub>   | Storage temperature (ambient)                 |                                | -65  | +150                  | °C    |

| TJ                 | Junction temperature                          | Junction temperature           |      | +125                  | °C    |

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

2. Power supplies may turn on in any order.

3. V<sub>IN</sub> should not exceed V<sub>CCO</sub> by more than 3.6V over extended periods of time (e.g., longer than a day).

4. Spartan<sup>®</sup>-II device I/Os are 5V Tolerant whenever the LVTTL, LVCMOS2, or PCI33\_5 signal standard has been selected. With 5V Tolerant I/Os selected, the Maximum DC overshoot must be limited to either +5.5V or 10 mA, and undershoot must be limited to either -0.5V or 10 mA, whichever is easier to achieve. The Maximum AC conditions are as follows: The device pins may undershoot to -2.0V or overshoot to +7.0V, provided this over/undershoot lasts no more than 11 ns with a forcing current no greater than 100 mA.

5. Without 5V Tolerant I/Os selected, the Maximum DC overshoot must be limited to either V<sub>CCO</sub> + 0.5V or 10 mA, and undershoot must be limited to -0.5V or 10 mA, whichever is easier to achieve. The Maximum AC conditions are as follows: The device pins may undershoot to -2.0V or overshoot to V<sub>CCO</sub> + 2.0V, provided this over/undershoot lasts no more than 11 ns with a forcing current no greater than 100 mA.

6. For soldering guidelines, see the <u>Packaging Information</u> on the Xilinx<sup>®</sup> web site.

© 2000-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

| Input/Output |        | V <sub>IL</sub>        | V                      | н      | V <sub>OL</sub>        | V <sub>OH</sub>        | I <sub>OL</sub> | I <sub>ОН</sub> |

|--------------|--------|------------------------|------------------------|--------|------------------------|------------------------|-----------------|-----------------|

| Standard     | V, Min | V, Max                 | V, Min                 | V, Max | V, Max                 | V, Min                 | mA              | mA              |

| CTT          | -0.5   | V <sub>REF</sub> – 0.2 | V <sub>REF</sub> + 0.2 | 3.6    | V <sub>REF</sub> – 0.4 | V <sub>REF</sub> + 0.4 | 8               | -8              |

| AGP          | -0.5   | V <sub>REF</sub> – 0.2 | V <sub>REF</sub> + 0.2 | 3.6    | 10% V <sub>CCO</sub>   | 90% V <sub>CCO</sub>   | Note (2)        | Note (2)        |

#### Notes:

1. V<sub>OL</sub> and V<sub>OH</sub> for lower drive currents are sample tested.

2. Tested according to the relevant specifications.

## **Switching Characteristics**

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all Spartan-II devices unless otherwise noted.

## Global Clock Input to Output Delay for LVTTL, with DLL (Pin-to-Pin)<sup>(1)</sup>

|                       |                                                                                                                    |        | S   | Speed Grade |     |       |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|-----|-------|

|                       |                                                                                                                    |        | All | -6          | -5  |       |

| Symbol                | Description                                                                                                        | Device | Min | Max         | Max | Units |

| T <sub>ICKOFDLL</sub> | Global clock input to output delay<br>using output flip-flop for LVTTL,<br>12 mA, fast slew rate, <i>with</i> DLL. | All    |     | 2.9         | 3.3 | ns    |

#### Notes:

1. Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

- Output timing is measured at 1.4V with 35 pF external capacitive load for LVTTL. The 35 pF load does not apply to the Min values. For other I/O standards and different loads, see the tables "Constants for Calculating TIOOP" and "Delay Measurement Methodology," page 60.

- 3. DLL output jitter is already included in the timing calculation.

- 4. For data *output* with different standards, adjust delays with the values shown in "IOB Output Delay Adjustments for Different Standards," page 59. For a global clock input with standards other than LVTTL, adjust delays with values from the "I/O Standard Global Clock Input Adjustments," page 61.

## Global Clock Input to Output Delay for LVTTL, *without* DLL (Pin-to-Pin)<sup>(1)</sup>

|                    |                                                                                 |         |     | Speed Grade |     |       |

|--------------------|---------------------------------------------------------------------------------|---------|-----|-------------|-----|-------|

|                    |                                                                                 |         | All | -6          | -5  | -     |

| Symbol             | Description                                                                     | Device  | Min | Max         | Max | Units |

| T <sub>ICKOF</sub> | Global clock input to output delay                                              | XC2S15  |     | 4.5         | 5.4 | ns    |

|                    | using output flip-flop for LVTTL,<br>12 mA, fast slew rate, <i>without</i> DLL. | XC2S30  |     | 4.5         | 5.4 | ns    |

|                    |                                                                                 | XC2S50  |     | 4.5         | 5.4 | ns    |

|                    |                                                                                 | XC2S100 |     | 4.6         | 5.5 | ns    |

|                    |                                                                                 | XC2S150 |     | 4.6         | 5.5 | ns    |

|                    |                                                                                 | XC2S200 |     | 4.7         | 5.6 | ns    |

Notes:

1. Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

Output timing is measured at 1.4V with 35 pF external capacitive load for LVTTL. The 35 pF load does not apply to the Min values. For other I/O standards and different loads, see the tables "Constants for Calculating TIOOP" and "Delay Measurement Methodology," page 60.

For data *output* with different standards, adjust delays with the values shown in "IOB Output Delay Adjustments for Different Standards," page 59. For a global clock input with standards other than LVTTL, adjust delays with values from the "I/O Standard Global Clock Input Adjustments," page 61.

DS001-4 (v2.8) June 13, 2008

## Spartan-II FPGA Family: Pinout Tables

**Product Specification**

## Introduction

This section describes how the various pins on a Spartan<sup>®</sup>-II FPGA connect within the supported component packages, and provides device-specific thermal characteristics. Spartan-II FPGAs are available in both standard and Pb-free, RoHS versions of each package, with the Pb-free version adding a "G" to the middle of the package code. Except for the thermal characteristics, all

information for the standard package applies equally to the Pb-free package.

## **Pin Types**

Most pins on a Spartan-II FPGA are general-purpose, user-defined I/O pins. There are, however, different functional types of pins on Spartan-II FPGA packages, as outlined in Table 35.

#### Table 35: Pin Definitions

| Pin Name                              | Dedicated | Direction                     | Description                                                                                                                                                                                          |

|---------------------------------------|-----------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCK0, GCK1, GCK2,<br>GCK3             | No        | Input                         | Clock input pins that connect to Global Clock Buffers. These pins become user inputs when not needed for clocks.                                                                                     |

| M0, M1, M2                            | Yes       | Input                         | Mode pins are used to specify the configuration mode.                                                                                                                                                |

| CCLK                                  | Yes       | Input or Output               | The configuration Clock I/O pin. It is an input for slave-parallel and slave-serial modes, and output in master-serial mode.                                                                         |

| PROGRAM                               | Yes       | Input                         | Initiates a configuration sequence when asserted Low.                                                                                                                                                |

| DONE                                  | Yes       | Bidirectional                 | Indicates that configuration loading is complete, and that the start-up sequence is in progress. The output may be open drain.                                                                       |

| INIT                                  | No        | Bidirectional<br>(Open-drain) | When Low, indicates that the configuration memory is being cleared. This pin becomes a user I/O after configuration.                                                                                 |

| BUSY/DOUT                             | No        | Output                        | In Slave Parallel mode, BUSY controls the rate at which configuration data is loaded. This pin becomes a user I/O after configuration unless the Slave Parallel port is retained.                    |

|                                       |           |                               | In serial modes, DOUT provides configuration data to downstream devices in a daisy-chain. This pin becomes a user I/O after configuration.                                                           |

| D0/DIN, D1, D2, D3, D4,<br>D5, D6, D7 | No        | Input or Output               | In Slave Parallel mode, D0-D7 are configuration data input pins. During readback, D0-D7 are output pins. These pins become user I/Os after configuration unless the Slave Parallel port is retained. |

|                                       |           |                               | In serial modes, DIN is the single data input. This pin becomes a user I/O after configuration.                                                                                                      |

| WRITE                                 | No        | Input                         | In Slave Parallel mode, the active-low Write Enable signal. This pin becomes a user I/O after configuration unless the Slave Parallel port is retained.                                              |

| CS                                    | No        | Input                         | In Slave Parallel mode, the active-low Chip Select signal. This pin becomes a user I/O after configuration unless the Slave Parallel port is retained.                                               |

| TDI, TDO, TMS, TCK                    | Yes       | Mixed                         | Boundary Scan Test Access Port pins (IEEE 1149.1).                                                                                                                                                   |

| V <sub>CCINT</sub>                    | Yes       | Input                         | Power supply pins for the internal core logic.                                                                                                                                                       |

| V <sub>CCO</sub>                      | Yes       | Input                         | Power supply pins for output drivers (subject to banking rules)                                                                                                                                      |

| V <sub>REF</sub>                      | No        | Input                         | Input threshold voltage pins. Become user I/Os when an external threshold voltage is not needed (subject to banking rules).                                                                          |

| GND                                   | Yes       | Input                         | Ground.                                                                                                                                                                                              |

| IRDY, TRDY                            | No        | See PCI core documentation    | These signals can only be accessed when using Xilinx <sup>®</sup> PCI cores. If the cores are not used, these pins are available as user I/Os.                                                       |

© 2000-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

www.xilinx.com

| Package        | Leads | Туре                               | Maximum<br>I/O | Lead Pitch<br>(mm) | Footprint<br>Area (mm) | Height<br>(mm) | Mass <sup>(1)</sup><br>(g) |

|----------------|-------|------------------------------------|----------------|--------------------|------------------------|----------------|----------------------------|

| VQ100 / VQG100 | 100   | Very Thin Quad Flat Pack (VQFP)    | 60             | 0.5                | 16 x 16                | 1.20           | 0.6                        |

| TQ144 / TQG144 | 144   | Thin Quad Flat Pack (TQFP)         | 92             | 0.5                | 22 x 22                | 1.60           | 1.4                        |

| CS144 / CSG144 | 144   | Chip Scale Ball Grid Array (CSBGA) | 92             | 0.8                | 12 x 12                | 1.20           | 0.3                        |

| PQ208 / PQG208 | 208   | Plastic Quad Flat Pack (PQFP)      | 140            | 0.5                | 30.6 x 30.6            | 3.70           | 5.3                        |

| FG256 / FGG256 | 256   | Fine-pitch Ball Grid Array (FBGA)  | 176            | 1.0                | 17 x 17                | 2.00           | 0.9                        |

| FG456 / FGG456 | 456   | Fine-pitch Ball Grid Array (FBGA)  | 284            | 1.0                | 23 x 23                | 2.60           | 2.2                        |

#### Table 36: Spartan-II Family Package Options

#### Notes:

1. Package mass is  $\pm 10\%$ .

Note: Some early versions of Spartan-II devices, including the XC2S15 and XC2S30 ES devices and the XC2S150 with date code 0045 or earlier, included a power-down pin. For more information, see <u>Answer Record 10500</u>.

## VCCO Banks

Some of the I/O standards require specific V<sub>CCO</sub> voltages. These voltages are externally connected to device pins that serve groups of IOBs, called banks. Eight I/O banks result from separating each edge of the FPGA into two banks (see Figure 3 in Module 2). Each bank has multiple V<sub>CCO</sub> pins which must be connected to the same voltage. In the smaller packages, the V<sub>CCO</sub> pins are connected between banks, effectively reducing the number of independent banks available (see Table 37). These interconnected banks are shown in the Pinout Tables with V<sub>CCO</sub> pads for multiple banks connected to the same pin.

#### Table 37: Independent VCCO Banks Available

| Package           | VQ100 | CS144 | FG256 |

|-------------------|-------|-------|-------|

|                   | PQ208 | TQ144 | FG456 |

| Independent Banks | 1     | 4     | 8     |

## Package Overview

Table 36 shows the six low-cost, space-saving productionpackage styles for the Spartan-II family.

Each package style is available in an environmentally friendly lead-free (Pb-free) option. The Pb-free packages include an extra 'G' in the package style name. For example, the standard "CS144" package becomes "CSG144" when ordered as the Pb-free option. Leaded (non-Pb-free) packages may be available for selected devices, with the same pin-out and without the "G" in the ordering code; contact Xilinx sales for more information. The mechanical dimensions of the standard and Pb-free packages are similar, as shown in the mechanical drawings provided in Table 38. For additional package information, see <u>UG112</u>: *Device Package User Guide*.

## **Mechanical Drawings**

Detailed mechanical drawings for each package type are available from the Xilinx web site at the specified location in Table 38.

Material Declaration Data Sheets (MDDS) are also available on the <u>Xilinx web site</u> for each package.

#### Table 38: Xilinx Package Documentation

| Package | Drawing         | MDDS         |

|---------|-----------------|--------------|

| VQ100   | Package Drawing | PK173_VQ100  |

| VQG100  |                 | PK130_VQG100 |

| TQ144   | Package Drawing | PK169_TQ144  |

| TQG144  |                 | PK126_TQG144 |

| CS144   | Package Drawing | PK149_CS144  |

| CSG144  | _               | PK103_CSG144 |

| PQ208   | Package Drawing | PK166_PQ208  |

| PQG208  | _               | PK123_PQG208 |

| FG256   | Package Drawing | PK151_FG256  |

| FGG256  |                 | PK105_FGG256 |

| FG456   | Package Drawing | PK154_FG456  |

| FGG456  |                 | PK109_FGG456 |

## **Pinout Tables**

The following device-specific pinout tables include all packages available for each Spartan<sup>®</sup>-II device. They follow the pad locations around the die, and include Boundary Scan register locations.

## **XC2S15 Device Pinouts**

| XC2S15 Pad Name          |      |       |       |       | Bndry |

|--------------------------|------|-------|-------|-------|-------|

| Function                 | Bank | VQ100 | TQ144 | CS144 | Scan  |

| GND                      | -    | P1    | P143  | A1    | -     |

| TMS                      | -    | P2    | P142  | B1    | -     |

| I/O                      | 7    | P3    | P141  | C2    | 77    |

| I/O                      | 7    | -     | P140  | C1    | 80    |

| I/O, V <sub>REF</sub>    | 7    | P4    | P139  | D4    | 83    |

| I/O                      | 7    | P5    | P137  | D2    | 86    |

| I/O                      | 7    | P6    | P136  | D1    | 89    |

| GND                      | -    | -     | P135  | E4    | -     |

| I/O                      | 7    | P7    | P134  | E3    | 92    |

| I/O                      | 7    | -     | P133  | E2    | 95    |

| I/O, V <sub>REF</sub>    | 7    | P8    | P132  | E1    | 98    |

| I/O                      | 7    | P9    | P131  | F4    | 101   |

| I/O                      | 7    | -     | P130  | F3    | 104   |

| I/O, IRDY <sup>(1)</sup> | 7    | P10   | P129  | F2    | 107   |

| GND                      | -    | P11   | P128  | F1    | -     |

| V <sub>CCO</sub>         | 7    | P12   | P127  | G2    | -     |

| V <sub>CCO</sub>         | 6    | P12   | P127  | G2    | -     |

| I/O, TRDY <sup>(1)</sup> | 6    | P13   | P126  | G1    | 110   |

| V <sub>CCINT</sub>       | -    | P14   | P125  | G3    | -     |

| I/O                      | 6    | -     | P124  | G4    | 113   |

| I/O                      | 6    | P15   | P123  | H1    | 116   |

| I/O, V <sub>REF</sub>    | 6    | P16   | P122  | H2    | 119   |

| I/O                      | 6    | -     | P121  | H3    | 122   |

| I/O                      | 6    | P17   | P120  | H4    | 125   |

| GND                      | -    | -     | P119  | J1    | -     |

| I/O                      | 6    | P18   | P118  | J2    | 128   |

| I/O                      | 6    | P19   | P117  | J3    | 131   |

| I/O, V <sub>REF</sub>    | 6    | P20   | P115  | K1    | 134   |

| I/O                      | 6    | -     | P114  | K2    | 137   |

| I/O                      | 6    | P21   | P113  | K3    | 140   |

| I/O                      | 6    | P22   | P112  | L1    | 143   |

| M1                       | -    | P23   | P111  | L2    | 146   |

| GND                      | -    | P24   | P110  | L3    | -     |

| M0                       | -    | P25   | P109  | M1    | 147   |

| V <sub>CCO</sub>         | 6    | P26   | P108  | M2    | -     |

| V <sub>CCO</sub>         | 5    | P26   | P107  | N1    | -     |

## XC2S15 Device Pinouts (Continued)

| XC2S15 Pad Name       |      |       |       |       | Bndry |

|-----------------------|------|-------|-------|-------|-------|

| Function              | Bank | VQ100 | TQ144 | CS144 | Scan  |

| M2                    | -    | P27   | P106  | N2    | 148   |

| I/O                   | 5    | -     | P103  | K4    | 155   |

| I/O, V <sub>REF</sub> | 5    | P30   | P102  | L4    | 158   |

| I/O                   | 5    | P31   | P100  | N4    | 161   |

| I/O                   | 5    | P32   | P99   | K5    | 164   |

| GND                   | -    | -     | P98   | L5    | -     |

| V <sub>CCINT</sub>    | -    | P33   | P97   | M5    | -     |

| I/O                   | 5    | -     | P96   | N5    | 167   |

| I/O                   | 5    | -     | P95   | K6    | 170   |

| I/O, V <sub>REF</sub> | 5    | P34   | P94   | L6    | 173   |

| I/O                   | 5    | -     | P93   | M6    | 176   |

| V <sub>CCINT</sub>    | -    | P35   | P92   | N6    | -     |

| I, GCK1               | 5    | P36   | P91   | M7    | 185   |

| V <sub>CCO</sub>      | 5    | P37   | P90   | N7    | -     |

| V <sub>CCO</sub>      | 4    | P37   | P90   | N7    | -     |

| GND                   | -    | P38   | P89   | L7    | -     |

| I, GCK0               | 4    | P39   | P88   | K7    | 186   |

| I/O                   | 4    | P40   | P87   | N8    | 190   |

| I/O                   | 4    | -     | P86   | M8    | 193   |

| I/O, V <sub>REF</sub> | 4    | P41   | P85   | L8    | 196   |

| I/O                   | 4    | -     | P84   | K8    | 199   |

| I/O                   | 4    | -     | P83   | N9    | 202   |

| V <sub>CCINT</sub>    | -    | P42   | P82   | M9    | -     |

| GND                   | -    | -     | P81   | L9    | -     |

| I/O                   | 4    | P43   | P80   | K9    | 205   |

| I/O                   | 4    | P44   | P79   | N10   | 208   |

| I/O, V <sub>REF</sub> | 4    | P45   | P77   | L10   | 211   |

| I/O                   | 4    | -     | P76   | N11   | 214   |

| I/O                   | 4    | P46   | P75   | M11   | 217   |

| I/O                   | 4    | P47   | P74   | L11   | 220   |

| GND                   | -    | P48   | P73   | N12   | -     |

| DONE                  | 3    | P49   | P72   | M12   | 223   |

| V <sub>cco</sub>      | 4    | P50   | P71   | N13   | -     |

| V <sub>CCO</sub>      | 3    | P50   | P70   | M13   | -     |

| PROGRAM               | -    | P51   | P69   | L12   | 226   |

| I/O (INIT)            | 3    | P52   | P68   | L13   | 227   |

| I/O (D7)              | 3    | P53   | P67   | K10   | 230   |

| I/O                   | 3    | -     | P66   | K11   | 233   |

| I/O, V <sub>REF</sub> | 3    | P54   | P65   | K12   | 236   |

| I/O                   | 3    | P55   | P63   | J10   | 239   |

| I/O (D6)              | 3    | P56   | P62   | J11   | 233   |

| "O (DO)               | 5    | 1.00  | 102   | 011   | 272   |

Bndry

Scan

203

206

209

212

215

218

-

219

-

-

220

227

230

233

236

239

242

-

-

\_

245

248

251

254

257

-

260

263

266

-

275

-

-

-

276

280

283

286

289

-

292

### **XC2S30 Device Pinouts**

| <b>XC2S30 Device Pinouts</b> | (Continued) |

|------------------------------|-------------|

|------------------------------|-------------|

| (C2330 D                 |      |       |       |       |       |       |                       |      |       |       |       |   |

|--------------------------|------|-------|-------|-------|-------|-------|-----------------------|------|-------|-------|-------|---|

| XC2S30 Pad               | Name |       |       |       |       | Bndry | XC2S30 Pad            | Name |       |       |       |   |

| Function                 | Bank | VQ100 | TQ144 | CS144 | PQ208 | Scan  | Function              | Bank | VQ100 | TQ144 | CS144 | ŀ |

| GND                      | -    | P1    | P143  | A1    | P1    | -     | I/O, V <sub>REF</sub> | 6    | P20   | P115  | K1    |   |

| TMS                      | -    | P2    | P142  | B1    | P2    | -     | I/O                   | 6    | -     | -     | -     |   |

| I/O                      | 7    | P3    | P141  | C2    | P3    | 113   | I/O                   | 6    | -     | P114  | K2    |   |

| I/O                      | 7    | -     | P140  | C1    | P4    | 116   | I/O                   | 6    | P21   | P113  | K3    |   |

| I/O                      | 7    | -     | -     | -     | P5    | 119   | I/O                   | 6    | P22   | P112  | L1    |   |

| I/O, V <sub>REF</sub>    | 7    | P4    | P139  | D4    | P6    | 122   | M1                    | -    | P23   | P111  | L2    |   |

| I/O                      | 7    | -     | P138  | D3    | P8    | 125   | GND                   | -    | P24   | P110  | L3    |   |

| I/O                      | 7    | P5    | P137  | D2    | P9    | 128   | MO                    | -    | P25   | P109  | M1    |   |

| I/O                      | 7    | P6    | P136  | D1    | P10   | 131   | V <sub>CCO</sub>      | 6    | P26   | P108  | M2    |   |

| GND                      | -    | -     | P135  | E4    | P11   | -     | V <sub>CCO</sub>      | 5    | P26   | P107  | N1    |   |

| V <sub>CCO</sub>         | 7    | -     | -     | -     | P12   | -     | M2                    | -    | P27   | P106  | N2    |   |

| 1/0                      | 7    | P7    | P134  | E3    | P14   | 134   | I/O                   | 5    | -     | P103  | K4    |   |

| I/O                      | 7    | -     | P133  | E2    | P15   | 137   | I/O                   | 5    | -     | -     | -     |   |

| I/O                      | 7    | -     | -     | -     | P16   | 140   | I/O, V <sub>REF</sub> | 5    | P30   | P102  | L4    |   |

| I/O                      | 7    | -     | -     | -     | P17   | 143   | I/O                   | 5    | -     | P101  | M4    |   |

| I/O                      | 7    | -     | -     | -     | P18   | 146   | I/O                   | 5    | P31   | P100  | N4    |   |

| GND                      | -    | -     | -     | -     | P19   | -     | I/O                   | 5    | P32   | P99   | K5    |   |

| I/O, V <sub>REF</sub>    | 7    | P8    | P132  | E1    | P20   | 149   | GND                   | -    | -     | P98   | L5    |   |

| I/O                      | 7    | P9    | P131  | F4    | P21   | 152   | V <sub>CCO</sub>      | 5    | -     | -     | -     |   |

| I/O                      | 7    | -     | P130  | F3    | P22   | 155   | V <sub>CCINT</sub>    | -    | P33   | P97   | M5    |   |

| I/O                      | 7    | -     | -     | -     | P23   | 158   | I/O                   | 5    | -     | P96   | N5    |   |

| I/O, IRDY <sup>(1)</sup> | 7    | P10   | P129  | F2    | P24   | 161   | I/O                   | 5    | -     | P95   | K6    |   |

| GND                      | -    | P11   | P128  | F1    | P25   | -     | I/O                   | 5    | -     | -     | -     |   |

| V <sub>CCO</sub>         | 7    | P12   | P127  | G2    | P26   | -     | I/O                   | 5    | -     | -     | -     |   |

| V <sub>CCO</sub>         | 6    | P12   | P127  | G2    | P26   | -     | I/O                   | 5    | -     | -     | -     |   |

| I/O, TRDY <sup>(1)</sup> | 6    | P13   | P126  | G1    | P27   | 164   | GND                   | -    | -     | -     | -     |   |

| V <sub>CCINT</sub>       | -    | P14   | P125  | G3    | P28   | -     | I/O, V <sub>REF</sub> | 5    | P34   | P94   | L6    |   |

| I/O                      | 6    | -     | P124  | G4    | P29   | 170   | I/O                   | 5    | -     | -     | -     |   |

| I/O                      | 6    | P15   | P123  | H1    | P30   | 173   | I/O                   | 5    | -     | P93   | M6    |   |

| I/O, V <sub>REF</sub>    | 6    | P16   | P122  | H2    | P31   | 176   | V <sub>CCINT</sub>    | -    | P35   | P92   | N6    |   |

| GND                      | -    | -     | -     | -     | P32   | -     | I, GCK1               | 5    | P36   | P91   | M7    |   |

| I/O                      | 6    | -     | -     | -     | P33   | 179   | V <sub>CCO</sub>      | 5    | P37   | P90   | N7    |   |

| I/O                      | 6    | -     | -     | -     | P34   | 182   | V <sub>CCO</sub>      | 4    | P37   | P90   | N7    |   |

| I/O                      | 6    | -     | -     | -     | P35   | 185   | GND                   | -    | P38   | P89   | L7    |   |

| I/O                      | 6    | -     | P121  | H3    | P36   | 188   | I, GCK0               | 4    | P39   | P88   | K7    |   |

| I/O                      | 6    | P17   | P120  | H4    | P37   | 191   | I/O                   | 4    | P40   | P87   | N8    |   |

| V <sub>CCO</sub>         | 6    | -     | -     | -     | P39   | -     | I/O                   | 4    | -     | P86   | M8    |   |

| GND                      | -    | -     | P119  | J1    | P40   | -     | I/O                   | 4    | -     | -     | -     |   |

| I/O                      | 6    | P18   | P118  | J2    | P41   | 194   | I/O, V <sub>REF</sub> | 4    | P41   | P85   | L8    |   |

| I/O                      | 6    | P19   | P117  | J3    | P42   | 197   | GND                   | -    | -     | -     | -     |   |

| I/O                      | 6    | -     | P116  | J4    | P43   | 200   | I/O                   | 4    | -     | -     | -     |   |

## XC2S100 Device Pinouts (Continued)

| XC2S100 Pad<br>Name   |      |       |       |                             |                             | Bndry |

|-----------------------|------|-------|-------|-----------------------------|-----------------------------|-------|

| Function              | Bank | TQ144 | PQ208 | FG256                       | FG456                       | Scan  |

| I/O                   | 2    | -     | -     | F12                         | G20                         | 695   |

| I/O                   | 2    | -     | P149  | E15                         | F19                         | 701   |

| I/O, V <sub>REF</sub> | 2    | P41   | P150  | F13                         | F21                         | 704   |

| V <sub>CCO</sub>      | 2    | -     | -     | V <sub>CCO</sub><br>Bank 2* | V <sub>CCO</sub><br>Bank 2* | -     |

| GND                   | -    | -     | -     | GND*                        | GND*                        | -     |

| I/O                   | 2    | -     | P151  | E14                         | F20                         | 707   |

| I/O                   | 2    | -     | -     | C16                         | F18                         | 710   |

| I/O                   | 2    | -     | -     | -                           | E21                         | 713   |

| I/O                   | 2    | P40   | P152  | E13                         | D22                         | 716   |

| I/O                   | 2    | -     | -     | B16                         | E20                         | 719   |

| I/O (DIN,<br>D0)      | 2    | P39   | P153  | D14                         | D20                         | 725   |

| I/O (DOUT,<br>BUSY)   | 2    | P38   | P154  | C15                         | C21                         | 728   |

| CCLK                  | 2    | P37   | P155  | D15                         | B22                         | 731   |

| V <sub>CCO</sub>      | 2    | P36   | P156  | V <sub>CCO</sub><br>Bank 2* | V <sub>CCO</sub><br>Bank 2* | -     |

| V <sub>CCO</sub>      | 1    | P35   | P156  | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| TDO                   | 2    | P34   | P157  | B14                         | A21                         | -     |

| GND                   | -    | P33   | P158  | GND*                        | GND*                        | -     |

| TDI                   | -    | P32   | P159  | A15                         | B20                         | -     |

| I/O (CS)              | 1    | P31   | P160  | B13                         | C19                         | 0     |

| I/O (WRITE)           | 1    | P30   | P161  | C13                         | A20                         | 3     |

| I/O                   | 1    | -     | -     | C12                         | D17                         | 9     |

| I/O                   | 1    | P29   | P162  | A14                         | A19                         | 12    |

| I/O                   | 1    | -     | -     | -                           | B18                         | 15    |

| I/O                   | 1    | -     | -     | D12                         | C17                         | 18    |

| I/O                   | 1    | -     | P163  | B12                         | D16                         | 21    |

| GND                   | -    | -     | -     | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 1    | -     | -     | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| I/O, V <sub>REF</sub> | 1    | P28   | P164  | C11                         | A18                         | 24    |

| I/O                   | 1    | -     | P165  | A13                         | B17                         | 27    |

| I/O                   | 1    | -     | -     | D11                         | D15                         | 33    |

| I/O                   | 1    | -     | P166  | A12                         | C16                         | 36    |

| I/O                   | 1    | -     | -     | -                           | D14                         | 39    |

| I/O, V <sub>REF</sub> | 1    | P27   | P167  | E11                         | E14                         | 42    |

| I/O                   | 1    | P26   | P168  | B11                         | A16                         | 45    |

| GND                   | -    | P25   | P169  | GND*                        | GND*                        | -     |

## XC2S100 Device Pinouts (Continued)

| XC2S100 Pad<br>Name   |               |     |       |                             |                             | Bndry |

|-----------------------|---------------|-----|-------|-----------------------------|-----------------------------|-------|

| Function              | Function Bank |     | PQ208 | FG256                       | FG456                       | Scan  |

| V <sub>CCO</sub>      | 1             | -   | P170  | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| V <sub>CCINT</sub>    | -             | P24 | P171  | V <sub>CCINT</sub> *        | V <sub>CCINT</sub> *        | -     |

| I/O                   | 1             | P23 | P172  | A11                         | C15                         | 48    |

| I/O                   | 1             | P22 | P173  | C10                         | B15                         | 51    |

| I/O                   | 1             | -   | -     | -                           | F12                         | 54    |

| I/O                   | 1             | -   | P174  | B10                         | C14                         | 57    |

| I/O                   | 1             | -   | P175  | D10                         | D13                         | 63    |

| I/O                   | 1             | -   | P176  | A10                         | C13                         | 66    |

| GND                   | -             | -   | P177  | GND*                        | GND*                        | -     |

| I/O, V <sub>REF</sub> | 1             | P21 | P178  | B9                          | B13                         | 69    |

| I/O                   | 1             | -   | P179  | E10                         | E12                         | 72    |

| I/O                   | 1             | -   | -     | A9                          | B12                         | 75    |

| I/O                   | 1             | P20 | P180  | D9                          | D12                         | 78    |

| I/O                   | 1             | P19 | P181  | A8                          | D11                         | 84    |

| I, GCK2               | 1             | P18 | P182  | C9                          | A11                         | 90    |

| GND                   | -             | P17 | P183  | GND*                        | GND*                        | -     |

| V <sub>CCO</sub>      | 1             | P16 | P184  | V <sub>CCO</sub><br>Bank 1* | V <sub>CCO</sub><br>Bank 1* | -     |

| V <sub>CCO</sub>      | 0             | P16 | P184  | V <sub>CCO</sub><br>Bank 0* | V <sub>CCO</sub><br>Bank 0* | -     |

| I, GCK3               | 0             | P15 | P185  | B8                          | C11                         | 91    |

| V <sub>CCINT</sub>    | -             | P14 | P186  | V <sub>CCINT</sub> *        | $V_{CCINT}^{*}$             | -     |

| I/O                   | 0             | P13 | P187  | A7                          | A10                         | 101   |

| I/O                   | 0             | -   | -     | D8                          | B10                         | 104   |

## XC2S150 Device Pinouts (Continued)

| XC2S150 Pad Name      |               |     |                             |                             | Pndry         |

|-----------------------|---------------|-----|-----------------------------|-----------------------------|---------------|

| Function              | Function Bank |     | FG256                       | FG456                       | Bndry<br>Scan |

| I/O                   | 6             | P46 | P1                          | T4                          | 404           |

| I/O                   | 6             | -   | L5                          | W1                          | 407           |

| I/O                   | 6             | -   | -                           | V2                          | 410           |

| I/O                   | 6             | -   | -                           | U4                          | 413           |

| I/O                   | 6             | P47 | N2                          | Y1                          | 416           |

| GND                   | -             | -   | GND*                        | GND*                        | -             |

| I/O                   | 6             | -   | M4                          | W2                          | 419           |

| I/O                   | 6             | -   | -                           | V3                          | 422           |

| I/O                   | 6             | -   | -                           | V4                          | 425           |

| I/O                   | 6             | P48 | R1                          | Y2                          | 428           |

| I/O                   | 6             | P49 | M3                          | W3                          | 431           |

| M1                    | -             | P50 | P2                          | U5                          | 434           |

| GND                   | -             | P51 | GND*                        | GND*                        | -             |

| MO                    | -             | P52 | N3                          | AB2                         | 435           |

| V <sub>CCO</sub>      | 6             | P53 | V <sub>CCO</sub><br>Bank 6* | V <sub>CCO</sub><br>Bank 6* | -             |