Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | C166SV2                                                                           |

| Core Size                  | 16/32-Bit                                                                         |

| Speed                      | 128MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI              |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                   |

| Number of I/O              | 75                                                                                |

| Program Memory Size        | 576KB (576K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 98K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                         |

| Data Converters            | A/D 16x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-100-8                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2361e72f128laakxuma1 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2014-06 Published by Infineon Technologies AG 81726 Munich, Germany © 2014 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Table | e 6 Pin De        | finition   | is and | Functions (cont'd)                                                                                                                                                                 |

|-------|-------------------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin   | Symbol            | Ctrl.      | Туре   | Function                                                                                                                                                                           |

| 6     | P7.0              | O0 / I     | St/B   | Bit 0 of Port 7, General Purpose Input/Output                                                                                                                                      |

|       | T3OUT             | 01         | St/B   | GPT12E Timer T3 Toggle Latch Output                                                                                                                                                |

|       | T6OUT             | O2         | St/B   | GPT12E Timer T6 Toggle Latch Output                                                                                                                                                |

|       | TDO_A             | OH /<br>IH | St/B   | JTAG Test Data Output / DAP1 Input/Output<br>If DAP pos. 0 or 2 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |

|       | ESR2_1            | I          | St/B   | ESR2 Trigger Input 1                                                                                                                                                               |

| 7     | P7.3              | O0 / I     | St/B   | Bit 3 of Port 7, General Purpose Input/Output                                                                                                                                      |

|       | EMUX1             | 01         | St/B   | External Analog MUX Control Output 1 (ADC1)                                                                                                                                        |

|       | U0C1_DOUT         | O2         | St/B   | USIC0 Channel 1 Shift Data Output                                                                                                                                                  |

|       | U0C0_DOUT         | O3         | St/B   | USIC0 Channel 0 Shift Data Output                                                                                                                                                  |

|       | CCU62_CCP<br>OS1A | I          | St/B   | CCU62 Position Input 1                                                                                                                                                             |

|       | TMS_C             | IH         | St/B   | JTAG Test Mode Selection Input<br>If JTAG pos. C is selected during start-up, an<br>internal pull-up device will hold this pin low when<br>nothing is driving it.                  |

|       | U0C1_DX0F         | I          | St/B   | USIC0 Channel 1 Shift Data Input                                                                                                                                                   |

| Pin | Symbol            | Ctrl.      | Туре | Function                                          |

|-----|-------------------|------------|------|---------------------------------------------------|

| 41  | P2.2              | 00/1       | -    | Bit 2 of Port 2, General Purpose Input/Output     |

|     | TxDC1             | 01         | St/B | CAN Node 1 Transmit Data Output                   |

|     | CCU63_CC6<br>2    | O2         | St/B | CCU63 Channel 2 Output                            |

|     | AD15              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 15       |

|     | CCU63_CC6<br>2INB | l          | St/B | CCU63 Channel 2 Input                             |

|     | ESR2_5            | I          | St/B | ESR2 Trigger Input 5                              |

|     | ERU_1A0           | I          | St/B | External Request Unit Channel 1 Input A0          |

| 42  | P4.0              | O0 / I     | St/B | Bit 0 of Port 4, General Purpose Input/Output     |

|     | CC2_CC24          | O3 / I     | St/B | CAPCOM2 CC24IO Capture Inp./ Compare Out.         |

|     | CS0               | ОН         | St/B | External Bus Interface Chip Select 0 Output       |

| 43  | P2.3              | O0 / I     | St/B | Bit 3 of Port 2, General Purpose Input/Output     |

|     | U0C0_DOUT         | 01         | St/B | USIC0 Channel 0 Shift Data Output                 |

|     | CCU63_COU<br>T63  | O2         | St/B | CCU63 Channel 3 Output                            |

|     | CC2_CC16          | O3 / I     | St/B | CAPCOM2 CC16IO Capture Inp./ Compare Out.         |

|     | A16               | ОН         | St/B | External Bus Interface Address Line 16            |

|     | ESR2_0            | I          | St/B | ESR2 Trigger Input 0                              |

|     | U0C0_DX0E         | I          | St/B | USIC0 Channel 0 Shift Data Input                  |

|     | U0C1_DX0D         | I          | St/B | USIC0 Channel 1 Shift Data Input                  |

|     | RxDC0A            | I          | St/B | CAN Node 0 Receive Data Input                     |

| 44  | P4.1              | O0 / I     | St/B | Bit 1 of Port 4, General Purpose Input/Output     |

|     | TxDC2             | O2         | St/B | CAN Node 2 Transmit Data Output                   |

|     | CC2_CC25          | O3 / I     | St/B | CAPCOM2 CC25IO Capture Inp./ Compare Out.         |

|     | CS1               | ОН         | St/B | External Bus Interface Chip Select 1 Output       |

|     | CCU62_CCP<br>OS0B | I          | St/B | CCU62 Position Input 0                            |

|     | T4EUDB            | I          | St/B | GPT12E Timer T4 External Up/Down Control<br>Input |

|     | ESR1_8            | 1          | St/B | ESR1 Trigger Input 8                              |

| Table | Table 6Pin Definitions and Functions (cont'd) |            |      |                                                                                                                                                                                                                                                                                                      |  |  |

|-------|-----------------------------------------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin   | Symbol                                        | Ctrl.      | Туре | Function                                                                                                                                                                                                                                                                                             |  |  |

| 80    | P10.9                                         | O0 / I     | DP/B | Bit 9 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                       |  |  |

|       | U0C0_SELO<br>4                                | 01         | DP/B | USIC0 Channel 0 Select/Control 4 Output                                                                                                                                                                                                                                                              |  |  |

|       | U0C1_MCLK<br>OUT                              | O2         | DP/B | USIC0 Channel 1 Master Clock Output                                                                                                                                                                                                                                                                  |  |  |

|       | AD9                                           | OH /<br>IH | DP/B | External Bus Interface Address/Data Line 9                                                                                                                                                                                                                                                           |  |  |

|       | CCU60_CCP<br>OS2A                             | I          | DP/B | CCU60 Position Input 2                                                                                                                                                                                                                                                                               |  |  |

|       | TCK_B                                         | IH         | DP/B | <b>DAP0/JTAG Clock Input</b><br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.<br>If DAP pos. 1 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |  |  |

|       | T3INB                                         | I          | DP/B | GPT12E Timer T3 Count/Gate Input                                                                                                                                                                                                                                                                     |  |  |

| 81    | P1.1                                          | O0 / I     | St/B | Bit 1 of Port 1, General Purpose Input/Output                                                                                                                                                                                                                                                        |  |  |

|       | CCU62_COU<br>T62                              | 01         | St/B | CCU62 Channel 2 Output                                                                                                                                                                                                                                                                               |  |  |

|       | U1C0_SELO<br>5                                | 02         | St/B | USIC1 Channel 0 Select/Control 5 Output                                                                                                                                                                                                                                                              |  |  |

|       | U2C1_DOUT                                     | O3         | St/B | USIC2 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                    |  |  |

|       | A9                                            | ОН         | St/B | External Bus Interface Address Line 9                                                                                                                                                                                                                                                                |  |  |

|       | ESR2_3                                        | I          | St/B | ESR2 Trigger Input 3                                                                                                                                                                                                                                                                                 |  |  |

|       | ERU_1B0                                       | I          | St/B | External Request Unit Channel 1 Input B0                                                                                                                                                                                                                                                             |  |  |

|       | U2C1_DX0C                                     | I          | St/B | USIC2 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                     |  |  |

| Table 6         Pin Definitions and Fund |                  |        |      | Functions (cont'd)                                                                                                                                                                 |

|------------------------------------------|------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin                                      | Symbol           | Ctrl.  | Туре | Function                                                                                                                                                                           |

| 86                                       | P10.13           | O0 / I | St/B | Bit 13 of Port 10, General Purpose Input/Output                                                                                                                                    |

|                                          | U1C0_DOUT        | O1     | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                                                  |

|                                          | U1C0_SELO<br>3   | O3     | St/B | USIC1 Channel 0 Select/Control 3 Output                                                                                                                                            |

|                                          | WR/WRL           | ОН     | St/B | <b>External Bus Interface Write Strobe Output</b><br>Active for each external write access, when $\overline{WR}$ , active for ext. writes to the low byte, when $\overline{WRL}$ . |

|                                          | U1C0_DX0D        | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                   |

| 87                                       | P1.3             | O0 / I | St/B | Bit 3 of Port 1, General Purpose Input/Output                                                                                                                                      |

|                                          | CCU62_COU<br>T63 | O1     | St/B | CCU62 Channel 3 Output                                                                                                                                                             |

|                                          | U1C0_SELO<br>7   | O2     | St/B | USIC1 Channel 0 Select/Control 7 Output                                                                                                                                            |

|                                          | U2C0_SELO<br>4   | O3     | St/B | USIC2 Channel 0 Select/Control 4 Output                                                                                                                                            |

|                                          | A11              | ОН     | St/B | External Bus Interface Address Line 11                                                                                                                                             |

|                                          | ESR2_4           | I      | St/B | ESR2 Trigger Input 4                                                                                                                                                               |

|                                          | ERU_3A0          | I      | St/B | External Request Unit Channel 3 Input A0                                                                                                                                           |

|                                          | CCU62_T12<br>HRB | I      | St/B | External Run Control Input for T12 of CCU62                                                                                                                                        |

| 89                                       | P10.14           | O0 / I | St/B | Bit 14 of Port 10, General Purpose Input/Output                                                                                                                                    |

|                                          | U1C0_SELO<br>1   | O1     | St/B | USIC1 Channel 0 Select/Control 1 Output                                                                                                                                            |

|                                          | U0C1_DOUT        | 02     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                  |

|                                          | RD               | OH     | St/B | External Bus Interface Read Strobe Output                                                                                                                                          |

|                                          | ESR2_2           | I      | St/B | ESR2 Trigger Input 2                                                                                                                                                               |

|                                          | U0C1_DX0C        | I      | St/B | USIC0 Channel 1 Shift Data Input                                                                                                                                                   |

The RTC module can be used for different purposes:

- System clock to determine the current time and date

- Cyclic time-based interrupt, to provide a system time tick independent of CPU frequency and other resources

- 48-bit timer for long-term measurements

- Alarm interrupt at a defined time

## **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- UART (asynchronous serial channel)

- module capability: maximum baud rate =  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- module capability: maximum baud rate =  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI (synchronous serial channel with or without data buffer)

- module capability: maximum baud rate =  $f_{SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- IIS (Inter-IC Sound Bus)

- module capability: maximum baud rate =  $f_{SYS}$  / 2

- Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

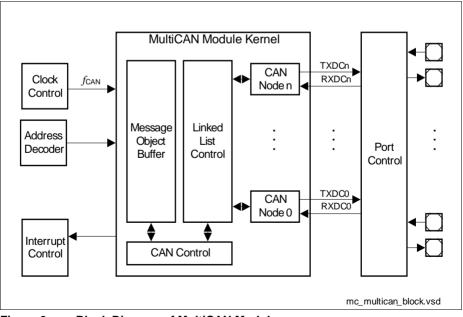

# 3.14 MultiCAN Module

The MultiCAN module contains independently operating CAN nodes with Full-CAN functionality which are able to exchange Data and Remote Frames using a gateway function. Transmission and reception of CAN frames is handled in accordance with CAN specification V2.0 B (active). Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

All CAN nodes share a common set of message objects. Each message object can be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects can be combined to build gateways between the CAN nodes or to set up a FIFO buffer.

Note: The number of CAN nodes and message objects depends on the selected device type.

The message objects are organized in double-chained linked lists, where each CAN node has its own list of message objects. A CAN node stores frames only into message objects that are allocated to its own message object list and it transmits only messages belonging to this message object list. A powerful, command-driven list controller performs all message object list operations.

Figure 9 Block Diagram of MultiCAN Module

The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

# 3.17 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XC236xE from a number of external or internal clock sources:

- External clock signals with pad voltage or core voltage levels

- External crystal or resonator using the on-chip oscillator

- On-chip clock source for operation without crystal/resonator

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals, a clock input signal, or from the on-chip clock source. See also **Section 4.7.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

# 3.18 Parallel Ports

The XC236xE provides up to 76 I/O lines which are organized into 7 input/output ports and 2 input ports. All port lines are bit-addressable, and all input/output lines can be individually (bit-wise) configured via port control registers. This configuration selects the direction (input/output), push/pull or open-drain operation, activation of pull devices, and edge characteristics (shape) and driver characteristics (output current) of the port drivers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. During the internal reset, all port pins are configured as inputs without pull devices active.

All port lines have alternate input or output functions associated with them. These alternate functions can be programmed to be assigned to various port pins to support the best utilization for a given application. For this reason, certain functions appear several times in **Table 10**.

All port lines that are not used for alternate functions may be used as general purpose I/O lines.

| Port | Width | I/O | Connected Modules                                                               |

|------|-------|-----|---------------------------------------------------------------------------------|

| P0   | 8     | I/O | EBC (A7A0), CCU6, USIC, CAN                                                     |

| P1   | 8     | I/O | EBC (A15A8), CCU6, USIC                                                         |

| P2   | 14    | I/O | EBC (READY, BHE, A23A16, AD15AD13, D15D13),<br>CAN, CC2, GPT12E, USIC, DAP/JTAG |

| P4   | 4     | I/O | EBC (CS3CS0), CC2, CAN, GPT12E, USIC                                            |

| P5   | 11    | I   | Analog Inputs, CCU6, DAP/JTAG, GPT12E, CAN                                      |

| P6   | 3     | I/O | ADC, CAN, GPT12E                                                                |

| P7   | 5     | I/O | CAN, GPT12E, SCU, DAP/JTAG, CCU6, ADC, USIC                                     |

| P10  | 16    | I/O | EBC (ALE, RD, WR, AD12AD0, D12D0), CCU6, USIC, DAP/JTAG, CAN                    |

| P15  | 5     | I   | Analog Inputs, GPT12E                                                           |

## Table 10 Summary of the XC236xE's Ports

| Table 11 I | ruction Set Summary (cont'd)                                                             |       |  |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------|-------|--|--|--|--|--|--|

| Mnemonic   | Description                                                                              | Bytes |  |  |  |  |  |  |

| ROL/ROR    | Rotate left/right direct word GPR                                                        | 2     |  |  |  |  |  |  |

| ASHR       | Arithmetic (sign bit) shift right direct word GPR                                        | 2     |  |  |  |  |  |  |

| MOV(B)     | Move word (byte) data                                                                    | 2/4   |  |  |  |  |  |  |

| MOVBS/Z    | Move byte operand to word op. with sign/zero extension                                   | 2/4   |  |  |  |  |  |  |

| JMPA/I/R   | Jump absolute/indirect/relative if condition is met                                      | 4     |  |  |  |  |  |  |

| JMPS       | Jump absolute to a code segment                                                          | 4     |  |  |  |  |  |  |

| JB(C)      | Jump relative if direct bit is set (and clear bit)                                       | 4     |  |  |  |  |  |  |

| JNB(S)     | Jump relative if direct bit is not set (and set bit)                                     | 4     |  |  |  |  |  |  |

| CALLA/I/R  | Call absolute/indirect/relative subroutine if condition is met                           | 4     |  |  |  |  |  |  |

| CALLS      | Call absolute subroutine in any code segment                                             | 4     |  |  |  |  |  |  |

| PCALL      | Push direct word register onto system stack and call absolute subroutine                 | 4     |  |  |  |  |  |  |

| TRAP       | Call interrupt service routine via immediate trap number                                 | 2     |  |  |  |  |  |  |

| PUSH/POP   | Push/pop direct word register onto/from system stack                                     | 2     |  |  |  |  |  |  |

| SCXT       | Push direct word register onto system stack and update register with word operand        | 4     |  |  |  |  |  |  |

| RET(P)     | Return from intra-segment subroutine<br>(and pop direct word register from system stack) | 2     |  |  |  |  |  |  |

| RETS       | Return from inter-segment subroutine                                                     | 2     |  |  |  |  |  |  |

| RETI       | Return from interrupt service subroutine                                                 | 2     |  |  |  |  |  |  |

| SBRK       | Software Break                                                                           | 2     |  |  |  |  |  |  |

| SRST       | Software Reset                                                                           | 4     |  |  |  |  |  |  |

| IDLE       | Enter Idle Mode                                                                          | 4     |  |  |  |  |  |  |

| PWRDN      | Unused instruction <sup>1)</sup>                                                         | 4     |  |  |  |  |  |  |

| SRVWDT     | Service Watchdog Timer                                                                   | 4     |  |  |  |  |  |  |

| DISWDT/ENW | DT Disable/Enable Watchdog Timer                                                         | 4     |  |  |  |  |  |  |

| EINIT      | End-of-Initialization Register Lock                                                      | 4     |  |  |  |  |  |  |

| ATOMIC     | Begin ATOMIC sequence                                                                    | 2     |  |  |  |  |  |  |

| EXTR       | Begin EXTended Register sequence                                                         | 2     |  |  |  |  |  |  |

| EXTP(R)    | Begin EXTended Page (and Register) sequence                                              | 2/4   |  |  |  |  |  |  |

| EXTS(R)    | Begin EXTended Segment (and Register) sequence                                           | 2/4   |  |  |  |  |  |  |

#### Table 11 Instruction Set Summary (cont'd)

# 4.1.3 Voltage Range Definition

The XC236xE timing depends on the supply voltage. If such a dependency exists the timing values are given for 2 voltage areas commonly used. The voltage areas are defined in the following tables.

### Table 14 Upper Voltage Range Definition

| Parameter                         | Symbol                |      | Values |      | Unit | Note /                           |

|-----------------------------------|-----------------------|------|--------|------|------|----------------------------------|

|                                   |                       | Min. | Тур.   | Max. |      | Test Condition                   |

| Digital supply voltage for        | $V_{\rm DDP}{\rm SR}$ | 4.5  | 5      | 5.5  | V    | $f_{\rm SYS} \le 100 \; \rm MHz$ |

| IO pads and voltage<br>regulators |                       | 4.75 | 5      | 5.25 | V    | f <sub>SYS</sub> ≤ 128 MHz       |

# Table 15 Lower Voltage Range Definition

| Parameter                                                       | Symbol               | Values |      |      | Unit | Note /         |

|-----------------------------------------------------------------|----------------------|--------|------|------|------|----------------|

|                                                                 |                      | Min.   | Тур. | Max. |      | Test Condition |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$ | 3.0    | 3.3  | 4.5  | V    |                |

# 4.1.4 Pad Timing Definition

If not otherwise noted, all timing parameters are tested and are valid for the corresponding output pins operating in strong driver, fast edge mode. See also "Pad Properties" on Page 106.

## 4.1.5 Parameter Interpretation

The parameters listed in the following include both the characteristics of the XC236xE and its demands on the system. To aid in correctly interpreting the parameters when evaluating them for a design, they are marked accordingly in the column "Symbol":

**CC** (Controller Characteristics):

The logic of the XC236xE provides signals with the specified characteristics.

SR (System Requirement):

The external system must provide signals with the specified characteristics to the XC236xE.

# 4.2.1 DC Parameters for Upper Voltage Area

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{OV}$ .

Note: Operating Conditions apply.

Table 16 is valid under the following conditions:

$V_{\text{DDP}} \ge 4.5 \text{ V}; V_{\text{DDPtvp}} = 5 \text{ V}; V_{\text{DDP}} \le 5.5 \text{ V}$

| Parameter                                                                                   | Symbol                   |                            | Values |                           | Unit | Note /                                                                                             |

|---------------------------------------------------------------------------------------------|--------------------------|----------------------------|--------|---------------------------|------|----------------------------------------------------------------------------------------------------|

|                                                                                             |                          | Min.                       | Тур.   | Max.                      |      | Test Condition                                                                                     |

| Pin capacitance (digital inputs/outputs). To be doubled for double bond pins. <sup>1)</sup> | C <sub>IO</sub> CC       | _                          | _      | 10                        | pF   | not subject to<br>production test                                                                  |

| Input Hysteresis <sup>2)</sup>                                                              | HYS CC                   | 0.11 x<br>V <sub>DDP</sub> | _      | _                         | V    | $R_{\rm S} = 0 \ \Omega$                                                                           |

| Absolute input leakage current on pins of analog ports <sup>3)</sup>                        | I <sub>OZ1</sub>  <br>CC | -                          | 10     | 200                       | nA   | $V_{\rm IN}$ > 0 V;<br>$V_{\rm IN}$ < $V_{\rm DDP}$                                                |

| Absolute input leakage<br>current for all other pins.<br>To be doubled for double           | I <sub>OZ2</sub>  <br>CC | _                          | 0.2    | 5                         | μΑ   | $T_{\rm J} \leq 110 ~^{\rm o}{\rm C};$<br>$V_{\rm IN} < V_{\rm DDP};$<br>$V_{\rm IN} > V_{\rm SS}$ |

| bond pins. <sup>3)1)4)</sup>                                                                |                          | _                          | 0.2    | 15                        | μΑ   | $T_{\rm J} \leq 150 ~^{\circ}{\rm C};$<br>$V_{\rm IN} < V_{\rm DDP};$<br>$V_{\rm IN} > V_{\rm SS}$ |

| Pull Level Force Current <sup>5)</sup>                                                      | $ I_{PLF} $ SR           | 250                        | -      | -                         | μA   | 6)                                                                                                 |

| Pull Level Keep Current <sup>7)</sup>                                                       | I <sub>PLK</sub>  <br>SR | -                          | -      | 30                        | μA   | 6)                                                                                                 |

| Input high voltage<br>(all except XTAL1)                                                    | $V_{\rm IH}{\rm SR}$     | 0.7 х<br>V <sub>DDP</sub>  | -      | V <sub>DDP</sub><br>+ 0.3 | V    |                                                                                                    |

| Input low voltage<br>(all except XTAL1)                                                     | $V_{\rm IL}{ m SR}$      | -0.3                       | -      | 0.3 x<br>V <sub>DDP</sub> | V    |                                                                                                    |

| Output High voltage <sup>8)</sup>                                                           | V <sub>OH</sub> CC       | V <sub>DDP</sub><br>- 1.0  | -      | -                         | V    | $I_{\rm OH} \ge I_{\rm OHmax}$                                                                     |

|                                                                                             |                          | V <sub>DDP</sub><br>- 0.4  | -      | -                         | V    | $I_{\rm OH} \ge I_{\rm OHnom}^{9)}$                                                                |

## Table 16 DC Characteristics for Upper Voltage Range

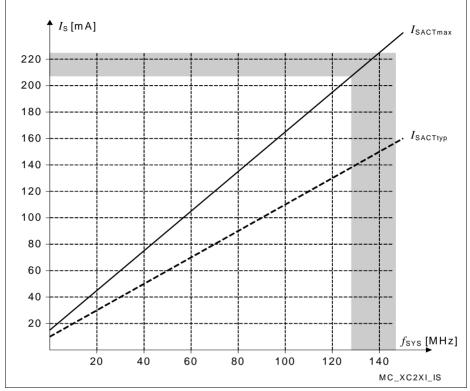

Figure 11 Supply Current in Active Mode as a Function of Frequency

Note: Operating Conditions apply.

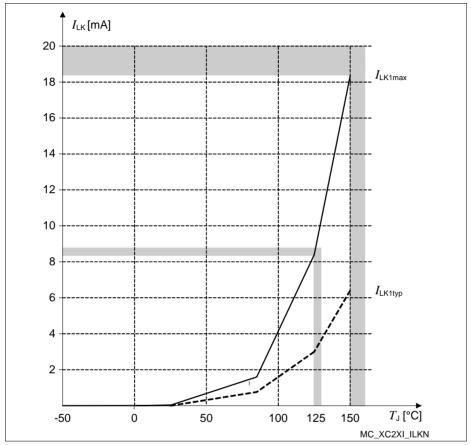

Figure 12 Leakage Supply Current as a Function of Temperature

Sample time and conversion time of the XC236xE's A/D converters are programmable. The timing above can be calculated using Table 23.

The limit values for  $f_{ADCI}$  must not be exceeded when selecting the prescaler value.

| GLOBCTR.5-0<br>(DIVA) | A/D Converter Analog Clock $f_{\text{ADCI}}$ | INPCRx.7-0<br>(STC) | Sample Time <sup>1)</sup><br>t <sub>s</sub> |

|-----------------------|----------------------------------------------|---------------------|---------------------------------------------|

| 000000 <sub>B</sub>   | f <sub>SYS</sub>                             | 00 <sub>H</sub>     | $t_{ADCI} \times 2$                         |

| 000001 <sub>B</sub>   | f <sub>SYS</sub> / 2                         | 01 <sub>H</sub>     | $t_{ADCI} \times 3$                         |

| 000010 <sub>B</sub>   | f <sub>SYS</sub> / 3                         | 02 <sub>H</sub>     | $t_{ADCI} \times 4$                         |

| :                     | $f_{\rm SYS}$ / (DIVA+1)                     | :                   | $t_{ADCI} \times (STC+2)$                   |

| 111110 <sub>B</sub>   | f <sub>SYS</sub> / 63                        | FE <sub>H</sub>     | $t_{ADCI} \times 256$                       |

| 111111 <sub>B</sub>   | f <sub>SYS</sub> / 64                        | FF <sub>H</sub>     | $t_{ADCI} \times 257$                       |

Table 23

A/D Converter Computation Table

1) The selected sample time is doubled if broken wire detection is active (due to the presampling phase).

## **Converter Timing Example A:**

| Assumptions:                | $f_{\rm SYS}$           | = 128 MHz (i.e. $t_{SYS}$ = 7.8 ns), DIVA = 06 <sub>H</sub> , STC = 00 <sub>H</sub>              |  |  |  |  |

|-----------------------------|-------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| Analog clock                | $f_{\rm ADCI}$          | $= f_{SYS} / 7 = 18.3 \text{ MHz}$ , i.e. $t_{ADCI} = 54.7 \text{ ns}$                           |  |  |  |  |

| Sample time                 | t <sub>S</sub>          | $= t_{ADCI} \times 2 = 109.4 \text{ ns}$                                                         |  |  |  |  |

| Conversion 12-b             | oit:                    |                                                                                                  |  |  |  |  |

|                             | <i>t</i> <sub>C10</sub> | = $16 \times t_{ADCI}$ + 2 × $t_{SYS}$ = 16 × 54.7 ns + 2 × 7.8 ns = 0.891 µs                    |  |  |  |  |

| Conversion 10-b             | Conversion 10-bit:      |                                                                                                  |  |  |  |  |

|                             | t <sub>C8</sub>         | = $12 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $12 \times 54.7$ ns + $2 \times 7.8$ ns = 0.672 µs |  |  |  |  |

| Converter Timing Example B: |                         |                                                                                                  |  |  |  |  |

| Assumptions:   | $f_{\rm SYS}$           | = 40 MHz (i.e. $t_{SYS}$ = 25 ns), DIVA = 02 <sub>H</sub> , STC = 03 <sub>H</sub>                  |

|----------------|-------------------------|----------------------------------------------------------------------------------------------------|

| Analog clock   | $f_{\rm ADCI}$          | $= f_{SYS} / 3 = 13.3 \text{ MHz}$ , i.e. $t_{ADCI} = 75 \text{ ns}$                               |

| Sample time    | t <sub>S</sub>          | $= t_{ADCI} \times 5 = 375 \text{ ns}$                                                             |

| Conversion 12- | bit:                    |                                                                                                    |

|                | <i>t</i> <sub>C10</sub> | = $19 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $19 \times 75$ ns + $2 \times 25$ ns = 1.475 $\mu$ s |

| Conversion 10- | bit:                    |                                                                                                    |

|                | t <sub>C8</sub>         | = $15 \times t_{ADCI}$ + 2 × $t_{SYS}$ = 15 × 75 ns + 2 × 25 ns = 1.175 µs                         |

|                |                         |                                                                                                    |

# 4.5 Flash Memory Parameters

The XC236xE is delivered with all Flash sectors erased and with no protection installed. The data retention time of the XC236xE's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                                  | Symbol                   | Values |                 |                 | Unit       | Note /                                                  |

|------------------------------------------------------------|--------------------------|--------|-----------------|-----------------|------------|---------------------------------------------------------|

|                                                            |                          | Min.   | Тур.            | Max.            |            | Test Condition                                          |

| Parallel Flash module                                      | $N_{\rm PP}{\rm SR}$     | -      | -               | 5 <sup>1)</sup> |            | $N_{\rm FL_RD} \leq 1$                                  |

| program/erase limit<br>depending on Flash read<br>activity |                          | -      | -               | 1 <sup>2)</sup> |            | $N_{\rm FL_RD}$ > 1                                     |

| Flash erase endurance for security pages                   | $N_{\rm SEC}{ m SR}$     | 10     | -               | -               | cycle<br>s | $t_{RET} \ge 20$ years                                  |

| Flash wait states <sup>3)</sup>                            | $N_{\rm WSFLAS}$         | 1      | -               | -               |            | $f_{SYS} \le 8 \text{ MHz}$                             |

|                                                            | <sub>H</sub> SR          | 2      | -               | -               |            | $f_{SYS} \le 13 \text{ MHz}$                            |

|                                                            |                          | 3      | -               | -               |            | $f_{\rm SYS} \le$ 17 MHz                                |

|                                                            |                          | 4      | -               | -               |            | $f_{\rm SYS}$ > 17 MHz                                  |

| Flash wait state                                           | N <sub>WSFLE</sub><br>SR | 0      | -               | -               |            | $f_{\rm SYS} \le$ 80 MHz                                |

| extension <sup>4)</sup>                                    |                          | 1      | -               | -               |            | $f_{\rm SYS}$ > 80 MHz;<br>$f_{\rm SYS}$ $\leq$ 128 MHz |

| Erase time per<br>sector/page                              | t <sub>ER</sub> CC       | _      | 7 <sup>5)</sup> | 8.0             | ms         |                                                         |

| Programming time per page                                  | t <sub>PR</sub> CC       | _      | 3 <sup>5)</sup> | 3.5             | ms         |                                                         |

| Data retention time                                        | t <sub>RET</sub> CC      | 20     | -               | -               | year<br>s  | $N_{\rm Er} \le 1\ 000$ cycles                          |

| Drain disturb limit                                        | $N_{\rm DD}{ m SR}$      | 32     | -               | -               | cycle<br>s |                                                         |

### Table 27 Flash Parameters

Note: The term CLKOUT refers to the reference clock output signal which is generated by selecting  $f_{SYS}$  as the source signal for the clock output signal EXTCLK on pin P2.8 and by enabling the high-speed clock driver on this pin.

### Variable Memory Cycles

External bus cycles of the XC236xE are executed in five consecutive cycle phases (AB, C, D, E, F). The duration of each cycle phase is programmable (via the TCONCSx registers) to adapt the external bus cycles to the respective external module (memory, peripheral, etc.).

The duration of the access phase can optionally be controlled by the external module using the READY handshake input.

This table provides a summary of the phases and the ranges for their length.

| Table 33 | Programmable Bus C | vcle Phases ( | (see timing | diagrams) |

|----------|--------------------|---------------|-------------|-----------|

|          |                    |               |             |           |

| Bus Cycle Phase                                                                                                                                | Parameter | Valid Values | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|------|

| Address setup phase, the standard duration of this phase (1 $\dots$ 2 TCS) can be extended by 0 $\dots$ 3 TCS if the address window is changed | tpAB      | 1 2 (5)      | TCS  |

| Command delay phase                                                                                                                            | tpC       | 03           | TCS  |

| Write Data setup/MUX Tristate phase                                                                                                            | tpD       | 0 1          | TCS  |

| Access phase                                                                                                                                   | tpE       | 1 32         | TCS  |

| Address/Write Data hold phase                                                                                                                  | tpF       | 0 3          | TCS  |

Note: The bandwidth of a parameter (from minimum to maximum value) covers the whole operating range (temperature, voltage) as well as process variations. Within a given device, however, this bandwidth is smaller than the specified range. This is also due to interdependencies between certain parameters. Some of these interdependencies are described in additional notes (see standard timing).

Note: Operating Conditions apply;  $C_L = 20 \text{ pF}$ .

## Table 39 USIC SSC Slave Mode Timing for Lower Voltage Range

|                                                                                   |                           |        | •    |      | •    | 0              |

|-----------------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

| Parameter                                                                         | Symbol                    | Values |      |      | Unit | Note /         |

|                                                                                   |                           | Min.   | Тур. | Max. |      | Test Condition |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>       | <i>t</i> <sub>10</sub> SR | 7      | -    | -    | ns   |                |

| Select input DX2 hold after<br>last clock input DX1<br>receive edge <sup>1)</sup> | <i>t</i> <sub>11</sub> SR | 7      | -    | -    | ns   |                |

| Receive data input setup<br>time to shift clock receive<br>edge <sup>1)</sup>     | <i>t</i> <sub>12</sub> SR | 7      | -    | -    | ns   |                |

| Data input DX0 hold time<br>from clock input DX1<br>receive edge <sup>1)</sup>    | <i>t</i> <sub>13</sub> SR | 5      | -    | -    | ns   |                |

| Data output DOUT valid time                                                       | <i>t</i> <sub>14</sub> CC | 8      | -    | 41   | ns   |                |

1) These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

## Package and Reliability

# 5.3 Quality Declarations

The operation lifetime of the XC236xE depends on the applied temperature profile in the application. For a typical example, please refer to **Table 46**; for other profiles, please contact your Infineon counterpart to calculate the specific lifetime within your application.

| Table 45 | Quality Parameters |

|----------|--------------------|

|----------|--------------------|

| Parameter                                                    | Symbol             | Values |      |       | Unit | Note /                       |

|--------------------------------------------------------------|--------------------|--------|------|-------|------|------------------------------|

|                                                              |                    | Min.   | Тур. | Max.  |      | Test Condition               |

| Operation lifetime                                           | t <sub>OP</sub> CC | -      | -    | 20    | а    | See Table 46<br>and Table 47 |

| ESD susceptibility<br>according to Human Body<br>Model (HBM) | $V_{\rm HBM}$ SR   | -      | -    | 2 000 | V    | AEC-Q100-002                 |

| ESD susceptibility                                           | $V_{CDM}$          | -      | _    | 500   | V    | JESD22-C101                  |

| according to Charged<br>Device Model (CDM)                   | SR                 | _      | -    | 750   | V    | Corner Pins,<br>JESD22-C101  |

| Moisture sensitivity level                                   | MSL CC             | _      | -    | 3     | -    | JEDEC<br>J-STD-020C          |

## Table 46 Typical Usage Temperature Profile

| Operating Time (Sum = 20 years) | Operating Temperat.                           | Notes            |

|---------------------------------|-----------------------------------------------|------------------|

| 1 200 h                         | $T_{\rm J} = 150^{\circ}{\rm C}$              | Normal operation |

| 3 600 h                         | $T_{\rm J} = 125^{\circ}{\rm C}$              | Normal operation |

| 7 200 h                         | $T_{\rm J} = 110^{\circ}{\rm C}$              | Normal operation |

| 12 000 h                        | $T_{\rm J} = 100^{\circ}{\rm C}$              | Normal operation |

| 7 × 21 600 h                    | $T_{\rm J} = 010^{\circ} {\rm C},,$<br>6070°C | Power reduction  |

| Table 47 | Long Time Storage Temperature Profile |

|----------|---------------------------------------|

|----------|---------------------------------------|

| Operating Time (Sum = 20 years) | Operating Temperat.               | Notes            |

|---------------------------------|-----------------------------------|------------------|

| 2 000 h                         | $T_{\rm J}$ = 150°C               | Normal operation |

| 16 000 h                        | $T_{\rm J}$ = 125°C               | Normal operation |

| 6 000 h                         | $T_{\rm J} = 110^{\circ}{\rm C}$  | Normal operation |

| 151 200 h                       | $T_{\rm J} \le 150^{\circ}{ m C}$ | No operation     |