Welcome to E-XFL.COM

#### Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

#### Details

| Product Status                  | Active                                                                     |

|---------------------------------|----------------------------------------------------------------------------|

| Programmable Type               | In System Programmable                                                     |

| Delay Time tpd(1) Max           | 5.8 ns                                                                     |

| Voltage Supply - Internal       | 1.7V ~ 1.9V                                                                |

| Number of Logic Elements/Blocks | 2                                                                          |

| Number of Macrocells            | 32                                                                         |

| Number of Gates                 | -                                                                          |

| Number of I/O                   | 32                                                                         |

| Operating Temperature           | 0°C ~ 90°C (TJ)                                                            |

| Mounting Type                   | Surface Mount                                                              |

| Package / Case                  | 48-LQFP                                                                    |

| Supplier Device Package         | 48-TQFP (7x7)                                                              |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/lc4032ze-5tn48c |

|                                 |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

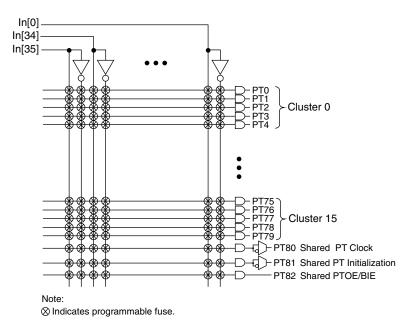

Figure 3. AND Array

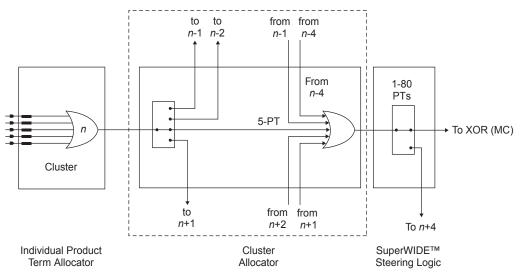

### **Enhanced Logic Allocator**

Within the logic allocator, product terms are allocated to macrocells in product term clusters. Each product term cluster is associated with a macrocell. The cluster size for the ispMACH 4000ZE family is 4+1 (total 5) product terms. The software automatically considers the availability and distribution of product term clusters as it fits the functions within a GLB. The logic allocator is designed to provide two speed paths: 20-PT Speed Locking path and an up to 80-PT path. The availability of these two paths lets designers trade timing variability for increased performance.

The enhanced Logic Allocator of the ispMACH 4000ZE family consists of the following blocks:

- Product Term Allocator

- Cluster Allocator

- Wide Steering Logic

Figure 4 shows a macrocell slice of the Logic Allocator. There are 16 such slices in the GLB.

#### Figure 4. Macrocell Slice

- Block CLK2

- Block CLK3

- PT Clock

- PT Clock Inverted

- Shared PT Clock

- Ground

### **Clock Enable Multiplexer**

Each macrocell has a 4:1 clock enable multiplexer. This allows the clock enable signal to be selected from the following four sources:

- PT Initialization/CE

- PT Initialization/CE Inverted

- Shared PT Clock

- Logic High

### **Initialization Control**

The ispMACH 4000ZE family architecture accommodates both block-level and macrocell-level set and reset capability. There is one block-level initialization term that is distributed to all macrocell registers in a GLB. At the macrocell level, two product terms can be "stolen" from the cluster associated with a macrocell to be used for set/reset functionality. A reset/preset swapping feature in each macrocell allows for reset and preset to be exchanged, providing flexibility.

Note that the reset/preset swapping selection feature affects power-up reset as well. All flip-flops power up to a known state for predictable system initialization. If a macrocell is configured to SET on a signal from the block-level initialization, then that macrocell will be SET during device power-up. If a macrocell is configured to RESET on a signal from the block-level initialization or is not configured for set/reset, then that macrocell will RESET on power-up. To guarantee initialization values, the  $V_{CC}$  rise must be monotonic, and the clock must be inactive until the reset delay time has elapsed.

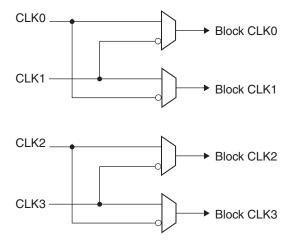

### **GLB Clock Generator**

Each ispMACH 4000ZE device has up to four clock pins that are also routed to the GRP to be used as inputs. These pins drive a clock generator in each GLB, as shown in Figure 6. The clock generator provides four clock signals that can be used anywhere in the GLB. These four GLB clock signals can consist of a number of combinations of the true and complement edges of the global clock signals.

#### Figure 6. GLB Clock Generator

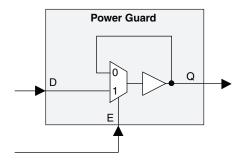

#### Figure 9. Power Guard

All the I/O pins in a block share a common Power Guard Enable signal. For a block of I/Os, this signal is called a Block Input Enable (BIE) signal. BIE can be internally generated using MC logic, or could come from external sources using one of the user I/O or input pins.

Any I/O pin in the block can be programmed to ignore the BIE signal. Thus, the feature can be enabled or disabled on a pin-by-pin basis.

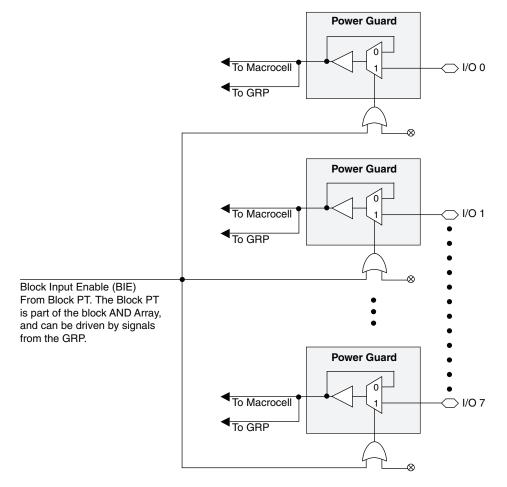

Figure 10 shows Power Guard and BIE across multiple I/Os in a block that has eight I/Os.

#### Figure 10. Power Guard and BIE in a Block with 8 I/Os

The block-level OE PT of each GLB is also tied to Block Input Enable (BIE) of that block. Hence, for a 256-macrocell device (with 16 blocks), each block's BIE signal is driven by block-level OE PT from each block.

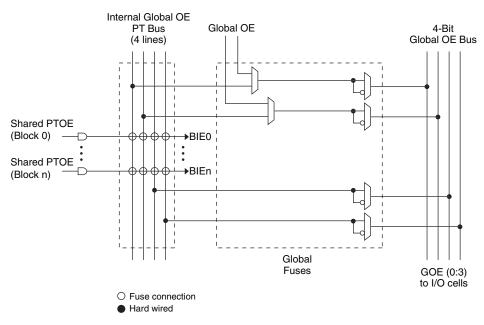

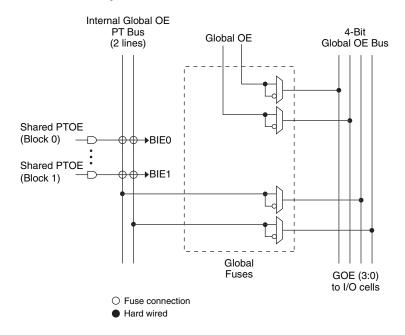

Figure 12. Global OE Generation for ispMACH 4032ZE

## **On-Chip Oscillator and Timer**

An internal oscillator is provided for use in miscellaneous housekeeping functions such as watchdog heartbeats, digital de-glitch circuits and control state machines. The oscillator is disabled by default to save power. Figure 13 shows the block diagram of the oscillator and timer block.

#### Figure 13. On-Chip Oscillator and Timer

Table 11. On-Chip Oscillator and Timer Signal Names

| Signal Name | Input or Out-<br>put | Optional /<br>Required | Description                                                        |

|-------------|----------------------|------------------------|--------------------------------------------------------------------|

| OSCOUT      | Output               | Optional               | Oscillator Output (Nominal Frequency: 5MHz)                        |

| TIMEROUT    | Output               | Optional               | Oscillator Frequency Divided by an integer TIMER_DIV (Default 128) |

| TIMERRES    | Input                | Optional               | Reset the Timer                                                    |

| DYNOSCDIS   | Input                | Optional               | Disables the Oscillator, resets the Timer and saves the power.     |

OSCTIMER has two outputs, OSCOUT and TIMEROUT. The outputs feed into the Global Routing Pool (GRP). From GRP, these signals can drive any macrocell input, as well as any output pin (with macrocell bypass). The output OSCOUT is the direct oscillator output with a typical frequency of 5MHz, whereas, the output TIMEROUT is the oscillator output divided by an attribute TIMER\_DIV.

The attribute TIMER\_DIV can be: 128 (7 bits), 1024 (10 bits) or 1,048,576 (20 bits). The divided output is provided for those user situations, where a very slow clock is desired. If even a slower toggling clock is desired, then the programmable macrocell resources can be used to further divide down the TIMEROUT output.

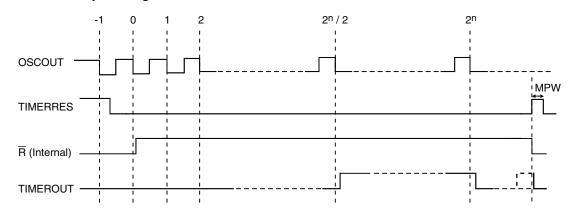

Figure 14 shows the simplified relationship among OSCOUT, TIMERRES and TIMEROUT. In the diagram, the signal " $\overline{R}$ " is an internal reset signal that is used to synchronize TIMERRES to OSCOUT. This adds one extra clock cycle delay for the first timer transition after TIMERRES.

#### Figure 14. Relationship Among OSCOUT, TIMERRES and TIMEROUT

Note: n = Number of bits in the divider (7, 10 or 20) Metastability: If the signal TIMERRES is not synchronous to OSCOUT, it could make a difference of one or two clock cycles to the TIMEROUT going high the first time.

mated test equipment. This equipment can then be used to program ispMACH 4000ZE devices during the testing of a circuit board.

### **User Electronic Signature**

The User Electronic Signature (UES) allows the designer to include identification bits or serial numbers inside the device, stored in E<sup>2</sup>CMOS memory. The ispMACH 4000ZE device contains 32 UES bits that can be configured by the user to store unique data such as ID codes, revision numbers or inventory control codes.

## **Security Bit**

A programmable security bit is provided on the ispMACH 4000ZE devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, this bit defeats readback of the programmed pattern by a device programmer, securing proprietary designs from competitors. Programming and verification are also defeated by the security bit. The bit can only be reset by erasing the entire device.

## Hot Socketing

The ispMACH 4000ZE devices are well-suited for applications that require hot socketing capability. Hot socketing a device requires that the device, during power-up and down, can tolerate active signals on the I/Os and inputs without being damaged. Additionally, it requires that the effects of I/O pin loading be minimal on active signals. The isp-MACH 4000ZE devices provide this capability for input voltages in the range 0V to 3.0V.

## **Density Migration**

The ispMACH 4000ZE family has been designed to ensure that different density devices in the same package have the same pin-out. Furthermore, the architecture ensures a high success rate when performing design migration from lower density parts to higher density parts. In many cases, it is possible to shift a lower utilization design targeted for a high density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

## ispMACH 4000ZE External Switching Characteristics

|                                      |                                                                            | LC40 | )32ZE | LC40 | 64ZE |      | All De | evices |      |       |

|--------------------------------------|----------------------------------------------------------------------------|------|-------|------|------|------|--------|--------|------|-------|

|                                      |                                                                            | -    | 4     | -    | 4    | -    | 5      | -      | 7    |       |

| Parameter                            | Description <sup>1, 2</sup>                                                | Min. | Max.  | Min. | Max. | Min. | Max.   | Min.   | Max. | Units |

| t <sub>PD</sub>                      | 20-PT combinatorial propagation delay                                      | —    | 4.4   | —    | 4.7  | —    | 5.8    | —      | 7.5  | ns    |

| t <sub>S</sub>                       | GLB register setup time before clock                                       | 2.2  | —     | 2.5  | —    | 2.9  | —      | 4.5    | —    | ns    |

| t <sub>ST</sub>                      | GLB register setup time before clock with<br>T-type register               | 2.4  | _     | 2.7  | —    | 3.1  | —      | 4.7    | —    | ns    |

| t <sub>SIR</sub>                     | GLB register setup time before clock, input register path                  | 1.0  | _     | 1.1  | —    | 1.3  | —      | 1.4    | —    | ns    |

| t <sub>SIRZ</sub>                    | GLB register setup time before clock with zero hold                        | 2.0  | _     | 2.1  | —    | 2.9  | —      | 4.0    | —    | ns    |

| t <sub>H</sub>                       | GLB register hold time after clock                                         | 0.0  | _     | 0.0  | —    | 0.0  | —      | 0.0    | —    | ns    |

| t <sub>HT</sub>                      | GLB register hold time after clock with T-type register                    | 0.0  | _     | 0.0  | —    | 0.0  | —      | 0.0    | —    | ns    |

| t <sub>HIR</sub>                     | GLB register hold time after clock, input register path                    | 1.0  | _     | 1.0  | —    | 1.3  | —      | 1.3    | —    | ns    |

| t <sub>HIRZ</sub>                    | GLB register hold time after clock, input register path with zero hold     | 0.0  | _     | 0.0  | —    | 0.0  | —      | 0.0    | —    | ns    |

| t <sub>co</sub>                      | GLB register clock-to-output delay                                         | —    | 3.0   | —    | 3.2  | —    | 3.8    | _      | 4.5  | ns    |

| t <sub>R</sub>                       | External reset pin to output delay                                         | —    | 5.0   | —    | 6.0  | —    | 7.5    | —      | 9.0  | ns    |

| t <sub>RW</sub>                      | External reset pulse duration                                              | 1.5  | _     | 1.7  | —    | 2.0  | —      | 4.0    | —    | ns    |

| t <sub>PTOE/DIS</sub>                | Input to output local product term output enable/disable                   | _    | 7.0   | —    | 8.0  | _    | 8.2    | _      | 9.0  | ns    |

| t <sub>GPTOE/DIS</sub>               | Input to output global product term output enable/disable                  | _    | 6.5   | _    | 7.0  | _    | 10.0   | _      | 10.5 | ns    |

| t <sub>GOE/DIS</sub>                 | Global OE input to output enable/disable                                   | _    | 4.5   | _    | 4.5  | _    | 5.5    |        | 7.0  | ns    |

| t <sub>CW</sub>                      | Global clock width, high or low                                            | 1.0  | _     | 1.5  | —    | 1.8  | —      | 2.8    | —    | ns    |

| t <sub>GW</sub>                      | Global gate width low (for low transparent) or high (for high transparent) | 1.0  | _     | 1.5  | _    | 1.8  | _      | 2.8    | _    | ns    |

| t <sub>WIR</sub>                     | Input register clock width, high or low                                    | 1.0  | —     | 1.5  | —    | 1.8  | —      | 2.8    | —    | ns    |

| f <sub>MAX</sub> (Int.) <sup>3</sup> | Clock frequency with internal feedback                                     |      | 260   | —    | 241  |      | 200    |        | 172  | MHz   |

| f <sub>MAX</sub> (Ext.)              | clock frequency with external feedback, $[1 / (t_S + t_{CO})]$             | _    | 192   | -    | 175  | _    | 149    | _      | 111  | MHz   |

#### **Over Recommended Operating Conditions**

1. Timing numbers are based on default LVCMOS 1.8 I/O buffers. Use timing adjusters provided to calculate other standards.

Measured using standard switching GRP loading of 1 and 1 output switching.

Standard 16-bit counter using GRP feedback.

Timing v.0.8

## ispMACH 4000ZE Internal Timing Parameters (Cont.)

### **Over Recommended Operating Conditions**

|              |                                                 |                                                       | LC40 | 32ZE | LC40 | 64ZE |       |

|--------------|-------------------------------------------------|-------------------------------------------------------|------|------|------|------|-------|

|              |                                                 |                                                       | -    | 4    | -    | 4    |       |

| Parameter    | Description                                     |                                                       | Min. | Max. | Min. | Max. | Units |

| LVCMOS15_out | Output Configured as 1.5V Buffer                | t <sub>EN</sub> , t <sub>DIS</sub> , t <sub>BUF</sub> | _    | 0.20 | _    | 0.20 | ns    |

| LVCMOS18_out | Output Configured as 1.8V Buffer                | t <sub>EN</sub> , t <sub>DIS</sub> , t <sub>BUF</sub> | —    | 0.00 | _    | 0.00 | ns    |

| LVCMOS25_out | Output Configured as 2.5V Buffer                | t <sub>EN</sub> , t <sub>DIS</sub> , t <sub>BUF</sub> | _    | 0.10 | —    | 0.10 | ns    |

| LVCMOS33_out | Output Configured as 3.3V Buffer                | t <sub>EN</sub> , t <sub>DIS</sub> , t <sub>BUF</sub> | _    | 0.20 | —    | 0.20 | ns    |

| PCI_out      | Output Configured as PCI Compati-<br>ble Buffer | t <sub>EN</sub> , t <sub>DIS</sub> , t <sub>BUF</sub> | _    | 0.20 | _    | 0.20 | ns    |

| Slow Slew    | Output Configured for Slow Slew<br>Rate         | t <sub>EN</sub> , t <sub>BUF</sub>                    | _    | 1.00 | _    | 1.00 | ns    |

Note: Internal Timing Parameters are not tested and are for reference only. Refer to the timing model in this data sheet for further details. Timing v.0.8

## ispMACH 4000ZE Internal Timing Parameters (Cont.)

| Over Recommended Operating Conditions |

|---------------------------------------|

|---------------------------------------|

|                               |                                                     |                                                           |      | ]     |      |       |       |

|-------------------------------|-----------------------------------------------------|-----------------------------------------------------------|------|-------|------|-------|-------|

|                               |                                                     |                                                           | -    | 5     | -    | -7    |       |

| Parameter                     | Description                                         |                                                           | Min. | Max.  | Min. | Max.  | Units |

| t <sub>SRR</sub>              | Asynchronous Reset or Set Recov                     | ery Delay                                                 | —    | 1.80  | —    | 1.67  | ns    |

| Control Delays                |                                                     |                                                           |      |       |      |       |       |

| t <sub>BCLK</sub>             | GLB PT Clock Delay                                  |                                                           | —    | 1.45  | —    | 0.95  | ns    |

| t <sub>PTCLK</sub>            | Macrocell PT Clock Delay                            |                                                           | —    | 1.45  |      | 1.15  | ns    |

| t <sub>BSR</sub>              | Block PT Set/Reset Delay                            |                                                           | —    | 1.85  | —    | 1.83  | ns    |

| t <sub>PTSR</sub>             | Macrocell PT Set/Reset Delay                        |                                                           | —    | 1.85  |      | 2.72  | ns    |

| t <sub>BIE</sub>              | Power Guard Block Input Enable D                    | elay                                                      | —    | 1.75  | —    | 1.95  | ns    |

| t <sub>PTOE</sub>             | Macrocell PT OE Delay                               |                                                           | —    | 2.40  | —    | 1.90  | ns    |

| t <sub>GPTOE</sub>            | Global PT OE Delay                                  |                                                           | —    | 4.20  | —    | 3.40  | ns    |

| Internal Oscillat             | or                                                  |                                                           |      |       |      |       |       |

| toscsu                        | Oscillator DYNOSCDIS Setup Time                     | 9                                                         | 5.00 | —     | 5.00 | —     | ns    |

| t <sub>oscн</sub>             | Oscillator DYNOSCDIS Hold Time                      |                                                           | 5.00 | —     | 5.00 | —     | ns    |

| t <sub>OSCEN</sub>            | Oscillator OSCOUT Enable Time (                     | To Stable)                                                | —    | 5.00  | —    | 5.00  | ns    |

| toscod                        | Oscillator Output Delay                             |                                                           |      | 4.00  | _    | 4.00  | ns    |

| t <sub>OSCNOM</sub>           | Oscillator OSCOUT Nominal Frequ                     | iency                                                     |      | 5.00  |      | 5.00  | MHz   |

| t <sub>OSCvar</sub>           | Oscillator Variation of Nominal Free                | quency                                                    | _    | 30    | _    | 30    | %     |

| t <sub>TMRCO20</sub>          | Oscillator TIMEROUT Clock (Nega<br>(20-Bit Divider) | tive Edge) to Out                                         | _    | 12.50 | —    | 14.50 | ns    |

| t <sub>TMRCO10</sub>          | Oscillator TIMEROUT Clock (Nega<br>(10-Bit Divider) | tive Edge) to Out                                         | _    | 7.50  | —    | 9.50  | ns    |

| t <sub>TMRCO7</sub>           | Oscillator TIMEROUT Clock (Nega<br>(7-Bit Divider)  | tive Edge) to Out                                         |      | 6.00  | _    | 8.00  | ns    |

| t <sub>TMRRSTO</sub>          | Oscillator TIMEROUT Reset to Out                    | t (Going Low)                                             | —    | 5.00  | _    | 7.00  | ns    |

| t <sub>TMRRR</sub>            | Oscillator TIMEROUT Asynchronol<br>Delay            | us Reset Recovery                                         |      | 4.00  | _    | 6.00  | ns    |

| t <sub>TMRRSTPW</sub>         | Oscillator TIMEROUT Reset Minim                     | um Pulse Width                                            | 3.00 | _     | 5.00 |       | ns    |

| Optional Delay                | Adjusters                                           | Base Parameter                                            |      |       |      |       |       |

| t <sub>INDIO</sub>            | Input Register Delay                                | t <sub>INREG</sub>                                        | _    | 1.60  |      | 2.60  | ns    |

| t <sub>EXP</sub>              | Product Term Expander Delay                         | t <sub>MCELL</sub>                                        | —    | 0.45  | _    | 0.50  | ns    |

| t <sub>BLA</sub>              | Additional Block Loading Adders                     | t <sub>ROUTE</sub>                                        | —    | 0.05  | _    | 0.05  | ns    |

| t <sub>IOI</sub> Input Buffer | Delays                                              | I                                                         |      |       | 1    |       |       |

| LVTTL_in                      | Using LVTTL Standard with<br>Hysteresis             | t <sub>IN</sub> , t <sub>GCLK_IN</sub> , t <sub>GOE</sub> | _    | 0.60  | _    | 0.60  | ns    |

| LVCMOS15_in                   | Using LVCMOS 1.5 Standard                           | t <sub>IN</sub> , t <sub>GCLK_IN</sub> , t <sub>GOE</sub> |      | 0.20  | _    | 0.20  | ns    |

| LVCMOS18_in                   | Using LVCMOS 1.8 Standard                           | t <sub>IN</sub> , t <sub>GCLK_IN</sub> , t <sub>GOE</sub> |      | 0.00  | _    | 0.00  | ns    |

| LVCMOS25_in                   | Using LVCMOS 2.5 Standard with Hysteresis           | t <sub>IN</sub> , t <sub>GCLK_IN</sub> , t <sub>GOE</sub> | _    | 0.80  | _    | 0.80  | ns    |

| LVCMOS33_in                   | Using LVCMOS 3.3 Standard with Hysteresis           | t <sub>IN</sub> , t <sub>GCLK_IN</sub> , t <sub>GOE</sub> | _    | 0.80  | _    | 0.80  | ns    |

| PCI_in                        | Using PCI Compatible Input with Hysteresis          | t <sub>IN</sub> , t <sub>GCLK_IN</sub> , t <sub>GOE</sub> | _    | 0.80  | _    | 0.80  | ns    |

| t <sub>IOO</sub> Output Buf   | -                                                   | 1                                                         | 1    | 1     | 1    | I     | 1     |

| LVTTL_out                     | Output Configured as TTL Buffer                     | t <sub>EN</sub> , t <sub>DIS</sub> , t <sub>BUF</sub>     | _    | 0.20  | _    | 0.20  | ns    |

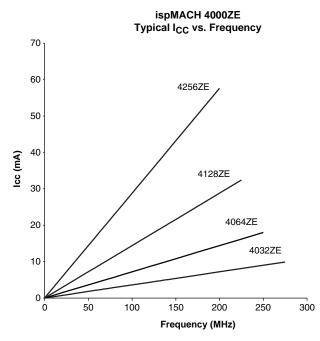

## **Power Consumption**

## **Power Estimation Coefficients**<sup>1</sup>

| Device         | Α     | В     |

|----------------|-------|-------|

| ispMACH 4032ZE | 0.010 | 0.009 |

| ispMACH 4064ZE | 0.011 | 0.009 |

| ispMACH 4128ZE | 0.012 | 0.009 |

| ispMACH 4256ZE | 0.013 | 0.009 |

1. For further information about the use of these coefficients, refer to TN1187, <u>Power Esti-</u> mation in ispMACH 4000ZE Devices.

## **Switching Test Conditions**

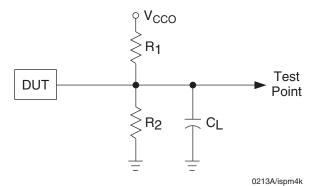

Figure 17 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 13.

#### Figure 17. Output Test Load, LVTTL and LVCMOS Standards

Table 13. Test Fixture Required Components

| Test Condition               | R <sub>1</sub> | R <sub>2</sub> | CL1  | Timing Ref.                      | V <sub>cco</sub>   |

|------------------------------|----------------|----------------|------|----------------------------------|--------------------|

|                              |                |                |      | LVCMOS 3.3 = 1.5V                | LVCMOS 3.3 = 3.0V  |

|                              |                |                |      | LVCMOS 2.5 = $\frac{V_{CCO}}{2}$ | LVCMOS 2.5 = 2.3V  |

| LVCMOS I/O, (L -> H, H -> L) | 106Ω           | 106Ω           | 35pF | LVCMOS 1.8 = $\frac{V_{CCO}}{2}$ | LVCMOS 1.8 = 1.65V |

|                              |                |                |      | LVCMOS 1.5 = $\frac{V_{CCO}}{2}$ | LVCMOS 1.5 = 1.4V  |

| LVCMOS I/O (Z -> H)          | $\infty$       | 106Ω           | 35pF | 1.5V                             | 3.0V               |

| LVCMOS I/O (Z -> L)          | 106Ω           | ×              | 35pF | 1.5V                             | 3.0V               |

| LVCMOS I/O (H -> Z)          | $\infty$       | 106Ω           | 5pF  | V <sub>OH</sub> - 0.3            | 3.0V               |

| LVCMOS I/O (L -> Z)          | 106Ω           | 8              | 5pF  | V <sub>OL</sub> + 0.3            | 3.0V               |

1. C<sub>L</sub> includes test fixtures and probe capacitance.

## **Signal Descriptions**

| Signal Names                          | Desci                                                                                                | ription                                                                                                 |  |  |  |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|

| TMS                                   | Input – This pin is the IEEE 1149.1 Test M the state machine.                                        | Input – This pin is the IEEE 1149.1 Test Mode Select input, which is used to control the state machine. |  |  |  |  |

| ТСК                                   | Input – This pin is the IEEE 1149.1 Test C state machine.                                            | Input – This pin is the IEEE 1149.1 Test Clock input pin, used to clock through the state machine.      |  |  |  |  |

| TDI                                   | Input – This pin is the IEEE 1149.1 Test D                                                           | ata In pin, used to load data.                                                                          |  |  |  |  |

| TDO                                   | Output – This pin is the IEEE 1149.1 Test                                                            | Data Out pin used to shift data out.                                                                    |  |  |  |  |

| GOE0/IO, GOE1/IO                      | These pins are configured to be either Global Output Enable Input or as general I/O pins.            |                                                                                                         |  |  |  |  |

| GND                                   | Ground                                                                                               | Ground                                                                                                  |  |  |  |  |

| NC                                    | Not Connected                                                                                        | Not Connected                                                                                           |  |  |  |  |

| V <sub>CC</sub>                       | The power supply pins for logic core and J                                                           | ITAG port.                                                                                              |  |  |  |  |

| CLK0/I, CLK1/I, CLK2/I, CLK3/I        | These pins are configured to be either CLI                                                           | K input or as an input.                                                                                 |  |  |  |  |

| V <sub>CCO0</sub> , V <sub>CCO1</sub> | The power supply pins for each I/O bank.                                                             |                                                                                                         |  |  |  |  |

|                                       | Input/Output <sup>1</sup> – These are the general pur reference (alpha) and z is macrocell reference |                                                                                                         |  |  |  |  |

|                                       | ispMACH 4032ZE                                                                                       | y: A-B                                                                                                  |  |  |  |  |

| yzz                                   | ispMACH 4064ZE                                                                                       | y: A-D                                                                                                  |  |  |  |  |

|                                       | ispMACH 4128ZE                                                                                       | y: A-H                                                                                                  |  |  |  |  |

|                                       | ispMACH 4256ZE                                                                                       | y: A-P                                                                                                  |  |  |  |  |

1. In some packages, certain I/Os are only available for use as inputs. See the Logic Signal Connections tables for details.

## **ORP Reference Table**

|                                          | 4032ZE |    | 4064ZE                         |    | 412 | 8ZE |    | 4256ZE |                    |

|------------------------------------------|--------|----|--------------------------------|----|-----|-----|----|--------|--------------------|

| Number of I/Os                           | 32     | 32 | 48                             | 64 | 64  | 96  | 64 | 96     | 108                |

| Number of GLBs                           | 2      | 4  | 4                              | 4  | 8   | 8   | 16 | 16     | 16                 |

| Number of<br>I/Os per GLB                | 16     | 8  | Mixture of<br>9, 10,<br>14, 15 | 16 | 8   | 12  | 4  | 6      | Mixture of 6, 7, 8 |

| Reference ORP<br>Table (I/Os per<br>GLB) | 16     | 8  | 9, 10,<br>14, 15               | 16 | 8   | 12  | 4  | 6      | 6, 7, 8            |

## ispMACH 4000ZE Power Supply and NC Connections<sup>1</sup> (Cont.)

| Signal                 | 132 ucBGA <sup>3</sup> | 144 csBGA <sup>3</sup>                                                                                                                                                                                                                                                                 | 144 TQFP <sup>2</sup>                  |

|------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| VCC                    | M1, M7, A12, B5        | H5, H8, E8, E5                                                                                                                                                                                                                                                                         | 36, 57, 108, 129                       |

| VCCO0<br>VCCO (Bank 0) | B1, H4, L2, J5, A4     | E4, F4, G4, J5, D5                                                                                                                                                                                                                                                                     | 3, 19, 34, 47, 136                     |

| VCCO1<br>VCCO (Bank 1) | K9, L12, F12, D9, C7   | J8, H9, G9, F9, D8                                                                                                                                                                                                                                                                     | 64, 75, 91, 106, 119                   |

| GND                    | E5, E8, H5, H8         | F6, G6, G7, F7                                                                                                                                                                                                                                                                         | 1, 37, 73, 109                         |

| GND (Bank 0)           | E2, H2, M4, B7, B3     | G5, H4, H6, E6, F5                                                                                                                                                                                                                                                                     | 10, 18 <sup>4</sup> , 27, 46, 127, 137 |

| GND (Bank 1)           | L7, J9, H12, E9, A9    | H7, J9, G8, F8, E7                                                                                                                                                                                                                                                                     | 55, 65, 82, 90 <sup>4</sup> , 99, 118  |

| NC                     |                        | 4064ZE: E4, B2, B1, D2, D3, E1,<br>H1, H3, H2, L1, G4, M1, K3, M2,<br>M4, L5, H7, L8, M8, L10, K9, M11,<br>H9, L12, L11, J12, J11, H10, D10,<br>F10, D12, B12, F9, A12, C10, B10,<br>A9, B8, E6, B5, A5, C4, B3, A2<br>4128ZE: D2, D3, H2, M1, K3, M11,<br>J12, J11, D12, A12, C10, A2 |                                        |

1. All grounds must be electrically connected at the board level. However, for the purposes of I/O current loading, grounds are associated with the bank shown.

2. Pin orientation follows the conventional order from pin 1 marking of the top side view and counter-clockwise.

3. Pin orientation A1 starts from the upper left corner of the top side view with alphabetical order ascending vertically and numerical order ascending horizontally.

4. For the LC4256ZE, pins 18 and 90 are no connects.

## ispMACH 4032ZE and 4064ZE Logic Signal Connections: 64 csBGA

|             |             | ispMACH 4032ZE | ispMACH 4064ZE |  |  |

|-------------|-------------|----------------|----------------|--|--|

| Ball Number | Bank Number | GLB/MC/Pad     | GLB/MC/Pad     |  |  |

| B2          | -           | TDI            | TDI            |  |  |

| B1          | 0           | A5             | A8             |  |  |

| C2          | 0           | A6             | A10            |  |  |

| C1          | 0           | A7             | A11            |  |  |

| GND*        | 0           | GND (Bank 0)   | GND (Bank 0)   |  |  |

| C3          | 0           | NC             | A12            |  |  |

| E3          | 0           | VCCO (Bank 0)  | VCCO (Bank 0)  |  |  |

| D1          | 0           | A8             | B15            |  |  |

| D2          | 0           | NC             | B14            |  |  |

| E1          | 0           | A9             | B13            |  |  |

| D3          | 0           | A10            | B12            |  |  |

| F1          | 0           | A11            | B11            |  |  |

| E2          | 0           | NC             | B10            |  |  |

| G1          | 0           | NC             | B9             |  |  |

| F2          | 0           | NC             | B8             |  |  |

| H1          | -           | ТСК            | TCK            |  |  |

| E4          | -           | VCC            | VCC            |  |  |

| GND*        | -           | GND            | GND            |  |  |

| G2          | 0           | A12            | B6             |  |  |

| H2          | 0           | NC             | B5             |  |  |

| H3          | 0           | A13            | B4             |  |  |

| GND*        | 0           | NC             | GND (Bank 0)   |  |  |

| F4          | 0           | NC             | VCCO (Bank 0)  |  |  |

| G3          | 0           | A14            | B3             |  |  |

| F3          | 0           | NC             | B2             |  |  |

| H4          | 0           | A15            | B0             |  |  |

| G4          | 0           | CLK1/I         | CLK1/I         |  |  |

| H5          | 1           | CLK2/I         | CLK2/I         |  |  |

| F5          | 1           | B0             | CO             |  |  |

| G5          | 1           | B1             | C1             |  |  |

| G6          | 1           | B2             | C2             |  |  |

| H6          | 1           | B3             | C4             |  |  |

| F6          | 1           | B4             | C5             |  |  |

| H7          | 1           | NC             | C6             |  |  |

| H8          | -           | TMS            | TMS            |  |  |

| G7          | 1           | B5             | C8             |  |  |

| F7          | 1           | B6             | C10            |  |  |

| G8          | 1           | B7             | C11            |  |  |

| GND*        | 1           | GND (Bank 0)   | GND (Bank 1)   |  |  |

| F8          | 1           | NC             | C12            |  |  |

| D6          | 1           | VCCO (Bank 1)  | VCCO (Bank 1)  |  |  |

| E8          | 1           | B8             | D15            |  |  |

# ispMACH 4064ZE, 4128ZE and 4256ZE Logic Signal Connections: 100 TQFP (Cont.)

| Pin    | Bank   | LC4064ZE      | LC4128ZE      | LC4256ZE      |

|--------|--------|---------------|---------------|---------------|

| Number | Number | GLB/MC/Pad    | GLB/MC/Pad    | GLB/MC/Pad    |

| 42     | 1      | C1            | E2            | 16            |

| 43     | 1      | C2            | E4            | 110           |

| 44     | 1      | C3            | E6            | 112           |

| 45     | 1      | VCCO (Bank 1) | VCCO (Bank 1) | VCCO (Bank 1) |

| 46     | 1      | GND (Bank 1)  | GND (Bank 1)  | GND (Bank 1)  |

| 47     | 1      | C4            | E8            | J2            |

| 48     | 1      | C5            | E10           | J6            |

| 49     | 1      | C6            | E12           | J10           |

| 50     | 1      | C7            | E14           | J12           |

| 51     | -      | GND           | GND           | GND           |

| 52     | -      | TMS           | TMS           | TMS           |

| 53     | 1      | C8            | F0            | K12           |

| 54     | 1      | C9            | F2            | K10           |

| 55     | 1      | C10           | F4            | K6            |

| 56     | 1      | C11           | F6            | K2            |

| 57     | 1      | GND (Bank 1)  | GND (Bank 1)  | GND (Bank 1)  |

| 58     | 1      | C12           | F8            | L12           |

| 59     | 1      | C13           | F10           | L10           |

| 60     | 1      | C14           | F12           | L6            |

| 61     | 1      | C15           | F13           | L4            |

| 62*    | 1      | I             | I             | I             |

| 63     | 1      | VCCO (Bank 1) | VCCO (Bank 1) | VCCO (Bank 1) |

| 64     | 1      | D15           | G14           | M4            |

| 65     | 1      | D14           | G12           | M6            |

| 66     | 1      | D13           | G10           | M10           |

| 67     | 1      | D12           | G8            | M12           |

| 68     | 1      | GND (Bank 1)  | GND (Bank 1)  | GND (Bank 1)  |

| 69     | 1      | D11           | G6            | N2            |

| 70     | 1      | D10           | G5            | N6            |

| 71     | 1      | D9            | G4            | N10           |

| 72     | 1      | D8            | G2            | N12           |

| 73*    | 1      | I             |               | 1             |

| 74     | -      | TDO           | TDO           | TDO           |

| 75     | -      | VCC           | VCC           | VCC           |

| 76     | -      | GND           | GND           | GND           |

| 77*    | 1      | I             |               | 1             |

| 78     | 1      | D7            | H13           | 012           |

| 79     | 1      | D6            | H12           | O10           |

| 80     | 1      | D5            | H10           | O6            |

| 81     | 1      | D4            | H8            | O2            |

| 82     | 1      | GND (Bank 1)  | GND (Bank 1)  | GND (Bank 1)  |

# ispMACH 4064ZE, 4128ZE and 4256ZE Logic Signal Connections: 144 csBGA

| Ball   | Bank   | LC4064ZE      | LC4128ZE      | LC4256ZE      |

|--------|--------|---------------|---------------|---------------|

| Number | Number | GLB/MC/Pad    | GLB/MC/Pad    | GLB/MC/Pad    |

| F6     | -      | GND           | GND           | GND           |

| A1     | -      | TDI           | TDI           | TDI           |

| E4     | 0      | NC Ball       | VCCO (Bank 0) | VCCO (Bank 0) |

| B2     | 0      | NC Ball       | B0            | C12           |

| B1     | 0      | NC Ball       | B1            | C10           |

| C3     | 0      | A8            | B2            | C8            |

| C2     | 0      | A9            | B4            | C6            |

| C1     | 0      | A10           | B5            | C4            |

| D1     | 0      | A11           | B6            | C2            |

| G5     | 0      | GND (Bank 0)  | GND (Bank 0)  | GND (Bank 0)  |

| D2     | 0      | NC Ball       | NC Ball       | D14           |

| D3     | 0      | NC Ball       | NC Ball       | D12           |

| E1     | 0      | NC Ball       | B8            | D10           |

| E2     | 0      | A12           | B9            | D8            |

| F2     | 0      | A13           | B10           | D6            |

| D4     | 0      | A14           | B12           | D4            |

| F1     | 0      | A15           | B13           | D2            |

| F3*    | 0      |               | B14           | D0            |

| F4     | 0      | VCCO (Bank 0) | VCCO (Bank 0) | VCCO (Bank 0) |

| G1     | 0      | B15           | C14           | E0            |

| E3     | 0      | B14           | C13           | E2            |

| G2     | 0      | B13           | C12           | E4            |

| G3     | 0      | B12           | C10           | E6            |

| H1     | 0      | NC Ball       | C9            | E8            |

| H3     | 0      | NC Ball       | C8            | E10           |

| H2     | 0      | NC Ball       | NC Ball       | E12           |

| H4     | 0      | GND (Bank 0)  | GND (Bank 0)  | GND (Bank 0)  |

| J1     | 0      | B11           | C6            | F2            |

| J3     | 0      | B10           | C5            | F4            |

| J2     | 0      | B9            | C4            | F6            |

| K1     | 0      | B8            | C2            | F8            |

| K2*    | 0      |               | C1            | F10           |

| L1     | 0      | NC Ball       | CO            | F12           |

| G4     | 0      | NC Ball       | VCCO (Bank 0) | VCCO (Bank 0) |

| L2     | -      | ТСК           | ТСК           | ТСК           |

| H5     | -      | VCC           | VCC           | VCC           |

| G6     | -      | GND           | GND           | GND           |

| M1     | 0      | NC Ball       | NC Ball       | G14           |

| K3     | 0      | NC Ball       | NC Ball       | G12           |

| M2     | 0      | NC Ball       | D14           | G10           |

| L3*    | 0      |               | D13           | G8            |

# ispMACH 4064ZE, 4128ZE and 4256ZE Logic Signal Connections: 144 csBGA (Cont.)

| Ball   | Bank   | LC4064ZE      | LC4128ZE      | LC4256ZE      |

|--------|--------|---------------|---------------|---------------|

| Number | Number | GLB/MC/Pad    | GLB/MC/Pad    | GLB/MC/Pad    |

| J4     | 0      | B7            | D12           | G6            |

| K4     | 0      | B6            | D10           | G4            |

| M3     | 0      | B5            | D9            | G2            |

| L4     | 0      | B4            | D8            | G0            |

| H6     | 0      | GND (Bank 0)  | GND (Bank 0)  | GND (Bank 0)  |

| J5     | 0      | VCCO (Bank 0) | VCCO (Bank 0) | VCCO (Bank 0) |

| M4     | 0      | NC Ball       | D6            | H12           |

| L5     | 0      | NC Ball       | D5            | H10           |

| K5     | 0      | B3            | D4            | H8            |

| J6     | 0      | B2            | D2            | H6            |

| M5     | 0      | B1            | D1            | H4            |

| K6     | 0      | B0            | D0            | H2            |

| L6     | 0      | CLK1/I        | CLK1/I        | CLK1/I        |

| H7     | 1      | NC Ball       | GND (Bank 1)  | GND (Bank 1)  |

| M6     | 1      | CLK2/I        | CLK2/I        | CLK2/I        |

| H8     | -      | VCC           | VCC           | VCC           |

| K7     | 1      | C0            | E0            | 12            |

| M7     | 1      | C1            | E1            | 14            |

| L7     | 1      | C2            | E2            | 16            |

| J7     | 1      | C3            | E4            | 18            |

| L8     | 1      | NC Ball       | E5            | l10           |

| M8     | 1      | NC Ball       | E6            | 12            |

| J8     | 1      | VCCO (Bank 1) | VCCO (Bank 1) | VCCO (Bank 1) |

| J9     | 1      | GND (Bank 1)  | GND (Bank 1)  | GND (Bank 1)  |

| M9     | 1      | C4            | E8            | J2            |

| L9     | 1      | C5            | E9            | J4            |

| K8     | 1      | C6            | E10           | J6            |

| M10    | 1      | C7            | E12           | J8            |

| L10    | 1      | NC Ball       | E13           | J10           |

| K9     | 1      | NC Ball       | E14           | J12           |

| M11    | 1      | NC Ball       | NC Ball       | J14           |

| G7     | -      | GND           | GND           | GND           |

| M12    | -      | TMS           | TMS           | TMS           |

| H9     | 1      | NC Ball       | VCCO (Bank 1) | VCCO (Bank 1) |

| L12    | 1      | NC Ball       | F0            | K12           |

| L11    | 1      | NC Ball       | F1            | K10           |

| K10    | 1      | C8            | F2            | K8            |

| K12    | 1      | C9            | F4            | K6            |

| J10    | 1      | C10           | F5            | K4            |

| K11    | 1      | C11           | F6            | K2            |

| G8     | 1      | GND (Bank 1)  | GND (Bank 1)  | GND (Bank 1)  |

# ispMACH 4064ZE, 4128ZE and 4256ZE Logic Signal Connections: 144 csBGA (Cont.)

| Ball   | Bank   | LC4064ZE      | LC4128ZE      | LC4256ZE      |

|--------|--------|---------------|---------------|---------------|

| Number | Number | GLB/MC/Pad    | GLB/MC/Pad    | GLB/MC/Pad    |

| J12    | 1      | NC Ball       | NC Ball       | L14           |

| J11    | 1      | NC Ball       | NC Ball       | L12           |

| H10    | 1      | NC Ball       | F8            | L10           |

| H12    | 1      | C12           | F9            | L8            |

| G11    | 1      | C13           | F10           | L6            |

| H11    | 1      | C14           | F12           | L4            |

| G12    | 1      | C15           | F13           | L2            |

| G10*   | 1      | Ι             | F14           | LO            |

| G9     | 1      | VCCO (Bank 1) | VCCO (Bank 1) | VCCO (Bank 1) |

| F12    | 1      | D15           | G14           | M0            |

| F11    | 1      | D14           | G13           | M2            |

| E11    | 1      | D13           | G12           | M4            |

| E12    | 1      | D12           | G10           | M6            |

| D10    | 1      | NC Ball       | G9            | M8            |

| F10    | 1      | NC Ball       | G8            | M10           |

| D12    | 1      | NC Ball       | NC Ball       | M12           |

| F8     | 1      | GND (Bank 1)  | GND (Bank 1)  | GND (Bank 1)  |

| E10    | 1      | D11           | G6            | N2            |

| D11    | 1      | D10           | G5            | N4            |

| E9     | 1      | D9            | G4            | N6            |

| C12    | 1      | D8            | G2            | N8            |

| C11*   | 1      | I             | G1            | N10           |

| B12    | 1      | NC Ball       | G0            | N12           |

| F9     | 1      | NC Ball       | VCCO (Bank 1) | VCCO (Bank 1) |

| B11    | -      | TDO           | TDO           | TDO           |

| E8     | -      | VCC           | VCC           | VCC           |

| F7     | -      | GND           | GND           | GND           |

| A12    | 1      | NC Ball       | NC Ball       | O14           |

| C10    | 1      | NC Ball       | NC Ball       | 012           |

| B10    | 1      | NC Ball       | H14           | O10           |

| A11*   | 1      | I             | H13           | O8            |

| D9     | 1      | D7            | H12           | O6            |

| B9     | 1      | D6            | H10           | O4            |

| C9     | 1      | D5            | H9            | 02            |

| A10    | 1      | D4            | H8            | O0            |

| E7     | 1      | GND (Bank 1)  | GND (Bank 1)  | GND (Bank 1)  |

| D8     | 1      | VCCO (Bank 1) | VCCO (Bank 1) | VCCO (Bank 1) |

| A9     | 1      | NC Ball       | H6            | P12           |

| B8     | 1      | NC Ball       | H5            | P10           |

| C8     | 1      | D3            | H4            | P8            |

| A8     | 1      | D2            | H2            | P6            |

| D7     | 1      | D1            | H1            | P4            |

| B7     | 1      |               |               | P2/GOE1       |

## ispMACH 4128ZE and 4256ZE Logic Signal Connections: 144 TQFP (Cont.)

|            |             | LC4128ZE      | LC4256ZE      |

|------------|-------------|---------------|---------------|

| Pin Number | Bank Number | GLB/MC/Pad    | GLB/MC/Pad    |

| 86         | 1           | F12           | L8            |

| 87         | 1           | F13           | L6            |

| 88         | 1           | F14           | L4            |

| 89*        | 1           | NC            | I             |

| 90         | 1           | GND (Bank 1)  | NC            |

| 91         | 1           | VCCO (Bank 1) | VCCO (Bank 1) |

| 92*        | 1           | NC            | I             |

| 93         | 1           | G14           | M2            |

| 94         | 1           | G13           | M4            |

| 95         | 1           | G12           | M6            |

| 96         | 1           | G10           | M8            |

| 97         | 1           | G9            | M10           |

| 98         | 1           | G8            | M12           |

| 99         | 1           | GND (Bank 1)  | GND (Bank 1)  |

| 100        | 1           | G6            | N2            |

| 101        | 1           | G5            | N4            |

| 102        | 1           | G4            | N6            |

| 103        | 1           | G2            | N8            |

| 104        | 1           | G1            | N10           |

| 105        | 1           | G0            | N12           |

| 106        | 1           | VCCO (Bank 1) | VCCO (Bank 1) |

| 107        | -           | TDO           | TDO           |

| 108        | -           | VCC           | VCC           |

| 109        | -           | GND           | GND           |

| 110*       | 1           | NC            | I             |

| 111        | 1           | H14           | O12           |

| 112        | 1           | H13           | O10           |

| 113        | 1           | H12           | O8            |

| 114        | 1           | H10           | O6            |

| 115        | 1           | H9            | 04            |

| 116        | 1           | H8            | 02            |

| 117*       | 1           | NC            | I             |

| 118        | 1           | GND (Bank 1)  | GND (Bank 1)  |

| 119        | 1           | VCCO (Bank 1) | VCCO (Bank 1) |

| 120        | 1           | H6            | P12           |

| 121        | 1           | H5            | P10           |

| 122        | 1           | H4            | P8            |

| 123        | 1           | H2            | P6            |

| 124        | 1           | H1            | P4            |

| 125        | 1           | H0/GOE1       | P2/GOE1       |

| 126        | 1           | CLK3/I        | CLK3/I        |

| 127        | 0           | GND (Bank 0)  | GND (Bank 0)  |

| 128        | 0           | CLK0/I        | CLK0/I        |

# **Revision History**

| ucBGA packages.<br>Updated ispMACH 4000ZE Power Supply and NC Connections table to include 64-ball ucB<br>and 132-ball ucBGA packages.<br>Added Logic Signal Connections tables for 64-ball ucBGA and 132-ball ucBGA packages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Date           | Version | Change Summary                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------|---------------------------------------------------------------------------------------------------------------------|

| August 2008   01.2   Data sheet status changed from advance to final.     Updated 144 TQFP Logic Signal Connections table.   Updated 144 TQFP Logic Signal Connections table.     Updated 144 TQFP Logic Signal Connections table.   Updated 144 TQFP Logic Signal Connections table.     Updated 144 TQFP Logic Signal Connections table.   Updated 144 TQFP Logic Signal Connections table.     Updated 144 TQFP Logic Signal Connections table.   Updated Supply Current table.     Updated 144 TQFP Logic Signal Connections table.   Updated 144 TQFP Logic Signal Connections table.     Updated 144 TQFP Logic Signal Connections table.   Updated 144 TQFP Logic Signal Connections table.     Dupdated 144 TQFP Logic Signal Connections table.   Updated 144 TQFP Logic Signal Connections table.     Dupdated 144 TQFP Logic Signal Connections table.   Updated Supply Current table.     Updated Supply Current table.   Updated Internal Timing Parameters.     Updated Ordering Information mark format example.   Updated Ordering Information mark format example.     December 2008   01.3   Updated ispMACH 4000ZE Fower Supply and NC Connections table to include 64-ball ucBGA packages.     Updated ispMACH 4000ZE Fower Supply and NC Connections table to include 64-ball ucBGA packages.   Updated Logic Signal Connections tables for 64-ball ucBGA packages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | April 2008     | 01.0    | Initial release.                                                                                                    |

| Updated Power Guard for Dedicated Inputs section.     Updated DC Electrical Characteristics table.     Updated Supply Current table.     Updated ispMACH 4000ZE Timing Model.     Added new parameters for the Internal Oscillator.     Updated 100 TQFP Logic Signal Connections table.     Updated 144 csBGA Logic Signal Connections table with LC4128ZE and 4256ZE.     Updated 144 rQFP Logic Signal Connections table with LC4128ZE and 4256ZE.     Added 144 rQFP Logic Signal Connections table.     Updated Supply Current table.     Updated External Switching Characteristics.     Updated Ordering Information mark format example.     December 2008   01.3     Updated ispMACH 4000ZE Family Selection Guide table to include 64-ball ucBGA and 132 ucBGA packages.     Updated ispMACH 4000ZE Power Supply and NC Connections table to include 64-ball ucBGA packages.     Added Logic Signal Connections tables for 64-ball ucBGA and 132-ball ucBGA packages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | July 2008 01.1 |         | Updated Features bullets.                                                                                           |

| Image: Provide a state of the state of  |                |         | Updated typical Hysteresis voltage.                                                                                 |

| Updated Supply Current table.     Updated I/O DC Electrical Characteristics table and note 2.     Updated ispMACH 4000ZE Timing Model.     Added new parameters for the Internal Oscillator.     Updated ORP Reference table.     Updated 100 TQFP Logic Signal Connections table.     Updated 144 csBGA Logic Signal Connections table with LC4128ZE and 4256ZE.     Updated 144 csBGA Logic Signal Connections table with LC4128ZE and 4256ZE.     Added 144 TQFP Logic Signal Connections table.     Updated Supply Current table.     Updated Supply Current table.     Updated Supply Current table.     Updated Supply Current table.     Updated Internal Timing Parameters.     Updated Ordering Information mark format example.     Updated SupACH 4000ZE Family Selection Guide table to include 64-ball ucBGA and 132-ball ucBGA packages.     Added Logic Signal Connections tables for 64-ball ucBGA and 132-ball ucBGA packages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |         | Updated Power Guard for Dedicated Inputs section.                                                                   |

| Image: December 2008   01.3   Updated ispMACH 4000ZE Timing Model.     Added new parameters for the Internal Oscillator.   Updated ORP Reference table.     Updated 100 TQFP Logic Signal Connections table.   Updated 100 TQFP Logic Signal Connections table with LC4128ZE and 4256ZE.     Updated 144 csBGA Logic Signal Connections table.   Updated 144 csBGA Logic Signal Connections table.     August 2008   01.2   Data sheet status changed from advance to final.     Updated Internal Timing Parameters.   Updated Internal Timing Parameters.     Updated Ordering Information mark format example.   Updated spMACH 4000ZE Family Selection Guide table to include 64-ball ucBGA and 132 ucBGA packages.     Added Logic Signal Connections tables for 64-ball ucBGA and 132-ball ucBGA packages.   December 2008 and 132-ball ucBGA packages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |         | Updated DC Electrical Characteristics table.                                                                        |

| Updated ispMACH 4000ZE Timing Model.     Added new parameters for the Internal Oscillator.     Updated ORP Reference table.     Updated 100 TQFP Logic Signal Connections table.     Updated 144 csBGA Logic Signal Connections table with LC4128ZE and 4256ZE.     Updated 144 rQFP Logic Signal Connections table with LC4128ZE and 4256ZE.     Added 144 TQFP Logic Signal Connections table.     August 2008   01.2     Data sheet status changed from advance to final.     Updated Supply Current table.     Updated Internal Timing Parameters.     Updated Ordering Information mark format example.     December 2008   01.3     Updated ispMACH 4000ZE Family Selection Guide table to include 64-ball ucBGA and 132 ucBGA packages.     Updated Logic Signal Connections tables for 64-ball ucBGA and 132-ball ucBGA packages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |         | Updated Supply Current table.                                                                                       |

| Added new parameters for the Internal Oscillator.     Updated ORP Reference table.     Updated Power Supply and NC Connections table.     Updated 100 TQFP Logic Signal Connections table with LC4128ZE and 4256ZE.     Updated 144 csBGA Logic Signal Connections table with LC4128ZE and 4256ZE.     Added 144 TQFP Logic Signal Connections table with LC4128ZE and 4256ZE.     Added 144 TQFP Logic Signal Connections table with LC4128ZE and 4256ZE.     Added 144 TQFP Logic Signal Connections table.     August 2008   01.2     Data sheet status changed from advance to final.     Updated Supply Current table.     Updated Internal Timing Parameters.     Updated Ordering Information mark format example.     December 2008   01.3     Updated ispMACH 4000ZE Family Selection Guide table to include 64-ball ucBGA and 132-ball ucBGA packages.     Added Logic Signal Connections tables for 64-ball ucBGA and 132-ball ucBGA packages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |         | Updated I/O DC Electrical Characteristics table and note 2.                                                         |

| December 2008   01.3   Updated ispMACH 400ZE Power Supply and Power Supply Supply Currections table with LC4128ZE and 4256ZE.     August 2008   01.2   Data sheet status changed from advance to final.     Updated Supply Current table.   Updated External Switching Characteristics.     Updated Power Consumption graph and Power Estimation Coefficients table.     Updated Ordering Information mark format example.     December 2008   01.3     Updated ispMACH 4000ZE Power Supply and NC Connections table to include 64-ball ucBGA packages.     Added Logic Signal Connections tables for 64-ball ucBGA and 132-ball ucBGA packages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |         | Updated ispMACH 4000ZE Timing Model.                                                                                |

| Updated Power Supply and NC Connections table.     Updated 100 TQFP Logic Signal Connections table with LC4128ZE and 4256ZE.     Updated 144 csBGA Logic Signal Connections table with LC4128ZE and 4256ZE.     Added 144 TQFP Logic Signal Connections table.     August 2008   01.2     Data sheet status changed from advance to final.     Updated Supply Current table.     Updated Internal Timing Parameters.     Updated Ordering Information mark format example.     December 2008   01.3     Updated ispMACH 4000ZE Family Selection Guide table to include 64-ball ucBGA and 132-ball ucBGA packages.     Updated Logic Signal Connections tables for 64-ball ucBGA and 132-ball ucBGA packages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |         | Added new parameters for the Internal Oscillator.                                                                   |

| Image: Provide the i |                |         | Updated ORP Reference table.                                                                                        |

| Image: Provide the i |                |         | Updated Power Supply and NC Connections table.                                                                      |